### 저작자표시-비영리-변경금지 2.0 대한민국

### 이용자는 아래의 조건을 따르는 경우에 한하여 자유롭게

• 이 저작물을 복제, 배포, 전송, 전시, 공연 및 방송할 수 있습니다.

### 다음과 같은 조건을 따라야 합니다:

저작자표시. 귀하는 원저작자를 표시하여야 합니다.

비영리. 귀하는 이 저작물을 영리 목적으로 이용할 수 없습니다.

변경금지. 귀하는 이 저작물을 개작, 변형 또는 가공할 수 없습니다.

- 귀하는, 이 저작물의 재이용이나 배포의 경우, 이 저작물에 적용된 이용허락조건 을 명확하게 나타내어야 합니다.

- 저작권자로부터 별도의 허가를 받으면 이러한 조건들은 적용되지 않습니다.

저작권법에 따른 이용자의 권리는 위의 내용에 의하여 영향을 받지 않습니다.

이것은 이용허락규약(Legal Code)을 이해하기 쉽게 요약한 것입니다.

### 공학박사학위논문

# Silicide Induced Crystallization Phenomenon and Its Application for Low Temperature Polycrystalline Silicon Thin Film Transistors

실리사이드 유도 결정화 현상과 저온 다결정 실리콘 박막 트랜지스터의 적용에 관한 연구

2014년 8월

서울대학교 대학원 재료공학부 변 창 우

# Silicide Induced Crystallization Phenomenon and Its Application for Low Temperature Polycrystalline Silicon Thin Film Transistors

by

Chang Woo Byun

Under supervision of Prof. Seung Ki Joo

A dissertation submitted to the Faculty of Seoul National University in partial fulfillment of the requirements for the degree of Doctor of Philosophy

August 2014

School of Materials Science and Engineering

College of Engineering

Seoul National University.

© Copyright by Chang Woo Byun 2014 All Right Reserved

## 실리사이드 유도 결정화 현상과 저온 다결정 실리콘 박막 트랜지스터의 적용에 관한 연구

# SILICIDE INDUCED CRYSTALLIZATION PHENOMENON AND ITS APPLICATION FOR LOW TEMPERATURE POLYCRYSTALLINE SILICON THIN FILM TRANSISTOS

지도교수: 주 승 기

이 논문을 공학박사 학위논문으로 제출함 2014년 8월

> 서울대학교 대학원 재료공학부 변 창 우

변 창 우의 박사학위 논문을 인준함 2014년 5월

| 위원장  | 주 영 창 | (인) |

|------|-------|-----|

| 부위원장 | 주 승 기 | (인) |

| 위 원  | 임 인 곤 | (인) |

| 위 원  | 배 병 성 | (인) |

| 위 워  | 아 동 휘 | (이) |

#### **ABSTRACT**

# Silicide Induced Crystallization Phenomenon and Its Application for Low Temperature Polycrystalline Silicon Thin Film Transistors

Chang Woo Byun

Department of Materials Science and Engineering

The Graduate School

Seoul National University

After cathode ray tube (CRT) display in 1990s, the liquid crystal display (LCD) using thin film transistors (TFTs) with plasma display panel (PDP) using plasma led the display industry instead of CRT display as a result of the amorphous silicon (a-Si) TFTs have been integrated into the cheap glass substrate. Afterward the TFTs come to essential and fundamental electronic components in virtual all consumer and professional display products, from smart phones to large diagonal flat panel televisions. But recently, the active matrix light emitting diode (AMOLED) display worked by current receives attention from industry and academic. In order to meet the specific needs of AMOLED active material, a new active material having high field effect mobility became urgent requirement instead of a-Si which was used to active material on LCD panel because the a-Si exhibits low field-effect mobility and poor reliability. Many researchers concentrated on polycrystalline silicon (poly-Si), oxide type semiconductors, and organics to find new material. Among the new materials,

the poly-Si has been being focused by many researchers due to its high field-effect mobility and good reliability instead of oxide type compounds and organics having complicated processes, low field-effect mobility, and poor reliability. In industry, the excimer laser crystallization is used for crystallization of a-Si thin film. But its high cost and long time for process act as obstacles to realize the large area and the high resolution AMOLED.

In this study, the metal induced lateral crystallization (MILC), the unique alternate technology to supersede the laser crystallization, was advanced to a novel crystallization method – named silicide induced crystallization (SIC). The developed method could solve the problems of MILC technology such as low field-effect mobility and high leakage current. Particularly, we have concentrated on analyzing the mechanisms of leakage current through classification into two kinds of causes – trap assisted thermionic emission and pure tunneling due to lateral electric field.

In order to obtain a low leakage current with decreasing Ni contamination in the channel of the MILC poly-Si TFTs, the Ni silicide was used for crystallization instead of Ni thin film, and was confirmed the applicability of the low temperature poly-Si TFTs. The Ni silicide used in this study was formed by removal of Ni thin film right after sputtering deposition at room temperature. The Ni silicide density on the a-Si surface was increased with increasing sputtering temperature. Therefore, the net area of grain boundary was increased due to decreased grain size. It was experimentally demonstrated that the increased grain boundary degraded the electrical properties of the SIC poly-Si TFTs.

The silicide induced lateral crystallization (SILC) poly-Si TFTs was also fabricated by using room temperature silicidation demonstrated by SIC. The advantage of room temperature silicidation realized the high performance SILC poly-Si TFTs. Moreover,

the self-aligned structured MILC poly-Si TFTs, having bad electrical properties due to defect at MIC/MILC boundary, were developed by SILC technology.

It is well known that the MILC/MILC boundary (MMB) in the channel greatly affects the electrical properties of MILC poly-Si TFT. In this study, the asymmetrically formed silicide induced lateral crystallization method was also developed in order to eject the SILC/SILC boundary (SSB), formed by same mechanism of MILC growth, from the channel. Both a low off-state leakage current and a free short channel effect (kink effect) were observed in high electric-field conditions. Furthermore, it can be observed that the field-effect mobility and drain current noise were drastically improved by ejecting the SILC boundary in the source direction, when the trapped Ni silicide as scattering source was removed from the channel.

After crystallization using the MIC or SIC, Ni silicide residues remained on the poly-Si surface and they degrade the electrical properties of devices. To remove the remained Ni silicide residues after crystallization, the gettering process was applied in this study. It has noticed that not only the leakage current but also the driving characteristics such as the on-state current, the field-effect mobility, the threshold voltage, and the subthreshold slope were considerably improved by the gettering of Ni silicide in the poly-Si channel. Moreover, the reduced trap state density, main cause of improved electrical performance of gettered SIC poly-Si TFTs, was systemically analyzed through Levinson-Proano plot.

From analysis of second leakage current mechanism – pure tunneling emission at high lateral electric field, the lightly doped drain (LDD) structure was applied to SILC poly-Si TFTs. To form the LDD structure, gate insulator doping mask technique was

used. As a result, the LDD structure effectively suppressed the leakage current at high

reverse bias region.

From the SILC method, the applications were expanded to previous studies on

MILC poly-Si TFTS for better electrical performance. The first one is a channel

splitting. The SILC poly-Si TFT having the split channel exhibits the improved

driving characteristics because the Ni silicides at front of crystallites was filtered

during lateral growth. Furthermore, the effective channel width was enlarged by

channel splitting. The results were systemically analyzed by capacitance measurement

and various electrical analyses. The second one is an electrical stress. The electrical

stress enhanced not only leakage current but also driving characteristics. The electrical

stress mechanism was modeled through experimental measurement at various

electrical condition and computer simulation.

Since the developed processes in this study is not complicated technique, it can be

easily applicable to potential future flat panel display applications.

**Keywords:** active matrix organic light remitting diode (AMOLED), low

polycrystalline temperature silicon (LTPS), metal-induced

crystallization (MILC), thin film transistor (TFT), silicide, gettering, electrical

stress, leakage current, field effect mobility

**Student Number: 2010-30960**

iv

## **Table of Contents**

| Abstract                                           | i  |

|----------------------------------------------------|----|

| Table of contents                                  | v  |

| List of Tables                                     | ix |

| List of Figures                                    | xi |

|                                                    |    |

| Chapter 1. Introduction                            |    |

| 1.1 Thin Film Transistors for Display              | 1  |

| 1.2 Material Issues in TFTs                        | 10 |

| 1.3 Objective of the Dissertation                  | 13 |

| 1.4 Organization of the Dissertation               | 16 |

|                                                    |    |

| Chapter 2. Background and Previous Works           |    |

| 2.1 Low Temperature Polycrystalline Silicon (LTPS) | 19 |

| 2.2 Metal-Induced Lateral Crystallization (MILC)   | 21 |

| 2.3 Poly-Si TFT Device Theories                    | 30 |

| 2.4 Electrical Properties Characterization         | 38 |

| 2.4.1 The $I_D$ - $V_G$ Transfer Characterization  | 38 |

| 2.4.2 The $I_D$ - $V_D$ Output Characterization    | 44 |

|                                                    |    |

### **Chapter 3. Experimental Procedures**

| 3.1 Device Fabrication                                  | 47  |

|---------------------------------------------------------|-----|

| 3.1.1 The Fabrication of Conventional MILC Poly-Si TFTs | 47  |

| 3.1.2 Silicide Induced Lateral Crystallization          | 49  |

| 3.1.3 Gettering                                         | 55  |

| 3.1.4 SILC/SILC Boundary Ejection                       | 58  |

| 3.1.5 Lightly Doped Drain Structure                     | 60  |

| 3.2 Analytical Methods for Thin Film Characterization   | 62  |

| 3.2.1 Auger Electron Spectroscopy (AES)                 | 62  |

| 3.2.2 X-ray Photoelectron Spectroscopy (XPS)            | 65  |

| 3.2.3 Raman Spectroscopy                                | 68  |

| 3.2.4 X-ray Diffraction (XRD)                           | 70  |

| 3.2.5 Scanning Electron Microscopy (SEM)                | 72  |

| 3.2.6 Scanning Probe Microscopy (SPM)                   | 73  |

| 3.3 Electrical Properties Measurement                   | 75  |

|                                                         |     |

| Chapter 4. Reduction of the Leakage Current             |     |

| 4.1 Leakage Current Mechanism in Poly-Si TFTs           | 77  |

| 4.2 Minimization of Ni Contamination                    | 78  |

| 4.2.1 Silicide Induced Crystallization                  | 79  |

| 4.2.2 Silicide Induced Lateral Crystallization          | 97  |

| 4.2.3 Analysis on Improved Electrical Performance       | 117 |

| 4.3 Gettering                                           | 124 |

| 4.3.1 Gettered MIC and SIC Poly-Si TFTs                 | 126 |

| 4.3.2 Gettering Process using Etch Stopper                  | 129 |

|-------------------------------------------------------------|-----|

| 4.4 SILC/SILC Boundary Ejection                             | 133 |

| 4.4.1 Mechanism of SILC/SILC Boundary Formation             | 135 |

| 4.4.2 Electrical Properties of SSB Ejected SILC Poly-Si TFT | 136 |

| 4.5 Lightly Doped Drain Structure                           | 141 |

| 4.5.1 LDD Region on MILC Poly-Si TFTs                       | 142 |

| 4.5.2 Leakage Current Suppression                           | 144 |

|                                                             |     |

| Chapter 5. Enhancement of Driving Characeristics            |     |

| 5.1 Factors Influencing the Driving Characteristics         | 151 |

| 5.2 Channel Splitting Effect                                | 152 |

| 5.2.1 Experimental                                          | 153 |

| 5.2.2 Results and Discussion                                | 156 |

| 5.3 Electrical Stress Effect                                | 169 |

| 5.3.1 Experimental                                          | 169 |

| 5.3.2 Results and Discussion                                | 172 |

|                                                             |     |

| Chapter 6. Conclusion                                       |     |

| 6.1 Summary of Results                                      | 191 |

| 6.2 Future Works and Suggested Research                     | 195 |

|                                                             |     |

| Appendices                                                  | 197 |

| A. Ni-Si Solid-State Reaction                               | 197 |

| B. Dopant Effect on MILC Phenomenon                         | 219 |

| Abbreviation         | <br>227 |

|----------------------|---------|

| Bibliography         | <br>230 |

| Abstract (In Korean) | <br>264 |

| Achievement          | <br>267 |

| Acknowledgement      | 278     |

### LIST OF TABLES

| Table 1.1 | Comparison between (a) AMLCD and (b) AMOLED.                                                |

|-----------|---------------------------------------------------------------------------------------------|

| Table 3.1 | Detailed conditions of fabrication processes for MILC poly-Si TFT                           |

| Table 3.2 | Designations of different crystallization method.                                           |

| Table 4.1 | The relative atomic percentages of each element on the surface of MIC and SIC poly-Si.      |

| Table 4.2 | Device key parameters of the MIC, MILC, and SIC poly-Si TFTs.                               |

| Table 4.3 | Device key parameters of the MILC and SILC poly-Si TFTs.                                    |

| Table 4.4 | Device key parameters of the SA-MILC and SA-SILC poly-Si TFTs                               |

| Table 4.5 | Device key parameters of the MIC, SA-MILC, OS-MILC, SIC, SA-SILC, and OS-SILC poly-Si TFTs. |

| Table 4.6 | Device key parameters of MIC, GMIC, SIC, and GSIC poly-Si TFTs                              |

| Table 4.7 | Device key parameters of the MIC, SIC and G-SIC poly-Si TFTs                                |

| Table 4.8 | Device key parameters of the conventional SILC, drain SSB, and source SSB poly-Si TFTs.     |

| Table 4.9 | Device key parameters of conventional SILC and LDD stricture SILC poly-Si TFTs              |

- Table 5.1

Factors influencing poly-Si TFT performance.

- **Table 5.2** Details of Prepared poly-Si TFTs having various number of splitchannel paths.

- **Table 5.3** Device key parameters of SC-1 (conventional), SC-2, SC-5, and SC-10 poly-Si TFTs.

- **Table 5.4** Various electrical stress conditions and effects on poly-Si TFTs.

- **Table 5.5** Designations for electrical stress model.

- **Table A.1** Ni silicides and their crystal structures, prototype, heat of formation  $\Delta H^0$ , and effective heat of formation  $\Delta H_{\text{eff}}[A.7]$ .

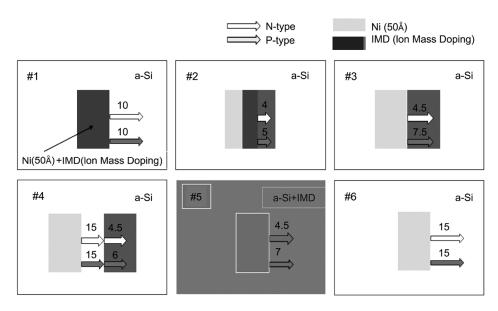

- **Table B.1** IMD conditions. For *n*-type and *p*-type, phosphorus and boron were used, respectively.

### LIST OF FIGURES

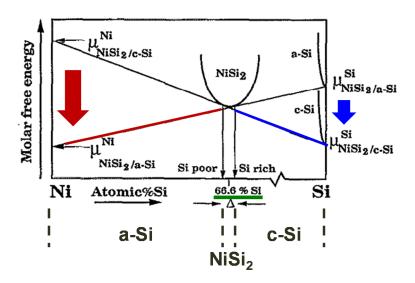

Figure 1.1 Schematic diagrams of (a) Lilinenfeld's patent and (b) Heil's patent about field effect device [1.2, 1.4]. Schematic cross sectional (top) and plan (bottom) views of Figure 1.2 Weimer's top-gate CdS TFT structure [1.5]. Schematic cross sectional of an insulated-gate field-effect transistor Figure 1.3 (IGFET) in crystalline Si [1.8]. Figure 1.4 Schematic structure of an (a) PMLCD and (b) AMLCD. Figure 1.5 Schematic pixel circuit of a pixel in a (a) AMLCD and (b) AMOLED. Figure 2.1 The metal-induced lateral crystallization (MILC) process flows. The microstructure of (a) Pd-induced lateral crystallization (b) Ni-Figure 2.2 induced lateral crystallization. Schematic illustrations of the MILC reaction model. 1<sup>st</sup> step: Si bond Figure 2.3 breaking and coherent adsorption to the interface /1/ (Ni vacancy formation), 2<sup>nd</sup> step: Ni ion and Ni vacancy hopping, and 3<sup>rd</sup> step: Si atom coherent rearrangement – crystallization. Ni-Si phase diagram.  $\beta 1$ : Ni<sub>4</sub>Si,  $\beta_2$  &  $\beta_3$ : Ni<sub>3</sub>Si,  $\Gamma$ : Ni<sub>31</sub>Si<sub>12</sub>,  $\theta$  &  $\delta$ : Figure 2.4  $Ni_2Si_1$ ,  $\varepsilon$ :  $Ni_3Si_2$ . Figure 2.5 Schematic equilibrium molar free-energy diagram for NiSi<sub>2</sub> in contact with a-Si and c-Si.

- Figure 2.6 The phenomenon of caused grain-boundary defects during MILC process.

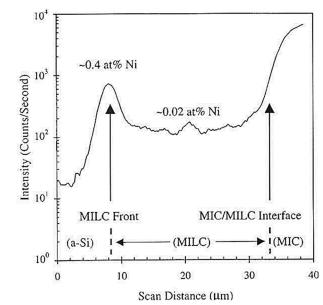

- Figure 2.7 Distribution of Ni across the MIC, the MILC, and the a-Si regions obtained by secondary ion mass spectroscopy (SIMS).

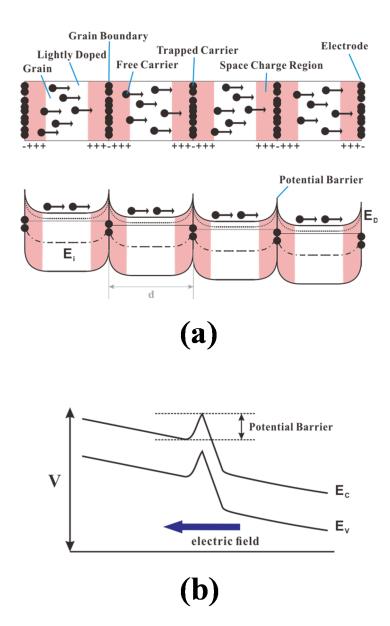

- Figure 2.8 Cross-sectional view of a poly-Si TFT and the potential distribution around the grain boundary.

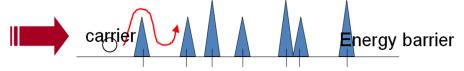

- Figure 2.9 Simple sketch of carrier movement in the poly-Si. The oppositely charged grain boundary defect leads the potential barriers that impede the movement of carriers.

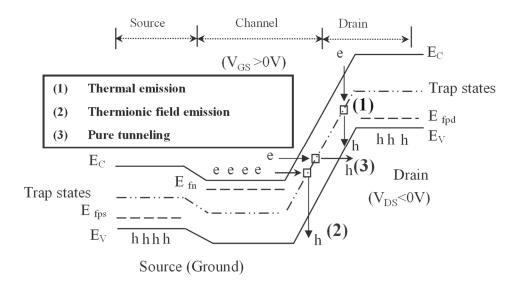

- Figure 2.10 Anomalous leakage current mechanism (1) thermal emission, (2) thermionic emission, and (3) pure tunneling.

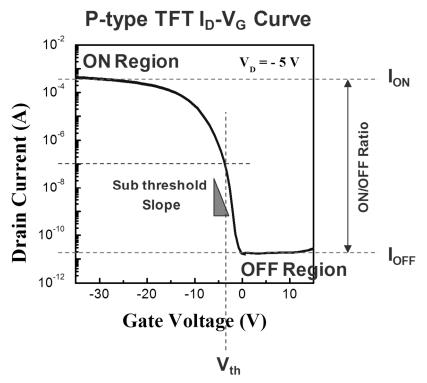

- Figure 2.11 Typical  $I_D$ - $V_G$  transfer characteristics curve. The key parameters such as on-state current, off-state current, subthreshold slope, threshold voltage, and on/off current ratio are represented in the figure. The field-effect mobility was determined from the transconductance at low drain voltage by mathematical calculation.

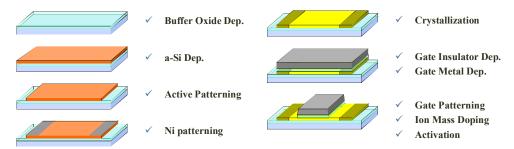

- Figure 3.1 Schematic diagrams of fabrication process for conventional MILC poly-Si TFT.

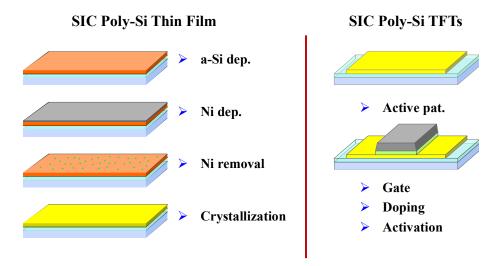

- Figure 3.2 Schematic diagram of fabrication processes for SIC poly-Si thin film and its application for TFT.

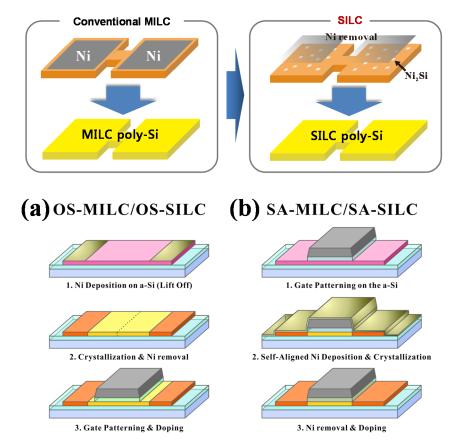

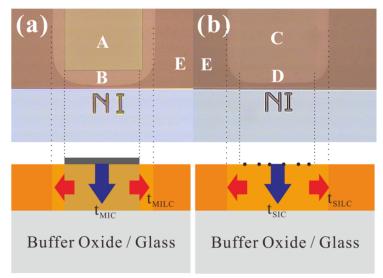

- Figure 3.3 Schematic diagram of fabrication processes for SILC poly-Si thin film compared with conventional MILC poly-Si thin film (Top).

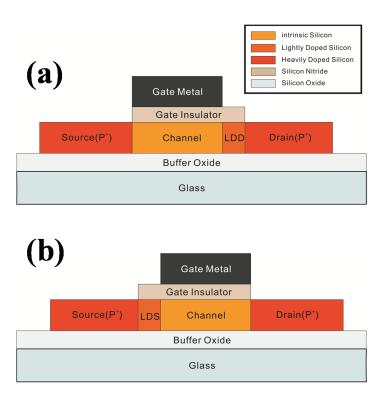

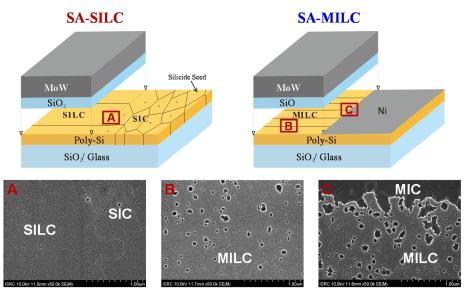

Schematic diagrams for explain of Off-set SILC (OS-SILC) Poly-Si TFT and (b) Self-aligned SILC (SA-SILC) Poly-Si TFT. In order to comparison, The Off-set and Self-aligned MILC poly-Si TFTs fabrication processed are included in the figure.

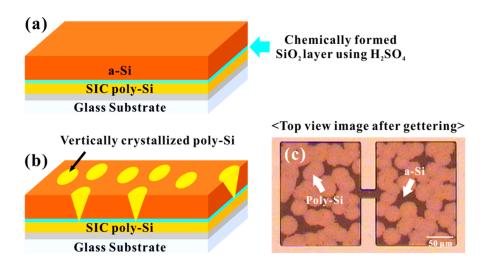

- Figure 3.4 Schematic diagrams and optical microscopy image of key processes for gettered SIC poly-Si TFT, including (a) chemical SiO<sub>2</sub> and gettering layer formation after active layer crystallization, (b) after annealing for gettering, and (c) microscopy top view image of gettering layer after gettering annealing at 550 °C for 2 h.

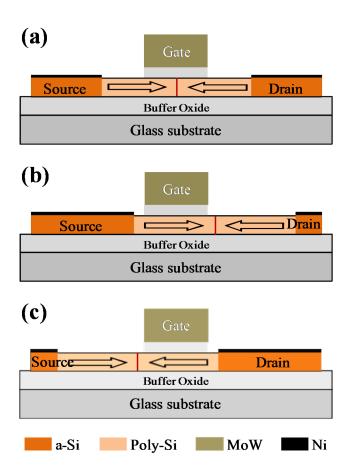

- Figure. 3.5 Schematic diagrams of fabrication processes for (a) conventional SILC, (b) drain-SSB, and (c) source-SSB poly-Si TFTs.

- Figure 3.6 Schematic drawings for two structures with lightly doped region in the channel. (a) The lightly doped drain and (b) lightly doped source structures.

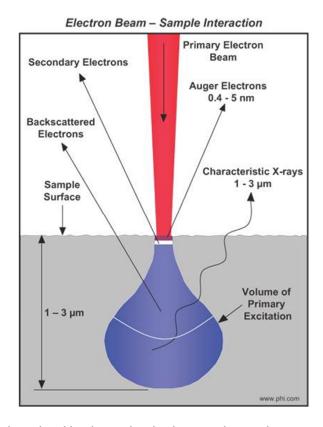

- Figure 3.7 Signals produced by electron bombardment on the sample

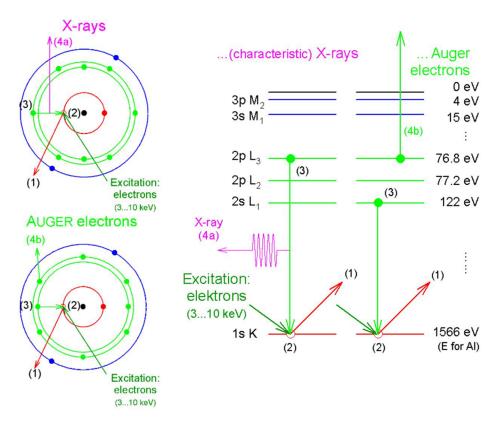

- Figure 3.8 The Auger process for emission of auger electron. The inner shell of an atom is ionized (1), mainly due to electron bombardment. The vacancy (2) is filled by an electron form an outer shell. The released energy is emitted as X-ray (4a) or is transferred by electromagnetic interaction to a 3<sup>rd</sup> electron. If it gets sufficient energy it can leave the atom as Auger electron (4b).

- Figure 3.9 Auger electron spectroscopy fabricated by Phi cooperation, and model name is *phi* 680 scanning Auger nanoprobe.

- Figure 3.10 X-ray photoelectron spectroscopy fabricated by Thermo Scientific VG, and model name is VG ESCA 220 I.

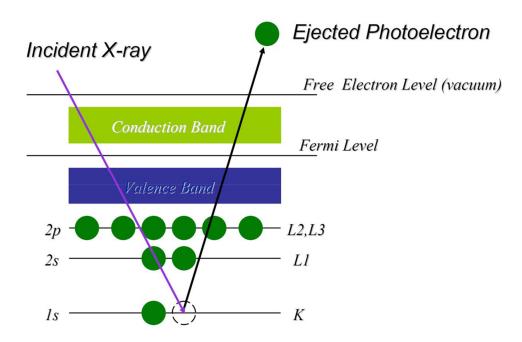

- Figure 3.11 Photoelectron process by interaction between incident X-ray and inner shell electron.

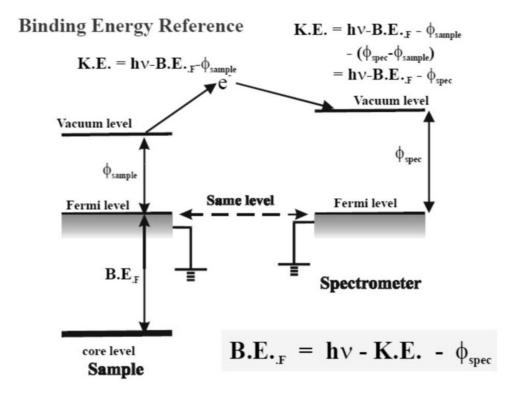

- **Figure 3.12** Graphically representation of the equation  $E_K$ =hv- $E_B$ - $\Phi$ .

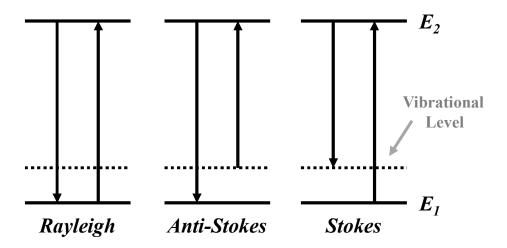

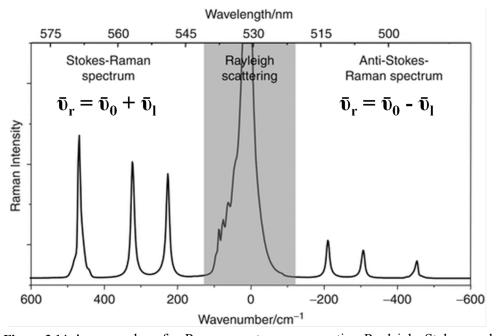

- Figure 3.13 Schematic deposition of various scattering processes within a medium. The incident photon energies are marked by the right-hand-side arrows.

- **Figure 3.14** An examples of a Raman spectrum representing Rayleigh, Stokes, and anti-Stokes Raman peaks.

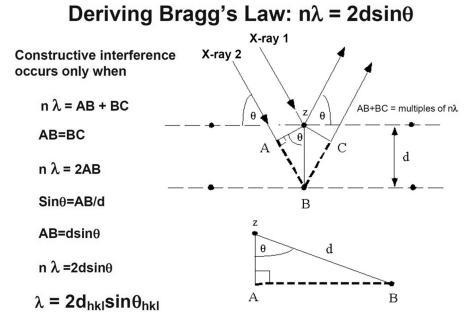

- Figure 3.15 Bragg condition for X-ray diffraction.

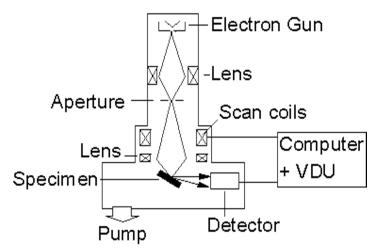

- **Figure 3.16** Schematic of a scanning electron microscopy.

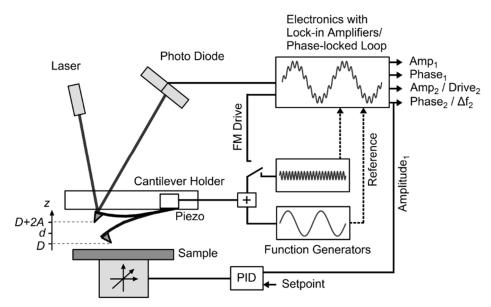

- Figure 3.17 Schematic of an atomic force microscopy (AFM) tip scanning over the surface of a sample.

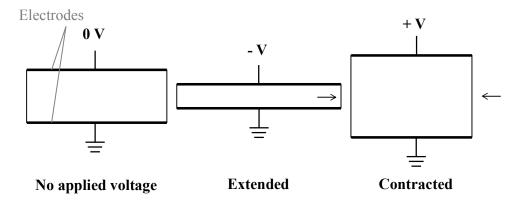

- **Figure 3.18** Reaction of a piezo-material to applied bias.

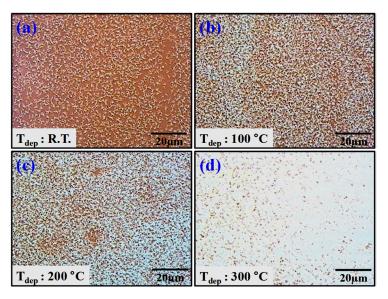

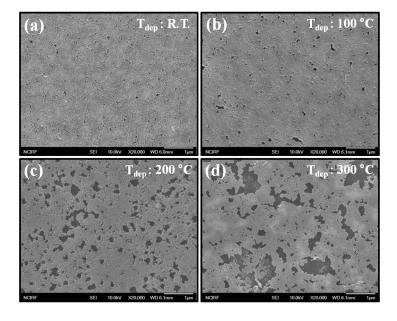

- Figure 4.1 Optical microscope images of Ni silicide seed deposited at various in-situ silicidation temperatures, for which short time annealing was carried out at 550 °C for 30 min.

- Figure 4.2 FESEM images of fully crystallized SIC poly-Si thin-films after Secco etchant treatment.

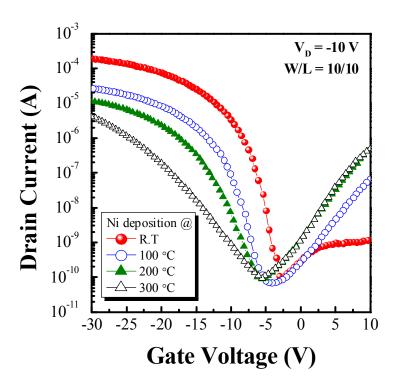

- Figure 4.3 Comparison of  $I_D$ - $V_G$  transfer characteristics of SIC poly-Si TFTs fabricated at various Ni deposition temperatures.

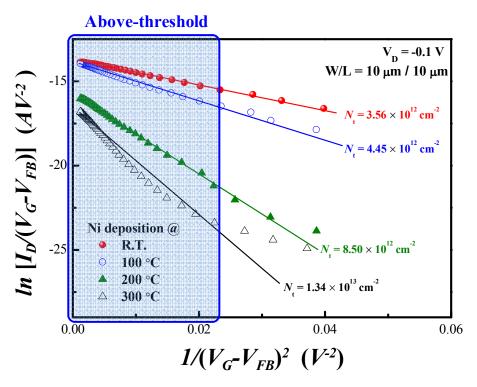

- Figure 4.4 Levinson and Proano plots and grain boundary trap-state densities of SIC poly-Si TFTs fabricated by *in-situ* Ni silicidation at various temperatures.

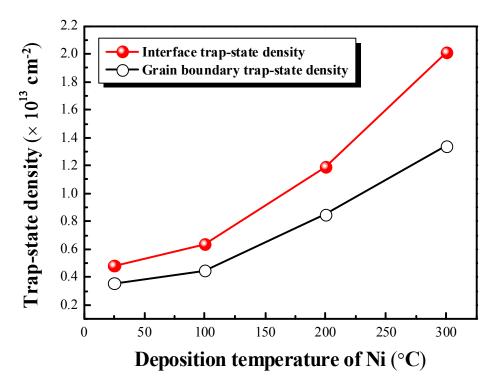

- Figure 4.5 Interface and grain boundary trap-state density changes of the SIC poly-Si TFTs as a function of Ni deposition temperature.

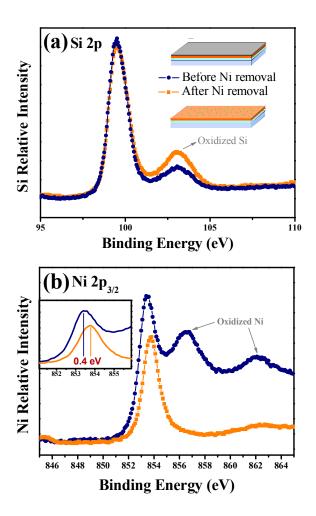

- Figure 4.6 XPS spectra before and after Ni removal on the a-Si films before crystallization. Comparison of (a) Si relative intensity (binding energy around 99 eV) and (b) Ni relative intensity (binding energy around 855 eV).

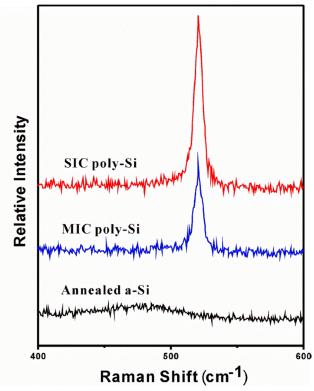

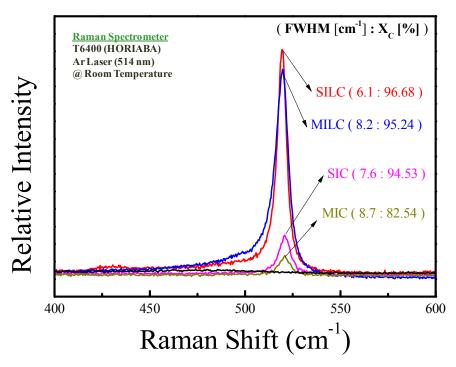

- Figure 4.7 Raman spectra of annealed a-Si, MIC and SIC poly-Si thin films.

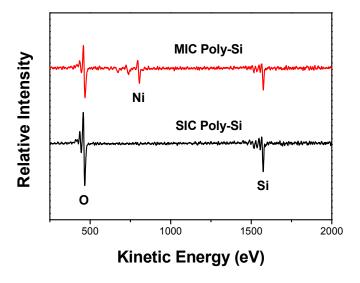

- Figure 4.8 AES spectra of SIC poly-Si and MIC poly-Si thin films (area 50  $\mu$ m  $\times$  50  $\mu$ m) at 500 °C after 1 h of crystallization heat treatment.

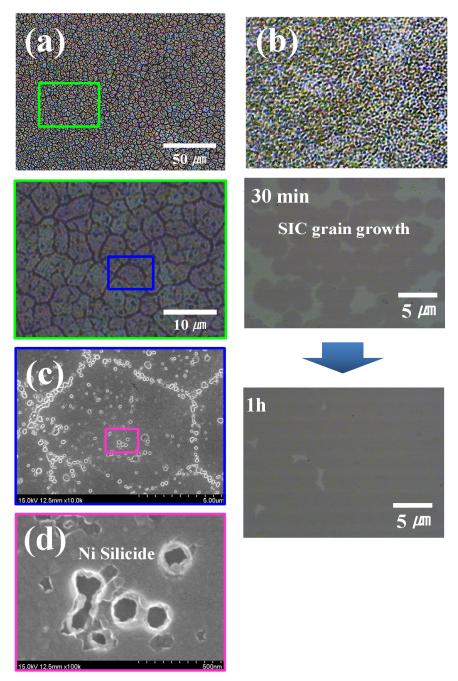

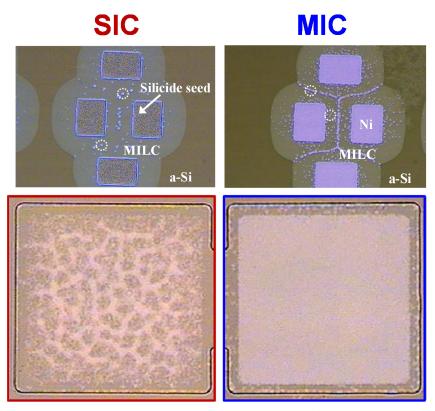

- Figure 4.9 Optical micrographs and SEM images of poly-Si films crystallized by (a) MIC, (b) SIC. (c) and (d) Magnified box areas in (a) and (c) respectively.

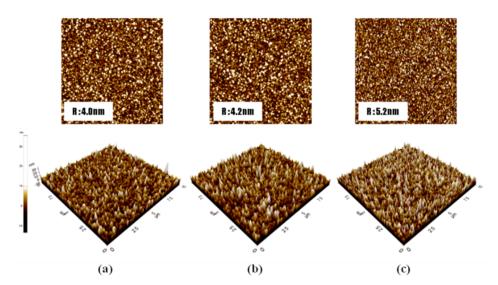

- Figure 4.10 AFM topology and three-dimensional images of the three surfaces (a) a-Si, (b) SIC poly-Si, and (c) MIC poly-Si, after crystallization annealing and subsequent un-reacted Ni removal at 70 °C for 30 in H<sub>2</sub>SO<sub>4</sub> min. R: root mean square (RMS).

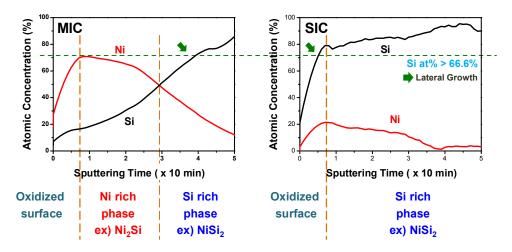

- Figure 4.11 AES depth profiles of Si and Ni concentration in (a) MIC and (b) SIC poly-Si thin films.

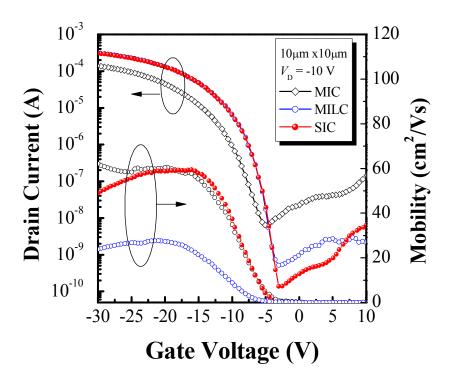

- Figure 4.12 Electrical properties of the *p*-channel poly-Si TFTs fabricated by MIC, MILC, and SIC.

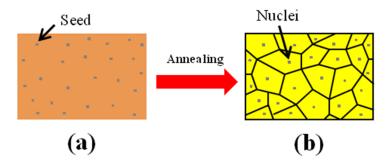

- Figure 4.13 Schematic diagram of the grain growth during crystallization annealing (a) seeds on the a-Si film before annealing (b) SIC poly-Si film after annealing

- Figure 4.14 Schematic diagram of the grain growth during crystallization annealing (a) dot shape of Ni silicide on the a-Si film before annealing (b) SIC poly-Si film after annealing.

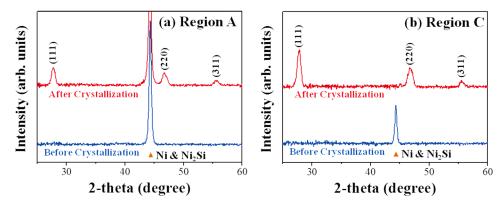

- Figure 4.15 XRD spectra of the MIC and SIC poly-Si thin films before and after crystallization annealing at 550 °C for 4 h.

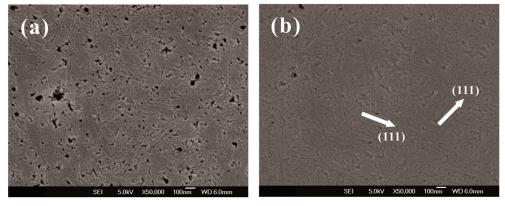

- Figure 4.16 FESEM images of the laterally crystallized poly-Si by (a) conventional MILC (region B) and (b) SILC (region D).

- Figure 4.17 Raman spectra of a-Si film and poly-Si films crystallized by MIC (region A), MILC (region B), SIC (region C), SILC (region D) and a-Si (region E).

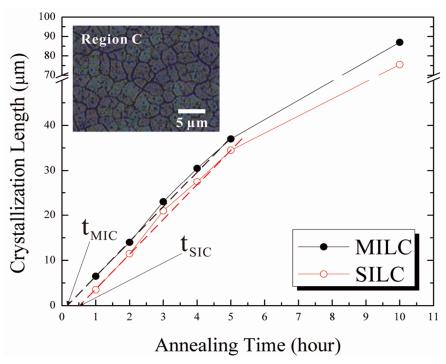

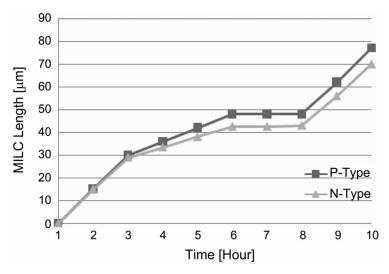

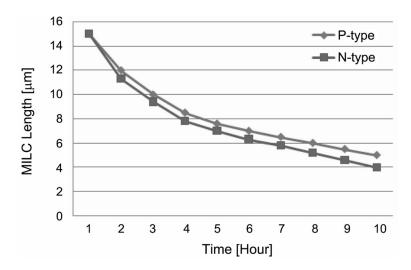

- Figure 4.18 Comparison of conventional MILC and SILC growth lengths as a function of annealing time from 1 to 10 h. Crystallization temperature was fixed at 550 °C.

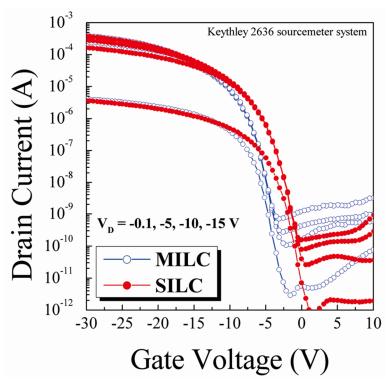

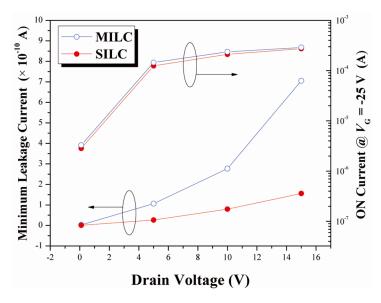

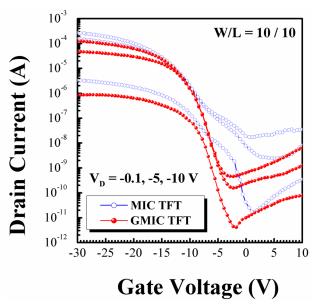

- Figure 4.19  $I_D$ - $V_G$  characteristics of the poly-Si TFTs (Width / Length = 10 / 10  $\mu$ m) fabricated by MILC and SILC. The poly-Si TFTs were measured at  $V_D$  = -0.1, -5, -10, -15 V respectively.

- Figure 4.20 Comparison of the minimum leakage current and on state current between MILC and SILC poly-Si TFTs. The drain voltages was varied from -0.1 to 15 V.

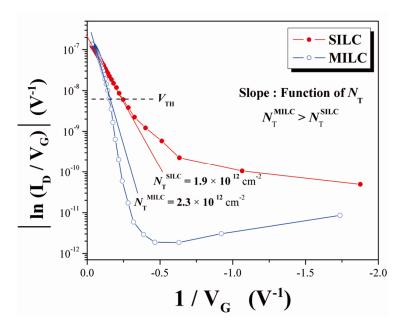

- Figure 4.21 Levinson plot of  $ln(I_D/V_G)$  vs.  $(1/V_G)$  for MILC and SILC poly-Si TFTs.  $I_D$  measured at  $V_D = -0.1$  V.

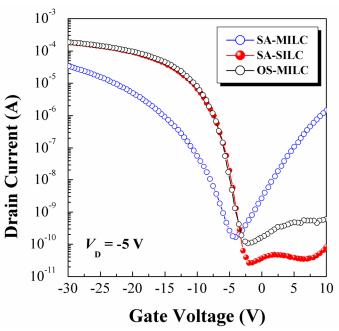

- Figure 4.22  $I_D$ - $V_G$  transfer curves of the poly-Si TFTs (width / Length = 10  $\mu$ m / 10  $\mu$ m) fabricated by SA-MILC and SA-SILC. Conventional OS-MILC poly-Si TFT was referred.

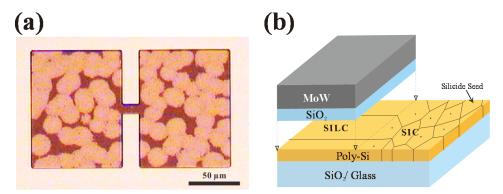

- Figure 4.23 Optical microscope image and schematic diagram of SILC (a)

Optical microscope image after crystallization annealing at 550 °C for 30 min (b) Schematic diagram for SILC. The gate was lifted to reveal the channel area crystallized by SILC.

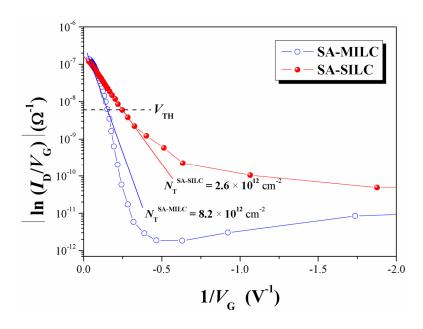

- Figure 4.24 Levinson plot of  $\ln (I_D / V_G)$  vs.  $(1 / V_G)$  for MILC and SILC poly-Si TFTs.  $I_D$  measured at  $V_D = -0.1$  V.

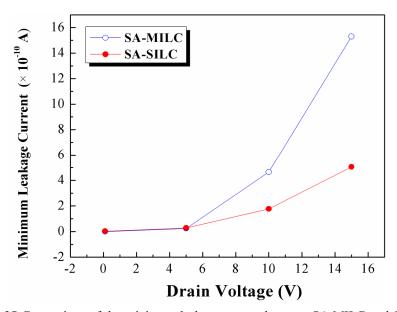

- Figure 4.25 Comparison of the minimum leakage current between SA-MILC and SA-SILC poly-Si TFTs. The drain voltages was varied from -0.1 to -15 V.

- Figure 4.26 Comparison of  $I_D$ - $V_D$  output characteristics of SA-MILC and SA-SILC poly-Si TFTs.

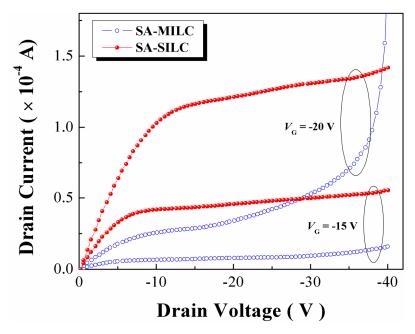

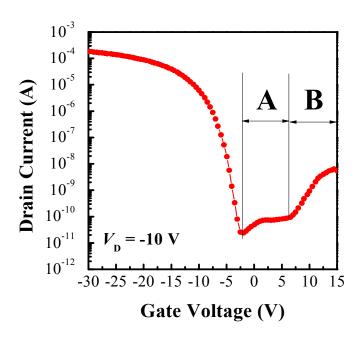

- Figure 4.27 Typical  $I_D$ - $V_G$  transfer curves of conventional MILC poly-Si TFT.

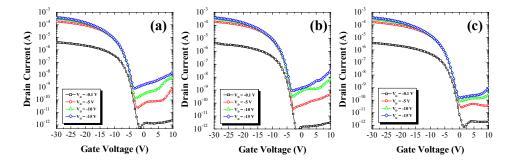

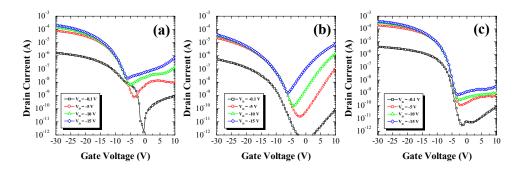

- Figure 4.28 Comparison of  $I_D$ - $V_G$  transfer curves of (a) SIC, (b) SA SILC, and (c) OS SILC.

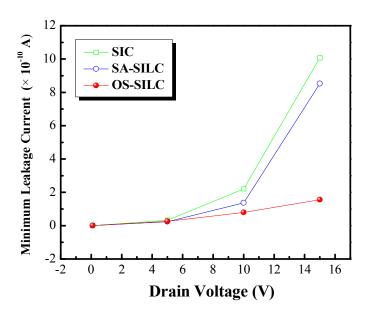

- Figure 4.29 Dependence of the minimum leakage current of SIC, SA-SILC and, OS-SILC as increasing of drain voltage.

- **Figure 4.30** Comparison of  $I_D$ - $V_G$  transfer curves of (a) MIC, (b) SA-MILC, and (c) OS-MILC.

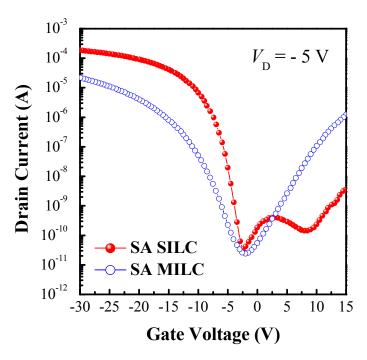

- Figure 4.31  $I_D$ - $V_G$  transfer curves of (a) SA-SILC, and (b) SA-MILC at  $V_D$  = -5 V.

- Figure 4.32 Schematic diagrams of crystallization mechanism of (a) SA-SILC and (b) SA-MILC. The gate was lifted to reveal the channel area crystallized by SILC and MILC.

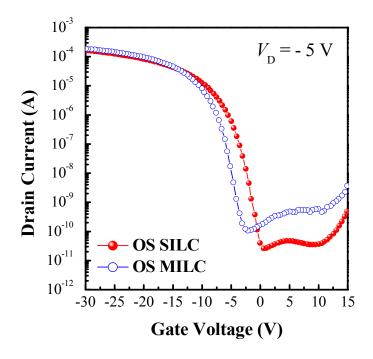

- Figure 4.33  $I_D$ - $V_G$  transfer curves of (a) OS-SILC, and (b) OS-MILC at  $V_D$  = -5 V.

- Figure 4.34 Optical microscope images of partially crystallized 2<sup>nd</sup> Si layer on the (a) metal-induced laterally crystallized and (b) silicide-induced laterally crystallized poly-Si thin films [4.59].; Amount of bright dots were concentrated to the MILC region as well as the MILC/MILC boundary. But, only a few bright dots exist only at the SILC/SILC boundary, and few bright dots exist in the SILC region. Therefore, it was revealed that captured Ni silicides could be reduced by silicide seed.

- Figure 4.35 Typical  $I_D$ - $V_G$  transfer curves of poly-Si TFTs (width / length = 10  $\mu$ m / 10  $\mu$ m) fabricated by MIC and GMIC.

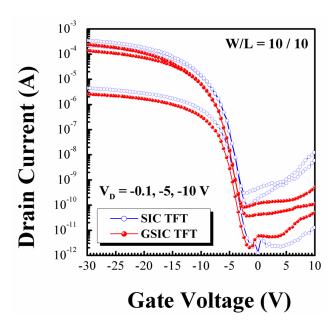

- Figure 4.36 Typical  $I_D$ - $V_G$  transfer curves of poly-Si TFTs (width / length = 10  $\mu$ m / 10  $\mu$ m) fabricated by SIC and GSIC.

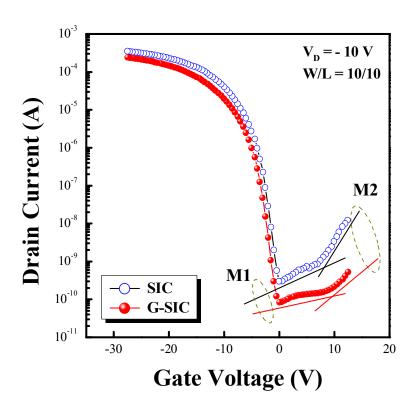

- **Figure 4.37** Comparison of  $I_D$ – $V_G$  characteristics of SIC, and G-SIC.

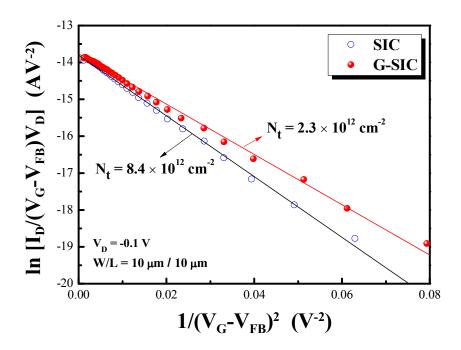

- Figure 4.38 Levinson and Proano plots of SIC and G-SIC poly-Si TFTs with different trap densities in the channel region. The lower slope corresponds to the lower trap density.

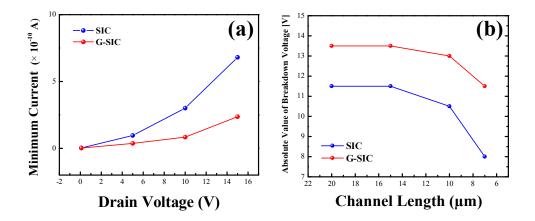

- Figure 4.39 (a) Dependences of the minimum leakage current as the increasing of drain voltage and (b) Drain breakdown voltage versus channel length for SIC TFT and G-SIC TFT.

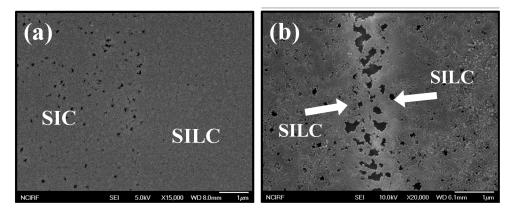

- Figure 4.40 FESEM images of SIC, SILC, and SILC boundary regions. The samples were chemically treated by Secco etchant before analysis.

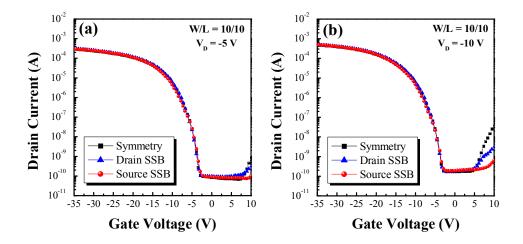

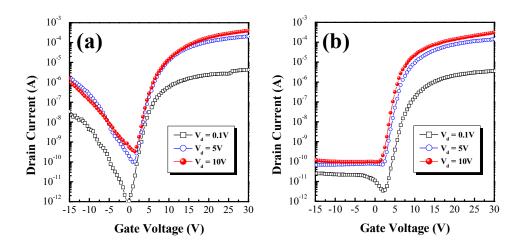

- Figure 4.41 Typical  $I_D$ - $V_G$  transfer curves of conventional symmetrical, drain-SSB, and source-SSB poly-Si TFTs measured at (a)  $V_D$  = -5 V and (b)  $V_D$  = -10 V.

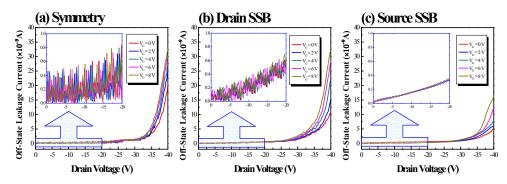

- Figure 4.42 Reverse gate bias dependence of leakage current as a function of drain voltage characteristics for (a) symmetry, (b) drain-SSB, and (c) source-SSB poly-Si TFTs. In each plots, the leakage drain current noise at low drain voltage is shown.

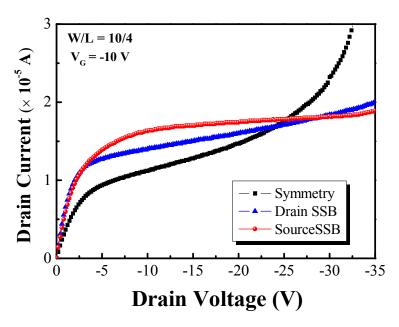

- Figure 4.43 Comparison of  $I_D$ - $V_D$  output characteristics of (a) symmetrical, (b) drain-SSB, and (c) source-SSB poly-Si TFTs.

- Figure 4.44  $I_D$ - $V_G$  transfer curves of (a) conventional MILC poly-Si TFT and (b) GIDM LDD MILC poly- Si TFT.

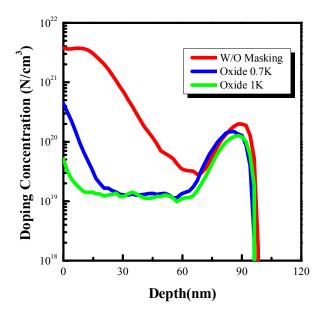

- Figure 4.45 Doping profiles for source/drain and the LDD regions of GIDM LDD TFTs with different gate insulator thicknesses.

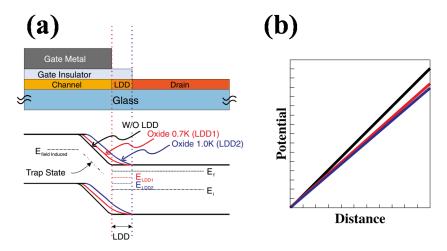

- (a) Energy-band diagrams of the conventional SILC TFT (Without LDD) and GIDM LDD TFT with different gate insulator thickness.

(b) Potential gradients near the drain edge of channel region of the TFTs.

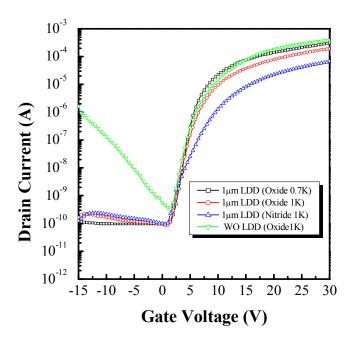

- Figure 4.47  $I_D$ - $V_G$  transfer characteristics of conventional SILC TFT and GIDM LDD SILC poly-Si TFTs with different gate insulators.

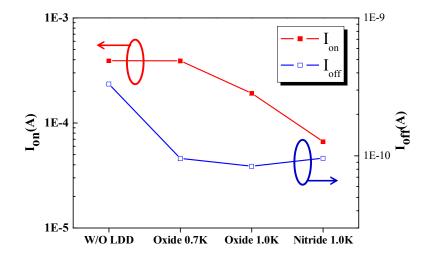

- **Figure 4.48** ON/OFF current variations as a function of gate insulator thickness.

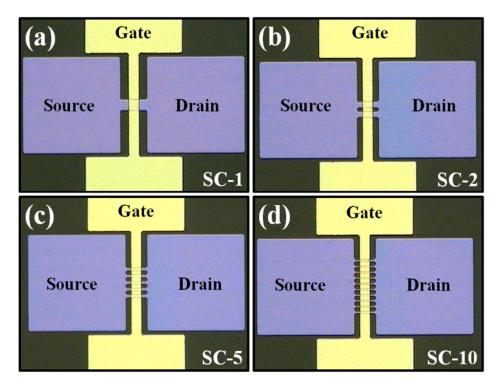

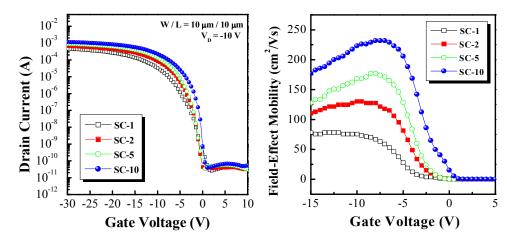

- Figure 5.1 Optical microscope top view images of split channel poly-Si TFTs with W/L = (a)  $10 \mu m / 10 \mu m \times 1$ , (b)  $5 \mu m / 10 \mu m \times 2$ , (c)  $2 \mu m / 10 \mu m \times 5$ , and (d)  $1 \mu m / 10 \mu m \times 10$ .

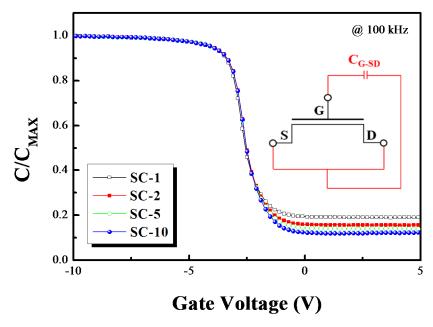

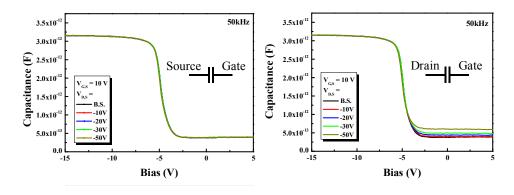

- Figure 5.2 Comparison of  $C_{GSD}$ - $V_G$  characteristics of SC-TFTs having a various number of split channels. The inset figure shows the measurement circuit.

- Figure 5.3 Comparison of  $C_{GSD}$ - $V_G$  characteristics of SC-TFTs having a various number of split channels. The inset figure shows the measurement circuit.

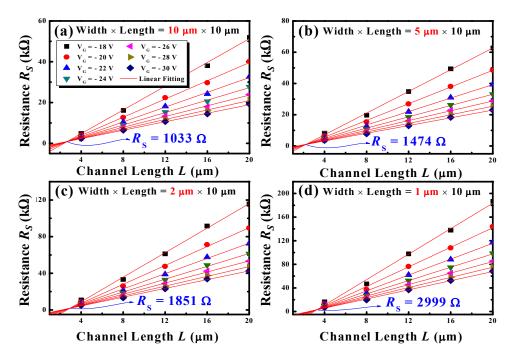

- Figure 5.4 Series resistances versus channel length as a function of gate voltage for various channel widths of (a) 10  $\mu$ m, (b) 5  $\mu$ m, (c) 2  $\mu$ m, and (d) 1  $\mu$ m, respectively.

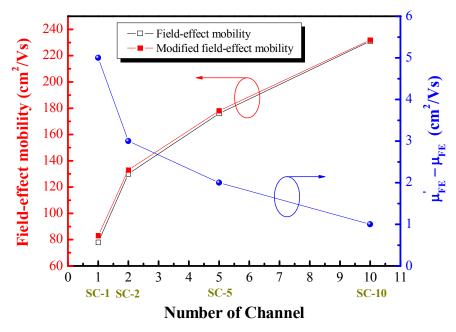

- Figure 5.5 The changes of field-effect mobility and modified field-effect mobility as a function of various split channel poly-Si TFTs. The quantity of field-effect mobility degradation is also shown.

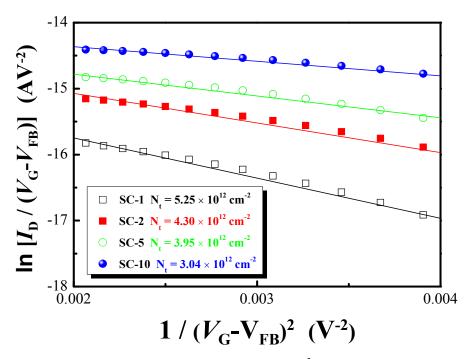

- Figure 5.6 The Plots of  $\ln[I_D/(V_G-V_{FB})]$  versus  $1/(V_G-V_{FB})^2$  of SC-TFTs having a various number of spilt channels. The plots were determined from the Levinson and Proano method at  $V_D = -0.1$  V and high  $V_G$ .

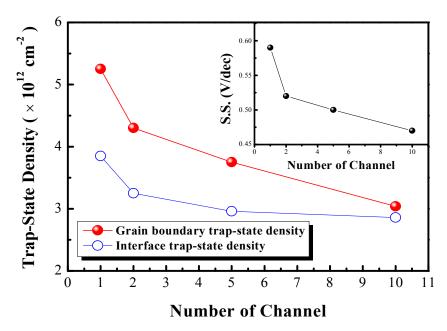

- Figure 5.7 The changes of grain boundary trap-state density and interface trap-state density versus four different poly-Si TFTs (SC-1, SC-2, SC-5, and SC-10) having a various number of split channels.

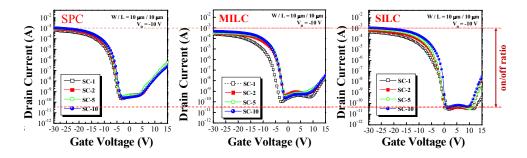

- Figure 5.8 The comparison of channel splitting effect on SPC, MILC, SILC poly-Si TFT.

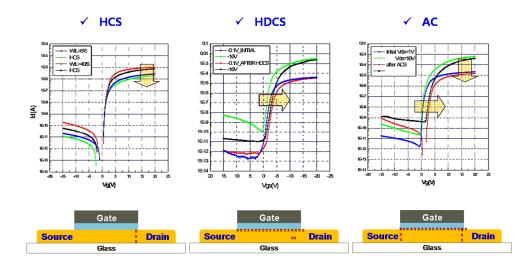

- Figure 5.9 Various electrical stress effects and mechanisms. The detailed conditions are summarized in Table 5.4.

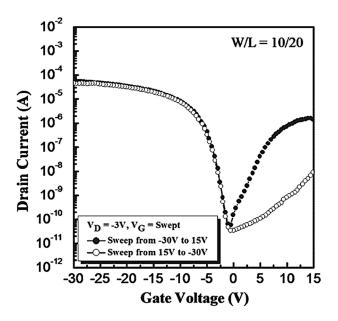

- **Figure 5.10** Initial  $I_D$ - $V_G$  curves of p-type SILC TFT. Two different leakage currents are shown depending on the sweeping direction of the gate voltages.

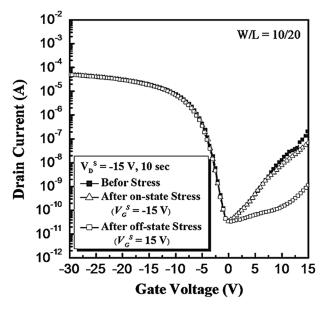

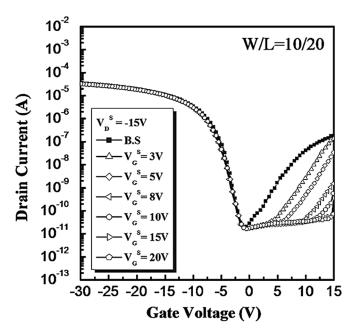

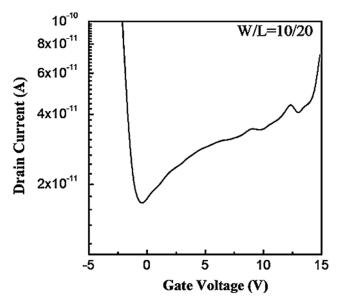

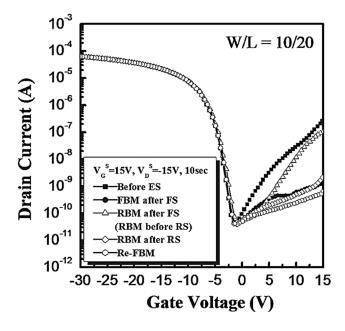

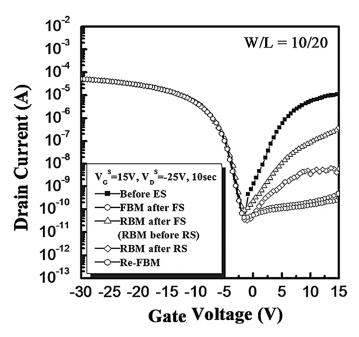

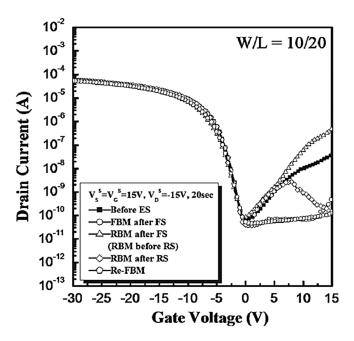

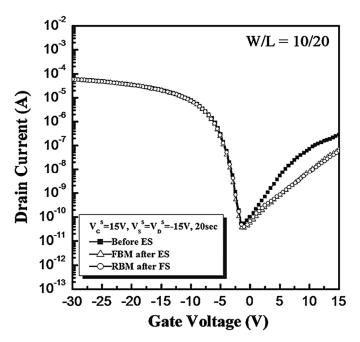

- Figure 5.11 Effect of the stress conditions on the leakage current in P-type SILC TFT. The stress conditions are  $V_G^S = \pm 15 \text{ V}$ ,  $V_D^S = -15 \text{ V}$ , for 10 sec.

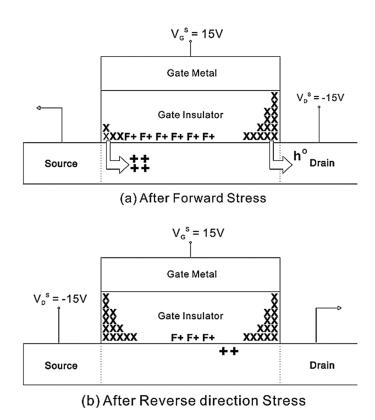

- Figure 5.12 Illustration of a charge distribution (a) after the forward electrical stress and (b) the reverse electrical stress.

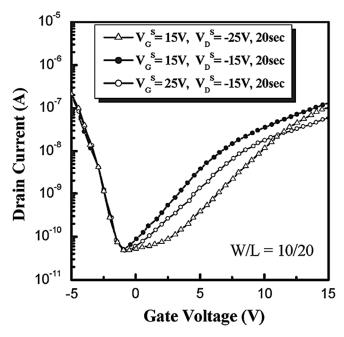

- Figure 5.13 Gate stress voltage on the leakage current in *p*-type MILC TFT.  $V_D^S$  was -15 V and the measurement was done at  $V_D = -3$  V.

- Figure 5.14 The leakage current after the electrical stress of  $V_D^S = -15 \text{ V}$ ,  $V_G^S = 20 \text{ V}$ . The measurement was done at  $V_D = -3 \text{ V}$ .

- Figure 5.15 Effect of the electrical stress bias on the leakage current behavior in *p*-channel MILC TFT.

- **Figure 5.16** The leakage current behavior under the different stress conditions.

- Figure 5.17 The leakage currents at the high drain voltage stress conditions.

- Figure 5.18 The leakage current behavior when the gate and the source are connected.

- Figure 5.19 The leakage current behavior when the source and the drain are connected.

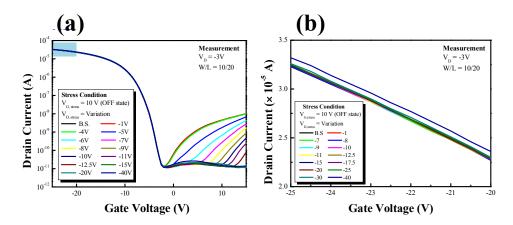

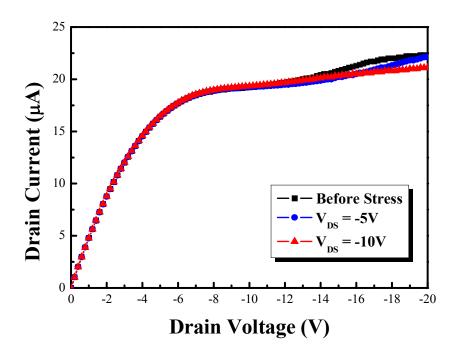

- Figure 5.20 Changes of  $I_D$ - $V_G$  transfer characteristics before and after electrical stress for various stress drain voltages. The magnified curves of onstate current are shown in (b).

- Figure 5.21 The on-state current changes as functions of stress drain voltage (red circle) and time (blue square).

- **Figure 5.22** Computer simulation (ATLAS) of the electric field distribution along the channel during electrical stress.

- Figure 5.23 Illustration of on-state current increase mechanism which is hot electron induced channel length shortening during the electrical stress.

- Figure 5.24 Drain current measurement with pulsed electrical stress for three times. Every electrical stress was applied for 10 sec.

- Figure 5.25  $I_D$ - $V_G$  output characteristics of poly-Si TFT before and after electrical stress. The electrical stress was applied at  $V_G = 10$  V and  $V_D = -5$ , -10 V respectively.

- **Figure 5.26** C-V curves of poly-Si TFT after electrical stress with various  $V_{DS}$ . (a) Gate to source capacitance. (b) Gate to drain capacitance.

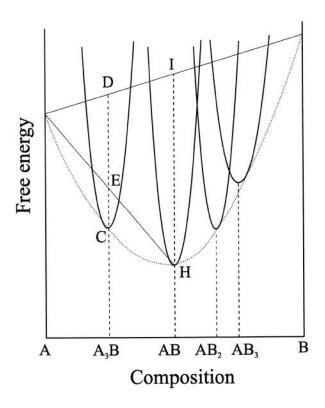

Figure A.1 The parabolic variation of free energy as a function of composition for several phases in an A/B binary system at a temperature T [A.1]. The system A/B is not in thermodynamical equilibrium. Upon heating, the system will form intermediate phases in order to lower its free energy. The presented system is representative for a typical M/Si system.

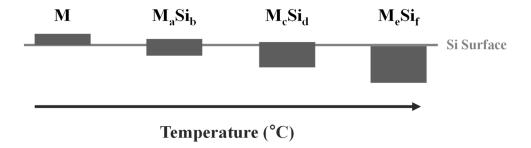

Figure A.2 Simplified representation of the sequential formation of intermediate  $M_x Si_y$  silicide phases upon heating of a metal (M) deposited on a Si substrate. Generally, Si is consumed and the sequential silicides are more Si rich.

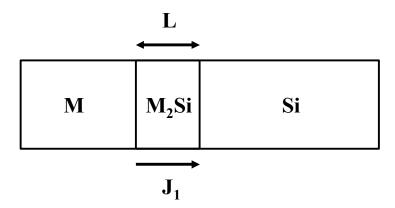

**Figure A.3** Representation of diffusion controlled growth of phase  $M_2Si$ , by reaction of a metal M and substrate Si. M is the most mobile species and diffuses through the phase (with increasing thickness L) to the  $M_2Si/Si$  interface resulting in systematic further growth of  $M_2Si$ .  $J_1$  represents the flux of atoms through the layer.

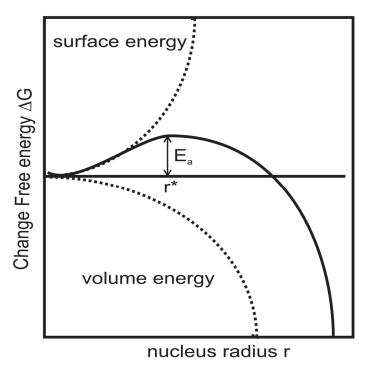

**Figure A.4** Graphical representation of the energy balance associated with formation of a nucleus with radius r.

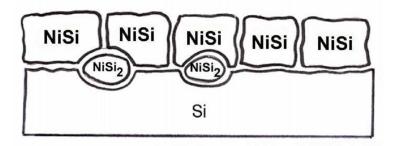

Figure A.5 Nucleation of  $NiSi_2$  through  $NiSi + Si \rightarrow NiSi_2$ . The figure illustrates both homogeneous (at a double grain boundary site) and heterogeneous nucleation (at a triple grain boundary site).

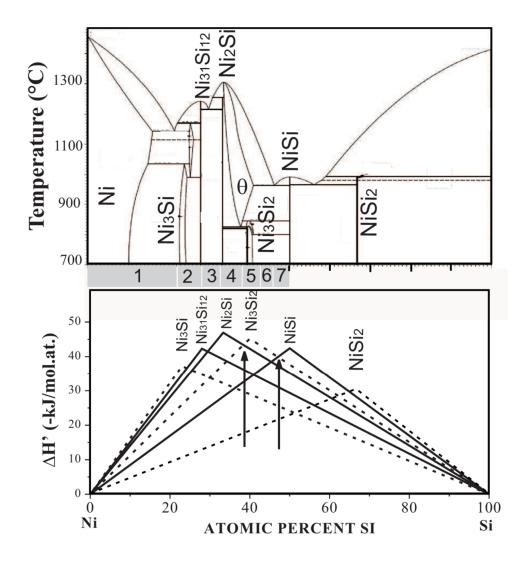

Figure A.6 The  $\Delta H_{\rm eff}$  diagram and phase diagram for the Ni-Si system. The dashed lines indicate non-congruent phases. Note that the values for  $\Delta H'$  of  $\delta$ -Ni<sub>2</sub>Si and NiSi are nearly identical and cannot be distinguished when taking into account typical error bars on thermodynamic data [A.7].

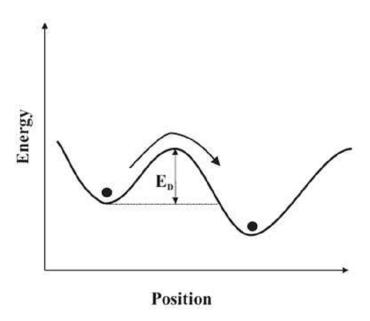

- Figure A.7 Illustration of the atomic diffusion process on microscopic scale (figure taken from [A.12]).  $E_D$  represents the diffusion activation energy.

- **Figure B.1** The rate of MILC annealed at 550 °C for 2h after IMD

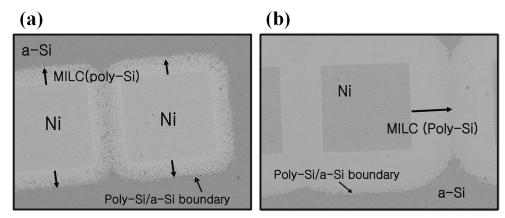

- **Figure B.2** MILC dependency on doped area.  $B_2H_6$  and  $PH_3$  were doped after the deposition of Ni thin films and they were annealed at 550 °C 4 times.

- Figure B.3 Optical microscope images of crystallized Si in case of (a) doped Si and (b) undoped Si.

- **Figure B.4** MILC dependency on doping time.  $B_2H_6$  and  $PH_3$  were doped 2 times interval after the Ni thin film deposition.

### **CHAPTER 1**

### Introduction

### 1.1 Thin Film Transistors for Display

HIN FILM TRANSISTORs (TFTs) have been intensively researched for possible electronic and display applications in the last two decade, and become the main stream of the electronic flat panel display industry, just as Si chips were earlier called the rice or staple of the computer revolution. Tens of giants factories today produce millions of displays each year, with each display incorporating several million thin film transistors.

How we got to this point is an interesting tale of technology evolution and development that stretches over nearly 70 years, going back to the earliest days of semiconductor physics. It was at that time that materials were first being classified according to their electronic structure so that semiconductors were understood not just as materials with conductivity intermediate between that of metals and insulator, but as crystalline materials with small number of mobile charges per unit cell and a distinguishing temperature dependence of conductivity. Looking back, we can see that the concept of the thin-film transistor and its potential utility significantly predated the

device that gave rice to the term "transistor". Indeed, for many years it was overshadowed by the astounding developments associated with the original bipolar transistor and its technological cousin, the metal oxide semiconductor field-effect transistor (MOSFET) [1.1].

In this chapter we will systematically introduce, how the TFT has evolved in materials and structure to the forms most widely used today.

### 1.1.1 History of Thin-Film Transistors

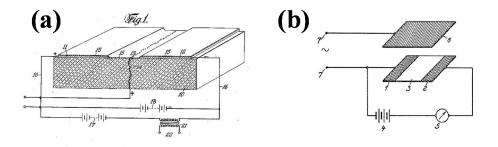

It is mostly cited in papers that field-effect device was firstly invented by Lilienfeld in his patent in 1934 - Figure 1.1(a) [1.2], but as argued by Brody [1.3]. Heil has a more solid claim to the inventorship of TFT in his patent in 1935 - Figure 1.1(b) [1.4] in which Heil showed the knowledge and understanding of semiconductors and showed a correct device structure. However, these two patents seem to be concept patents only without any indication of practice or experimental.

**Figure 1.1** Schematic diagrams of (a) Lilinenfeld's patent and (b) Heil's patent about field effect device [1.2, 1.4].

Based on understanding of the Schottky diode, i.e., a metal-semiconductor contact, Shockley represented the invention of the metal-semiconductor field-effect transistor (MESFET) in 1939. In his first idea of a triode where a grid embedded in semiconductor material could be used to deplete a zone between the cathode and anode, cutting off the flow of current. After realizing such a structure might be difficult to make, he adapted to applying an electric field to a semiconductor film by making use of an insulator and a gate electrode. He made a thin-film field-effect device with a germanium film. However, the device performance was disappointing as the change in the conductivity observed was far smaller than that of theoretically expected based on the gate capacitance because of the lower carrier mobility of the induced charges and the existence of a large number of surface states.

**Figure 1.2** Schematic cross sectional (top) and plan (bottom) views of Weimer's top-gate CdS TFT structure [1.5].

The history of the TFT really began with the work of P. K. Weimer at RCA laboratories in 1962 [1.5]. He used a thin-film of polycrystalline cadmium sulfide (CdS), together with insulating films such as Si monoxide in a staggered structure, with the source and drain contacts on the opposite side of the film from the gate - Figure 1.2. Weimer achieved a transconductance of 25000 μA/V for a gate capacitance value of about 50 pF and oscillation frequency close to 20 MHz. Shortly after Weimer's report, F. V. Shallcross [1.6] reported very similar results for TFTs made with cadmium selenide (CdSe). In 1964 Weimer reported *p*-channel TFTs with tellurium as the active material [1.7].

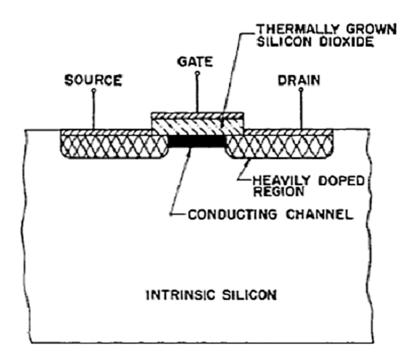

**Figure 1.3** Schematic cross sectional of an insulated-gate field-effect transistor (IGFET) in crystalline Si [1.8].

With the appearance of insulated-gate field-effect transistor (IGFET) – Figure 1.3 [1.8], now known as MOSFET, in 1962 and the probability of more dense integrated circuit chips, the expectation of cost saving with TFT technology is difficult to sustain. This led to a decline in TFT development activity by the end of the 1960s. The golden opportunity for TFTs appeared again when people noticed that low cost is inseparable from small chip size for crystalline Si and at the same time large arrays of low-cost electronics are required for some applications, such as liquid crystal displays. By 1973 T. P. Brody and his group had demonstrated a liquid crystal display with CdSe TFTs [1.9]. However, such kinds of TFTs suffer from poor DC stability [1.10].

After it had been discovered that hydrogenated amorphous Si (a-Si:H), in contrast to pure amorphous Si (a-Si), could be doped with donors or acceptors to induce *n*- or *p*-type conductivity [1.11], TFTs using a-Si as the active material was introduced in 1979 [1.12]. Up to the end of 1980s, many companies had mastered the art of making a-Si TFTs having considerably good electrical performances such as low off current (<1 pA), good on/off ratio (>10<sup>7</sup>), reasonable mobility (0.5-1.0 cm²/Vs) and good stability. Low temperature polycrystalline silicon (LTPS) TFTs were fabricated by Morozumi *et al.* [1.13] with a low off current (<0.1 pA) and a high on/off ratio (>10<sup>7</sup>), but the mobility is low (~2-3 cm²/Vs). High performance polycrystalline silicon (poly-Si) TFTs were fabricated by recrystallization of a-Si to poly-Si as active layer at a high temperature [1.14]. LTPS TFTs with characteristics as good as that of high temperature poly-Si TFTs were reported by Little *et al* [1.15] in 1991. In 1990 a new class of TFT based on organic semiconductor active layer material was reported [1.16] and afterwards investigated intensively for the fabrication of displays on flexible substrates.

### 1.1.2 Flat Panel Displays (FPDs)

Electronic displays, including cathode-ray tube (CRT), plasma display panel (PDP), light-emitting diode (LED) display, organic light-emitting diode (OLED) display, liquid crystal display (LCD), etc., are widely used in our personal and professional lives. They are of different structures, advantages, and operation principles.

The CRT is the oldest while still an important electronic display technology. It is widely has been used for televisions (TVs) and personal computer (PC) monitors. It has the advantages including mature manufacturing, high display quality in brightness contrast ratio, resolution, color rendering, response and view angle, and at the same time, intrinsic disadvantages including large volume, heavy weight, high power consumption and large heat generation.

Owing to its obvious advantages, such as thin, light, small volume, low power dissipation, which just remedy the drawbacks of CRT, flat-panel display (FPD) is becoming a more and more important branch of electronic displays. This technology develops fast and occupies a larger display market. LCD is the most important FPD technology and takes up to 75% f the FPD market [1.17].

Addressable LCDs can be separated into two types, passive-matrix (PM) and active-matrix (AM) LCDs.

#### Passive-Matrix-Liquid Crystal Display (PMLCD)

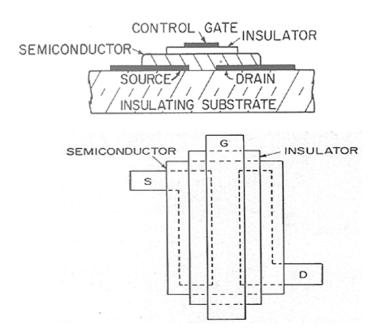

The schematic structure of an PMLCD is shown in Figure 1.4(a). The PM LCDs use a simple grid to supply the voltage to a particular pixel on the display. Such grids are created starting with two glass layers called substrates. One substrate is given columns. The other is given rows. The rows or columns are connected to integrated

Figure 1.4 Schematic structure of an (a) PMLCD and (b) AMLCD.

circuits that control the time when a voltage is sent down a particular column or row. The liquid crystal material is sandwiched between these two glass substrates. To turn on a pixel, the integrated circuit sends a voltage down the correct column of one substrate and a ground activated on the correct row of the other. The row and column intersect at the designated pixel, and that delivers the voltage to control the liquid crystals at that pixel. The drawbacks of PM include slow response time and imprecise voltage control, which will result in "ghost" and fuzzy images or images lacking in contrast, respectively.

The PM is typically restricted to small display sizes due to issues with image quality that arise as the size and resolution of the display increase. Improvements on

the liquid crystal material and the associated addressing schemes have extended the applicability range of PM addressed panels beyond the limits predicted by conventional technologies. Despite such improvements, however, the intrinsic limitations of PM technology have restricted the application range of PM panels and positioned AM addressing as the technology of choice for high-end display applications.

#### Active-Matrix-Liquid Crystal Display (AMLCD)

The schematic structure of an AMLCD and the schematic pixel circuit are shown in Figure 1.4(b) and Figure 1.5(a), respectively. AM addressing uses independent electronic switches to individually control the state of each pixel. In this manner, the display performance is free of the shortcomings of PM addressing schemes. AM essentially consists of TFTs, storage capacitor and peripheral driver circuits. The peripheral driver circuits could be either implemented in the form of Si chips which are then mounted onto the substrate or directly fabricated on the substrate when the TFT arrays are fabricated.

The schematic structure of an AMLCD and the schematic pixel circuit are shown in Figure 1.4 and Figure 1.5a, respectively. TFTs are needed to charge pixel capacitors, each consisting of a liquid crystal capacitor ( $C_{lc}$ ) and a storage capacitor ( $C_s$ ). When the TFTs in one row are turned on, data writing will be performed in the pixels of this row with  $C_{lc}$  and  $C_s$  charged up, the pixels in other rows will not be affected. When the TFTs are turned off, charge stored in the storage capacitors will be held for a limited period of time until the next refresh cycle. The hold voltage signal is used to control the state of the liquid crystal molecule and determine the optical state of the pixel.

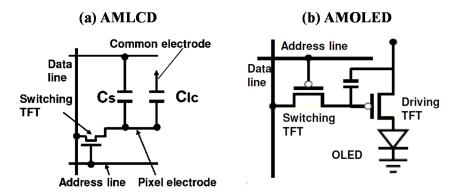

Figure 1.5 Schematic pixel circuit of a pixel in a (a) AMLCD and (b) AMOLED.

**Table 1.1** Comparison between (a) AMLCD and (b) AMOLED.

|                     | AMLCD                                                               | AMOLED Poly-Si                                  |  |

|---------------------|---------------------------------------------------------------------|-------------------------------------------------|--|

| Active<br>Materials | a-Si                                                                |                                                 |  |

| Mobility            | Low mobility (0.5~1 cm²/Vs)  Low current  Low definition (TFT size) | High mobility (20~250cm²/Vs)<br>High definition |  |

| Driving             | Voltage Driving                                                     | <b>Current Driving</b>                          |  |

| Problem             | Only N-type Driving Ohmic contact problem between silicon and TCO   | Crystallization Process                         |  |

| Flexible            | Bad<br>- Cell-gap change<br>- Back light unit                       | Good                                            |  |

| Transparent         | Bad<br>- Color Filter, Back Light Unit                              | Good                                            |  |

| 3-D                 | Good                                                                | Bad                                             |  |

### Active-Matrix Organic Light-Emitting Diode (AMOLED)

OLED display is another important branch of FPDs, which shows great potential to replace LCD due to its superior characteristics, such as self-emission, video rate response, wide view-angle and thin form factor. Unlike the optical state of a pixel in a

LCD that can be voltage-switched using a single TFT, current-controlled emission of an OLED pixel requires at least two TFTs, one as a switch and the other as a current supplier as shown in Figure 1.5(b). Sometimes, four or more TFTs are used to compensate for the dispersed threshold voltages and drain currents of the driving TFTs to improve the display uniformity. The switch TFT's function is similar to that in AMLCD to control the transferring of the data signals. When the switch TFT is turned on, the data signals are transferred to the gate of the driving TFT and a corresponding driving current will be supplied to the OLED. The storage capacitor will be charged up at the same time. The data signals maintained by  $C_s$  allow the driving TFT to continue supplying current to the OLED when the switch TFT is turned off. The comparison between AMLCD and AMOLED is briefly shown in Table 1.1.

### 1.2 Material Issues in TFTs

#### 1.2.1 Amorphous Silicon (a-Si)

The a-Si:H was first used as an active channel material to fabricate TFTs for switches of LCD. Also a-Si is widely used as low cost solar cell material. The advantage of a-Si is the low temperature process (below 300 °C), good uniformity and low cost. However, the disadvantage of a-Si is its poor stability and low field-effect mobility due to the large amount of dangling bonds which acts as recombination states of electrons and holes. The devices show considerable threshold voltage shift during

operation. The low field-effect mobility of a-Si TFT (~1 cm<sup>2</sup>/Vs) constraints future application for OLED or high performance circuits.

### 1.2.2 Oxide Type Semiconductors

Transparent conductive oxides (TCOs) are unique materials because they are both electrically conductive and visually transparent. Initially, they are widely used as simple passive electrical or optical coatings, such as in antistatic coatings, touch display panels, solar cells, flat panel displays, and optical coatings. The TCOs such as indium-tin oxide (ITO) and zinc oxide (ZnO) have found applications as electrical interconnections and as window electrodes in FPDs and solar cells. Recently ZnO has attracted lots interest in the application as channel material for TFTs with aluminum zinc oxide (AZO). Single-crystal InGaZnO<sub>4</sub> TFT with the field-effect mobility of 80 cm<sup>2</sup>/Vs and amorphous InGaZnO<sub>4</sub> TFT with the field-effect mobility of 20 cm<sup>2</sup>/Vs have been reported. The advantages of ZnO based TFTs are higher mobility than a-Si and better uniformity than poly-Si. However, the lower mobility of ZnO TFTs than poly-Si limits its further application for high performance integrated circuits (ICs), such as radio frequency (RF) circuits, logic circuits, analog amplifies, and AMOLED. Particularly, The low field-effect mobility cause result of low definition of panel. Therefore, the oxide type semiconductor for AMOLED actually give up in industry.

### 1.2.3 Low Temperature Polycrystalline Silicon

The motivation of using poly-Si as channel material for TFTs is the higher fieldeffect mobility (50~300 cm<sup>2</sup>/Vs) than that of a-Si or oxide type semiconductors, which means that for the same on-current, the size of the poly-Si TFT is much smaller than that of a-Si. This results in higher aperture ratio and higher resolution for displays. Also the driver circuits can be integrated peripherally on displays due to the increased mobility of poly-Si TFTs. Poly-Si TFTs also show better stability than that of a-Si TFTs and they have no threshold voltage shift under electrical stress. The high mobility and high electrical stability of poly-Si TFTs are very suitable for AMOLED switches which require TFTs with high drive current and good electrical reliability. However, for small grain (<1μm) poly-Si TFT, the disadvantage is the low mobility (<100 cm<sup>2</sup>/Vs) due to dense grain boundaries inside and between grains in the channel region. The grain boundaries act as trap states which decrease the field effect mobility of electrons and holes. For large grain (>1 µm) poly-Si TFT, the disadvantage is the poor uniformity of the motilities due to the fact that location of the large grain size is random. Although there are several technologies to control the location of the large grains, the orientations of the large grains are still random. In order to deposit high quality poly-Si, several technologies are proposed: direct deposition by chemical vapor deposition (CVD); solid phase crystallization (SPC) of a-Si by high temperature thermal annealing (>600 °C) or metal induced lateral crystallization (MILC); liquid phase crystallization by laser crystallization such as zone melting regrowth (ZMR), and excimer laser annealing (ELA). Laser crystallization of a-Si film can produce high performance poly-Si. However, if the laser energy is below complete melt of the a-Si film, the grains are small ( $<1 \mu m$ ) and the mobility is low ( $<100 \text{ cm}^2/\text{Vs}$ ). If the laser

energy is above CM, large grains (>1  $\mu$ m) are formed and the mobility can up to 300 cm<sup>2</sup>/Vs. However, the large grains are randomly located and the orientations of the grains are random which result in a high variation of the field effect mobilities. The crystallization methods are summarized in Table 1.2.

Excimer Laser Metal Induced Lateral Super Grained Silicon Method Crystallization (SPC) Crystallization (MIC) Annealing (ELA) Crystallization (MILC) (SGS) n metal elements , Pd, W, etc.) Cap layer (SiNx, SiO<sub>2</sub>) Thin metal layer (Ni, Pd, 등) Glass Process 수직&수평 성장 0000000000 Micro-Structure -Ni Silicide Catalyst -Good Crystallinity -Simple Process -Low Temperature -Good Crystallinity -Good Crystallinity -Low Contamination -High Temperature (<550°C) -Surface Roughness -Large Grain -Low Contamination Remarks (600°C~750°C) Small Grain -Direction Dependence -Complex Process -Add Mask -Substrate -Metal Contamination Expensive Process (Dep.-Etch-Dep.) -Leakage Current Shrinkage (Leakage current -Large Area Limit -Leakage Current Low Mobility)

**Table 1.2** The major crystallization methods.

## 1.3 Objective of the Dissertation

A LTPS TFT fabrication process is necessary for the realization of display panels in cheap display-grade glass substrates to avoid glass shrinkage and pattern distortion. The maximum fabrication temperature is commonly constrained to less than 600-650  $^{\circ}$ C.

a-Si:H TFT is widely used in AMLCDs because of the simple and low temperature TFT fabrication process, capability of large-area and uniform a-Si film preparation. But there are a large number of localized band sate distributing throughout the bandgap of a-Si:H even with the passivation of most of the dangling bonds with hydrogen atoms. In a-Si:H TFTs, carriers have to fill up the localized states and Fermi level has to move through energy levels of deep and shallow trap states before conduction begins. This increases the threshold voltage and reduces the field-effect mobility. Field-effect mobility of  $0.4 \sim 1.5 \text{ cm}^2/\text{Vs}$  for electrons and much lower field-effect mobility of  $2 \times 10^4 \sim 7 \times 10^4 \text{ cm}^2/\text{Vs}$  for holes [1.18-1.23] limit the application of a-Si:H TFTs to pixel switches. In addition, because of the low field-effect mobility, large channel width, usually in the order of 100  $\mu$ m, with a channel length of 8-10  $\mu$ m is required to provide an adequate drive current. The large device size reduces the aperture ratio, resolution and brightness of the display. a-Si:H TFT also suffers from long time performance degradation.

Poly-Si TFTs have many advantages over a-Si:H TFTs as pixel active elements. Poly-Si consists of locally ordered grains with grain boundaries in between, so the field-effect mobility of poly-Si TFTs is usually much higher than that of a-Si TFTs. As to the higher field-effect mobility, the size of the poly-Si TFT can be reduced which will increase the aperture ratio, brightness and consequently reduce the power consumption of the display. Low-temperature poly-Si could be obtained using a variety of techniques, such as SPC, ELA and MILC.

Usually, as-deposited poly-Si film consists of grains in the order of hundreds of nanometer, SPC poly-Si with larger grains could be achieved by recrystallization of a-Si with Si implantation [1.24] or crystallization of precursor a-Si at a temperature around 600°C for a long time of tens of hours [1.25]. The crystallized grain grows

from spontaneous nucleation, so both the orientations of crystallized grains and the grain boundaries are random. The grain size of the poly-Si is affected by the microstructure of the precursor a-Si, grain size up to 2~5 µm has been reported [1.24, 1.25]. The SPC process is simple while it requires relatively high process temperature and long crystallization time which are big problems for commonly used glass substrates.

Laser crystallization has been widely used as a low-temperature technology to prepare high quality poly-Si films with few defects. The a-Si film is heated to melt with laser irradiation in a short time and cools down after the irradiation, through which the molten a-Si solidifies and transforms into poly-Si. The damage to the commonly used glass substrate can be minimized by choosing a short-wavelength and short-pulse laser. Both excimer laser [1.26] and continuous-wave laser [1.27] have been reported to be used to fabricate high quality poly-Si and high performance poly-Si TFTs. The drawbacks of this technique are the high equipment cost, complex processing, inherent energy variant, and sensitivity of poly-Si quality to the laser energy density.

Low-temperature crystallization of a-Si is also possible by using some metals as crystallization catalyst to reduce the phase-change energy from a-Si to poly-Si. The metals can be classified into two groups, one includes eutectic-forming metals such as Ag, Au, Al, Sb, and In, and the other includes silicide-forming metals such as Pd, Ti, Ni, and Cu. Atoms of the former kind of metals dissolved in a-Si films may weaken Si bonds and enhance nucleation of crystalline Si [1.28]. Among the latter kind of metals, Ni is the mostly used crystallization catalyst as Ni silicide has the same crystalline structure as Si with only 0.4% lattice constant difference [1.29]. During the

crystallization process, a-Si is continuously transformed to poly-Si such that the poly-Si film consists of longitudinal grains and continuous grain boundaries [1.30].

Initially, TFTs with bilaterally crystallized poly-Si channel and self-aligned metal induced crystallized (MIC) poly-Si source/drain were proposed [1.31], but the highly defective MIC region at the drain junction leads to early drain breakdown and high leakage current [1.32]. New methods of introducing Ni to crystallize a-Si have been reported to either simplify the crystallization process [1.34] or fabricate high quality poly-Si [1.35]. Further improvement of the MILC poly-Si quality by a combination of MILC and post-crystallization, such as high temperature annealing [1.36] and laser annealing [1.37], has also been reported.

# 1.4 Organization of the Dissertation

New technologies, aiming at fabricating low temperature poly-Si TFTs having low leakage current and excellent driving characteristics, were proposed and successfully demonstrated in this research. This dissertation is consist of six chapters and organized as follows:

Chapter 2 Background and Previous Works. In order to understand this dissertation, basic theories and physical models are needed. Therefore this chapter gives an overview of the crystallization method of :SPC, ELA, and MILC etc. and simple physical models using mathematical formulations of TFT driving. Moreover, the determinations of device key parameters used in this dissertation are presented.

Chapter 3 Experimental Procedures describes the experimental procedures, including the preparation of samples and the development of fabrication processes to

make high performance MILC poly-Si TFTs having low leakage current. First, the conventional fabrication process of MILC poly-Si TFTs is introduced. Next, the direction of experimental is categorized according to 1) crystallization using minimum Ni catalyst, 2) removal of trapped Ni silicide residues using gettering and asymmetrically deposited Ni on the source and drain, and 3) lightly doped drain structure for suppression leakage current at high reverse gate bias region.

Chapter 4 Reduction of the Leakage Current will describes the leakage current mechanism in poly-Si TFTs and to achieve the low leakage current poly-Si TFTs, three kinds of fabrication method was developed. First *silicide induced crystallization* (SIC) using minimum Ni catalyst to decrease minimum leakage current at low reverse gate bias. Second is a novel process named "thin film gettering" to remove Ni silicide residues on the surface of active layer. The last is *lightly doped drain* (LDD) structure for suppression leakage current at high reverse gate bias region.

Chapter 5 Enhancement of Driving Characteristics will introduce three kinds of process development for high performance poly-Si TFTs. First is "split channel structure" to improve driving characteristics, subthreshold slope, on-state current, and field-effect mobility, of poly-Si TFTs. The second is "electrical stress". In order to investigate device stability, electrical stress was frequently used by many researchers. But in this study, the electrical stress was used the method for electrical performance improvement.

**Chapter 6 Conclusion and Future Work** will concludes the dissertation with a summary and suggestions for future research.

# **CHAPTER 2**

# **Background and Previous Works**

## 2.1 Low Temperature Polycrystalline Silicon (LTPS)

P OLY-SI exhibits advantages over a-Si technology on the achievable size vs. resolution limits for the display, as well as the opportunity to monolithically integrate additional functionality on the panel. The advantages of poly-Si are the significant performance gains of poly-Si TFTs over a-Si TFTs and its compatibility with complementary metal-oxide semiconductor (CMOS) fabrication. CMOS technology enables monolithic integration of peripheral drivers on panel, as well as opportunities for the addition of other value-added components on the display [2.1, 2.2].

In addition, many researches are concentrated on the AMOLED [2.3, 2.4] because of its low cost, low power consumption, wide viewing angle, and the possibility to be made on flexible substrates. For the pixel element of OLED, poly-Si TFTs are better than a-Si:H TFTs, because OLED is current-driving type and needs more current, while LCD is voltage-driving type.

Unlike MOSFET devices, the TFT active layer needs to be formed on such amorphous host material and that the temperature of all associated processing has to be constrained within the allowable rage prescribed by the materials characteristics of the substrate. For current display-glass substrates, the maximum processing temperature needs to be kept below ~650 °C. To form poly-Si TFTs on the commercial glass substrates, a number of researches have been carried on some methods.

Poly-Si thin films can directly be deposited on glass over 600 °C by PECVD but their electrical properties are inadequate for TFTs [2.5]. Therefore most of research groups have focused on the methods to crystallized a-Si thin films below 650 °C. The most direct method of obtaining poly-Si films from a-Si films is via SPC. However, it needs long time annealing during over 20 h at 600 °C and quality of poly-Si is not enough to make high performance poly-Si TFTs [2.6].

ELA uses excimer laser as a type of gas laser from an inert atom and halide atom. a-Si films are melted by laser irradiation during very short period, ~220 ns, and they are crystallized simultaneously with the solidification [2.7]. This method is also allowable to flexible substrate and can make high mobility poly-Si TFTs, but there are some problems on the productivity, surface roughness, non-uniformity of poly-Si.

Recently, many researches are concentrated on the MILC and MIC. They will be commented at following chapter.

## 2.2 Metal-Induced Lateral Crystallization (MILC)

The crystallization temperature of a-Si can be lowered by the addition of some metals into a-Si and it is called as MIC. The MIC is induced by some metals such as Au [2.8], Al [2.9], Sb [2.10], and In [2.11], which form eutectics with Si, or metals such as Pd, Ti, and Ni [2.12, 2.13], which form silicides with Si. These metals have been added to a-Si to enhance the nucleation rate. Some of these cases were reported to be successful in lowering the crystallization temperature down to 500 °C. The MIC process, however, has a serious drawback of undesirable incorporation of metal impurities into Si, so that it has not been applicable to the fabrication of TFTs. For example, the crystallization temperature of Al-Si is reported to be as low as 170 °C, but Al is an acceptor-type dopant within Si [2.14].

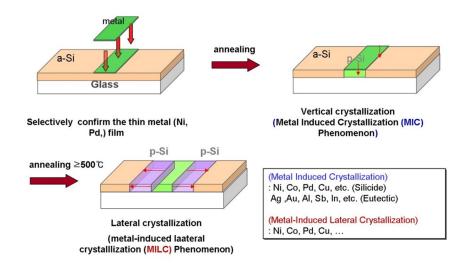

Figure 2.1 The metal-induced lateral crystallization (MILC) process flows.

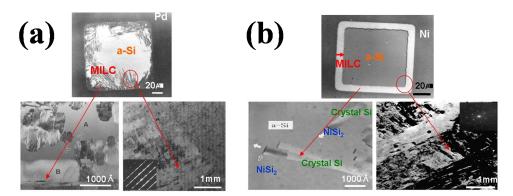

**Figure 2.2** The microstructure of (a) Pd-induced lateral crystallization (b) Ni-induced lateral crystallization.

Hence, it is of great significance to minimize the amount of metal incorporation into Si while a lower crystallization temperature is preferable. Liu and Fonash firstly showed that MIC can be applied to the fabrication of poly-Si TFTs, where they tried to minimize the metal contamination by depositing an ultra-thin Pd layer under a-Si films. Though they were able to reduce the crystallization annealing time, the crystallization temperature was still kept at 600 °C.

More recently, a different crystallization phenomenon has been reported, where MIC could be extended laterally into the metal-free areas over  $100~\mu m$  and this MILC has been known to take place for Pd, Ni, at temperatures lower than  $500~^{\circ}C$  [2.15, 2.16]. The MILC can provide large grained poly-Si films as well as low temperature crystallization. Figure 2.1 briefly shows the MILC process. Also Figure 2.2 indicates the microstructures of Pd-induced lateral crystallization and Ni-induced lateral crystallization respectively. The a-Si region contact with metal layer is crystallized by MIC and poly-Si grains laterally grow toward a-Si region where does not contact with

metal layer. Thus MILC poly-Si region has lower metal contamination than MIC region [2.17~2.19].

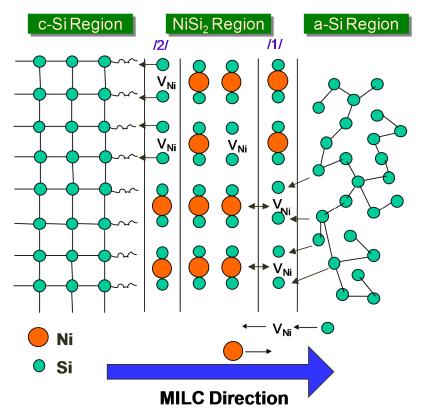

According to MILC reaction model [2.20], MILC phenomenon is caused by strain-stress among a-Si, metal silicide, and c-Si layers. At the tip of the lateral crystallization, there is a silicide of less than 50 Å in thickness, which moves into the a-Si leaving the poly-Si behind, as shown in Figure 2.2. The schematic drawing for this reaction is illustrated in Figure 2.3. For the catalytic phase transformation to occur, three different atomic fluxes are required in the system. Firstly, the bond breaking of a-Si atoms and migration of each atom towards the interface between a-Si and the silicide designated as /1/ in Figure 2.3 (F1). Migrated Si atoms are to be adsorbed at the silicide surface to create the metal vacancies. Secondly, the hopping of the abovementioned created metal vacancies inside the silicide to reach the interface between the silicide and poly-Si designated as /2/ (F2). Hopping of the metal vacancies should be coupled with the metal ions in the silicide. Finally, the rearrangement of the dissociated Si atoms at /2/ to be attached to the dangling bonds of the poly crystal (F3). Phase transformation of one atomic layer can be completed by the rearrangement of dissociated Si atoms at /2/. In a steady state, F1 should be equal to F2 and F3.

Since there is a volume expansion at /1/ and shrinkage at /2/, corresponding tensile and compressive stresses would be created. For Pd-MILC the volume is calculated to expand by two times at /2/ and to contract in half at /1/. Therefore the tensile stress drives the bond breaking of a-Si and the migration of Si atoms for adsorption at the silicide surface of /1/, while compressive stress built at /2/ would facilitate the atomic rearrangement. For Ni-MILC, the respective volumes occupied by one Si atom in crystalline, Ni silicide and a-Si are calculated to be 20.0, 19.9, and 20.3%. This

**Figure 2.3** Schematic illustrations of the MILC reaction model. 1st step: Si bond breaking and coherent adsorption to the interface /1/ (Ni vacancy formation), 2nd step: Ni ion and Ni vacancy hopping, and 3rd step: Si atom coherent rearrangement.

means that almost no volume change occurs at either interface /1/ of /2/ for Ni-MILC. This fact is related to the MILC growth rate and the adjacent metal effect.

Vacancy motion inside the silicide, which has to be coupled with the metal ions in the reverse direction, can be driven by the thermodynamic equilibrium potential difference between /1/ and /2/. It is known that a-Si can accommodate more metal elements than poly-Si, thermodynamically, so that the charged metal ions have to move toward /1/[2.16]. Also, MILC reaction model will be analyzed in detail.

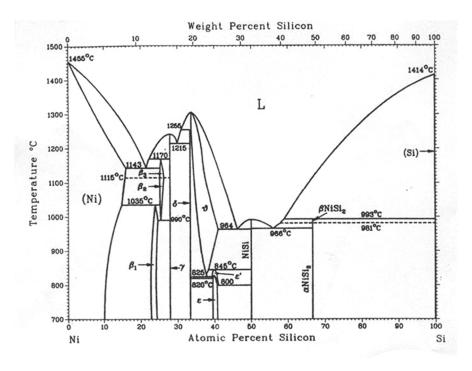

**Figure 2.4** Ni-Si phase diagram.  $\beta 1: Ni_4Si,\ \beta_2\ \&\ \beta_3: Ni_3Si,\ \Gamma: Ni_{31}Si_{12},\ \theta\ \&\ \delta: Ni_2Si,\ \epsilon: Ni_3Si_2$ .

#### A. Silicide formation

When a thick Ni film (> 100 Å) is deposited on a c-Si substrate and annealed, Ni rich phase of orthorhombic Ni<sub>2</sub>Si with the PbCl<sub>2</sub> structure is formed by a diffusion controlled process at temperatures as low as  $\sim 200$  °C. Annealing at temperatures in the range 350  $\sim 750$  °C leads to a diffusion-controlled transformation of Ni<sub>2</sub>Si into the monosilicide of NiSi, which is also orthorhombic with the MnP structure [2.21]. Ni has been found to be the dominant diffusing species in the formation of Ni<sub>2</sub>Si [2.22, 2.23] and NiSi [2.24, 2.25]. The transport of Si through NiSi has also been studied, although rather poor epitaxial layers of c-Si were observed [2.26]. At temperatures in the range 450  $\sim 750$  °C, the NiSi transforms into the thermodynamically favored end

phase, NiSi<sub>2</sub> [2.27, 2.28]. The high transformation temperature has been attributed to nucleation-controlled kinetics, and Ni has again been observed to be the fast diffusing species [2.29]. The disilicide NiSi<sub>2</sub> is cubic with the CaF structure and has a very close lattice parameter match to c-Si (~0.4%). Therefore, NiSi<sub>2</sub> coherently confirmed on the c-Si layer.

#### B. Nucleation of c-Si

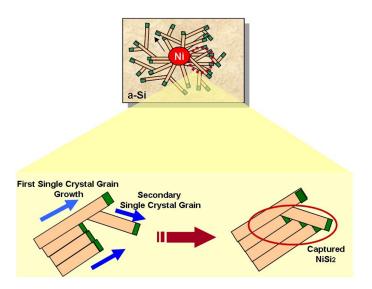

The phase transformation of a-Si to c-Si is mediated by NiSi<sub>2</sub> precipitates. Crystalline Si nucleates on one or more of the eight  $\{111\}$  faces of the octahedral NiSi<sub>2</sub>. The NiSi<sub>2</sub> is metallic with a very low resistivity of 35  $\mu\Omega$ cm and an extremely good lattice match with c-Si. The phenomenon of metal-induced crystallization is thought to be due to an interaction of the free electrons of the metal with the covalent Si bonds at a growing interface [2.30]. The small misfit (0.4%) between NiSi<sub>2</sub> and Si facilitates the formation of epitaxial c-Si on the  $\{111\}$  faces of the NiSi<sub>2</sub> precipitates. Localized networks of c-Si trails were often single crystal, despite the observation of NiSi<sub>2</sub> precipitates at the leading edge of each trail. Migration of NiSi<sub>2</sub> led to epitaxial growth of Si constrained to  $\{111\}$  directions. Impingement of migrating silicide precipitates with stationary precipitates promoted further epitaxial growth on variants of the (111) face.

#### C. Growth of MILC epitaxial c-Si

Following nucleation of c-Si on the NiSi<sub>2</sub> precipitates, growth always proceeded with a NiSi<sub>2</sub> precipitate at the planar advancing growth front. Many reports confirmed that the growth rate for each individual needle was dependent upon the NiSi<sub>2</sub> thickness in the growth direction. Many NiSi<sub>2</sub> fanned out, decreased in thickness, and

**Figure 2.5** Schematic equilibrium molar free-energy diagram for NiSi2 in contact with a-Si and c-Si.

were observed to migrate more rapidly. In general, the trails of c-Si developed a needlelike morphology because lateral growth of the a-Si/c-Si interface via conventional solid phase epitaxial growth occurred much more slowly. The c-Si needles were frequently seen to fan out, with a consequent reduction in the NiSi<sub>2</sub> thickness. At the same time, the growth velocity increased with decreasing NiSi<sub>2</sub> thickness.

The driving force for the phase transformation is the reduction in free energy associated with the transformation of meta-stable a-Si to stable c-Si [2.31]. Figure 2.5 shows the schematic equilibrium molar free-energy diagram for NiSi<sub>2</sub> in contact with a-Si and c-Si. The chemical potential of the Ni atoms is lower at the NiSi/a-Si interface, whereas the chemical potential of the Si atoms is lower at the NiSi<sub>2</sub>/c-Si interface. For a migrating NiSi<sub>2</sub> precipitate consuming a-Si at the leading interface and

Figure 2.6 The phenomenon of caused grain-boundary defects during MILC process.

forming a trail of epitaxial c-Si, there is a driving force for the forward diffusion of Ni atoms through the  $NiSi_2$  and a driving force for the diffusion of Si atoms in the reverse direction through the  $NiSi_2$ .

The MILC has many advantages such as large grains without defects [2.32], low temperature processes, smooth surface, high crystalline uniformity and low process cost, etc. Thus, MILC poly-Si TFTs were fabricated by some groups and they showed excellent properties [2.16, 2.19, 2.32, 2.33]. Their performance is better than that by SPC [2.16].

However, it has been reported that the leakage current of poly-Si TFTs using MILC is higher than those of poly-Si TFTs prepared by laser annealing process [2.34]. The MILC method uses metals, such as Ni and Pd [2.35, 2.36]. The crystallization occurs through lateral phase transformation from the MIC region and this lateral crystallization is mediated by silicides which are formed in the MIC regions. In

**Figure 2.7** Distribution of Ni across the MIC, the MILC, and the a-Si regions obtained by secondary ion mass spectroscopy (SIMS).

general, needle-shaped crystal Si grains grow toward the a-Si region with the migration of the silicide [2.37] and the individual crystallites form crystallized networks during the MILC process. If the silicide layer at the front of crystal Si grain meets other crystal grains which have already been crystallized by the MILC process, the silicide layer cannot migrate through the crystal Si grains anymore because there is no difference in chemical potential-driving force for the phase transformation between the facing the two crystal Si grains [2.31]. Therefore, the captured silicides can increase the silicide contamination in the MILC region. Figure 2.6 and 2.7 show these phenomenons. The presence of the captured silicides and/or poly-Si grain boundary defects in the channel region of TFTs degrades the electrical performance, resulting to the high leakage current of MILC poly-Si TFTs.

# 2.3 Poly-Si TFT Device Theories

#### 2.3.1 Seto's Model

Seto's paper concerning the electrical behavior of polycrystalline is a very important work in the field. [2.38] On the basis of initial experimental results reported by T. I. Kamins [2.39] and by M. E. Cowher & T. O. Sedgwick [2.40], J. Y. Seto was the first to give an original and credible interpretation of the specific conduction in polycrystalline materials. The main result concerned a high temperature process on boron doped poly-Si films and were well described in his paper.

The Seto's model is based on the following assumptions:

- a. Poly-Si film has small grain size,

- b. The single crystalline Si energy band structure is assumed to be applicable inside the crystallites,

- c. Doping concentration in poly-Si is uniform,

- d. All the doping atoms are ionized,

- e. All the grains have the same size,

- f. The representation is mono-dimensional,

- g. The grain boundaries have no thickness

- h. The defects are carrier traps that are located in grain boundaries. The trap concentration is defined per surface unit.

- i. The traps are acceptors in the n-type and donors in the p-type semiconductor.

- The trap energy level is unique and located more or less in the middle of the forbidden band.

The device characteristics of poly-Si TFTs are strongly influenced by the grain structure in poly-Si film. Even though the inversion channel region is also induced by the gate voltages as in MOSFETs, the existence of grain structure in channel layer bring huge differences in carrier transport phenomenon. Many researchers studying the electrical properties and the carrier transport in poly-Si TFTs have been reported. A simple grain boundary trapping model has been described by many authors in detail [2.41-2.49]. In this model, it is assumed that the poly-Si material is composed of a linear chain of identical crystallite having a grain size  $L_g$  and the grain boundary trap density  $N_t$ . The charge trapped at grain boundaries is compensated by opposite charged depletion regions surrounding the grain boundaries. From Poisson's equation, the charge in the depletion regions causes curvature in the energy bands, leading to potential barriers that impede the movement of any remaining free carriers from one grain to another. When the dopants/carrier density n is small, the poly-Si grains will be fully depleted. The width of the grain boundary depletion region  $x_d$  extends to be  $L_g/2$  on each side of the boundary, and the barrier height  $V_B$  can be expressed as

$$V_B = \frac{qn}{2\varepsilon_s} x_d^2 = \frac{qnL_g^2}{8\varepsilon_s}$$

(2-1)

As the dopant/carrier concentration is increased, more carriers are trapped at the grain boundary. The curvature of the energy band and the height of potential barrier increase, which making carrier transport from one grain to another more difficult. When the dopant/carrier density increases to exceed a critical value  $N^* = N_t / L_g$ , the poly-Si grains turn to be partially depleted and excess free carriers start to spear inside the grain region. The depletion width and the barrier height can be expressed as

$$x_d = \frac{N_t}{2n} \tag{2-2}$$

$$V_B = \frac{qn}{2\varepsilon_S} \left(\frac{N_t}{2n}\right)^2 = \frac{qN_t^2}{8\varepsilon_S n}$$

(2-3)

The depletion width and the barrier height turn to decrease with increasing dopant/carrier density, leading to improved conductivity in carrier transport. The carrier transport in partially-depleted poly-Si film can be described by the thermion emission over the barrier. Its current density can be written as [2.50]

$$J = qnv_c \exp\left[-\frac{q}{\kappa T}(V_B - V)\right]$$

(2.4)

Where n is the free-carrier density,  $v_c$  is the collection velocity ( $v_c = \sqrt{KT/2\pi n^*}$ ),  $V_B$  is the barrier height without applied bias, and  $V_G$  is the applied bias across the grain boundary region. For small applied biases, the applied voltage divided approximately uniformly between the two sides of a grain boundary. Therefore, the barrier in the forward-bias direction decrease by an amount of  $V_G/2$ . In the reverse-bias direction, the barrier increases by the same amount. The current density in these two directions then can be expressed as

$$J = qnv_c \exp\left[-\frac{q}{KT}\left(V_B - \frac{1}{2}V_G\right)\right]$$

(2-5)

$$J = qnv_c \exp\left[-\frac{q}{KT}\left(V_B + \frac{1}{2}V_G\right)\right]$$

(2-6)

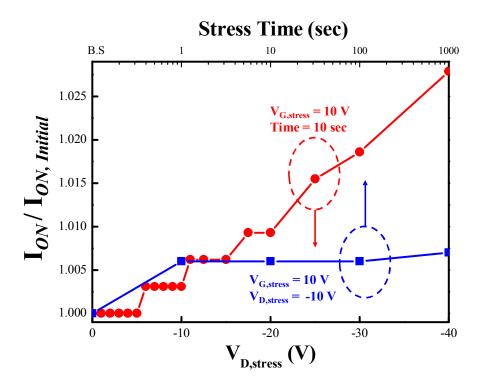

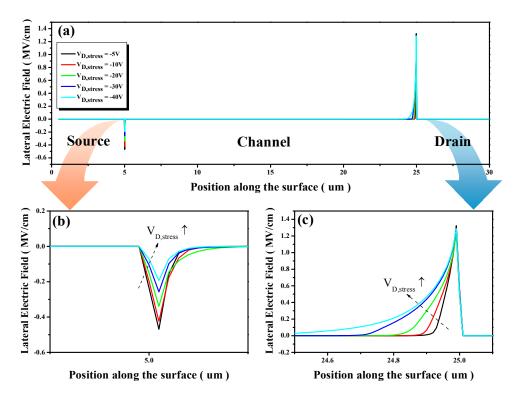

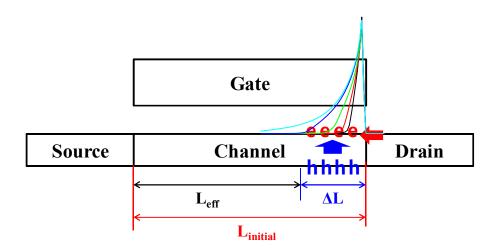

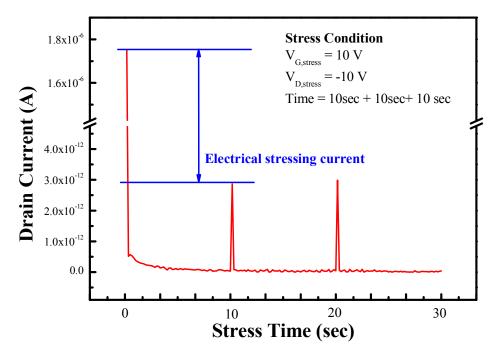

the net current density is then given by