#### 저작자표시-비영리-변경금지 2.0 대한민국

#### 이용자는 아래의 조건을 따르는 경우에 한하여 자유롭게

• 이 저작물을 복제, 배포, 전송, 전시, 공연 및 방송할 수 있습니다.

#### 다음과 같은 조건을 따라야 합니다:

저작자표시. 귀하는 원저작자를 표시하여야 합니다.

비영리. 귀하는 이 저작물을 영리 목적으로 이용할 수 없습니다.

변경금지. 귀하는 이 저작물을 개작, 변형 또는 가공할 수 없습니다.

- 귀하는, 이 저작물의 재이용이나 배포의 경우, 이 저작물에 적용된 이용허락조건 을 명확하게 나타내어야 합니다.

- 저작권자로부터 별도의 허가를 받으면 이러한 조건들은 적용되지 않습니다.

저작권법에 따른 이용자의 권리는 위의 내용에 의하여 영향을 받지 않습니다.

이것은 이용허락규약(Legal Code)을 이해하기 쉽게 요약한 것입니다.

#### 공학박사학위논문

Deep Neural Network Based Multi-Objective Dispatcher for Re-Entrant Manufacturing Lines

재유입 제조라인을 위한 심층신경망 기반 다중 목적 함수 디스패처

2019 년 2월

서울대학교 대학원 산업공학과

허재석

# Deep Neural Network Based Multi-Objective Dispatcher for Re-Entrant Manufacturing Lines

재유입 제조라인을 위한 심층신경망 기반 다중 목적 함수 디스패처

지도교수 박종헌

이 논문을 공학박사 학위논문으로 제출함 2018 년 12 월

> 서울대학교 대학원 산업공학과 허 재 석

허재석의 공학박사 학위논문을 인준함 2018 년 12 월

| 위 원 장 | 조성준   | _ (인) |

|-------|-------|-------|

| 부위원장  | 박종 헌  | _ (인) |

| 위 원   | 문 일 경 | _ (인) |

| 위 원   | 정 재 윤 | _ (인) |

| 위 원   | 김 관 호 | (인)   |

#### Abstract

## Deep Neural Network Based Multi-Objective Dispatcher for Re-Entrant Manufacturing Lines

Jaeseok Huh

Department of Industrial Engineering

The Graduate School

Seoul National University

A re-entrant manufacturing line (RML) is a manufacturing line in which parts make several visits to the same stage before exiting the line. RMLs have intrigued interest in both academia and industry with the recent emergence of semiconductor manufacturing and thin film transistor-liquid crystal display (LCD) manufacturing lines. As small devices embedded with flash memory and LCD have grown in demand, relevant research effort has been motivated to date.

This thesis aims to propose real-time dispatchers (RTD) based on deep neural networks (DNN) that decrease flow time without deteriorating resource utilization at the bottleneck stage for real-world RMLs. Frequent re-entrant parts between multiple stages in RMLs make it challenging to achieve the dual goals of reducing flow time and improving resource utilization. To be more specific, the level of resource utilization can be kept high by simply providing a sufficiently large amount of work-in-process (WIP) to maximize throughput. On the contrary, an excessive amount of

WIP leads to a longer waiting time for parts in the next operations, thus increasing flow time for the parts.

This thesis suggests new methods as follows. First, a discrete event based simulator (DEBS) and monitoring tool are implemented to generate training data and evaluate the performance of dispatching decisions. DEBS plays a role in imitating real-world RMLs and generating training data used for DNNs. The monitoring tool is in charge of presenting the state of an RML at the time of each dispatching decision being made. Furthermore, it also provides the ability to observe changes in various performance indicators over time.

Second, two deep neural network based RTDs with different decision-making processes are presented by the thesis. In the training phase, the proposed RTDs learn the preferences of each alternative when dispatching decisions are required according to RML data generated by the application of the developed DEBS. Then, in the real-time dispatching phase, RTDs perform dispatching decisions by considering intentional delays. A preferred alternative records a higher value as the dispatching decision is likely to reduce the part's waiting time and decrease the idle time of the resources in the bottleneck stage.

The thesis makes contributions and holds utilitarian significance in three ways. First, it developed a monitoring tool that allows users to investigate each dispatching decision. Second, the proposed approach is capable of generating training data used for DNNs by merely performing a simulation while using the developed DEBS that imitates real-world RMLs. Finally, the proposed RTDs are successful in decreasing flow time while increasing resource utilization at the bottleneck stage by factoring in intentional delays in RMLs.

Keywords: Re-entrant manufacturing lines, Real-time dispatcher, Intentional de-

lay, Deep neural network, Flow time, Utilization, Discrete event based simulator,

Monitoring tool

Student Number: 2013-23211

iii

### Contents

| Abstra  | act                                                      | i    |

|---------|----------------------------------------------------------|------|

| Conte   | nts                                                      | vi   |

| List of | Tables                                                   | vii  |

| List of | Figures                                                  | xiii |

| Chapt   | er 1 Introduction                                        | 1    |

| 1.1     | Background and motivation                                | 1    |

| 1.2     | Objectives                                               | 6    |

| 1.3     | Thesis outline                                           | 8    |

| Chapte  | er 2 Literature Review                                   | 9    |

| 2.1     | Dispatching decisions in RMLs                            | 9    |

| 2.2     | Neural network-based approaches to dispatching decisions | 13   |

| Chapte  | er 3 Problem Definition                                  | 17   |

| 3.1     | Multiple-chip product (MCP) assembly lines               | 17   |

| 3.2     | Lot dispatching process in MCP assembly lines            | 21   |

| Chapt | er 4 H | Frameworks for Data Generation and Performance Eval- |    |

|-------|--------|------------------------------------------------------|----|

|       | ι      | nation                                               | 24 |

| 4.1   | Discre | ete event-based simulator                            | 24 |

|       | 4.1.1  | Purpose of implementation                            | 24 |

|       | 4.1.2  | Details of the structure                             | 25 |

| 4.2   | Monit  | oring tool                                           | 30 |

|       | 4.2.1  | Purpose of implementation                            | 30 |

|       | 4.2.2  | Details of functions                                 | 32 |

| Chapt | er 5 I | Deep Neural Network Based Dispatcher                 | 43 |

| 5.1   | Real-t | sime rule selection dispatcher                       | 46 |

|       | 5.1.1  | Dispatcher structure                                 | 46 |

|       | 5.1.2  | Training phase                                       | 49 |

|       | 5.1.3  | Real-time dispatching phase                          | 52 |

| 5.2   | Real-t | ime lot selection dispatcher                         | 53 |

|       | 5.2.1  | Dispatcher structure                                 | 53 |

|       | 5.2.2  | Training phase                                       | 57 |

|       | 5.2.3  | Real-time dispatching phase                          | 58 |

| Chapt | er 6 I | $\mathbf{E}_{\mathbf{x}}$ periments                  | 60 |

| 6.1   | Datas  | ets                                                  | 60 |

| 6.2   | Exper  | iment settings                                       | 61 |

| 6.3   | Exper  | iment results                                        | 67 |

|       | 6.3.1  | Performance comparison                               | 67 |

|       | 6.3.2  | Performance differences according to weights         | 79 |

| 6.3.3 Robustness test                                             | 87                    |

|-------------------------------------------------------------------|-----------------------|

| Chapter 7 Conclusions                                             | 92                    |

| 7.1 Summary and contributions                                     | 92                    |

| 7.2 Limitations and future research                               | 94                    |

| Appendices                                                        | 96                    |

| Chapter A Performance comparison results                          | 97                    |

| Chapter B Performance contour of RTRD with respect to $\lambda_w$ | and $\lambda_l 104$   |

| Chapter C Performance contour of RTLD with respect to $\lambda_i$ | $_{w},\;\lambda_{l},$ |

| $\text{ and } \lambda_d$                                          | 117                   |

| Bibliography                                                      | 130                   |

| 국문초록                                                              | 146                   |

## List of Tables

| Table 2.1 | Overview of previous research on dispatching decisions of RMLs.           | 11 |

|-----------|---------------------------------------------------------------------------|----|

| Table 2.2 | Overview of previous research on dispatching decisions using              |    |

|           | neural networks                                                           | 14 |

| Table 4.1 | Descriptions on the event types for the event loop                        | 28 |

| Table 5.1 | Components of the state vector for $R_{q,s}$ of RTRD                      | 48 |

| Table 5.2 | Dispatching rules used to generate the action vector for $R_{q,s}$        |    |

|           | of RTRD                                                                   | 50 |

| Table 5.3 | Components of the lot-DA assignment vector, for $L_{i,k}$ and $R_{q,s}$ . | 55 |

| Table 6.1 | Descriptions on the datasets used for the experiments                     | 62 |

| Table 6.2 | Problem description for experiments                                       | 63 |

| Table 6.3 | Training results of the proposed dispatchers                              | 66 |

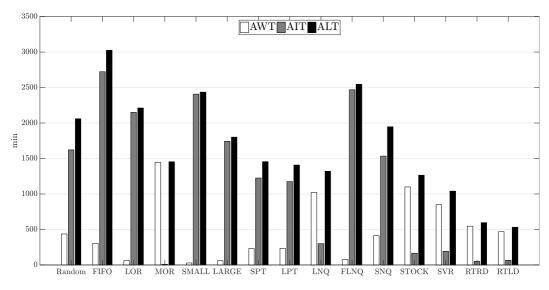

| Table 6.4 | ALT improvement rates of RTLD compared to the existing                    |    |

|           | methods and RTRD                                                          | 72 |

| Table 6.5 | Statistically significant differences in $ALT$ between RTRDs              |    |

|           | trained in different datasets                                             | 89 |

| Table 6.6 | Statistically significant differences in $ALT$ between RTLDs              |    |

|           | trained in different datasets                                             | 91 |

## List of Figures

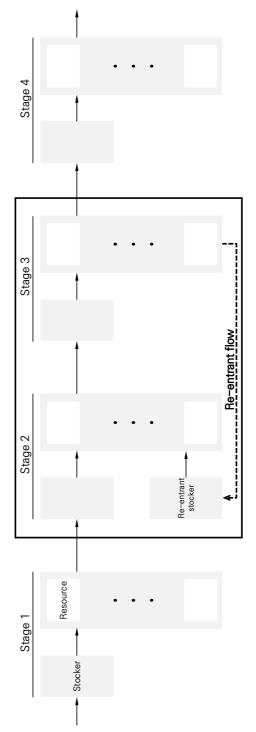

| Figure 1.1 | Concept of re-entrant manufacturing line                           | 2  |

|------------|--------------------------------------------------------------------|----|

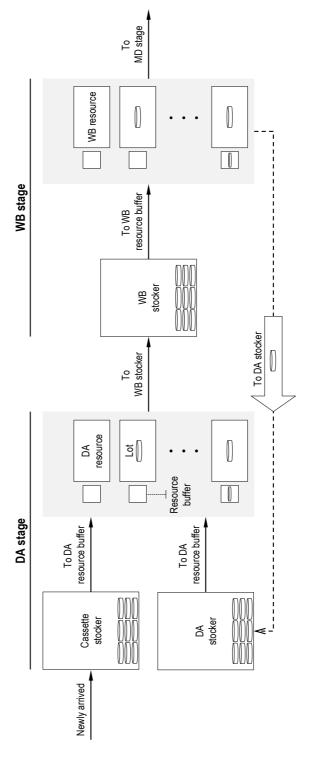

| Figure 3.1 | Lot flow of DA and WB stages in MCP production                     | 19 |

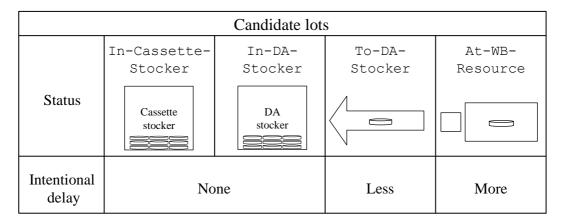

| Figure 3.2 | Candidate lots according to status and intentional delay           | 21 |

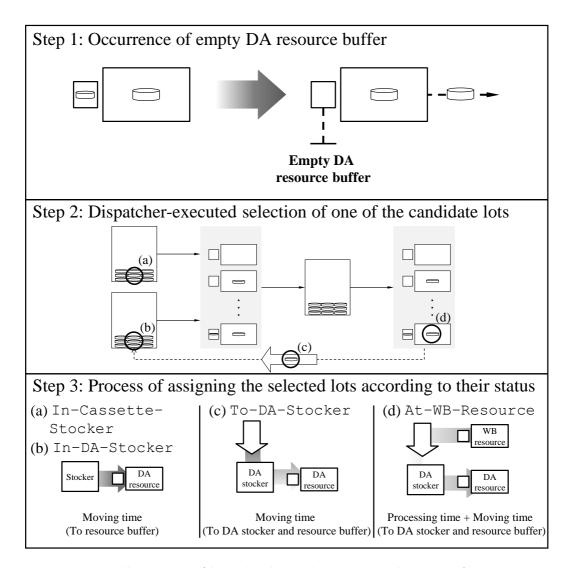

| Figure 3.3 | Illustration of how the dispatcher assigns a lot to a DA resource. | 23 |

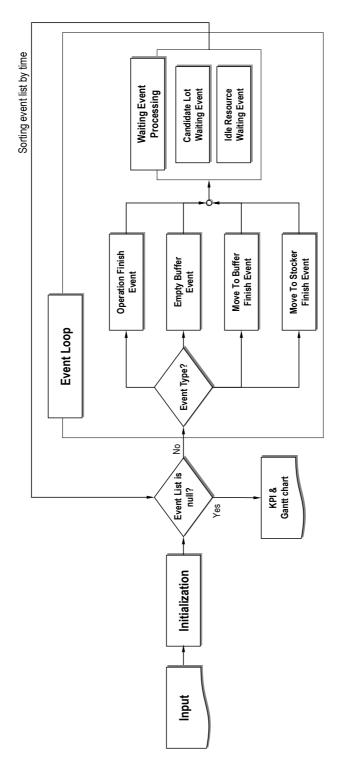

| Figure 4.1 | Structure of DEBS (Discrete Event Based Simulator)                 | 26 |

| Figure 4.2 | Main screen of the monitoring tool                                 | 32 |

| Figure 4.3 | Resource view of the monitoring tool                               | 33 |

| Figure 4.4 | Decision window of the resource view                               | 35 |

| Figure 4.5 | Statistics view of the monitoring tool                             | 37 |

| Figure 4.6 | KPI view of the monitoring tool                                    | 38 |

| Figure 4.7 | WIP charts of the monitoring tool                                  | 40 |

| Figure 4.8 | Comparison page of the monitoring tool                             | 42 |

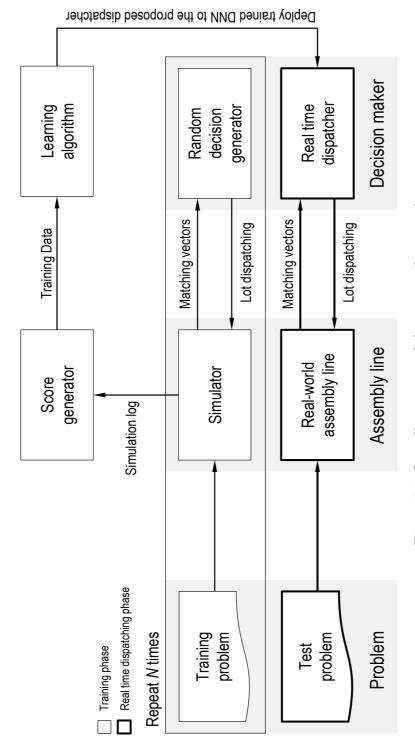

| Figure 5.1 | Overall structure of the proposed approach                         | 45 |

| Figure 5.2 | The structure of RTRD                                              | 46 |

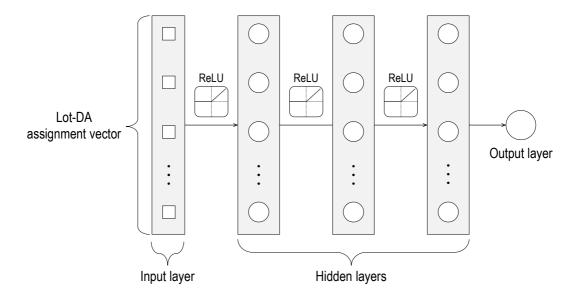

| Figure 5.3 | The structure of RTLD                                              | 54 |

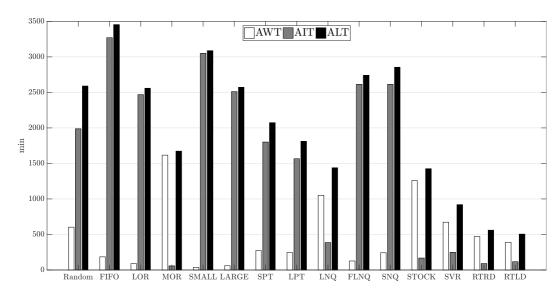

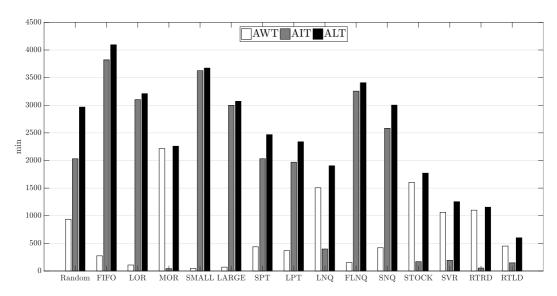

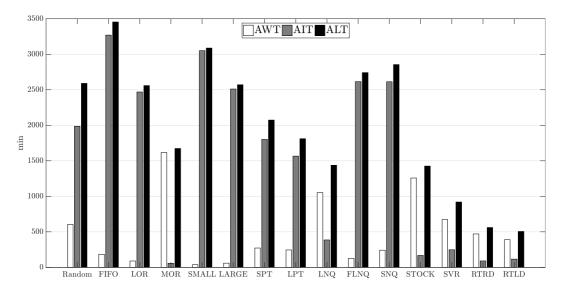

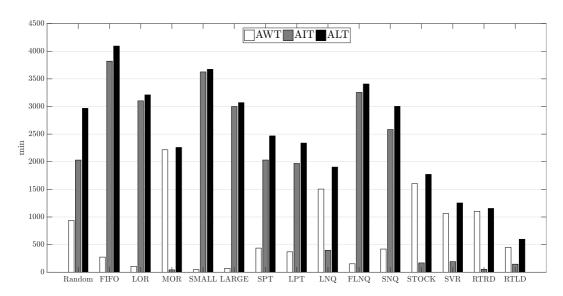

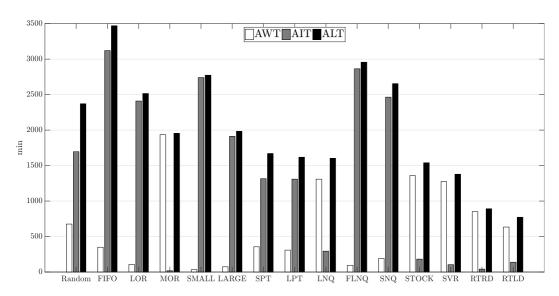

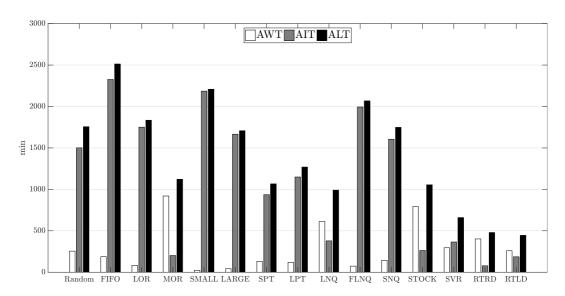

| Figure 6.1 | $AWT,\ AIT,\ {\rm and}\ ALT$ results of the proposed dispatchers   |    |

|            | and the existing methods for dataset 1                             | 68 |

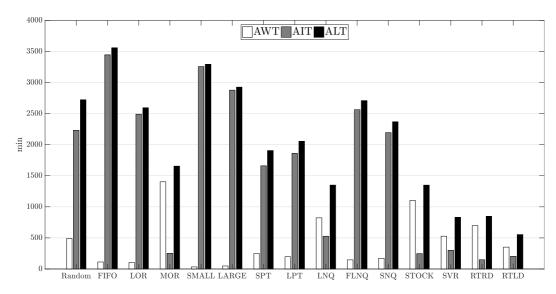

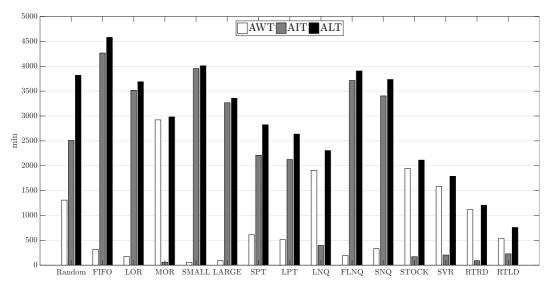

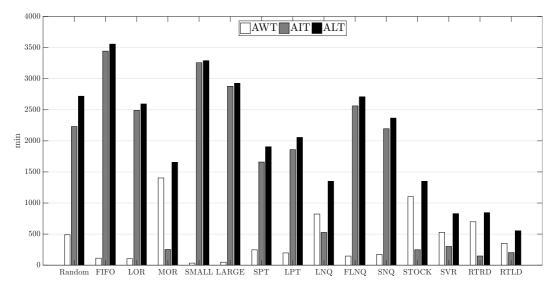

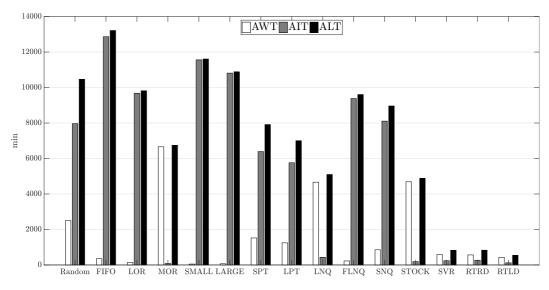

| Figure 6.2  | AWT, $AIT$ , and $ALT$ results of the proposed dispatchers                |    |

|-------------|---------------------------------------------------------------------------|----|

|             | and the existing methods for dataset 2                                    | 69 |

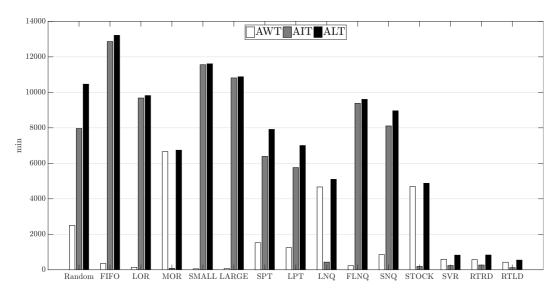

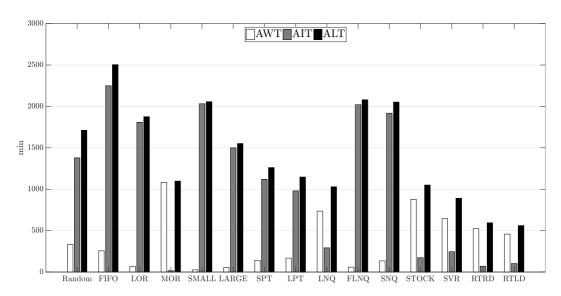

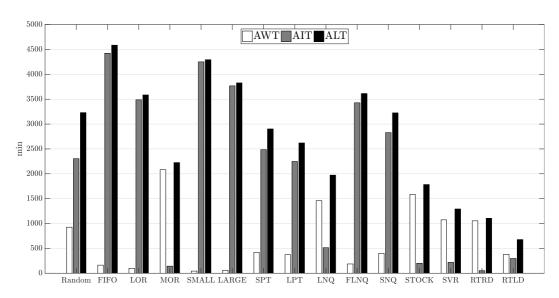

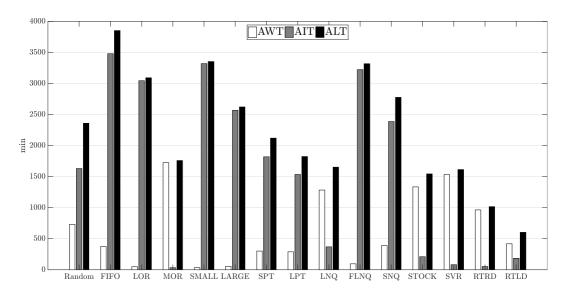

| Figure 6.3  | AWT, $AIT$ , and $ALT$ results of the proposed dispatchers                |    |

|             | and the existing methods for dataset 7                                    | 70 |

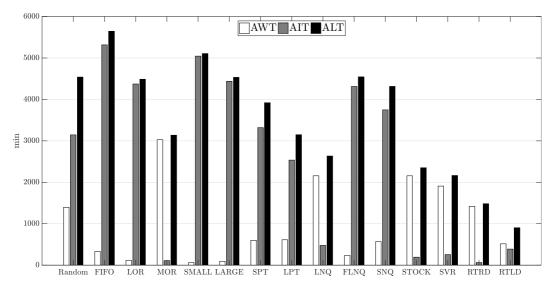

| Figure 6.4  | AWT, $AIT$ , and $ALT$ results of the proposed dispatchers                |    |

|             | and the existing methods for dataset 11                                   | 71 |

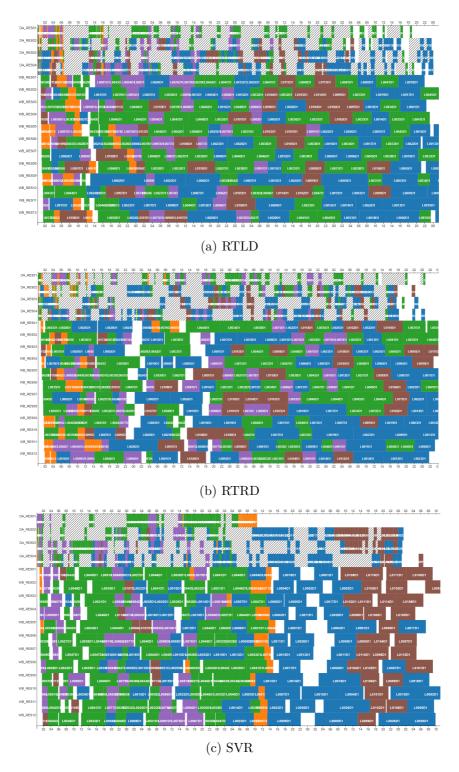

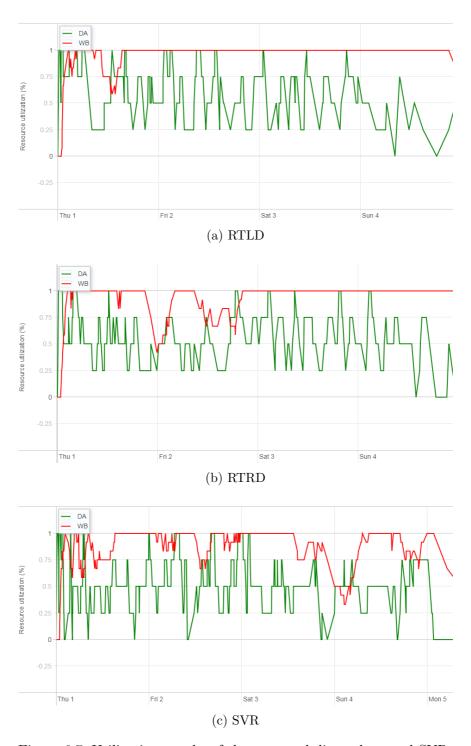

| Figure 6.5  | WIP graphs of the proposed dispatchers, and SVR                           | 73 |

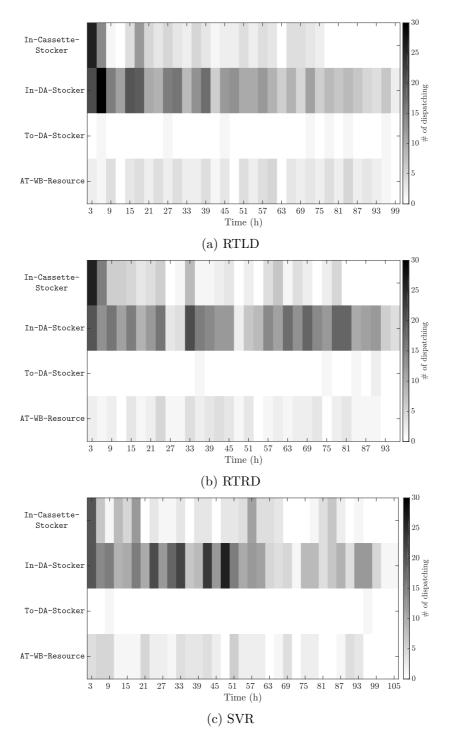

| Figure 6.6  | Gantt charts of the proposed dispatchers and SVR                          | 74 |

| Figure 6.7  | Utilization graphs of the proposed dispatchers and SVR. $$                | 75 |

| Figure 6.8  | Dispatching frequencies according to lot statuses over time.              | 76 |

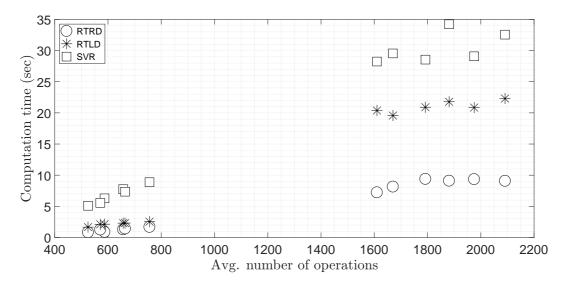

| Figure 6.9  | Computation time of RTRD, RTLD, and SVR according to                      |    |

|             | the average number of operations                                          | 78 |

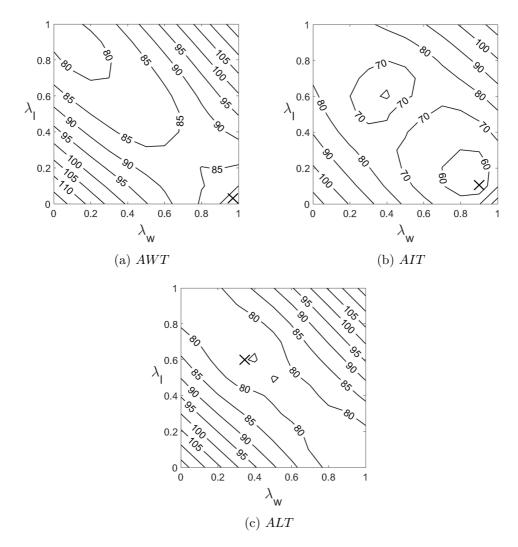

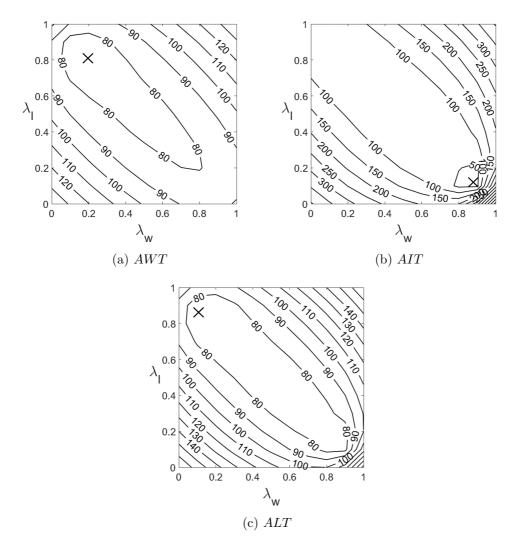

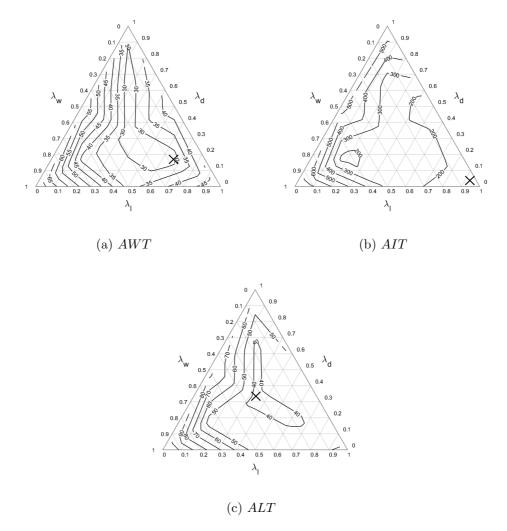

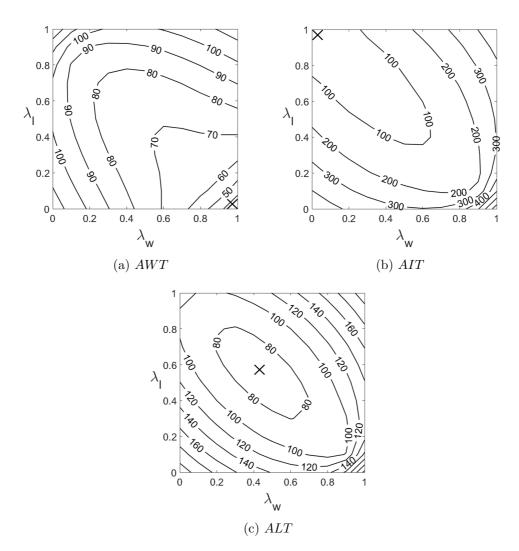

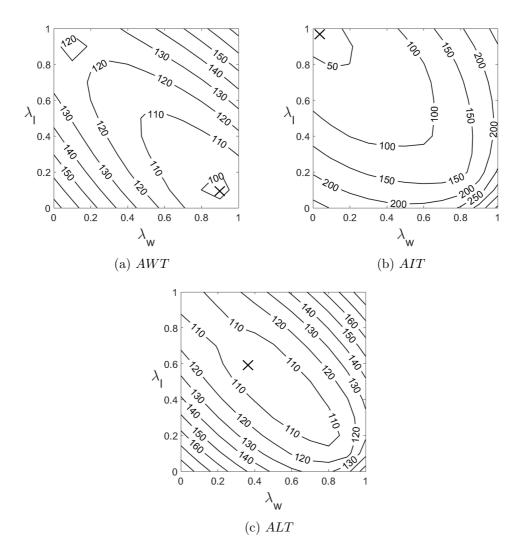

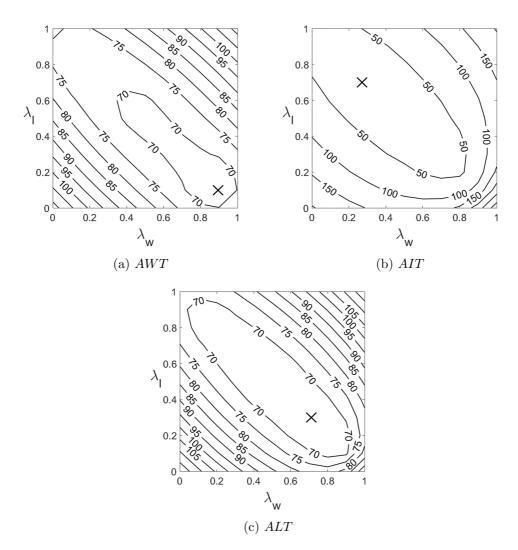

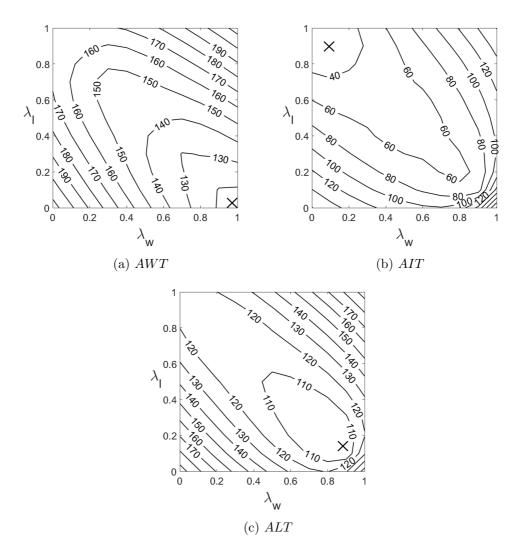

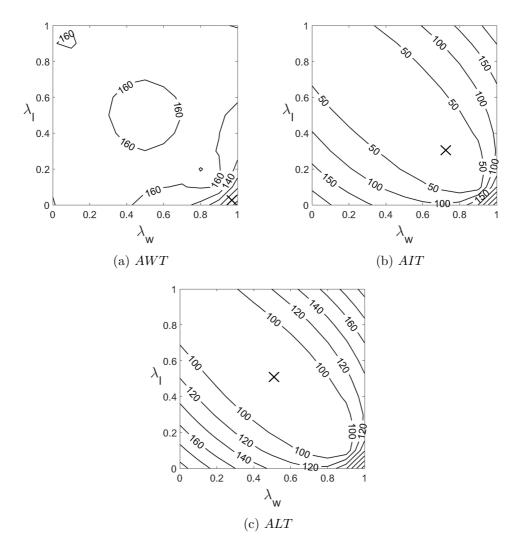

| Figure 6.10 | Performances of RTRD against SVR depending on $\lambda_w$ and             |    |

|             | $\lambda_l$ in dataset 4                                                  | 80 |

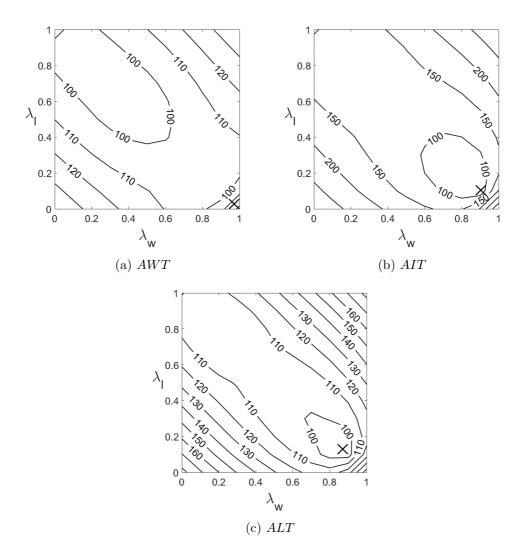

| Figure 6.11 | Performances of RTRD against SVR depending on $\lambda_w$ and             |    |

|             | $\lambda_l$ in dataset 9                                                  | 81 |

| Figure 6.12 | Performances of RTRD against SVR depending on $\lambda_w$ and             |    |

|             | $\lambda_l$ in dataset 10                                                 | 82 |

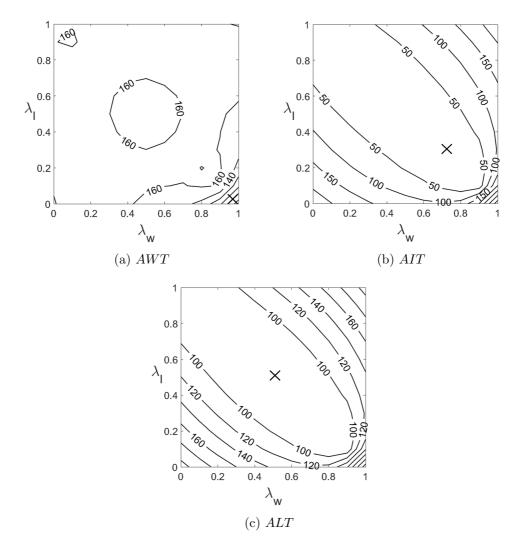

| Figure 6.13 | Performances of RTRD against SVR depending on $\lambda_w$ and             |    |

|             | $\lambda_l$ in dataset 11                                                 | 83 |

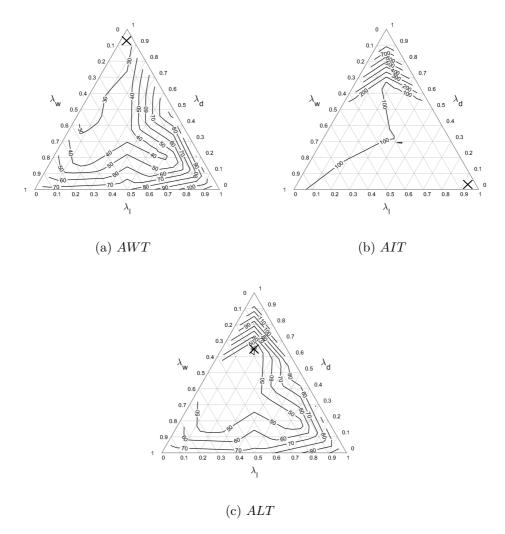

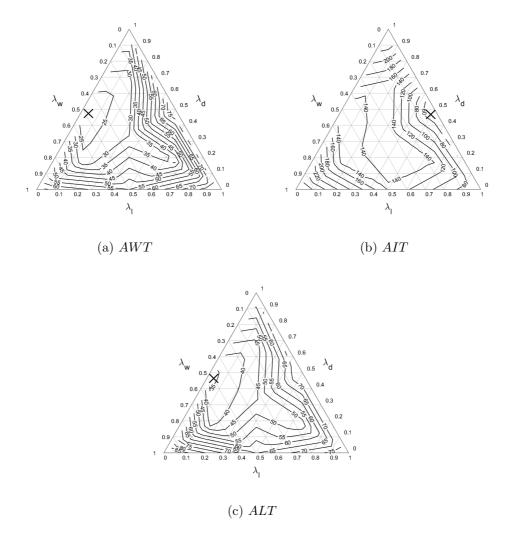

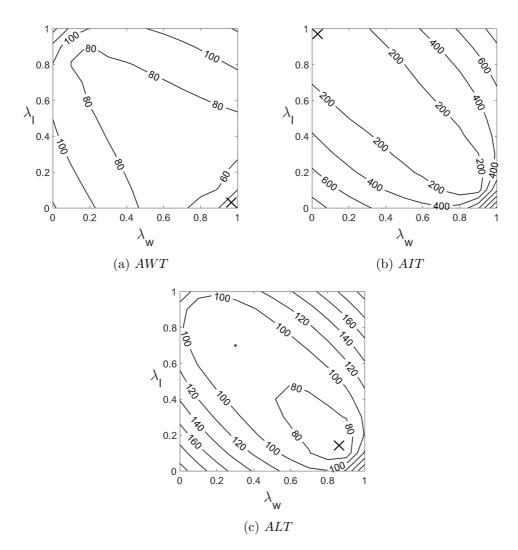

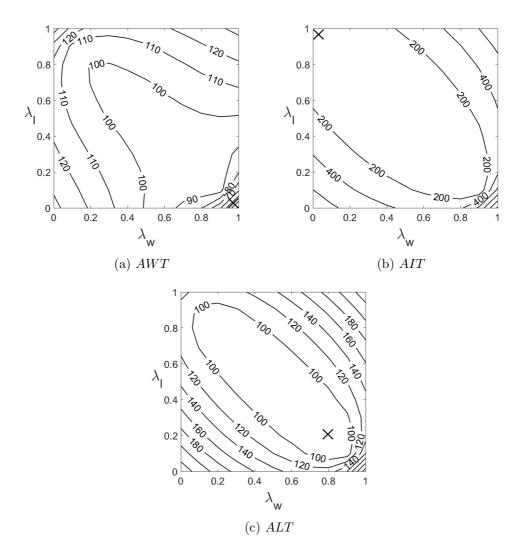

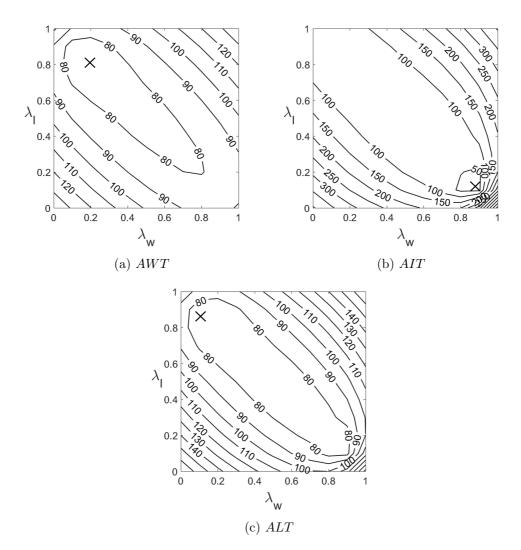

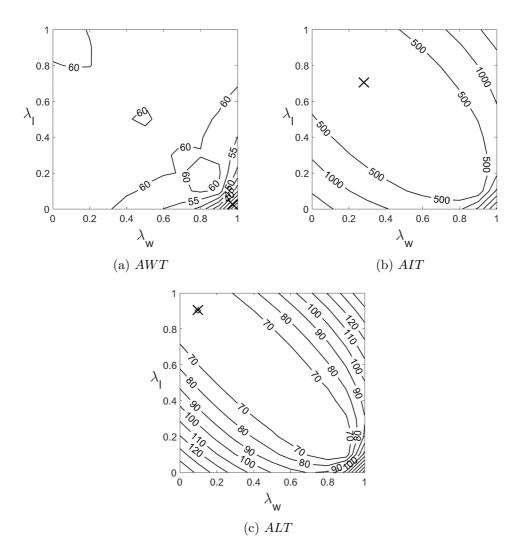

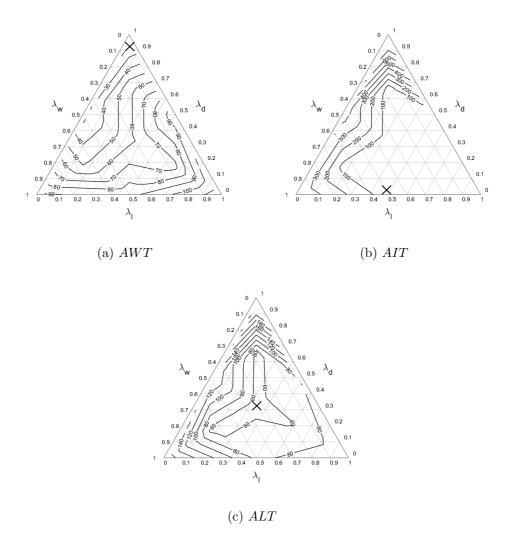

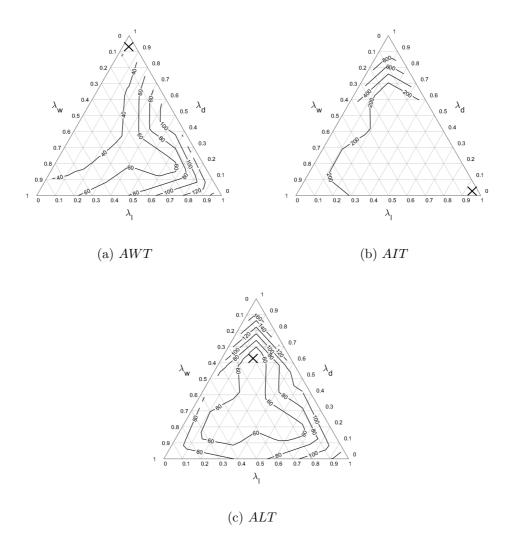

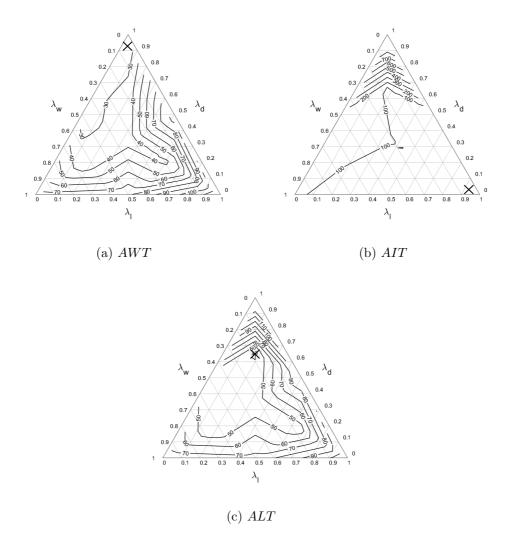

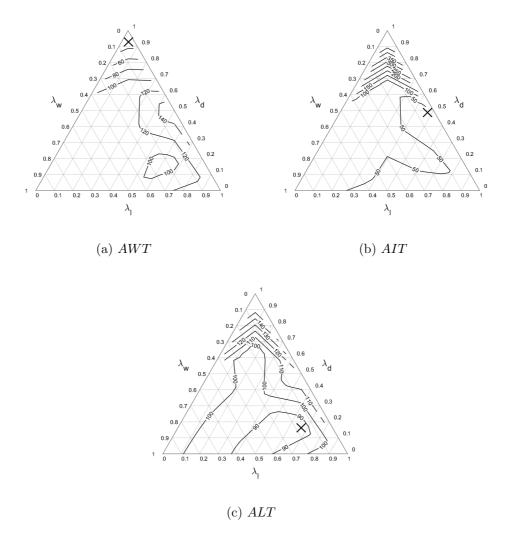

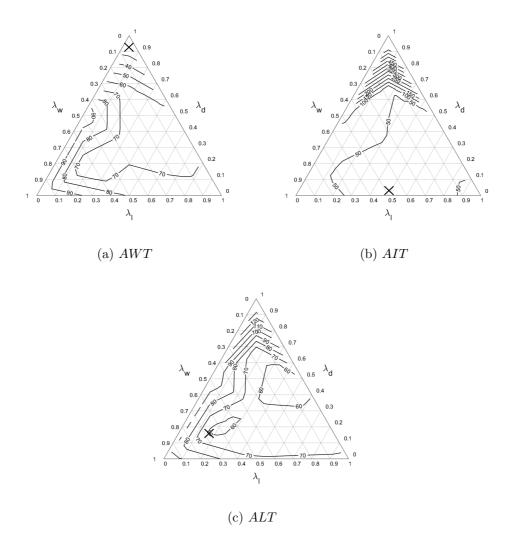

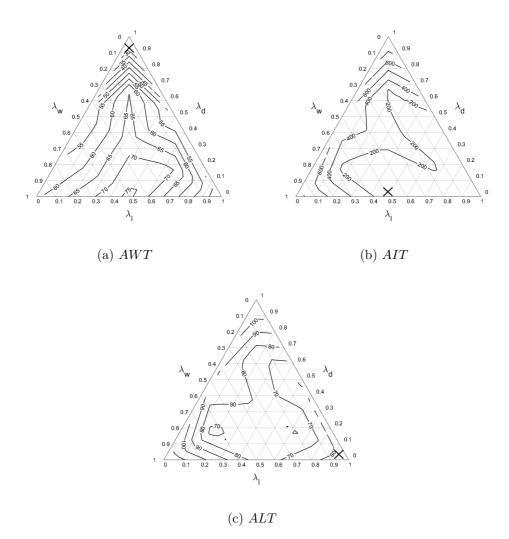

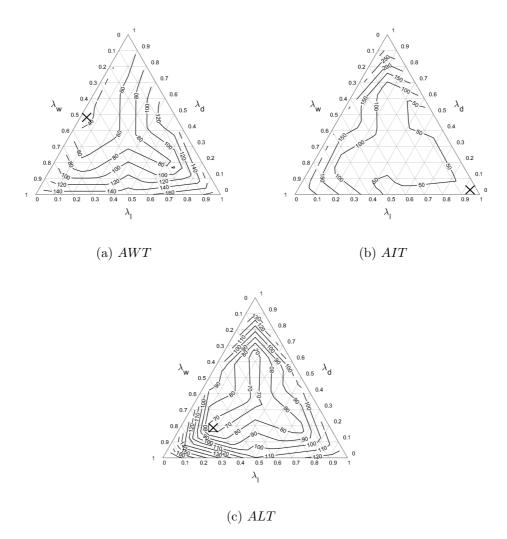

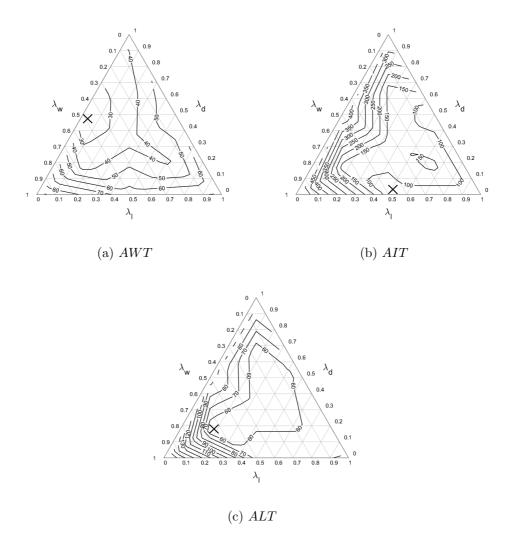

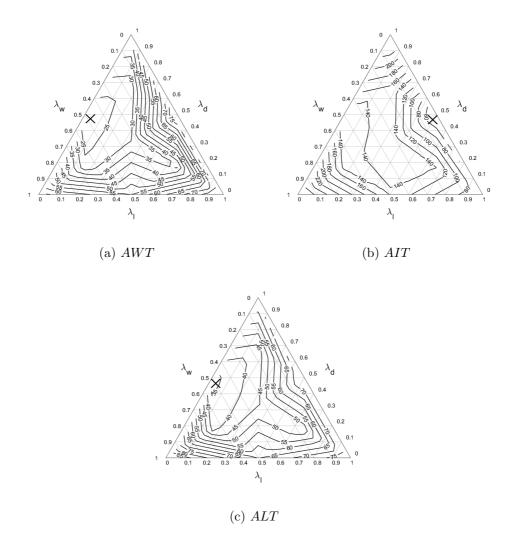

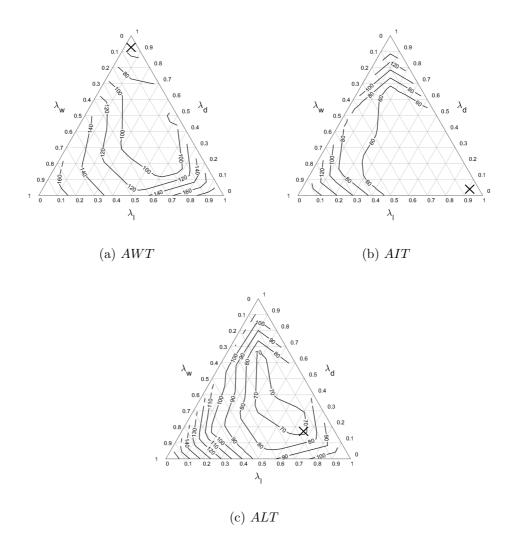

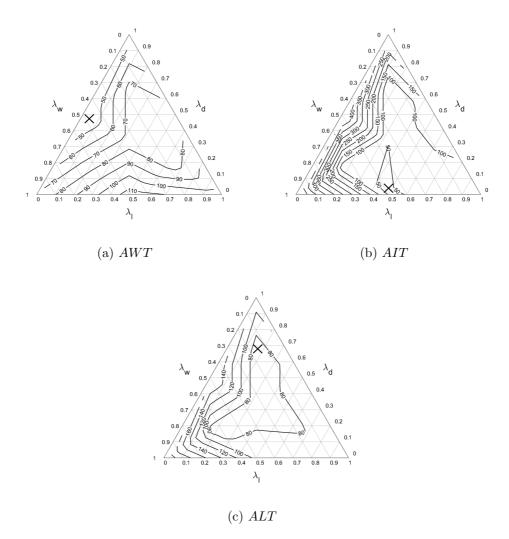

| Figure 6.14 | Performances of RTLD against SVR depending on $\lambda_w$ , $\lambda_l$ , |    |

|             | and $\lambda_d$ in dataset 3                                              | 84 |

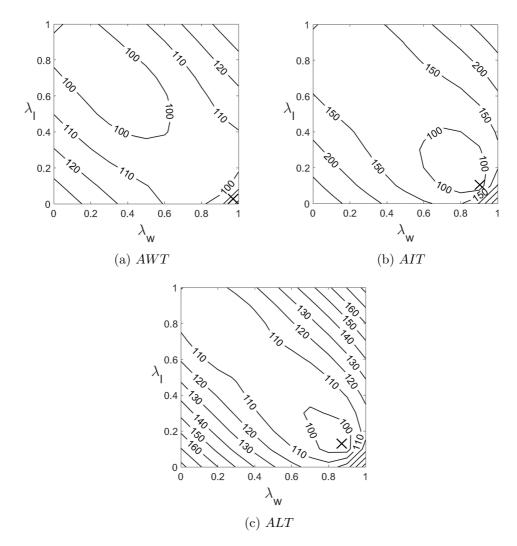

| Figure 6.15 | Performances of RTLD against SVR depending on $\lambda_w, \lambda_l$ ,    |    |

|             | and $\lambda_d$ in dataset 6                                              | 85 |

| Figure 6.16 | Performances of RTLD against SVR depending on $\lambda_w$ , $\lambda_l$ , |     |

|-------------|---------------------------------------------------------------------------|-----|

|             | and $\lambda_d$ in dataset 9                                              | 86  |

| Figure 6.17 | Performances of RTLD against SVR depending on $\lambda_w$ , $\lambda_l$ , |     |

|             | and $\lambda_d$ in dataset 12                                             | 87  |

| Figure A.1  | $AWT,\ AIT,\ {\rm and}\ ALT$ results of the proposed dispatchers          |     |

|             | and the existing methods for dataset $1. \dots \dots \dots$ .             | 97  |

| Figure A.2  | $AWT,\ AIT,\ {\rm and}\ ALT$ results of the proposed dispatchers          |     |

|             | and the existing methods for dataset 2                                    | 98  |

| Figure A.3  | $AWT,\ AIT,\ {\rm and}\ ALT$ results of the proposed dispatchers          |     |

|             | and the existing methods for dataset 3                                    | 98  |

| Figure A.4  | $AWT,\ AIT,\ {\rm and}\ ALT$ results of the proposed dispatchers          |     |

|             | and the existing methods for dataset 4                                    | 99  |

| Figure A.5  | $AWT,\ AIT,\ {\rm and}\ ALT$ results of the proposed dispatchers          |     |

|             | and the existing methods for dataset 5                                    | 99  |

| Figure A.6  | $AWT,\ AIT,\ {\rm and}\ ALT$ results of the proposed dispatchers          |     |

|             | and the existing methods for dataset 6                                    | 100 |

| Figure A.7  | AWT, $AIT$ , and $ALT$ results of the proposed dispatchers                |     |

|             | and the existing methods for dataset 7                                    | 100 |

| Figure A.8  | AWT, $AIT$ , and $ALT$ results of the proposed dispatchers                |     |

|             | and the existing methods for dataset 8                                    | 101 |

| Figure A.9  | AWT, $AIT$ , and $ALT$ results of the proposed dispatchers                |     |

|             | and the existing methods for dataset 9                                    | 101 |

| Figure A.10 | AWT, $AIT$ , and $ALT$ results of the proposed dispatchers                |     |

|             | and the existing methods for dataset 10                                   | 102 |

| Figure A.11 | AWT, $AIT$ , and $ALT$ results of the proposed dispatchers       |     |

|-------------|------------------------------------------------------------------|-----|

|             | and the existing methods for dataset 11                          | 102 |

| Figure A.12 | $AWT,\ AIT,\ {\rm and}\ ALT$ results of the proposed dispatchers |     |

|             | and the existing methods for dataset 12                          | 103 |

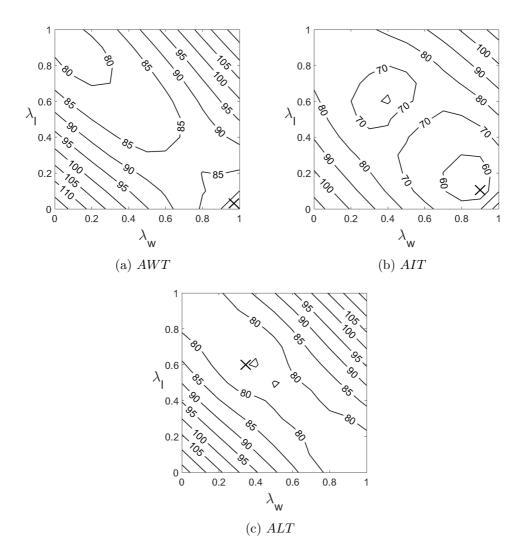

| Figure B.1  | Performances of RTRD against SVR depending on $\lambda_w$ and    |     |

| O           | $\lambda_l$ in dataset 1                                         | 105 |

| Figure B.2  | Performances of RTRD against SVR depending on $\lambda_w$ and    |     |

|             | $\lambda_l$ in dataset 2                                         | 106 |

| Figure B.3  | Performances of RTRD against SVR depending on $\lambda_w$ and    |     |

|             | $\lambda_l$ in dataset 3                                         | 107 |

| Figure B.4  | Performances of RTRD against SVR depending on $\lambda_w$ and    |     |

|             | $\lambda_l$ in dataset 4                                         | 108 |

| Figure B.5  | Performances of RTRD against SVR depending on $\lambda_w$ and    |     |

|             | $\lambda_l$ in dataset 5                                         | 109 |

| Figure B.6  | Performances of RTRD against SVR depending on $\lambda_w$ and    |     |

|             | $\lambda_l$ in dataset 6                                         | 110 |

| Figure B.7  | Performances of RTRD against SVR depending on $\lambda_w$ and    |     |

|             | $\lambda_l$ in dataset 7                                         | 111 |

| Figure B.8  | Performances of RTRD against SVR depending on $\lambda_w$ and    |     |

|             | $\lambda_l$ in dataset 8                                         | 112 |

| Figure B.9  | Performances of RTRD against SVR depending on $\lambda_w$ and    |     |

|             | $\lambda_l$ in dataset 9                                         | 113 |

| Figure B.10 | Performances of RTRD against SVR depending on $\lambda_w$ and    |     |

|             | $\lambda_l$ in dataset 10                                        | 114 |

| Figure B.11 | Performances of RTRD against SVR depending on $\lambda_w$ and             |     |

|-------------|---------------------------------------------------------------------------|-----|

|             | $\lambda_l$ in dataset 11                                                 | 115 |

| Figure B.12 | Performances of RTRD against SVR depending on $\lambda_w$ and             |     |

|             | $\lambda_l$ in dataset 12                                                 | 116 |

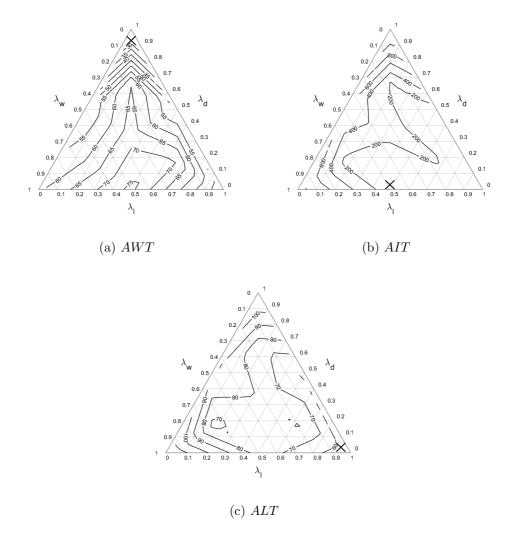

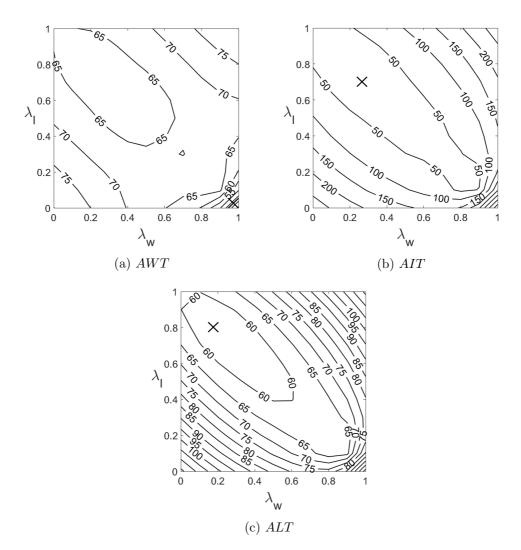

| Figure C.1  | Performances of RTLD against SVR depending on $\lambda_w$ , $\lambda_l$ , |     |

|             | and $\lambda_d$ in dataset 1                                              | 118 |

| Figure C.2  | Performances of RTLD against SVR depending on $\lambda_w, \lambda_l$ ,    |     |

|             | and $\lambda_d$ in dataset 2                                              | 119 |

| Figure C.3  | Performances of RTLD against SVR depending on $\lambda_w$ , $\lambda_l$ , |     |

|             | and $\lambda_d$ in dataset 3                                              | 120 |

| Figure C.4  | Performances of RTLD against SVR depending on $\lambda_w$ , $\lambda_l$ , |     |

|             | and $\lambda_d$ in dataset 4                                              | 121 |

| Figure C.5  | Performances of RTLD against SVR depending on $\lambda_w$ , $\lambda_l$ , |     |

|             | and $\lambda_d$ in dataset 5                                              | 122 |

| Figure C.6  | Performances of RTLD against SVR depending on $\lambda_w$ , $\lambda_l$ , |     |

|             | and $\lambda_d$ in dataset 6                                              | 123 |

| Figure C.7  | Performances of RTLD against SVR depending on $\lambda_w$ , $\lambda_l$ , |     |

|             | and $\lambda_d$ in dataset 7                                              | 124 |

| Figure C.8  | Performances of RTLD against SVR depending on $\lambda_w$ , $\lambda_l$ , |     |

|             | and $\lambda_d$ in dataset 8                                              | 125 |

| Figure C.9  | Performances of RTLD against SVR depending on $\lambda_w$ , $\lambda_l$ , |     |

|             | and $\lambda_d$ in dataset 9                                              | 126 |

| Figure C.10 | Performances of RTLD against SVR depending on $\lambda_w$ , $\lambda_l$ , |     |

|             | and $\lambda_d$ in dataset 10                                             | 127 |

| Figure C.11 | Performances of RTLD against SVR depending on $\lambda_w$ , $\lambda_l$ , |     |

|-------------|---------------------------------------------------------------------------|-----|

|             | and $\lambda_d$ in dataset 11                                             | 128 |

| Figure C.12 | Performances of RTLD against SVR depending on $\lambda_w$ , $\lambda_l$ , |     |

|             | and $\lambda_{z}$ in dataset 12                                           | 129 |

#### Chapter 1

#### Introduction

#### 1.1 Background and motivation

Re-entrant manufacturing lines (RML) have become at the center of attention in both academia and industry since semiconductor manufacturing and thin film transistor-liquid crystal display (LCD) manufacturing lines came along [1, 2, 3, 4, 5]. RMLs are systems where parts can visit the same stage several times before exiting the line [6, 7, 8]. Research in this discipline has been motivated with an increasing demand for small devices equipped with flash memory and LCD such as smart phones and wearable devices [9, 10].

Figure 1.1 shows the concept of RML and the dashed line at the bottom of the figure indicates the flow of parts which go back to the previous stage. There are two types of stockers where parts stay temporarily. The first one at the top of the figure is a place where parts, which have completed an operation at the previous stage, wait before they enter the current one. The second at the bottom of the figure, called a re-entrant stocker, illustrates a place where parts, which have completed the next stage, wait for the re-entrance to the current one.

There are parallel resources that are responsible for processing parts at each stage and assigning a part to a resource is referred to as the dispatching decision.

Figure 1.1: Concept of re-entrant manufacturing line.

Furthermore, a typical type of RML may regard a stage as a bottleneck if its resource utilization is above 85% [11, 12, 13]. This value is considerably subjective. In practice, it is maintained above 90% for semiconductor manufacturing lines [14]. Since the maximum throughput is determined by the bottleneck stage, it is essential to maintain a high level of resource utilization in the bottleneck [15].

It is achievable to keep the resource utilization level high by simply providing a sufficiently large amount of work-in-process (WIP). On the contrary, an excessive amount of WIP leads to increase in the waiting time for parts in the next operations, thus increasing flow time of parts [16]. Therefore, managing WIP levels properly matters in order to resolve the multi-objective problem of reducing flow time of parts and improving resource utilization [17].

Unfortunately, the re-entrant nature brings about a challenge to WIP level control [18]. Specifically, if newly arrived parts are frequently assigned to resources of the non-bottleneck stage with re-entrant parts not into consideration, the WIP level of the bottleneck stage will excessively increase. On the other hand, giving a high priority level to re-entrant parts in the non-bottleneck stage can result in a lack of WIP at the bottleneck stage, which decreases resource utilization in the bottleneck stage [19, 20].

From the remark above, it is clear that RMLs require dispatching decisions that differ from those performed in traditional manufacturing lines and flow shops [21, 22, 23]. For this reason, a number of scholars have presented methods for dispatching decisions in RMLs using optimization, meta-heuristics, and dispatching rules [19, 22, 24, 25, 26, 27, 28, 29, 30].

On one hand, approaches with a long computation time to yield dispatching de-

cisions, such as optimization and meta-heuristics, are not proper to be applied to real-world RMLs although they successfully improve objectives through an exhaustive search over solution spaces [31]. This is because, from a practical standpoint, a part has to be immediately assigned to a resource in the event that the resource requests a part.

On the other hand, the benefits of the rule based methods include computational efficiency and ease of implementation [32, 33]. However, the majority of previous dispatching rules are usually designed to address a sole objective, and have limitations when addressing various characteristics of real-world RMLs [34, 35].

In the meantime, it should be noted herein that the previous studies have focused mainly on selecting one among the waiting parts ready to be processed immediately. That is, a resource becomes idle only when there are no waiting parts in the stockers. Yet, it is well known that performance can be improved when an intentional delay is made in resource usage by idling a resource even through there are parts waiting for its processing [36, 37].

Motivated by the considerations above, this thesis attempts to suggest a dispatching method based on deep neural networks (DNNs) that decrease flow time without loss in resource utilization of the bottleneck stage for real-world RMLs. Whenever a dispatching decision is required, the proposed method choose the best part by considering both cases: when parts are processed directly; and when parts undergo an intentional delay in a resource. In other words, the proposed method maintains a high level of resource utilization and minimizes flow time by continuously prioritizing newly arrived parts and re-entrant parts according to the status of the RML.

To achieve this, we use a simulator to generate training data that are used to train the dispatcher. The main difference between the existing learning-based methods and our efforts lies in the fact that the existing work requires training data generated from optimal solutions which are difficult to obtain, while our method is capable of generating training data by simply performing simulations with random decision making. In detail, the performances of the decisions in randomly generated simulation logs are measured by the proposed score generator, and the evaluated simulation logs are used to train the DNN in the proposed dispatcher. In real-time dispatching phase, the proposed method quantifies the degree of preference for each decision with a numerical score and then completes the dispatching decision based on the score.

As mentioned above, to learn dispatching decisions considering intentional delay, we employ a DNN which is capable of capturing complex non-linear dynamics [38]. Furthermore, it is known that a DNN enables computational models to learn representations of data through multiple levels of abstraction to understand the hidden relationships among input features [39, 40]. Neural networks (NNs) have been successfully applied to a variety of areas which involve decisions, including dispatching and scheduling problems [41, 42, 43, 44, 45, 46, 47, 48].

#### 1.2 Objectives

The objective of this thesis is to propose a real time dispatcher (RTD) for decreasing flow time while maintaining a high level of resource utilization in real-world RMLs. The thesis consists of two major studies to reach its goals. The first one focuses on implementing an underlying environment for conducting research. Then, the second one that deals with developing RTDs is sub-categorized into two parts according to how decisions are made. The basic concepts and purposes of the studies are summarized as follows.

First, a discrete event based simulator (DEBS) and monitoring tool are proposed in Chapter 4. DEBS is designed to imitate the RML described in Chapter 3, and calculate key performance indicators (KPIs) such as mean flow time and resource utilization. Furthermore, a DEBS takes on generating training data used to train a DNN. In addition to the functions of the existing Gantt chart, the monitoring tool presents various information on RMLs at the time of a dispatching decision being made. This feature is used to analyze the reason behind dispatching decision making, which is helpful to improving performance in RTDs.

Second, two DNN based RTDs with different decision-making processes are suggested in Chapter 5. RTDs are in charge of choosing the best part by considering both cases: when parts are processed directly; and when parts undergo an intentional delay in a resource at the non-bottleneck stage. To make that happen, we utilize the DEBS developed in Chapter 4 to generate training data used for RTDs in the training phase. In the real time dispatching phase, dispatching decisions can be made quickly thanks to the calculation of using parameters of the trained RTDs.

In detail, each alternative of the dispatching decision for a resource is represented

in the form of a vector. The proposed method quantifies the degree of preference for each vector with a numerical score, on which it completes the dispatching decision. A preferred vector receives a higher value as the dispatching decision is likely to shorten the part's waiting time and reduce the idle time of resources in the bottleneck stage.

Finally, the effectiveness and efficiency of the proposed methods are demonstrated through extensive experiments in Chapter 6. The performances of the proposed RTDs are compared with the conventional dispatching methods in terms of flow time and bottleneck resource utilization. Additionally, numerical experiments are conducted to investigate the merits and demerits of the proposed two RTDs.

#### 1.3 Thesis outline

This thesis is comprised of seven chapters and the remainder is organized as follows. In Chapter 2, previous research on the dispatching methods for RMLs is examined and DNN based techniques applied to the dispatching decision are reviewed. Chapter 3 describes the problem under consideration and defines the notations used in the thesis. The features and functions of DEBS and monitoring tool are presented in Chapter 4. The proposed approaches, consisting of two RTDs, a score generator, and learning algorithm, is introduced in Chapter 5. Subsequently, the experimental results are summarized and discussed in Chapter 6. Finally, we conclude this work with contributions and future work of this thesis in Chapter 7.

#### Chapter 2

#### Literature Review

#### 2.1 Dispatching decisions in RMLs

A considerable amount of literature has been published on dispatching methods in RMLs. Previous research is classified according to their approaches and performance metrics, as presented in Table 2.1.

Simulation-based studies have attempted to understand the characteristics of part flows by executing tasks virtually in advance [49, 50]. Most studies utilized simulation techniques to analyze or improve their objectives [51, 52, 53, 54]. On the other hand, researchers in [55, 56] sought simulation methods that precisely represent real-world RMLs and quickly process events.

Another line of research aims to perform dispatching decisions by utilizing dispatching rules [15, 57]. Publications on rule-based dispatching can be classified into two categories. The first group proposes methods for selecting a dispatching rule among the existing ones to obtain desired performance measures in a specific situation [14, 58, 59, 60]. To effectively cope with changes in the bottleneck stage, algorithms to detect bottleneck stage are also to be applied in [14, 60].

The second category focuses mainly on improving objectives by developing their own rule-based methods [61, 62, 63, 64]. In particular, Bard et al. [63] presented a

multi-stage approach consisting of three steps, which decides on the best resourcetooling configurations and the way to assign parts to resources. They succeeded in increasing weighted throughput in small-size problems. However, their method requires a longer computation time as problems become as large as those in the real world.

To overcome the limitations of the dispatching rules, Ma et al. [65] investigated a dynamic scheduling method based on support vector regression (SVR). Specifically, they proposed a composite dispatching rule - a linear combination of multiple dispatching rules with a weight assigned to each rule. The scheduling model trained with SVR determines the weights of the composite dispatching rule for a given production line state. Their method outperformed simple dispatching rules in terms of multiple performance measures such as flow time and resource utilization.

Besides the rule-based methods, some studies investigating meta-heuristics have been conducted to improve their particular objectives through an exhaustive search over solution spaces [26]. Genetic algorithm (GA) based methods were popularly used to decrease flow time and increase resource utilization [19, 29, 66]. In particular, the work in [29, 66] utilized the heuristic algorithm as proposed in [73] to reduce time spent on searching solution space.

Additionally, a Tabu search (TS) based algorithm, presented in [30], aims to minimize tardiness. Kang et al. [30] introduced a rolling horizon method that limits the area of unnecessary neighborhood solutions, thus decreasing computation time. Although the existing studies of meta-heuristics attempted to reduce computation time, it is difficult to introduce them into the real-world RMLs where dispatching decisions are required to be made in a real-time manner.

Table 2.1: Overview of previous research on dispatching decisions of RMLs.

| Approaches                | Performance metrics | References                   |

|---------------------------|---------------------|------------------------------|

|                           | Flow time           | [49], [50], [51], [52], [53] |

| Simulation                | Simulation cost     | [55], [56]                   |

| Simulation                | Tardiness           | [54], [52]                   |

|                           | Throughput          | [52]                         |

|                           | Flow time           | [14], [15], [57], [58], [59] |

| Dispatching rule          | Tardiness           | [61], [62], [60]             |

| Dispatching rule          | Throughput          | [60], [63]                   |

|                           | Utilization         | [58], [63], [64]             |

| Support vector regression | Flow time           | [65]                         |

| Support vector regression | Utilization         | [00]                         |

|                           | Flow time           | [19], [29], [66]             |

| Meta-heuristic            | Tardiness           | [30]                         |

| Meta-neuristic            | Throughput          | [26]                         |

|                           | Utilization         | [19], [31]                   |

| Case-based reasoning      | Utilization         | [34]                         |

|                           | Flow time           | [27], [67]                   |

| Mathematical programming  | Tardiness           | [68], [69]                   |

| Wathematical programming  | Throughput          | [28]                         |

|                           | Utilization         | [21], [25], [28]             |

| Reinforcement learning    | Flow time           | [70]                         |

| reminorcement learning    | Throughput          | [23], [71], [72]             |

To resolve the disadvantages of meta-heuristics, such as a long computation time to obtain solutions, Lim et al. [34] extended the earlier work in [31] using case-based reasoning. Unfortunately, they failed to achieve as much resource utilization as the existing method provides [31].

Studies were conducted to analyze dispatching decisions using the mathematical formulation of part flow in RMLs [27, 68, 69]. To reduce complexity of the problem of determining dispatching decisions, the works in [21, 25, 28, 67] divided RMLs in different hierarchical layers. Furthermore, reinforcement learning based methods also have been proposed to perform dispatching decisions in RMLs [71, 72, 23, 70]. These methods are characterized in that they attempted to improve the performance of cumulative dispatching results rather than that of immediate dispatching results.

# 2.2 Neural network-based approaches to dispatching decisions

Recently, there has been a considerable interest in using NNs for dispatching decisions in various manufacturing domains [43, 74, 75]. Table 2.2 presents the summary of the previous studies on dispatching decisions with the help of NNs. They are categorized into four cases according to subject.

The field of job shops have attracted attention among many researchers, and the dispatching decision in the job shop system is traditionally known as a complex task [47, 76]. Two NNs are proposed in order to decide different dispatching rules locally for each resource [77]. Due to the structure of the developed NNs, the proposed method was not robust to the number of resources.

An attempt was made to generate training datasets for NNs by using a GA, which can obtain the optimal solution to job shop problems [44]. Although a trained NN successfully yielded performances at the closest level to those of the GA, the NN was designed solely to work for 6x6 job shop problems. Branke et al. [78] used NNs to automatically design dispatching rules in a dynamic stochastic job shop scenario. They also compared three different techniques for automated rule design: NNs, a linear combination of attributes, and a tree representation. Their numerical experiments indicated that NNs outperformed the rest for small-sized problems.

Meanwhile, a sensitivity analysis was conducted [47] in order to find which input attributes of the NN has significant impact on the performance of dispatching results. To be more specific, it measured the relative importance among the inputs of the NN and illustrated how NN output is changed in response to variations in input.

A flow shop is different from the job shop in that all jobs follow the same process-

Table 2.2: Overview of previous research on dispatching decisions using neural networks.

| Subject    | References | References Description                                                                      |

|------------|------------|---------------------------------------------------------------------------------------------|

|            | [77]       | Two NNs that decide different dispatching rules locally for each resource                   |

| Tob abon   | [44]       | Prioritizing each job using NN and GA                                                       |

| പ്വാഭ വാദ  | [78]       | Automated designing dispatching rules through network representation                        |

|            | [47]       | Conducting sensitivity analysis of the effectiveness of the input variables of NN           |

| Flour chon | [62]       | Adjusting the learning rate dynamically by utilizing the proposed algorithm                 |

| done won   | [41]       | Determining the weights of the NN with the developed SA                                     |

| FMS        | [80]       | Assigning different dispatching rules to each of the resources using self-organizing map NN |

| CTATI      | [81]       | Integrating GA and NN to select the optimal subgroup of features from the state of system   |

|            | [59]       | Selecting dispatching rules when desired performance measures are given                     |

| BMI        | [45]       | Approximating the optimal value function using NN                                           |

| TOME       | [33]       | Dynamically determining the parameters of NN based on real-time information of the line     |

|            | [82]       | Predicting the performance of the dispatching rule selected by decision tree                |

ing order [83]. Mouelhi-Chibani and Pierreval [41] suggested a NN based approach for assigning the most suited dispatching rule to a resource each time the resource becomes available. In their research, weights of the NN are determined with the simulated annealing (SA) method rather than using training examples.

Unlike the flow shop, a hybrid flow shop (HFS) contains at least one stage that consists of multiple resources [84]. The delta-bar-delta algorithm was developed to further speed up the convergence of the weights of NNs in the HFS [79]. This algorithm is tasked with adjusting the learning rate dynamically based on the variation of training errors.

Some authors investigated how to use NNs in a flexible manufacturing system (FMS) defined in [85]. On the one hand, Shiue and Guh [81] presented a hybrid learning framework that integrates a NN and GA to select the optimal subgroup of features from the state of the FMS. Although the performance of the framework is superior to other machine learning methods, it takes an excessively long computation time to discover the chromosomes and determine the learning parameters of the NN.

Meanwhile, Guh et al. [80] developed a method to assign different dispatching rules in each of the resources using self-organizing map (SOM) NNs. In detail, the proposed method determines appropriate multiple dispatching rules (MDRs) for a specific period. The results showed that their method outperforms two alternatives with the same dispatching rule in all resources.

Adding to this, many studies were carried out on the dispatching decisions using NNs in RMLs [33, 45, 59, 82]. To take a closer look, Min and Yih [59] proposed an approach for the selection of dispatching rules when desired performance measures are given with the status of the RML. However, they made an unsuccessful effort

to obtain high quality datasets of dispatching decisions, which has been left to be addressed.

In order to dynamically determine the parameters of a NN, Li et al. [33] devised an adaptive dispatching rule (ADR) that takes into account real-time state information of RMLs. They demonstrated that their method was superior to the existing dispatching rules by doing numerical experiments on semiconductor fabrication facilities.

A hybrid knowledge discovery framework was developed to decide the most appropriate dispatching rule using a decision tree and NN [82], which are responsible for selecting one among the existing dispatching rules, and then predicting the performance of the selected rule. In addition, Zhou et al. [45] attempted to approximate the optimal value function by using a NN. More specifically, they presented a dynamic dispatching approach for RMLs by combining dynamic programming (DP) with DNNs.

In spite of the fact that previous research successfully addresses the use of NNs for dispatching decisions on various manufacturing systems, most conventional methods can learn dispatching strategies only if training datasets are obtained from optimal solutions. This only implies inefficiency as their methods necessitate a solver that yields optimal solutions for given problems. Furthermore, as mentioned above, they do not factor in intentional delay decisions, which can possibly improve performance if they are done properly.

#### Chapter 3

#### **Problem Definition**

#### 3.1 Multiple-chip product (MCP) assembly lines

We consider a multiple-chip products (MCPs) assembly line for semiconductor manufacturing which is the most representative one of RMLs [17]. MCP production involves complex and correlated assembly stages consisting of backlap, wafer sawing, die attach (DA), wire bonding (WB), and molding [29, 61]. Especially, in the DA and WB stages, wafers are grouped as a lot and processed by a resource. Here, assigning a lot to a resource is referred to as the lot dispatching decision.

For producing the large capacity MCPs, frequently re-entrant lots between the DA and WB stages are necessary to assemble multiple chips into one single packaging module [61]. In particular, the capacity of MCP tends to be proportional to the number of visits to these stages [31]. The WB stage is usually considered as a bottleneck compared to the DA stage due to its extremely long processing time for soldering a number of wires to each die [86]. To efficiently operate assembly lines, maintaining high utilization of resources in the WB stage is essential.

To manage the WIP level, in an attempt to decrease the flow time without loss in resource utilization of the bottleneck stage, in this thesis, we focus on controlling the lot flow in the DA stage. This is because the lot dispatching decision in a nonbottleneck stage has a significant impact on the WIP level of an assembly line [54, 86]. Furthermore, the utilization of the DA stage is not necessary to be kept high if that of the WB stage does not decrease because the throughput of the assembly line is determined by the bottleneck stage [15].

For lot dispatching in the bottleneck stage, a higher utilization rate of resources can be achieved simply by processing lots primarily with longer processing time [86, 87]. Therefore, the lot dispatching decisions of the WB stage in this thesis are carried out by using the rule that assigns a high priority level to the lot which has the longest processing time for a resource.

We are given a set of resource types,  $M = \{M_q | q = 1, ..., N_M\}$ , where  $M_q$  is associated with  $n_q$  resources,  $R_{q,1}, ..., R_{q,n_q}$ . For each operation, its available resources and processing time are determined according to the resource type. There is a set of job types,  $J = \{J_i | i = 1, ..., N_J\}$ , where  $J_i$  consists of a sequence of operations specified in a predetermined order. We represent the  $j^{th}$  operation of  $J_i$  as  $O_{i,j}$ , and  $A(O_{i,j})$  indicates a set of resource types capable of processing  $O_{i,j}$ . The  $k^{th}$  lot for  $J_i$  is denoted as  $L_{i,k}$ ,  $k = 1, ..., n_i$ , where  $n_i$  is the number of lots of type  $J_i$ . Thus,  $L_{i,k}$  is processed according to the operation sequence corresponding to  $J_i$ , and  $I(L_{i,k})$  returns the smallest index among those of the operations waiting to be processed. Additionally, the processing time of a lot is to be proportional to the number of chips in the lot.

Fig. 3.1 illustrates the lot flow of the MCP production process considered in this thesis. Specifically, a lot is required to be processed in the DA stage prior to the WB stage, and the final operation of a lot is to complete in the WB stage. The dashed line at the bottom represents the flow of lots which revisit the DA stage

Figure 3.1: Lot flow of DA and WB stages in MCP production.

after finishing the WB operation.

As shown in Fig. 3.1, there are three types of stockers, namely cassette, DA, and WB stockers where lots stay temporarily. First, the cassette stocker provides locations for where newly arrived lots wait for the first DA operation. Next, the DA stocker is a re-entrant stocker where lots that have completed a WB operation wait for the re-entrance to the next DA operation. Finally, the WB stocker is where lots that have completed a DA operation wait before they enter their WB operation.

Lots in either the cassette or DA stockers are transported to the WB stocker after DA operations are finished. This means that newly arrived and re-entrant lots are located together in the WB stocker, which yields complex lot flows. For this reason, it becomes challenging to manage the WIP level of the WB stocker at appropriate level, which is highly likely to decrease the utilization of the WB resources or increase the waiting time of lots in the WB stocker.

In front of each resource, there is a resource buffer in which a lot waits for the operation until the resource becomes idle. The capacity of a resource buffer is assumed to be one. A lot is not interrupted once its operation starts, and an operation is carried out by one resource at a time. Additionally, it is assumed that there is no setup time between lots of different job types.

Regarding MCP assembly lines under the characteristics described above, we aim to minimize the waiting time of lots and the idle time of WB resources in order to reduce the flow time while maintaining high utilization of the bottleneck stage. This is due to the fact that the flow time consists of processing time, moving time, and waiting time. Since the processing and moving time are necessary to complete all operations of a lot, the reduction in flow time is mainly achievable by decreasing

Figure 3.2: Candidate lots according to status and intentional delay.

the waiting time. Furthermore, the average utilization rate of the resources increases as resources perform operations with shorter idle periods [17].

## 3.2 Lot dispatching process in MCP assembly lines

A candidate lot refers to one that is assignable to a DA resource when its resource buffer is empty. The types of a candidate lot according to its status are illustrated in Fig. 3.2. A lot dispatching method determines the assignment between a candidate lot,  $L_{i,k}$ , and a DA resource with an empty resource buffer,  $R_{q,s}$ , based on the decision policy if  $M_q \in A(O_{i,I(L_{i,k})})$ . Furthermore, once a lot is dispatched, it is excluded from the candidate lots.

For a DA resource, a lot can be moved from the stocker to the DA resource buffer immediately whenever a candidate lot whose status is In-Cassette-Stocker or In-DA-Stocker is selected to be dispatched. Otherwise, in case that a candidate lot whose status is either To-DA-Stocker or At-WB-Resource is selected, this results in an intentional delay on the DA resource due to the additional time to carry out

the remaining WB operation and/or to arrive at a DA stocker. The details of how the dispatcher assigns a lot to a DA resource are described in Figure 3.3. The bottom part of the step 3 shows the time for each lot to arrive the DA resource after the lot is selected by the dispatcher.

In particular, the flow time of a lot begins to be measured when the lot in the cassette stocker is dispatched. This is a well-known practice in MCP assembly lines where the product type of each lot is determined when the first operation of the lot is performed. In other words, the time lots spend in the cassette stocker is not the interest in terms of WIP management.

In the WB stage, intentional delays are not necessary since high utilization of resources should be achieved. Accordingly, among the lots in the WB stocker, the lot with longest processing time is assigned to a WB resource when its resource buffer is empty.

Figure 3.3: Illustration of how the dispatcher assigns a lot to a DA resource.

# Chapter 4

# Frameworks for Data Generation and Performance Evaluation

In this chapter, we present a DEBS and monitoring tool which are essential for generating training data and evaluating the performance of dispatching decisions. Python and JavaScript are adopted to implement DEBS and the monitoring tool, respectively, as their programming language.

## 4.1 Discrete event-based simulator

## 4.1.1 Purpose of implementation

A discrete event simulation (DES) is a widely used approach to analyzing and understanding the dynamics of manufacturing lines. It is a highly flexible tool that can evaluate different alternatives of system configurations and operation strategies to determine decisions in the manufacturing lines [88]. Under this rational, the purpose of implementing DEBS directly in this thesis can be summarized in three ways.

The first purpose is to simulate real-world RMLs where practical constraints and various types of events exist. A DEBS is required to perform dispatching decisions in the situation where resource types capable of processing an operation are determined. The resource buffer capacity and the physical path of the lot should also be

considered. Furthermore, implementation is carried out on an event with an empty resource buffer as well as all events that change the state of the manufacturing line.

More importantly, the second aim is to generate training data used for DNNs. When a lot dispatching decision is required, a DEBS has to extract desired information from various parameters representing the status of RMLs. After all simulations are completed, the extracted information is printed in the form of a vector suitable for the input layer of the DNN.

Finally, KPIs such as waiting time, idle time, WIP level and resource utilization are calculated by a DEBS. The KPI calculations are used to evaluate dispatching results and compare the proposed method with the existing methods. In addition, a DEBS is in charge of generating a text file used as input data of the monitoring tool. The text file contains not only the information needed to illustrate the Gantt chart but also the information captured at the time each dispatching decision being made.

#### 4.1.2 Details of the structure

Fig. 4.1 depicts the overall process of the proposed DEBS, which is a simulator where state changes happen exclusively in discrete instances in time. In other words, not any change in state occurs by the DEBS between two consecutive events [89]. The description of each component of the DEBS is as follows.

## Input

The input of the DEBS includes: (a) resource-related information that contains resource types, the number of resources, and operations that each resource can process;

Figure 4.1: Structure of DEBS (Discrete Event Based Simulator).

(b) job-related information, including job types, the operation sequence of each job type, the number of lots assigned to each job type, and the number of chips in each lot; and (c) physical constraints which determine processing and moving time for lots, the capacity of a resource buffer, and whether pre-emption is allowed.

#### Initialization

Based on the input, the initialization step builds a set of variables for representing the status of a RML and calculating the performance of dispatching decisions. These variables are used to generate vectors for a DNN when a lot dispatching decision is required. Furthermore, this step creates an event list and data structures for the monitoring tool.

Another important role of the initialization step to play is to insert initial events into the event list. As all resource buffers of the RML are empty, multiple lot dispatching decisions are required in this step. After lot dispatching decisions are determined, each event corresponding to each decision is generated and added to the event list.

#### Event loop

An event contains information of the lot and resource related to the event, and timestamp. The timestamp indicates the time when the state changes due to the processing of the event. In addition, the generation of an event leads to the determination of its type. There are six types of events as shown in Fig. 4.1.

An event loop is a loop that is terminated when all events on the event list are exhausted. This loop repeatedly consumes and processes events on the list by

Table 4.1: Descriptions on the event types for the event loop.

| Event                      | Description                                                                           | Generated event                       |

|----------------------------|---------------------------------------------------------------------------------------|---------------------------------------|

| Operation-<br>Finish       | Event triggered when a resource finishes processing a lot                             | Move-To-<br>Stocker-Finish            |

| Empty-Buffer               | Event triggered when a resource buffer is empty                                       | Move-To-<br>Buffer-Finish             |

| Move-To-<br>Buffer-Finish  | Event triggered when a lot arrives at a resource buffer                               | Empty-Buffer,<br>Operation-<br>Finish |

| Move-To-<br>Stocker-Finish | Event triggered when a lot arrives at a DA or WB stocker                              | -                                     |

| Candidate-Lot-<br>Waiting  | Event waiting for candidate lots for a resource with an empty resource buffer         | Move-To-<br>Buffer-Finish             |

| Idle-Resource-<br>Waiting  | Event waiting for a resource to become idle to process the lot in the resource buffer | Empty-Buffer,<br>Operation-<br>Finish |

ascending order of timestamp among the rest. This process executes some code of the DEBS to materialize an appropriate change in state, which is likely to result in the generation of a new event. The details of events are summarized in Table 4.1.

If an Operation-Finish event is selected on the event list, a resource finishes processing a lot and the status of the resource becomes idle. If the lot has remaining operations, a DEBS sends the lot to the stocker for the next operation and generates a Move-To-Stocker-Finish event.

An Empty-Buffer event is an event requiring a lot dispatching decision. When this type of event is triggered, a DEBS creates a list of candidate lots for the resource with an empty resource buffer. If there is no candidate lot for the resource, the DEBS adds a Candidate-Lot-Waiting event whose timestamp is  $\infty$  to the event list. Otherwise, a lot dispatching decision is made via a lot dispatching method.

Once a lot is assigned to an empty resource buffer as a result of the lot dispatching decision, a Move-To-Buffer-Finish event is generated.

When a Move-To-Buffer-Finish event is selected on the event list, a lot arrives at a resource buffer. If the resource is processing the other lot, a DEBS adds an Idle-Resource-Waiting event whose timestamp is  $\infty$  to the event list. Otherwise, the resource starts to process the lot in the resource buffer, which causes Empty-Buffer and Operation-Finish events to be included on the event list.

A Move-To-Stocker-Finish event is triggered when a lot with remaining operations arrives at the stocker for the next operation. This event is different from other types of events in that it changes the state but does not generate a new event.

Since the timestamp of waiting events is  $\infty$ , Candidate-Lot-Waiting and Idle-Resource-Waiting events are not able to be selected in the event loop. Therefore, for each iteration of the event loop, a DEBS performs waiting event processing after any event with a finite timestamp is selected among the four events.

In the waiting event processing, for Candidate-Lot-Waiting events, a DEBS searches for candidate lots of the resource associated with each Candidate-Lot-Waiting event. If there is a candidate lot of any resource, the waiting event of the resource is removed from the event list. Then, a lot dispatching decision is made by a lot dispatching method, and a Move-To-Buffer-Finish event is added to the event list.

Meanwhile, a DEBS checks out the idleness of each resource related to Idle-Resource-Waiting events. If a resource is idle, the lot in the resource buffer starts to be processed by the resource Consequently, Empty-Buffer and Operation-Finish events are to be added to the event list. Then, the Idle-Resource-Waiting event

corresponding to that resource is removed from the event list.

#### KPI and Gantt chart

Once the event list is exhausted, KPIs such as waiting time, idle time, and resource utilization are calculated by a DEBS. Furthermore, the DEBS yields the simulation log containing the entire dispatching history, which is used to generate training datasets for NNs.

For the monitoring tool, DEBS also writes a text file in JSON (JavaScript Object Notation) format, which can be easily parsed in different programming languages [90, 91]. Based on the text file, the monitoring tool illustrates a Gantt chart for the sequence of dispatched lots of each resource. In addition, the text file contains the information of the RML at the time each lot dispatching decision being made.

## 4.2 Monitoring tool

## 4.2.1 Purpose of implementation

Gantt chart is known as a basic schedule representation tool that displays each resource's operational status by changing the color or position of bars [92, 93]. A few studies attempted to extend the basic Gantt chart. Jo et al. [94] proposed a framework containing algorithms to explore the schedule of large-scale manufacturing lines. An interface was also proposed by [95] to deal with specific disruptions in resources and the historical analysis of manufacturing line performance.

Although the previous research successfully improved the basic Gantt chart, their framework has limitations in performing the analysis of dispatching decision units. Therefore, we propose a novel monitoring tool with additional functions needed to monitor KPIs and analyze RTD performances. The purpose of developing the monitoring tool is presented as follows.

One of the most important purposes is to display a variety of information about RMLs at the time each lot dispatching decision being made. The monitoring tool is required to present figures including all alternatives, the amount of WIP, the number of resources in operation. Through examining these values, a user can analyze the reason why the lot dispatching decisions were conducted. The results of the analysis are based on improving the learning framework or the decision making method of the proposed dispatchers.

The second purpose is to illustrate how various performance indicators change over time. Since dispatching decisions occur sequentially, it is important to observe indicators that change in value according to the decisions made. Therefore, the proposed monitoring tool is essential to presenting time-dependent changes in indicators such as the amount of WIP, resource utilization, and the number of lots that complete all operations.

Finally, the monitoring tool is required to be designed to compare multiple dispatching results. As there are a few indicators that represent the performance of dispatching decisions, it is challenging to simply compare and analyze multiple dispatching results. Accordingly, the proposed function provides the ability to compare the performances of multiple RTDs with DNNs learned under different parameters in a single screen.

Figure 4.2: Main screen of the monitoring tool.

### 4.2.2 Details of functions

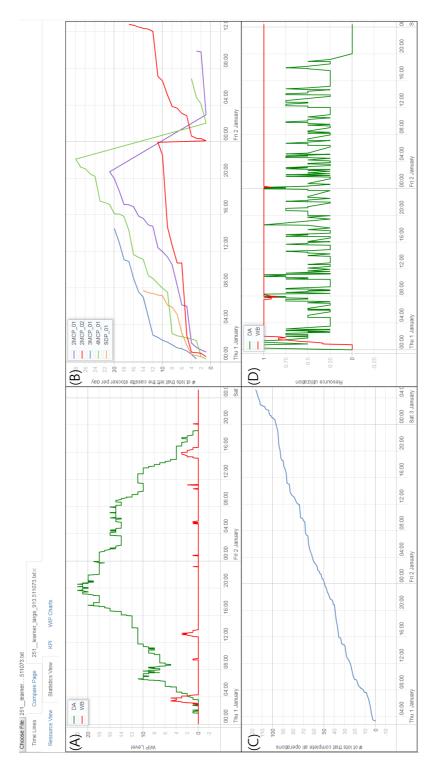

The main screen of the monitoring tool is presented in Fig. 4.2. A user can load a DEBS-generated text file by pushing the 'Choose file' button on the upper left side (A). When a text file is loaded, the 'Time Lines' tab (B) displays several views in the bottom box. The 'Compare Page' (C) shows the performances of multiple dispatching results on a page when text files are additionally loaded.

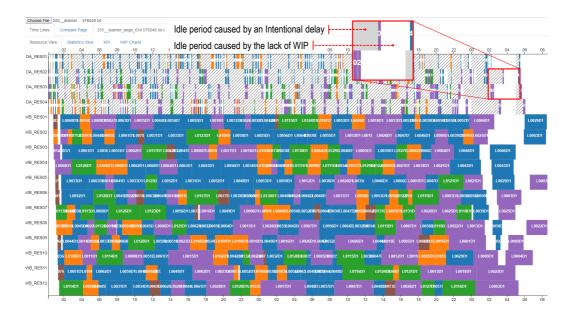

#### Resource view

Fig. 4.3 illustrates the resource view when a text file is loaded with the 'Choose file' button pushed. This view differs from the existing Gantt chart. The idle periods caused by intentional delays are shown differently from those by the lack of WIP. The former is visualized in the form of a rectangle filled with diagonal stripe patterns;

Figure 4.3: Resource view of the monitoring tool.

while the latter is shown in the shape of simple white rectangles.

If a user selects any operation in the resource view, the screen switches to the one shown in the Fig. 4.4. The selected operation is highlighted and surrounded by a red line (A), and only the operations that belong to the lot corresponding to the selected operation are displayed on the screen. The vertical red line (B) signifies the decision time - the time at which the lot dispatching decision corresponding to the selected operation was made.

Furthermore, a pop-up window shows up, elaborating the properties of the lot and resource involved in the lot dispatching decision and the status of the RML at the decision time. Specifically, the first column (C) shows lot-related information such as the number of chips, operation type, and the start and end time of the operation in the resource. The job and resource types of the lot and resource involved in the lot dispatching decision are presented in the second column (D). The last column (E) displays RML-related properties including the amount of WIP, the number of resources in operation, and the number of lots that departed the cassette stocker at the decision time.

Finally, the table at the bottom (F) represents alternatives, including the one chosen as a result of the dispatching decision at the decision time. For each alternative, lot-related information and the scores marked in terms of waiting and idle time are presented. In detail, lot-related information includes the operation type of the lot and the location where the lot stays at the decision time, and the job type of the lot.

Figure 4.4: Decision window of the resource view.

#### Statistics view

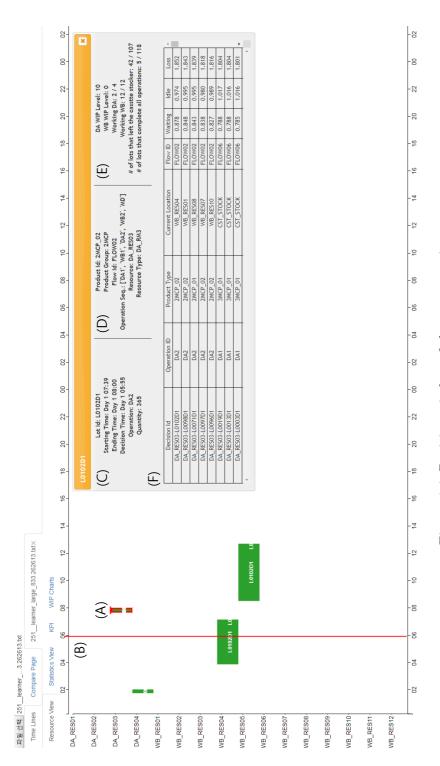

The statistics view illustrates how the four performance indices change over time as shown in Fig. 4.5. The upper left graph (A) shows the amount of WIP for DA and WB stages, which means the numbers of lots in the DA and WB stockers, respectively. The number of lots that departed the cassette stocker per day for each job type is visualized in the upper right graph (B).

The bottom left graph (C) with the increasing trends indicates the number of lots with all operations complete. Finally, the graph on the bottom right represents the resource utilization at each stage. The values in the graph mean the number of resources processing a lot for each stage that is divided by the total number of resources in the corresponding stage.

Figure 4.5: Statistics view of the monitoring tool.

Figure 4.6: KPI view of the monitoring tool.

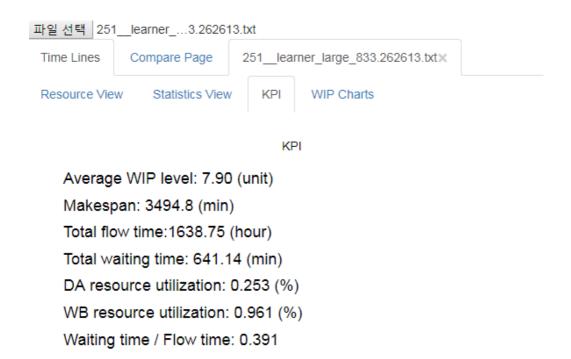

### **KPI** view

As shown in Fig. 4.6, the KPI view shows the performances yielded after all dispatching decisions are completed. Unlike other views of the monitoring tool, this function shows the overall performance rather than time-based changes or information on dispatching decision units.

To be more specific, 'Average WIP level' is calculated as the average of the number of WIPs that are recorded every time that of WIPs changes. 'Total flow time' indicates the sum of the flow time of all lots while 'Total waiting time' means the sum of the waiting time of all lots. Here, waiting time is the sum of the time

that a lot waits in stockers or resource buffers from the start of the first operation to the completion of all operations.

The average utilization rate of resources is calculated separately for each stage. 'DA resource utilization' is calculated as the average of the utilization of DA resources. The utilization of each resource is obtained by dividing the total processing time of the operations assigned to the resource by the dispatching horizon which represents a time period for which the lots necessary for satisfying production requirements are dispatched. Similarly, the value of 'WB resource utilization' is also obtained.

#### WIP charts

Fig. 4.7 visualizes the amount of WIP in more detail than the statistics view does. In WIP charts, the number of graphs represented is twice that of job types which appear on the assembly line. Specifically, a row is generated to illustrate how the amount of WIP for each job type changes over time. The row is divided into two columns, each of which contains a graph.

A graph in the left column (A) shows the amount of WIP for DA and WB stages, which means the number of lots belonging to one job type in the DA and WB stockers, respectively. On the other hand, a graph in the right column (B) indicates the amount of WIP for each operation type, which means the number of lots belonging to the corresponding operation type in stockers.

Figure 4.7: WIP charts of the monitoring tool.

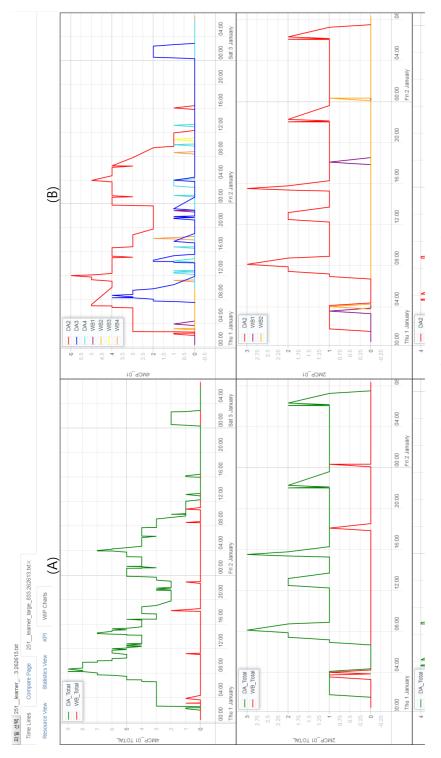

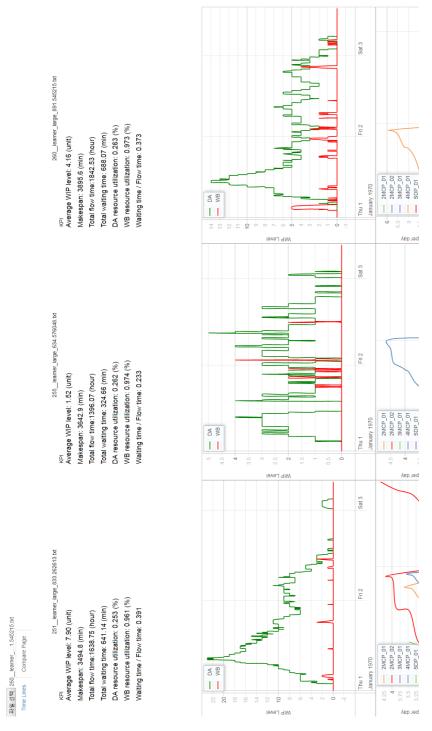

## Compare page

The 'Compare page' is activated when multiple text files are loaded, allowing a user to compare multiple dispatching results on a single screen. As shown in Fig. 4.8, this page lists KPI and statistics views for each text file in the vertical direction, and a column in the same format is added whenever text files are additionally loaded.

Figure 4.8: Comparison page of the monitoring tool.

# Chapter 5

# Deep Neural Network Based Dispatcher

Fig. 5.1 depicts the overall process of the proposed approach. In the training phase, we deploy a simulator that executes the DA and WB stages in MCP production as shown in Fig. 3.1 to generate simulation logs. By utilizing the simulator, all lot dispatching decisions of a problem are determined using a random decision generator (RDG) which is responsible for randomly assigning one of the candidate lots to a DA resource with an empty buffer. The performances of the decisions by RDG are then measured, and the scored simulation logs will be used by a learning algorithm to train the DNNs embedded in RTDs. In the real-time dispatching phase, for a given test problem, the simulator calls the trained dispatcher whenever a lot dispatching decision is required.

In this thesis, we propose two DNN based RTDs with different decision-making processes. The first one is a real-time rule selection dispatcher (RTRD). It determines the best dispatching rule among the existing ones at the time when a lot dispatching decision is required. According to the determined rule, one of the candidate lots is assigned to a DA resource with an empty resource buffer. Secondly, a real-time lot selection dispatcher (RTLD) marks scores for all candidate lots and assigns the lot with the highest score to the DA resource. The details of RTDs are described in the

following sections.

Figure 5.1: Overall structure of the proposed approach.

## 5.1 Real-time rule selection dispatcher

## 5.1.1 Dispatcher structure

Fig. 5.2 illustrates the architecture of RTRD which consists of five layers: an input layer, three hidden layers, and an output layer. The input layer contains 37 nodes, and the number of nodes in each hidden layer are 64, 32, and 16, respectively, whereas the output layer has one node. The numbers of hidden layers and nodes in the hidden layers are empirically determined to reduce the training error. The rectified linear unit (ReLU), f(z) = max(0, z), is applied before each hidden layer in order to provide a non-linear transformation, and all layers are fully connected [96].

Figure 5.2: The structure of RTRD.

The input layer can be divided into two groups: state and action vectors. The former describes the status of an MCP assembly line when a particular DA resource,

$R_{q,s}$ , has an empty resource buffer, while the latter indicates the dispatching rule used to select the lot to be assigned to  $R_{q,s}$ . We propose the components of the state vector, and then introduce dispatching rules for the action vector.

Table 5.1 presents the details of the state vector for  $R_{q,s}$ . From the state vector, a RTRD is capable of capturing the characteristics of candidate lots and the flow of lots in the assembly line. This is the basis on which the RTRD determines dispatching rules for  $R_{q,s}$ . Specifically, the state vector contains 26 features that are categorized into DA resource, statistics of candidate lots, and the distribution of lots as shown in Table 5.1. First, a single feature associated with  $R_{q,s}$  indicates how much time remains until  $R_{q,s}$  becomes idle.

Next, the 12 features associated with candidate lots represent the minimum, maximum, and average values of the four attributes that each lot has. The four attributes are: the time when the lot departed the cassette stocker, the number of chips in the lot, the number of the remaining operations to be processed, and the processing time on  $R_{q,s}$ . Other attributes of the lot were excluded since they are not related to the performance measures that are considered in this thesis. RTRD utilizes the statistics of all candidate lots rather than the characteristics of each one because RTRD is not able to specify the lot to be assigned to  $R_{q,s}$  until the dispatching rule is determined, which differentiates RTRD from RTLD.

Finally, each feature belonging to the lot distribution includes the number of lots that correspond to one of the 13 different locations, covering all areas where a lot can exist in assembly lines. With these features, the proposed dispatcher knows not only the distribution of lots in the assembly line, but also the progress of the overall processes.

Table 5.1: Components of the state vector for  $R_{q,s}$  of RTRD.

| Categories                   | Descriptions                                                           |

|------------------------------|------------------------------------------------------------------------|

| DA resource                  | The time remaining until $R_{q,s}$ becomes idle                        |

|                              | Earliest time when lots depart the cassette stocker                    |

|                              | Latest time when lots depart the cassette stocker                      |

|                              | Average time when lots depart the cassette stocker                     |

| Statistics of candidate lots | Minimum number of chips in lots                                        |

|                              | Maximum number of chips in lots                                        |

|                              | Average number of chips in lots                                        |

|                              | Minimum number of remaining operations assigned to lots                |

|                              | Maximum number of remaining operations assigned to lots                |

|                              | Average number of remaining operations assigned to lots                |

|                              | Minimum processing time of lots on $R_{q,s}$                           |

|                              | Maximum processing time of lots on $R_{q,s}$                           |

|                              | Average processing time of lots on $R_{q,s}$                           |

|                              | # of lots in the cassette stocker                                      |

|                              | # of lots being moved from the cassette stocker to DA resource buffers |

| Lot<br>distribution          | # of lots in DA resource buffers                                       |

|                              | # of lots being processed on DA resources                              |

|                              | # of lots being moved from WB stocker to WB resource buffers           |

|                              | # of lots in WB resource buffers                                       |

|                              | # of lots being processed on WB resources                              |

|                              | # of lots being moved from WB resources to the DA stocker              |

|                              | # of lots in the DA stocker                                            |

|                              | # of lots being moved from the DA stocker to DA resource buffers       |

|                              | # of lots being moved from DA resources to the WB stocker              |

|                              | # of lots in the WB stocker                                            |

|                              | # of lots that completed all operations                                |

Table 5.2 summarizes dispatching rules used to generate the action vector for  $R_{q,s}$ , and the manners in which each rule chooses one of candidate lots. Each rule was modified to be used in the assembly line considered. Among the existing dispatching rules, we chose the ones that affect the waiting time of lots and the utilization of resource [62, 97]. STOCKER is a rule developed in this thesis according to the assembly line considered herein.