Ph.D. Dissertation

# Design of Injection-Locked PLL and CDR with Circuit Techniques for Optimum Operation

최적 작동을 위한 주입 고정 위상 동기화 루프와 클럭 및 데이터 복구 회로 기술에 대한 연구

by

**Min-Seong Choo**

February, 2019

Department of Electrical Engineering and Computer Science College of Engineering Seoul National University

# Design of Injection-Locked PLL and CDR with Circuit Techniques for Optimum Operation

지도 교수 정 덕 균

이 논문을 공학박사 학위논문으로 제출함 2019 년 2 월

> 서울대학교 대학원 전기·컴퓨터 공학부 추 민 성

추민성의 공학박사 학위논문을 인준함 2019 년 2 월

| 위  | 원장_  | 김 재 하 | (인) |

|----|------|-------|-----|

| 부위 | 원장 _ | 정 덕 균 | (인) |

| 위  | 원_   | 전 동 석 | (인) |

| 위  | 원_   | 문 용 삼 | (인) |

| 위  | 원    | 전 정 훈 | (인) |

# Design of Injection-Locked PLL and CDR with Circuit Techniques for Optimum Operation

by

Min-Seong Choo

A Dissertation Submitted to the Department of Electrical Engineering and Computer Science in Partial Fulfillment of the Requirements for the Degree of Doctor of Philosophy

at

SEOUL NATIONAL UNIVERSITY February, 2019

Committee in Charge:

Professor Jaeha Kim, Chairman

Professor Deog-Kyoon Jeong, Vice-Chairman

Professor Dongsuk Jeon, Member

Professor Yongsam Moon, Member

Professor Jung-Hoon Chun, Member

### Abstract

Innovative injection-locking techniques for a high-speed serial link are proposed in both transmitter and receiver. Superior jitter performance is achieved using directly injecting the edge of the input signal to the oscillator. However, a frequency mismatch between the reference input and the local oscillator should be precisely adjusted to deliver the desired operation behavior. Besides, the injection strength should be chosen as a maximal value to achieve a wide bandwidth of the overall structure.

Firstly, a path-mismatch issue in the injection-locked phase-locked loop (ILPLL) is resolved by using a half-edge injection and deserialization of error information in the bang-bang phase and frequency detector (BBPFD). The injection timing is continuously tracked, and the frequency error between the reference clock and the local oscillator vanishes. The timing calibrator enables a robust ILPLL operation over the process, voltage, and temperature (PVT) variations. The proposed ILPLL consumes 5.65 mW at 5 GHz with 0.9-V supply voltage. The measured jitter integrated from 1 kHz to 40 MHz is 152 fs, and the spur levels at the reference and second subharmonic are –62 dBc and –53 dBc, respectively.

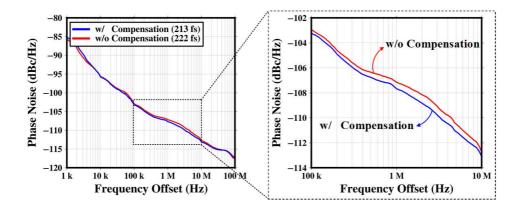

Secondly, to achieve a maximum bandwidth of the ILPLL, a technique that increases the injection strength as large as possible is proposed. Also, a phase domain response (PDR) of the injection-locked oscillator (ILO) is analyzed and re-derived for the physically implemented circuits. By doing so, more accurate PDR is obtained, and the optimal locking point is found. Thanks to the modification of the PDR and the exclusion of the pulse generator, this work achieves a minimum reference spur and integrated jitter in both at the 15-GHz clock. The proposed ILPLL shows integrated jitter from 1 kHz to 40 MHz of 213 fs while achieving a power consumption of 17.81 mW at a clock rate of 15 GHz.

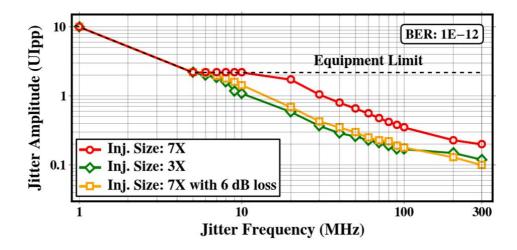

Third, the injection-locking technique is applied to a clock and data recovery (CDR) circuit. To widen the bandwidth of the jitter tolerance (JTOL), directly modulating the phase of the local oscillator is adopted using a rising-edge injection method. Also, similar to an ILPLL structure, a path mismatch between the injection path and the feedback system is compensated using the proposed tracking loop. Just modifying the conventional phase detection logic, 2X oversampling, the path mismatch is detected and eliminated to operate in the desired operating condition. The timing margin of the sampler is maximized thanks to the proposed tracking loop, and it satisfies the bit error rate less than 10<sup>-12</sup> as 1-UIpp amplitude at the sinusoidal jitter frequency of 31 MHz. Also, the proposed ILCDR achieves the highest energy efficiency of 1.28 pJ/bit among the fully functional ILCDR chips published in the literature.

**Keywords:** All-digital phase-locked loop (ADPLL), injection-locked oscillator (ILO), injection-locked PLL (ILPLL), injection-locked CDR (ILCDR), injection-timing tracking, phase domain response (PDR)

Student Number: 2012-20878

## Contents

| Abstracts                                                 | i   |

|-----------------------------------------------------------|-----|

| Contents                                                  | iii |

| List of Tables                                            | vi  |

| List of Figures                                           | vii |

| Chapter 1 Introduction                                    | 1   |

| 1.1 Motivation                                            | 1   |

| 1.2 Thesis Organization                                   | 4   |

| Chapter 2 Background on Injection-Locked Oscillator (ILO) | 5   |

| 2.1 Injection-Locking Phenomenon                          | 5   |

| 2.2 Applications                                          | 8   |

| 2.2.1 Clock Multiplication                                | 8   |

| 2.2.2 Clock Recovery                                      | 10  |

| 2.2.3 Clock Divider                                       | 11  |

| 2.2.4 Clock Distribution                                  | 12  |

| 2.2.5 Clock Deskewing                                     | 13  |

| 2.3 Basic Analysis for ILO                                | 14  |

| 2.3.1 Adler's Equation                                    | 14  |

| 2.3.2 Phase Noise Analysis                                | 22  |

| 2.4 Design Challenges                                     | 27  |

| 2.5 Recent Works                                          | 28  |

| 2.5.1 Clock Multiplication                                | 28  |

| 2.5.2 Clock Recovery                                      |     |

| Chapter 3 ILPLL with Injection-Timing Tracking 3               | 52        |

|----------------------------------------------------------------|-----------|

| 3.1 Overview                                                   | 2         |

| 3.2 Analysis of Injection-Timing Effect                        | 5         |

| 3.2.1 Frequency Error by Injection-Timing Mismatch in ILPLL3   | \$5       |

| 3.2.2 Deterministic Noise for Injection Timing                 | ;9        |

| 3.3 Proposed ILPLL with Optimum Injection Timing4              | .3        |

| 3.3.1 Half-Edge Injection and Detecting Injection Timing4      | 13        |

| 3.3.2 Overall Architecture and Operation Principle4            | 15        |

| 3.4 Measurements                                               | 7         |

| 3.4.1 Noise Suppression using Injection and Timing Calibrator4 | 18        |

| 3.4.2 Verification of Timing Calibrator with Variations5       | 50        |

| 3.4.3 Performance Summary and Comparison5                      | 52        |

| Chapter 4 ILPLL with Maximum Injection Strength 5              | 54        |

| 4.1 Overview                                                   | 4         |

| 4.2 Previous Analyses of PDR                                   | 7         |

| 4.2.1 Impulse Injection                                        | 58        |

| 4.2.2 Pulse Injection6                                         | 58        |

| 4.3 Parallel Translation of PDR6                               | 5         |

| 4.4 Circuit Implementation                                     | 8         |

| 4.4.1 Proposed ILO6                                            | 58        |

| 4.4.2 Overall Architecture of ILPLL7                           | 0'        |

| 4.5 Measurements7                                              | 1         |

| Chapter 5. ILCDR with Maximum Timing-Margin Tracking 7         | 6         |

| 5.1 Overview                                                   | 6         |

| 5.2 Proposed ILCDR with Maximum Timing Margin7                 | '9        |

| 5.2.1 Overall Architecture and Operation Principle7            | <u>'9</u> |

| 5.2.2 Rising-Edge Injection and Detecting Injection Timing     | 32        |

| 5.3 Proposed ILO                                               | 34        |

| 5.4 Measurements                                               | 5         |

| Chapter 6 Conclusion 9                                         | )1        |

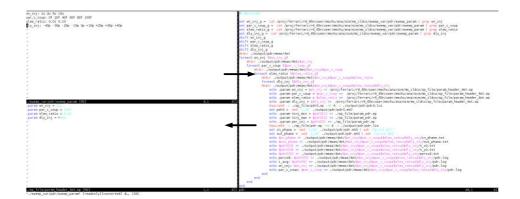

| Appendix A PDR Simulation Deck using HSPICE             | 93  |

|---------------------------------------------------------|-----|

| Appendix B Measurement Automation using Python Language | 96  |

| Bibliography                                            | 100 |

| 국문 초록                                                   | 106 |

## **List of Tables**

| Table 3.1 Performance Summary and Comparison | 53 |

|----------------------------------------------|----|

| Table 4.1 Performance Summary and Comparison | 75 |

| Table 5.1 Performance Summary and Comparison | 90 |

# **List of Figures**

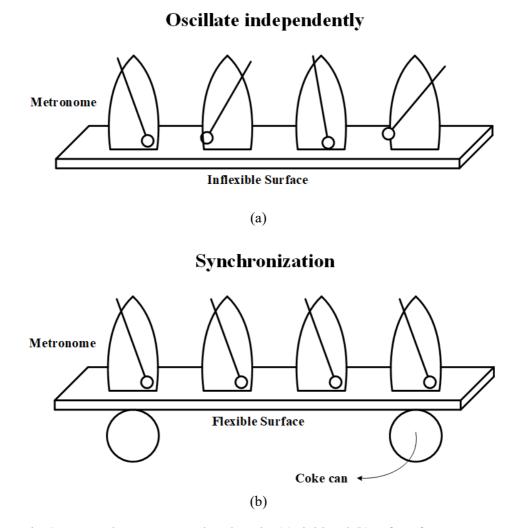

| Fig. 2.1 Several metronomes placed on the (a) rigid and (b) soft surface.        |

|----------------------------------------------------------------------------------|

|                                                                                  |

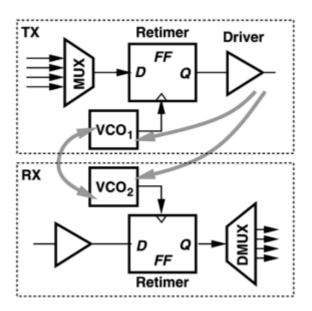

| Fig. 2.2 An example of injection pulling in broadband transceiver reported in    |

| [16]                                                                             |

| Fig. 2.3 An example of the injection-locked oscillator in clock multiplication   |

| and its conceptual timing diagram9                                               |

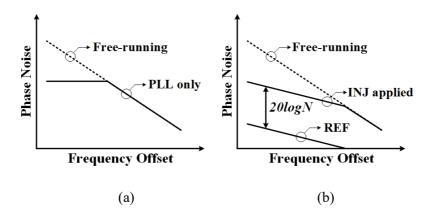

| Fig. 2.4 Phase noise curves of (a) PLL only and (b) injection-applied clock      |

| multiplications9                                                                 |

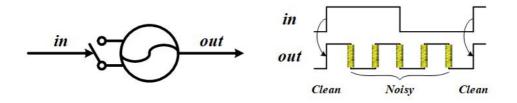

| Fig. 2.5 An example of the clock and data recovery from the input data stream    |

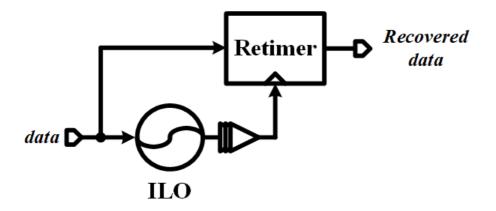

| using an injection-locked oscillator10                                           |

| Fig. 2.6 An example of the injection-locked frequency divider in the             |

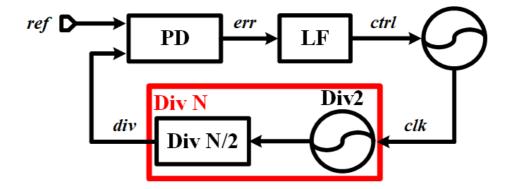

| application of the PLL11                                                         |

| Fig. 2.7 An example of the clock distribution using an injection-locked          |

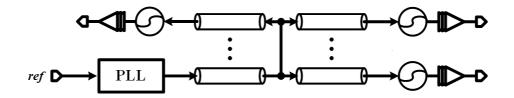

| oscillator                                                                       |

| Fig. 2.8 An example of the injection-locked oscillator as a delay element in a   |

| source synchronous clock recovery structure13                                    |

| Fig. 2.9 Oscillator circuit developed in [7] with signal descriptions14          |

| Fig. 2.10 A description of the injection-locking using rotating phasor diagram   |

| when the injection (a) starts, (b) is tracking, and (c) captures the             |

| original signal entirely while the frequency deviation is zero.                  |

|                                                                                  |

| Fig. 2.11 Magnitude and phase versus angular frequency illustrating off-         |

| resonant frequency [16]17                                                        |

| Fig. 2.12 Various output results of equation (2.18) with different initial phase |

| shifts while the frequency offset is zero20                                      |

| Fig. 2.13 General output-phase-shift results with various initial phase shifts |

|--------------------------------------------------------------------------------|

| when (a) injection locked and (b) injection pulling21                          |

| Fig. 2.14 Timing diagram before and after the injection affect the original    |

| clock edge reported in [14]22                                                  |

| Fig. 2.15 The extra phase shift due to the injection operation (a) shown using |

| the series phase steps and (b) impulse train employing hold operation          |

| reported in [14]23                                                             |

| Fig. 2.16 Phase noise model of the injection-locked PLL including the effect   |

| of the realignment and the up-conversion of the reference noise                |

| reported in [14]25                                                             |

| Fig. 2.17 Noise transfer function of (a) the reference and (b) the oscillator  |

| with various realignment factor                                                |

| Fig. 2.18 Effect of realignment factor on phase noise when the reference noise |

| is zero with different realignment factor26                                    |

| Fig. 2.19 An example of the clock multiplication when the frequency            |

| deviation exists reported in [28]27                                            |

| Fig. 2.20 (a) The concept of the pulse gating and (b) the timing diagram when  |

| the multiplication factor is four, and the gating rate is one fourth in        |

| [28]28                                                                         |

| Fig. 2.21 Block diagram of the replica-delay scheme and its timing diagram     |

| adjusting the frequency of the oscillator and path mismatch between            |

| the replica cells reported in [30]29                                           |

| Fig. 2.22 Block diagram of the replica-based ILCDR with reference PLL          |

| published in [39]                                                              |

| Fig. 2.23 An implementation example of the injection-locked clock and data     |

| recovery using the serial output of the phase detector to distinguish          |

| the error source [43]31                                                        |

| Fig. 3.1 The trend of the figure of merit (FoM) versus frequency by choice of  |

Fig. 3.2 Block diagram of conventional ILPLL with delay elements. ......35

- Fig. 3.4 (a) Deterministic jitter and (b) reference spur calculated from the equations of (2) and (3) as a function of injection-timing mismatch  $(\Delta t)$  for two different injection strengths ( $\beta = 0.1$  and  $\beta = 0.3$ ) in conventional ILPLL. In this example, N = 16 and  $f_{ref} = 312.5$  MHz.

- Fig. 3.5 (a) Behavioral phase-noise simulations of ILPLL when injection timing is perfectly tuned and (b) calculated jitter as a function of injection strength. In this example, N = 16,  $f_{ref} = 312.5$  MHz, the phase noise of an oscillator is -95 dBc/Hz at 1-MHz offset excluding flicker noise, and phase noise of reference clock is modeled as having a Gaussian random noise of -160 dBc......41 Fig. 3.6 The conceptual timing diagram of the half-edge injection with pro

- posed tracking loop disabled when multiplication factor (N) is 4.

| TT |

|----|

|----|

Fig. 3.7 Block diagram of the digital loop filter......44

Fig. 3.8 Block diagram of the proposed ILPLL. ......45

Fig. 3.9 Flowchart of the proposed ILPLL......46

- Fig. 3.11 Measured phase-noise curves of the output clock......48

- Fig. 3.12 Measured spectrums of the output clock......49

| Fig. 3.14 Measured (a) reference spur and (b) integrated jitter with and                 |

|------------------------------------------------------------------------------------------|

| without timing calibrator as a function of the normalized initial delay                  |

| control word51                                                                           |

| Fig. 4.1 (a) Conventional injection-locked oscillator (ILO) with a pulse                 |

| generator and its timing diagram. (b) Symmetric [25] and (c)                             |

| asymmetric [28] phase domain response (PDR) analyses55                                   |

| Fig. 4.2 Simplified half circuit of an LC oscillator with an injection N-type            |

| MOSFET [25]                                                                              |

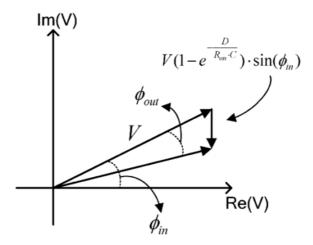

| Fig. 4.3 Voltage phasor diagram when an LC oscillator is injected during the             |

| period of <i>D</i> [25]                                                                  |

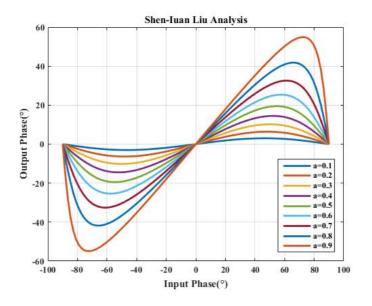

| Fig. 4.4 Transfer curve of equation (4.3) with different injection strength from         |

| 0.1 to 0.9                                                                               |

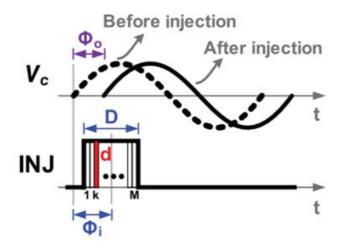

| Fig. 4.5 Timing diagram of the ILO in LC oscillator considering the pulse                |

| width of D divided into infinitesimally small impulse pulses [28].                       |

|                                                                                          |

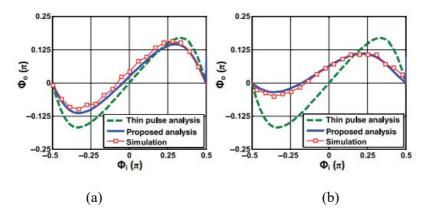

| Fig. 4.6 PDR analysis and simulation results in case (a) $R_{sw} = 20 \Omega$ , $D = 20$ |

| ps; (b) $R_{sw} = 40 \Omega$ , $D = 40$ ps in [28]64                                     |

| Fig. 4.7 Block diagram of the ILO with (a) ideal supply voltage, (b) physical            |

| circuit implemented, and (c) proposed scheme65                                           |

| Fig. 4.8 (a) Timing diagram and (b) phase domain response (PDR) when                     |

| voltage drop through the control circuit is considered                                   |

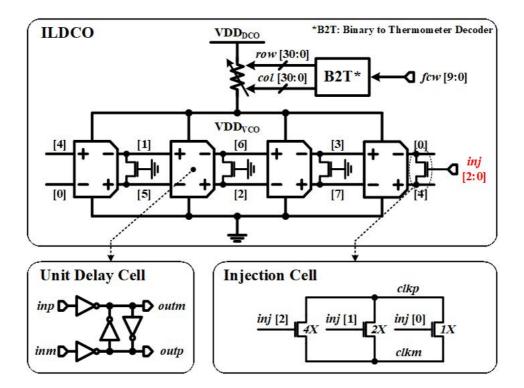

| Fig. 4.9 Block diagram of the proposed ILDCO.                                            |

| Fig. 4.10 (a) Block diagram of the proposed ILDCO and the simulated phase                |

| domain response (PDR) with different (a) injection duration and (b)                      |

| compensation switch size69                                                               |

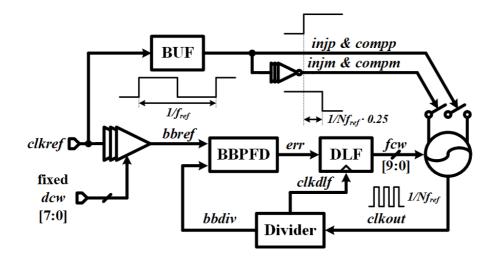

| Fig. 4.11 The overall architecture of the injection-locked PLL (ILPLL)70                 |

| Fig. 4.12 (a) Chip photomicrograph, (b) block description, and separated                 |

| rig. 4.12 (a) Chip photoinicrograph, (b) block description, and separated                |

power consumption at 15-GHz with a 1.3-V supply voltage. ......71

| Fig. 4.13 Measured integrated jitter and reference spur of ILPLL (a) without     |

|----------------------------------------------------------------------------------|

| and (b) with compensation switches in the ILDCO72                                |

| Fig. 4.14 Measured phase noise curves with and without compensation              |

| switches when the reference spur level shows the lowest value73                  |

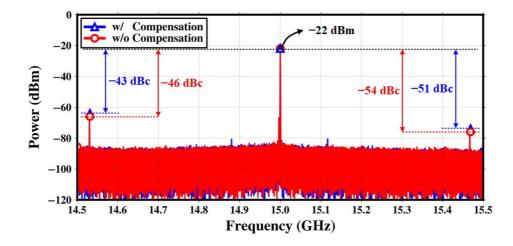

| Fig. 4.15 Measured spectrums with and without compensation switches when         |

| the reference spur level shows the lowest value74                                |

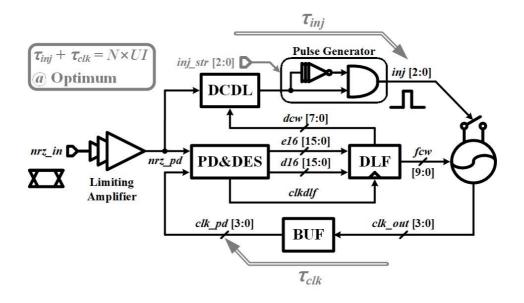

| Fig. 5.1 Block diagram of the proposed ILCDR79                                   |

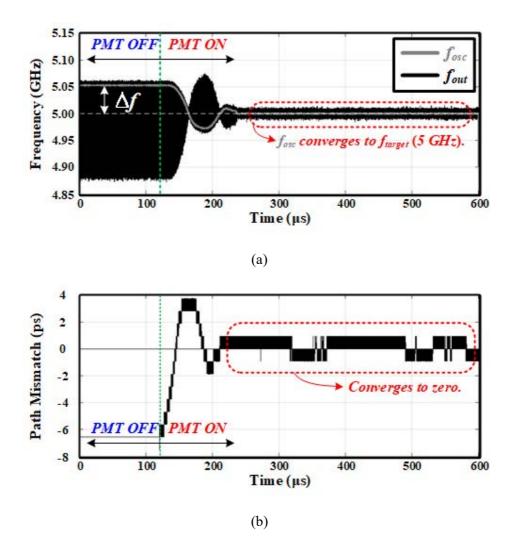

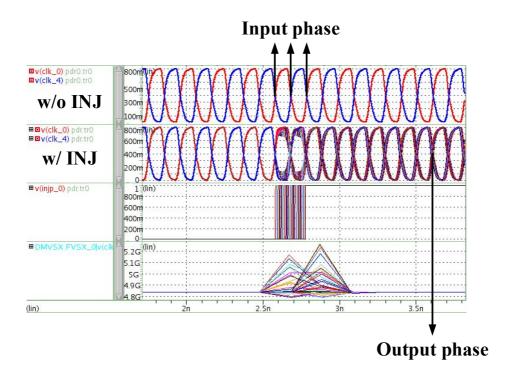

| Fig. 5.2 Behavioral transient simulations of the proposed ILCDR. (a)             |

| Frequency versus time. (b) Path mismatch versus time. In this                    |

| example, injection strength ( $\beta$ ) is 0.8, and initial path mismatch is set |

| to -6.56 ps with 10-Gb/s, 2 <sup>7</sup> -1 PRBS input data pattern              |

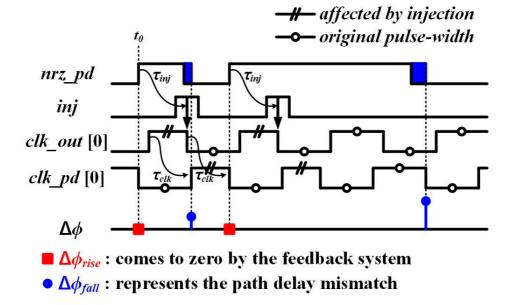

| Fig. 5.3 Conceptual timing diagram under path delay mismatch when the            |

| PMT loop is disabled82                                                           |

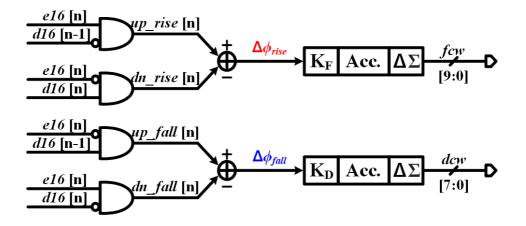

| Fig. 5.4 Block diagram of the proposed phase detector in the digital loop filter |

| that detects the path mismatch                                                   |

| Fig. 5.5 Block diagram of the proposed phase detector in the digital loop filter |

| that detects the path mismatch                                                   |

| Fig. 5.6 Chip photomicrograph, block description, and separated power            |

| consumption at 10 Gb/s with a 0.9-V supply voltage                               |

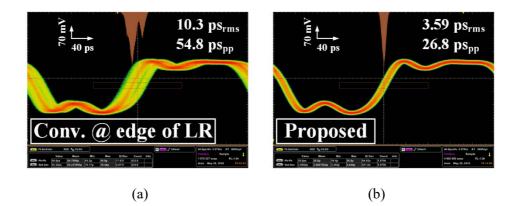

| Fig. 5.7 Measured jitter histograms of the 2.5-GHz recovered clock for (a) the   |

| conventional PLL-based ILCDR at the edge of the locking range and                |

| (b) the proposed ILCDR, satisfying the bit error rate less than $10^{-12}$ .     |

|                                                                                  |

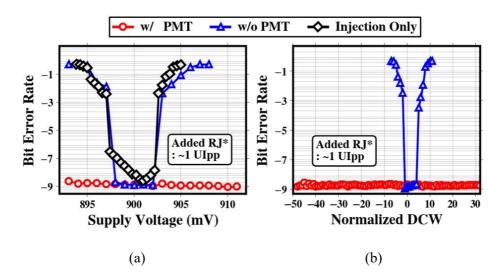

| Fig. 5.8 Measured bit error rate at 10 Gb/s with several different ILCDR with    |

| various (a) supply voltage and (b) delay control words. In this test, the        |

| random jitter of about 1 UIpp is intentionally added for degradation             |

|                                                                                  |

| of bit error rate                                                                |

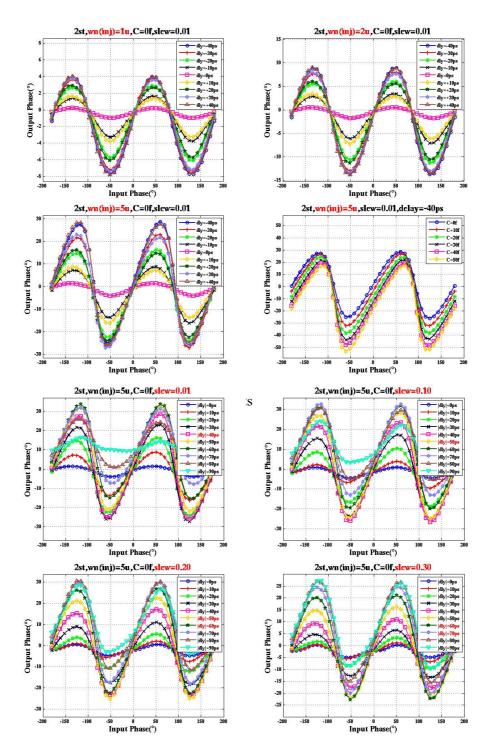

| Fig. A.1 PDR example in transient simulation94                       |

|----------------------------------------------------------------------|

| Fig. A.2 PDR-simulation procedure using TCSH language94              |

| Fig. A.3 Various PDR simulation results95                            |

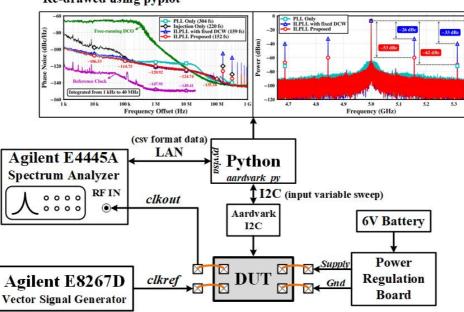

| Fig. B.1 An example of measurement automation using python           |

| Fig. B.2 An example of main test bench using python                  |

| Fig. B.3 An example with (a) output command while one measurement is |

| done and (b) saved data after several measurements are performed.    |

|                                                                      |

### **Chapter 1**

### Introduction

#### **1.1 Motivation**

With the continuous advance of the CMOS fabrication process, the complexity of very-large-scale integration (VLSI) has been increased. To embed much more functions and achieve higher controllability, a portion of the digital blocks in the entire system has been significant and increasing complexity of digital blocks makes timing budgets harsher. Therefore, for following a rapidly changing system and securing large timing margin, system clocks which have a higher bandwidth and lower jitter is required in numerous applications. Among some previously reported schemes, a methodology that utilizes an injection-locked oscillator (ILO) is a promising candidate to achieve them. Thus, this dissertation presents novel studies on an ILO-based phase-locked loop (PLL) and a clock data recovery (CDR) circuits.

1

ILOs have widely been adopted in many wireline transceivers since they make it possible to improve jitter performance, power consumption, and hardware size [23]–[34], [37]–[43], and [47]–[63]. Fundamentally, phase information in ILO is directly modified by the input injecting signal. Thus, available bandwidth employing ILO is relatively very high compared with the feedback-type applications such as PLL. Since the bandwidth of the overall system determines the amount of the noise suppression of the oscillator, as the system bandwidth increases, the jitter performance improves. More specifically, injection-locked phase locked loop circuits (ILPLLs), and data recovery circuits (ILCDRs) shows excellent jitter performance and low power consumption with minimal additive hardware in comparison to the conventional structures. Typically, to achieve a superior jitter tolerance (JTOL) performance in the conventional PLL or phase interpolator (PI) based CDRs, large power consumption should be required for better phase noise of the oscillator and the higher sensitivity of the sampler. However, an ILO has a large bandwidth because it directly forwards the transition of data to the local oscillator. In other words, an ILO tracks the phase of the input data stream rapidly, which results in higher JTOL performance.

Despite these advantages of the ILO-based systems, there are some issues have to be solved. In the case of ILPLLs, a robust operation is not ensured unless the injection timing is precisely controlled. Since the reference clock is directed to a phase detector, and at the same time injected into the oscillator, the two paths must be designed carefully since the phase of the oscillator might have already been adjusted by the injection before the phase detector catches the phase error, nullifying the operation of the PLL or vice versa. To resolve the timing issue in conventional ILPLLs, several calibration methods have been reported in [23]–[30], [33], and [34]. In the case of ILCDR, the main issue to be resolved is a frequency offset between the input data stream and the local oscillator. When the offset is not eliminated, the timing margin of the receiver is reduced significantly. Thus, the reduced timing margin causes a bit error when consecutive identical digits show up. Besides, if the offset exceeds the locking range of an ILO, it could fail to lock. For these reasons, to employ an ILO in CDR applications, a timing calibrator that cancels out the offset is necessary for robust operation over the process, supply voltage, temperature (PVT) variations.

In this dissertation, researches on novel ILPLL and ILCDR are presented, proposing the circuit techniques solving the design challenges as mentioned above. In addition, all ILOs are designed based on the ring oscillator (RO) to get a better tuning range and small silicon area. Conventionally, since the ring oscillators exhibit poor phase noise performance compared with LC oscillators, RO-based PLL shows worse jitter performance though it has some merits. However, since the injectionlocking technique can improve inherently poor jitter performance of the ring oscillators, RO-based ILOs have widely been researched in many clocking systems thanks to their remarkable jitter performance and simple implementation.

### **1.2 Thesis Organization**

The remaining chapters in this thesis are organized as follows. In chapter 2, we provide sufficient background of injection-locking techniques and then design examples are introduced for many applications.

In Chapter 3, an injection-timing effect in a conventional injection-locked phase-locked loop (ILPLL) is analyzed, and the timing tracking loop is proposed using a simple technique omitting injection signal every other cycle to achieve a superior jitter performance in the ILPLL structure.

In Chapter 4, a phase domain response (PDR) of the injection-locked oscillator (ILO) is presented in physically implemented circuits that are different from the previous analysis. Using the simple observation, the overall characteristic of the PDR is modified to exhibit an excellent jitter performance.

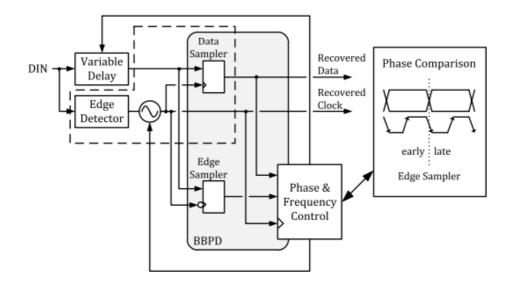

In Chapter 5, a half-rate all-digital injection-locked clock and data recovery (ILCDR) with maximum timing-margin tracking loop are proposed. Simply adjusting the phase detection scheme embedded in the digital loop filter, the path mismatch in the conventional ILCDR is continuously detected and compensated.

Chapter 6 summarizes the proposed works and concludes this dissertation.

### **Chapter 2**

## **Background on Injection-Locked Oscillator (ILO)**

### 2.1 Injection-Locking Phenomenon

Injection locking is a physical phenomenon that can occur when an oscillator interferes with another clocking source at the very close frequency. If the coupling strength is strong enough and the two frequencies are almost the same, the input signal can capture the original clocking source. There are several natural examples illustrating injection locking: pendulum clocks on the same walls and synchronization of the metronomes on the flexible material as illustrated in Fig. 2.1 [1]–[2]. In this example, the four metronomes have almost the same oscillation frequency; they could have slightly different frequency due to the manufactory mismatch. At first, individual metronomes are initiated by hand; they have different

Fig. 2.1 Several metronomes placed on the (a) rigid and (b) soft surface.

phase and frequency as shown in Fig. 2.1(a). After the initialization, the rigid material is replaced to the flexible one using the coke can under the plate as illustrated in Fig. 2.1(b). Since the surface in Fig. 2.1(b) is versatile, the metronomes start to communicate with each other. After some time, they finally achieve the synchronized state, showing same phase and frequency.

Fig. 2.2 An example of injection pulling in broadband transceiver reported in [16].

These situations could be performed on purpose like Fig. 2.1(b), or it could happen in an unwanted manner as shown in Fig. 2.2. If it occurred in an unintended way, it is regarded as a noise source. Thus, we have to eliminate the coupling effect between the signals consuming considerable cost. However, if the injection effect is performed in helpful or smart ways, that is, deliberately designed, we could achieve the desired performance (e.g., synchronization) at a relatively low cost.

### **2.2 Applications**

Injection-locking technique has widely been exploited in many applications in the frequency synthesis related works. For instance, it is designed for high-performance clock multiplication [23]–[34], clock recovery for burst-mode operation [37]– [43], high-speed clock division [46]–[51], clock distribution for long-distance buffering [52]–[57], and even the delay elements [58]–[63].

#### 2.2.1 Clock Multiplication

In the clock multiplication, injection-locked oscillators (ILOs) have been good alternatives of the conventional PLLs in the aspect of significant noise suppression. Because of its refreshment of the accumulated noise inherent in the noisy clock as shown in Fig. 2.3, it offers excellent noise performance in comparison to the conventional phase-locked loops especially in case of employing the ring oscillator. Another example of the multiplication of the clock is used in RF application which should synthesize the ultra-high-speed clock over tens of gigahertz. In this type of application, the primary goal of the design is to achieve the frequency, not for the stable operation, thus, minimizing the control circuits which might reduce the operating frequency, it can operate at an ultra-high speed such as over ten gigahertz.

Fig. 2.3 An example of the injection-locked oscillator in clock multiplication and its conceptual timing diagram.

Fig. 2.4 Phase noise curves of (a) PLL only and (b) injection-applied clock multiplications.

As shown in the Fig. 2.4(a), when the conventional PLL is utilized to synthesize clock, the jitter performance is determined by the loop bandwidth; usually, maximum feasible bandwidth is restricted to one-tenth of the frequency of the reference clock. Thus, the phase noise of the local oscillator should be designed having excellent phase noise, consuming large power dissipation. On the other hand, when the injection operation is applied to the local oscillator, as shown in Fig. 2.4(b), it follows the noise floor of the reference clock below the bandwidth, and the available bandwidth is much wider than the clock multiplication employing the PLL structure only. For this reason, carefully crafted an ILO-based clock synthesizer is a fascinating option concerning both the jitter performance and power consumption.

#### 2.2.2 Clock Recovery

In the embedded clock recovery system, PLL-based CDR is widely adopted for its stable and straightforward implementation. However, PLL-based CDR exhibits very low JTOL in an aspect of the bandwidth due to their loop filter inside the loop. In other words, generally, it cannot tolerate at the very high frequency of the input jitter over tens of the megahertz. For this reason, the method of enhancing the loop bandwidth is developed using a gated voltage-controlled oscillator (GVCO) or ILO applied structure. Thanks to its inherent feature that replace the original edges with the input signal, it naturally achieves a wider bandwidth compared with the PLLbased structures. An ILO-based CDR is adequate for the burst-mode applications or passive optical network (PON) to satisfy the instantaneous phase-locking criteria.

Fig. 2.5 An example of the clock and data recovery from the input data stream using an injection-locked oscillator.

#### 2.2.3 Clock Divider

In the applications that should synthesize very high frequency such as tens of gigahertz, typical methods to divide the oscillation clock is not adequate for a specific technology. Mostly, flip-flop based divider is commonly employed at the front of the division in the PLL application. Because of its internal delay of the flip-flop, it is challenging to achieve higher bandwidth without any help of the circuit techniques. Moreover, even if the internal delay is reduced with specific skills, their power consumption matters in low-power mobile design. For this reason, ILOs are established and implemented in the high-frequency clock synthesizers. The primary design goal in the clock divider using ILO is to secure wide locking range nullifying the compensation circuits for simple design and speed limitation while consuming less power consumption.

Fig. 2.6 An example of the injection-locked frequency divider in the application of the PLL.

#### 2.2.4 Clock Distribution

In a typical design of the microprocessors and other high-speed applications, clock distribution is one of the challenging missions because of their considerable power consumption and clocking noise. Distributing a clock source from one point to the multiple points is very bothering, and if their arrival time should be almost identical for the timing issue, it is very tough to make it; in a conventional buffered structure such as H-tree, careful design in the layout should be followed. To mitigate the drawbacks in the traditional buffering strategy, ILOs are introduced and applied as shown in Fig. 2.7. If the ILOs are successfully transmitting the clock source just using the metal wires, there is little overhead for the circuit design, and power dissipation is minimized. When the oscillator is deliberately designed in the LC-tuned tank considering the parasitic capacitance of the global network, it could be a great solution that can secure less power dissipation, and high-quality clock, while the skew of the each received local clock is well matched.

Fig. 2.7 An example of the clock distribution using an injection-locked oscillator.

#### 2.2.5 Clock Deskewing

Since the ILOs have a phase relationship between the input and output signal while frequency deviation exists, the ILOs also can be used for delay element in the system. Since it can make the output phase from  $-180^{\circ}$  to  $+180^{\circ}$  by tuning the free-running oscillator's frequency, theoretically, which will be covered later in Section 2.3, it can be used in the application of delay element as shown in Fig. 2.8. However, it has to be designed carefully because while the locking is failed, it cannot provide stable clocking as we desire. Besides, the jitter transfer function is not consistent with the amount of the frequency deviation that is another research topic.

Fig. 2.8 An example of the injection-locked oscillator as a delay element in a source synchronous clock recovery structure.

#### 2.3 Basic Analysis for ILO

#### 2.3.1 Adler's Equation

In 1946, R. Adler first developed the equations for an ILO using a phasor diagram, indicating quick and straightforward insights into the phenomenon discovered in the oscillator as shown in Fig. 2.9 [7]. Since then, numerous researches expanding the theory have been published including K. Kurokawa [9], B. Razavi [16]. Since this equation is straightforward to understand the phenomenon, it is considered the first step to study the injection-locking technique. Originally, phasor diagram is usually developed when analyzing the linear system for sinusoidal waveforms of the same frequency which have an angular phase difference between the two signals. In the analysis of R. Adler, "rotating" phasor is employed for expressing signals with a slightly different frequency between the two signals. There are three assumptions to start the analysis.

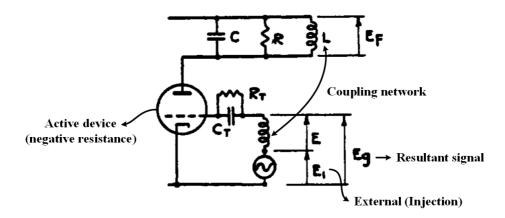

Fig. 2.9 Oscillator circuit developed in [7] with signal descriptions.

$$\omega_0 / 2Q \gg \Delta \omega_0. \tag{2.1}$$

$$T \ll 1/\Delta\omega_0$$

, where  $T = R_T C_T$ . (2.2)

$$E_1 \ll E \,. \tag{2.3}$$

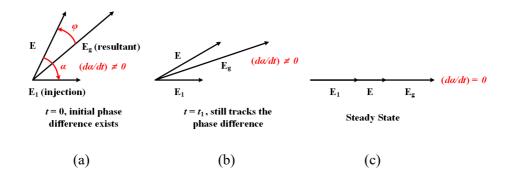

Equation (2.1) denotes that the injection frequency is very similar to the freerunning frequency of the oscillator. In other words, this analysis assumed the case while the injection successfully captures the oscillator clock. Also, an amplitude fluctuation due to the injection operation is ignored assuming the amplitude control mechanism is very fast as in (2.2). Lastly, the analysis in this paper focuses on the weak injection as in (2.3). With the three assumptions and introducing the concept of the rotating phasor diagram, the injection phenomenon can be explained. In Fig. 2.10, an example of the injection when the free-running frequency equals the injection frequency, which is the most straightforward case. In Fig. 2.10(a), since the initial phase is not the same between the two signals, the output phase shift exists as  $\varphi(t=0)$ . At the time  $t_l$  after that, the injection adjust the original signal, but not in the steady state, the output phase shift still exist, not zero as illustrated in Fig. 2.10(b). Finally, at the steady state, there is no phase difference between the two signals because of the zero frequency deviation as in Fig. 2.10(c). Expanding this observation to the case of non-zero frequency offset with the three assumptions (2.1), (2.2), and (2.3), the general equation can be derived using the rotating phasor diagram as in Fig. 2.9(a).

Fig. 2.10 A description of the injection-locking using rotating phasor diagram when the injection (a) starts, (b) is tracking, and (c) captures the original signal entirely while the frequency deviation is zero.

$$\sin \varphi = \frac{E_1}{Eg} \sin(-\alpha) = -\frac{E_1 \sin \alpha}{\sqrt{E_1^2 + E^2 + 2E_1 E \cos \alpha}} \approx -\frac{E_1}{E} \sin \alpha \,. \tag{2.4}$$

Under the weak injection,  $E_1 \ll E$ ,  $\phi \ll 1$ ,  $\sin \phi \approx \phi$ . Therefore, the following equation is derived.

$$\varphi = -\frac{E_1}{E} \sin \alpha \,. \tag{2.5}$$

Also, using the phase relationship of the resonant RLC circuits as shown in Fig. 2.11 with the assumption of the equation (2.1), the following equations are derived.

$$\varphi = \frac{d\varphi}{d\omega}(\omega - \omega_0) = \frac{d\varphi}{d\omega}(\omega - \omega_1 - \omega_0 + \omega_1) = \frac{d\varphi}{d\omega}(\Delta\omega - \Delta\omega_0). \quad (2.6)$$

Moreover, by the definition of the angular frequency in the rotating phasor diagram in Fig. 2.10(a),  $\Delta \omega$  is expressed as

$$\Delta \omega = \frac{d\alpha}{dt}.$$

(2.7)

Fig. 2.11 Magnitude and phase versus angular frequency illustrating off-resonant frequency [16].

Combining (2.6) and (2.7),

$$\varphi = \frac{d\varphi}{d\omega} (\Delta \omega - \Delta \omega_0) = \frac{d\varphi}{d\omega} (\frac{d\alpha}{dt} - \Delta \omega_0).$$

(2.8)

For an RLC tank, the impedance is calculated as

$$Z = R || sL || \frac{1}{sC} = \frac{j\omega RL}{j\omega L + R - \omega^2 RLC}$$

(2.9)

Its phase is calculated as

$$\angle Z = \frac{\pi}{2} - \tan^{-1} \left( \frac{\omega L}{R - \omega^2 R L C} \right) = \frac{\pi}{2} - \tan^{-1} \left( \frac{\omega L}{R} \frac{\omega_0^2}{\omega_0^2 - \omega^2} \right)$$

$$= \frac{\pi}{2} - \tan^{-1} \left( \frac{1}{Q} \frac{\omega_0}{2(\omega_0 - \omega)} \right) = \tan^{-1} \left( \frac{2Q}{\omega_0} (\omega_0 - \omega) \right)$$

(2.10)

Thus,

$$\tan(\angle Z) = \frac{2Q}{\omega_0}(\omega_0 - \omega).$$

(2.11)

In the notation of the phasor diagram in Fig. 2.10(a), the phase of the RLC tank can be expressed as  $\angle Z = -\varphi$ . Also, using the assumption of  $\varphi <<1$ ,  $\tan \varphi$  is approximated to  $\varphi$  ( $\tan \varphi \approx \varphi$ ). Thus, the equation of (2.11) can be re-derived as

$$\varphi = \frac{2Q}{\omega_0} (\omega - \omega_0) \,. \tag{2.12}$$

So its first derivative with respect to the angular frequency  $\omega$  is

$$\frac{d\varphi}{d\omega} = \frac{2Q}{\omega_0}.$$

(2.13)

Combining (2.5) and (2.8),

$$-\frac{E_1}{E}\sin\alpha = \frac{d\varphi}{d\omega} \left(\frac{d\alpha}{dt} - \Delta\omega_0\right).$$

(2.14)

Substituting (2.13) to the (2.14),

$$\frac{d\alpha}{dt} = -\frac{E_1}{E}\frac{\omega_0}{2Q}\sin\alpha + \Delta\omega_0.$$

(2.15)

From the equation (2.15), lock range of the harmonic oscillator can be calculated in the steady state while instantaneous phase drift with respect to the time settles. Since the left term in (2.15) is zero in the steady state, the following relationship is obtained as

$$\sin \alpha = 2Q \frac{E}{E_1} \frac{\Delta \omega_0}{\omega}, \ |\sin \alpha| = |2Q \frac{E}{E_1} \frac{\Delta \omega_0}{\omega}| \le 1,.$$

(2.16)

$$\frac{\Delta\omega_0}{\omega} \leq \frac{1}{2Q} \frac{E_1}{E}.$$

(2.17)

From the locking range in (2.17), it can be induced that as the injection strength is higher and the quality-factor Q gets smaller, the locking range increases. Equation (2.15) is expressed in the simplified form as

$$\frac{d\alpha}{dt} = -B(\sin\alpha - K), \ B = \frac{E_1}{E}\frac{\omega_0}{2Q}, \ K = 2Q\frac{E}{E_1}\frac{\Delta\omega_0}{\omega_0}.$$

(2.18)

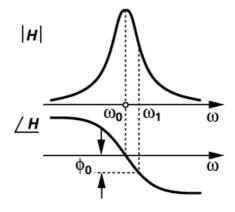

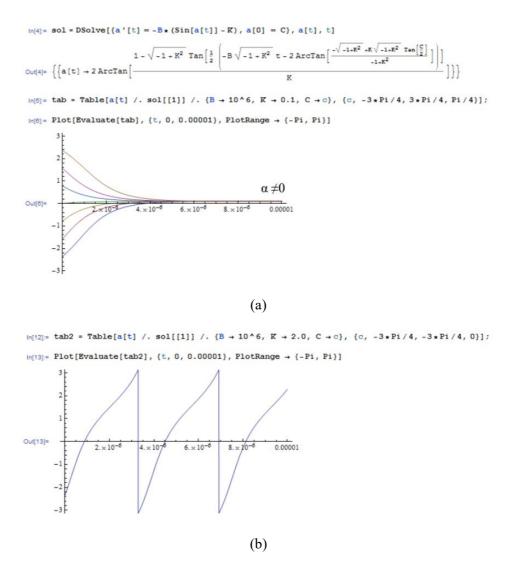

With the aid of the CAD tool of MATHEMATICA, the results are easily obtained as illustrated in Fig. 2.12 when the frequency-deviation  $\omega_0$  is zero. As shown in Fig. 2.12, regardless of the initial phase  $\alpha(0)$ , its final value at the steady state is zero. In the case of non-zero frequency deviation ( $\omega_0 \neq 0$ ), there are two cases of injection-locked and pulled situations. Its criteria are determined whether the K exceed one or not as derived in equation (2.17). While injection-locked, its output phase is illustrated in Fig. 2.13(a), showing the static phase shift between the two signals, in other words, at the steady state, its resultant output phase shift is not zero compared with the situation of zero frequency deviation as shown in Fig. 2.12. Fig. 2.13(b) shows the results while failed to injection locking, that is, injection pulling, thus it looks unstable or drifting.

Fig. 2.12 Various output results of equation (2.18) with different initial phase shifts while the frequency offset is zero.

Fig. 2.13 General output-phase-shift results with various initial phase shifts when (a) injection locked and (b) injection pulling.

#### 2.3.2 Phase Noise Analysis

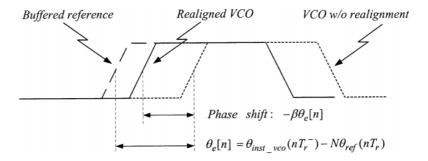

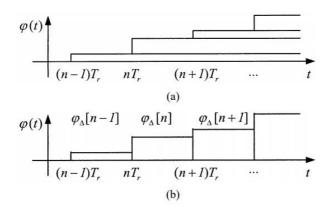

In [14], the noise transfer function of an ILO is presented regarding the noise sources in the specific application of the clock multiplication of *N*. There exist two noise sources in the ILOs; the oscillator itself and the injected signal. The accumulated noise of the oscillator is replaced with the injected signal. Thus, the relationship between the two noise sources can be derived using some assumptions and the understanding of the injection operation. This analysis is carried out while the frequency deviation between the two signals is ideally zero, and only the phase noise is considered. Even [14] does not include the effect of the frequency offset between the two signals, its derivation of the noise relationship is very meaningful to investigate the transfer function of the ILO-based clock multiplication in the frequency domain. As illustrated in Fig. 2.14, the instantaneous phase difference between the local oscillator and the injected signal is represented as

$$\theta_{e}[n] = \theta_{inst \ vco}(nT_{r}^{-}) - N\theta_{ref}(nT_{r}).$$

(2.19)

Fig. 2.14 Timing diagram before and after the injection affect the original clock edge reported in [14].

Fig. 2.15 The extra phase shift due to the injection operation (a) shown using the series phase steps and (b) impulse train employing hold operation reported in [14].

Here,  $T_r$  is the period of the reference clock and  $nT_r^-$  represents the time instant just before the injection is applied. After the injection happens, the amount of phase shift is defined as  $-\beta \theta_e[n]$  assuming a linear relationship between the input and the output phase. From this observation, the phase noise of the instantaneous oscillator can be given combining the noise from the oscillator itself and the extra noise portion from the injection operation:

$$\theta_{inst \ vco}(t) = \theta_{vco}(t) + \varphi(t). \tag{2.20}$$

Also, since the oscillator is originally phase integrator, each phase realignment can be expressed as the sum of a step increment to the oscillator phase noise as shown in Fig. 2.15:

$$\varphi(t) = -\beta \sum_{n=-\infty}^{\infty} \theta_e[n] \cdot u(t - nT_r).$$

(2.21)

By introducing the impulse train and "hold" operation, the following relationship is derived as

$$\varphi_{\Delta}[n] - \varphi_{\Delta}[n-1] \equiv -\beta \theta_{e}[n]. \qquad (2.22)$$

Combining (2.21) and (2.22) gives

$$\varphi(t) = \sum_{n=-\infty}^{\infty} \varphi_{\Delta}[n] \cdot h_{hold}(t - nT_r) . \qquad (2.23)$$

Taking the Fourier transform of (2.23),

$$\varphi(j\omega) = T_r e^{-j\omega T_r/2} \cdot \frac{\sin(\omega T_r/2)}{\omega T_r/2} \cdot \varphi_{\Delta}(z), \text{ where } z = e^{j\omega T_r}.$$

(2.24)

Here,  $\varphi_{\Delta}(z)$  is the *z* transform of  $\varphi_{\Delta}(n)$ .

Combining (2.19) and (2.22),

$$\varphi_{\Delta}[n] - \varphi_{\Delta}[n-1] = -\beta(\theta_{vco}[n] + \varphi_{\Delta}[n-1] - N\theta_{ref}[n]).$$

(2.25)

Taking the z transform of (2.24) and solving for the  $\varphi_{\Delta}(z)$ ,

$$\varphi_{\Delta}(z) = \frac{-\beta}{1 + (\beta - 1)z^{-1}} \theta_{vco}(z) + \frac{N\beta}{1 + (\beta - 1)z^{-1}} \theta_{ref}(z).$$

(2.26)

Combining (2.20), (2.24), and (2.26) gives

$$\theta_{inst\_vco}(j\omega) = \theta_{vco}(j\omega)H_{rl}(j\omega) + \theta_{ref}(j\omega)H_{up}(j\omega)$$

(2.27)

where

Fig. 2.16 Phase noise model of the injection-locked PLL including the effect of the realignment and the up-conversion of the reference noise reported in [14].

$$H_{rl}(j\omega) = 1 - \frac{\beta}{1 + (\beta - 1)e^{-j\omega T_r}} \cdot e^{-j\omega T_r/2} \cdot \frac{\sin(\omega T_r/2)}{\omega T_r/2}$$

(2.28)

and

$$H_{up}(j\omega) = \frac{N\beta}{1 + (\beta - 1)e^{-j\omega T_r}} \cdot e^{-j\omega T_r/2} \cdot \frac{\sin(\omega T_r/2)}{\omega T_r/2}.$$

(2.29)

The transfer function  $H_{rl}(j\omega)$  represents the effect of the phase realignment and  $H_{up}(j\omega)$  represents the up-conversion of the reference noise.

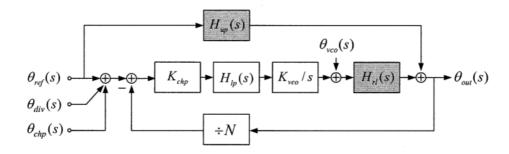

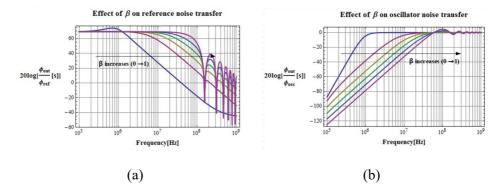

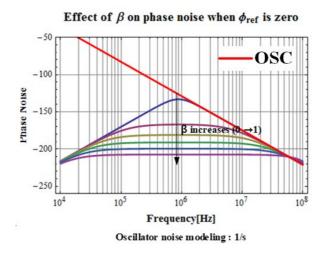

Fig. 2.16 shows the phase noise model of the injection-locked PLL containing the transfer function of  $H_{rl}(j\omega)$  and  $H_{up}(j\omega)$ . From the block diagram with the equations of (2.28) and (2.29), the output noise functions of the reference and oscillator are visualized in Fig. 2.17 with different realignment factor. Fig. 2.18 shows the noise suppression regarding the realignment factor when the oscillator noise is modeled as 1/s. As the injection strength increases, the amount of noise suppression also increases since the reference noise is extremely clean ( $\theta_{ref} = 0$ ).

Fig. 2.17 Noise transfer function of (a) the reference and (b) the oscillator with various realignment factor.

Fig. 2.18 Effect of realignment factor on phase noise when the reference noise is zero with different realignment factor.

# **2.4 Design Challenges**

According to the usage of the ILOs, the design challenges are slightly different. For instance, if the ILOs are utilized as a clock de-skewing element, the frequency offset is deliberately generated to make the desired output phase shift. Except for the application of the clock deskewing, all other circuits employing the ILOs should be designed to have a minimum frequency deviation for better performance. In this thesis, we focus on the calibration method of the frequency difference between the injected signal and the local free-running oscillator in the PLL-based ILO structure. If the difference between the two signals is not well matched, performance degradation is inevitable. In PLL design, considerable deterministic noise is caused, deteriorating the spur performance as shown in Fig. 2.19. Similarly, in CDR application, the generated deterministic noise reduces the timing margin of the data sampler, degenerating the tolerance for the consecutive identical digits (CIDs).

Fig. 2.19 An example of the clock multiplication when the frequency deviation exists reported in [28].

## 2.5 Recent Works

#### 2.5.1 Clock Multiplication

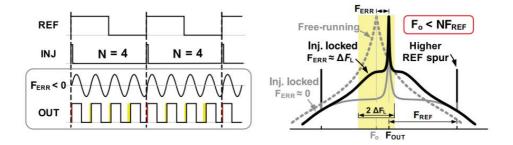

There are several ways reported in recent papers to solve the design challenges mentioned in Section 2.4. Sacrificing the phase information of the injection edge as depicted in Fig. 2.20(a), so-called gated pulse in [28], the phase detector inside the closed loop can detect the path mismatch between the two-phase align mechanism. The timing diagram in Fig. 2.20(b) offers detailed operation of this scheme. Since the injection pulse is gated once every four cycles, the accumulated frequency error is accumulated over N cycles; thus, its error between the two signals or the two paths can be detected, and the injection timing is compensated with the zero crossing of the signal which is the optimum injection point.

Fig. 2.20 (a) The concept of the pulse gating and (b) the timing diagram when the multiplication factor is four, and the gating rate is one fourth in [28].

The strategy suggested in [28] is very intuitive and straightforward, but, it has to sacrifice the high-quality of the reference to recognize it. In other words, it cannot achieve the maximum bandwidth compared with the scheme of full utilization of the reference clock. Next, nullifying the conventional phase detection in the PLL structure, the injection refreshes the local oscillator every cycle by employing the replica delay element as shown in Fig. 2.21 [30]. Assuming the same delay between the two elements, it can successfully discriminate the frequency deviation, the reference, and the local oscillator. However, it cannot confirm the perfect match because of the layout issues. In [30] as shown in Fig. 2.21, it compensates the path mismatch every negative edge of the reference rate, showing good reference spur level of –65 dBc/Hz.

Fig. 2.21 Block diagram of the replica-delay scheme and its timing diagram adjusting the frequency of the oscillator and path mismatch between the replica cells reported in [30].

#### 2.5.2 Clock Recovery

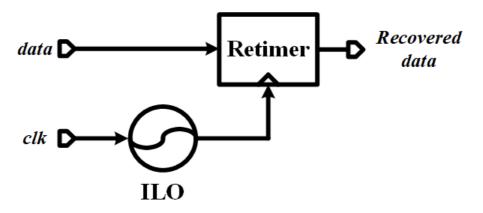

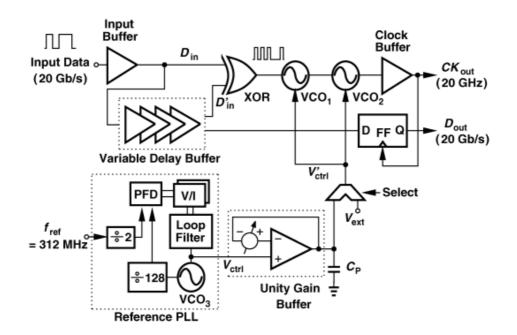

In Fig. 2.22, the PLL loop is present to make the similar frequency with the target frequency, in this example for 20 Gb/s data rate, 20 GHz [39]. The control voltage from the replica PLL is forwarded to the main ILO, VCO<sub>1</sub>, then the input data stream is injected through the pulse generator and the phase align is achieved. This scheme works, but, the hardware overhead is enormous, resulting in large silicon area and power dissipation. Also, the mismatch between the reference clock and data rate is not zero, and the layout issue of the replica scheme should be solved to be more stable or robust. Moreover, although phase align is achieved from the input data stream, the timing margin of the data sampler in Fig. 2.22 is not ensured to have a maximum value of 0.5 UI (unit interval).

Fig. 2.22 Block diagram of the replica-based ILCDR with reference PLL published in [39].

Since the proposed structure in [39] has a dual loop to generate the frequency of the local clock, and the inherent mismatch issues cannot be avoided, there have been studied for ILCDRs applying single loop excluding the reference clock [42]– [43]. As an example of such approaches, combining traditional PLL-based architecture with the data injection is present as shown in Fig. 2.23. Unlike the simple combination of the two-phase adjustment operation without further consideration, [43] suggests a new methodology distinguishing the error information whether it is from the phase inequality or the frequency mismatch. In this way, it can control the variable delay line in front of the data sampler and the frequency of the local oscillator simultaneously with minimum hardware additives assisted by the digital control.

Fig. 2.23 An implementation example of the injection-locked clock and data recovery using the serial output of the phase detector to distinguish the error source [43].

# Chapter 3

# **ILPLL with Injection-Timing Tracking**

## **3.1 Overview**

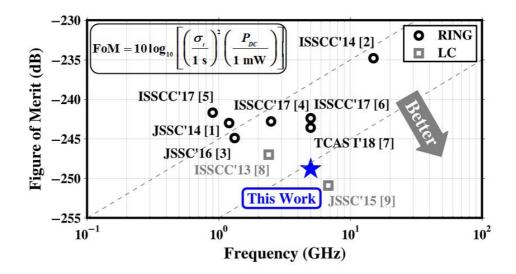

Conventional ring oscillators exhibit poor phase noise performance compared with LC oscillators. For this reason, a ring oscillator-based (RO-based) phase-locked loop (PLL) is designed to have a wide bandwidth to filter the considerable phase noise of the oscillator. However, the maximum feasible bandwidth is restricted to approximately one-tenth of the frequency of the reference clock. Even if they have poor jitter performance, RO-based PLLs have generally been explored because of their wide tuning range and small silicon area. To combine the advantages of RO-based PLLs with good jitter performance, injection-locked oscillators (ILOs) have widely been researched in many clock multipliers thanks to their remarkable jitter performance and simple implementation [23]–[34]. Fig. 3.1 shows the trend of a

Fig. 3.1 The trend of the figure of merit (FoM) versus frequency by choice of oscillator type in recent published ILPLLs.

figure of merit (FoM) versus frequency by choice of oscillator types in recent injection-locked PLLs (ILPLLs) [24], [26]–[33]. As expected, LC-based ILPLLs [24], [28] exhibit better jitter performance than RO-based ones. The RO-based ILPLL proposed in this work, however, shows a FoM comparable to LC-based ILPLLs and outstanding power efficiency. Thus, carefully crafted RO-based ILPLLs could be an attractive choice in clock multiplication thanks to the ease of design and smaller active area than LC-based ILPLLs.

Although ILPLLs are appealing regarding noise suppression, a robust operation is not ensured unless the injection timing is precisely controlled. Since the reference clock is directed to a phase detector, and at the same time injected into the oscillator, the two paths must be designed carefully since the phase of the oscillator might have already been adjusted by injection before the phase detector catches the phase error, nullifying the operation of the PLL or vice versa. To resolve the timing issue in conventional ILPLLs, several calibration methods have been reported in [23]–[30], [33], and [34].

In this work, to resolve the timing issue in ILPLL, an injection-timing calibrator that is focused on low power consumption is proposed, and a robust operation thereof is obtained over the process, supply voltage, and temperature (PVT) variations.

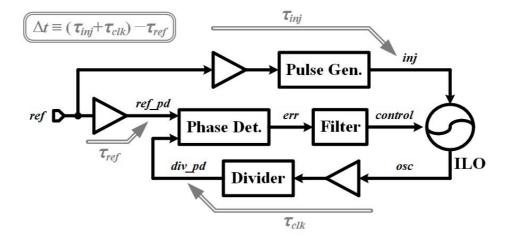

## 3.2 Analysis of Injection-Timing Effect

# 3.2.1 Frequency Error by Injection-Timing Mismatch in ILPLL

Fig. 3.2 shows a conventional ILPLL that includes delay elements in front of the phase detector. In this scheme, the timing mismatch is defined as  $\Delta t = (\tau_{inj} + \tau_{clk}) - \tau_{ref}$ . Once the feedback loop including the injection path locks, the phase detector cannot detect whether it locked to the desired timing or not. In [10], injection strength ( $\beta$ ) is introduced as the ratio of the output phase shift to the input phase deviation and the phase noise model of the oscillator at a fixed frequency ( $f_{osc}$ ) is presented without considering the loop. However, when the loop is closed,  $f_{osc}$  is varied depending on  $\Delta t$ .

Fig. 3.2 Block diagram of conventional ILPLL with delay elements.

(a)

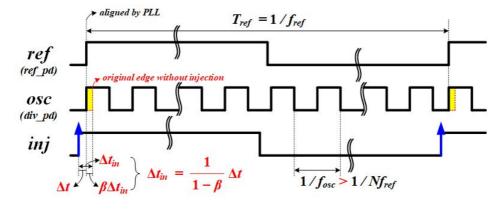

Fig. 3.3 Timing diagram of conventional ILPLL with  $\Delta t$  being (a) positive and (b) negative assuming  $\tau_{ref}$  and  $\tau_{clk}$  are zero.

Fig. 3.3 illustrates the timing diagram with fixed  $\Delta t$  being positive and negative assuming  $\tau_{ref}$  and  $\tau_{clk}$  are zero when the ILPLL achieves the phase lock in the steady state. Since the closed loop incorporating the PLL settles, the input phase error of the bang-bang phase and frequency detector (BBPFD) is zero on average regardless of the injection timing. The aligned phase of the oscillator (*osc*) is already changed by the reference injection, and the amount of phase shift due to the injection effect can be obtained from inverse operation of the equation in [14]. It is noted that the phase shift is not directly expressed as a function of  $\Delta t$  since the phase of *osc* in Fig. 3.3(a) is already disturbed by the injection as mentioned. Thus, we introduce a new variable to express the output phase shift. The new variable is denoted as  $\Delta t_{in}$ , and it means the input phase deviation in the definition of the injection strength [14]. Subsequently, its output phase shift is  $\beta \Delta t_{in}$ , and according to the timing relation demonstrated in Fig. 3, the following equation is derived as

$$\Delta t + \beta \Delta t_{in} = \Delta t_{in} \,. \tag{3.1}$$

Consequently,  $\Delta t_{in}$  can be written as

$$\Delta t_{in} = \frac{1}{1 - \beta} \Delta t \tag{3.2}$$

, where  $0 \le \beta < 1$ .

Using the relationship between  $\Delta t$  and  $\Delta t_{in}$ , and the additional phase shift,  $f_{osc}$  is derived as a function of  $\Delta t$  as

$$\left(\beta\Delta t_{in} + \frac{1}{f_{osc}}\right) + \frac{N-1}{f_{osc}} = \frac{1}{f_{ref}} \quad . \tag{3.3}$$

The first term represents the period disturbed by the injection at the N-th cycle. Subsequently, without the injection operation over (N-1) cycles, the oscillator runs freely having a period of ( $1/f_{osc}$ ); the second term in (3.3). Since we assumed that the ILPLL operates at the steady state, the sum of these two terms is identical to the period of the reference clock,  $1/f_{ref}$ . Then,  $f_{osc}$  is solved as a function of  $\Delta t_{in}$  as

$$f_{osc} = \frac{N f_{ref}}{1 - \beta f_{ref} \Delta t_{in}}.$$

(3.4)

We already have a relationship between  $\Delta t$  and  $\Delta t_{in}$  in (3.2), substituting (3.2) to (3.4),

$$f_{osc} = \frac{(1-\beta)Nf_{ref}}{(1-\beta) - \beta f_{ref}\Delta t}.$$

(3.5)

Equation (3.5) represents the frequency of the free-running oscillator is a function of the injection strength and the path mismatch in the ILPLL structure. When the injection strength is zero, in other words, injection is not applied to the oscillator,  $f_{osc}$  equals the  $Nf_{ref}$ , which is the target frequency of the ILPLL. Moreover, if the timing mismatch is ideally zero,  $f_{osc}$  is also equaled to the  $Nf_{ref}$ , which means there is no deterministic noise even the injection operation continuously modulates the phase of the local oscillator.

#### 3.2.2 Deterministic Noise for Injection Timing

In the condition that the free-running frequency of the oscillator,  $f_{osc}$ , is within the locking range of the ILO, the injection signal captures the free-running oscillator. Considering the phase error is accumulated during (N-1) cycles and, the injection induces an additional phase shift periodically to achieve the phase lock, the average frequency of the output signal,  $f_{out}$ , equals to  $Nf_{ref}$ . Assuming the offset in the instantaneous output period is approximately  $\alpha T_{out}$ , deterministic jitter (DJ) and reference spur (Spur) are derived as a function of the frequency error ( $\Delta f$ ), where  $\alpha$  is  $\Delta f / Nf_{ref}$  [23].

$$DJ \approx (N-1)\alpha T_{out} \approx \alpha T_{ref}$$

(3.6)

$$Spur \approx 20 \log_{10} (DJ / T_{out}) \approx 20 \log_{10} (\alpha N).$$

(3.7)

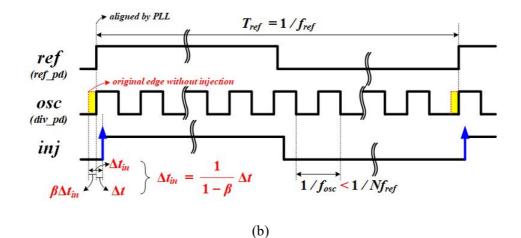

Because we made a relationship between  $f_{osc}$  and  $\Delta t$  in (3.1), the equations of *DJ* and *Spur* can be re-derived concerning  $\Delta t$ . Substituting (3.1) into the equations, the following formulas are derived and visualized in Fig. 3.4(a) and Fig. 3.4(b), respectively.

$$DJ \approx \alpha T_{ref} = \frac{\Delta f}{Nf_{ref}^2} = \frac{f_{osc} - Nf_{ref}}{Nf_{ref}^2} = \frac{\beta \Delta t}{(1 - \beta) - f_{ref} \beta \Delta t}.$$

(3.8)

$$Spur \approx 20\log_{10}(\alpha N) = 20\log_{10}\left(\frac{Nf_{ref}\beta\Delta t}{(1-\beta) - f_{ref}\beta\Delta t}\right).$$

(3.9)

Fig. 3.4 (a) Deterministic jitter and (b) reference spur calculated from the equations of (2) and (3) as a function of injection-timing mismatch ( $\Delta t$ ) for two different injection strengths ( $\beta = 0.1$  and  $\beta = 0.3$ ) in conventional ILPLL. In this example, N = 16 and  $f_{ref} = 312.5$  MHz.

In Fig. 3.4, when  $\beta$  is increased, the deterministic jitter is also increased more steeply with respect to the injection-timing mismatch because  $f_{osc}$  is much different from the target output frequency,  $Nf_{ref}$ , as shown in (3.1). In addition, phase noise performance is degraded by the injection-timing mismatch because of the decreased injection strength which will be covered in next Chapter 4. Therefore, overall jitter performance of the ILPLL hugely depends on the timing mismatch in the ILPLL, which forces continuous tracking mechanism of the mismatch to achieve a significant improvement of the jitter performance.

Fig. 3.5 (a) Behavioral phase-noise simulations of ILPLL when injection timing is perfectly tuned and (b) calculated jitter as a function of injection strength. In this example, N = 16,  $f_{ref} = 312.5$  MHz, the phase noise of an oscillator is -95 dBc/Hz at 1-MHz offset excluding flicker noise, and phase noise of reference clock is modeled as having a Gaussian random noise of -160 dBc.

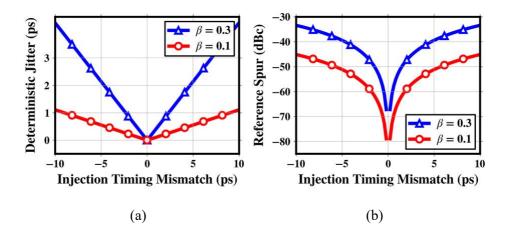

Fig. 3.5 shows the behavioral simulations with several different conditions. In this example, N = 16,  $f_{ref} = 312.5$  MHz, the phase noise of an oscillator is -95 dBc/Hz at 1-MHz offset excluding flicker noise, and phase noise of reference clock is modeled as having a Gaussian random noise of -160 dBc. In Fig. 3.5(a), the phasenoise curves are presented when injection timing is perfectly tuned, and three different injection strengths are applied. In this ideal case,  $\beta$  should be selected as large as possible to cut off the phase noise from the oscillator.

However, with the presence of non-zero  $\Delta t$ , blindly increasing injection strength might yield worse jitter performance due to the deterministic jitter and spur as indicated in (3.4) and (3.5). Simulation results are illustrated in Fig. 3.5(b). In this simulation, the integration range includes the reference frequency; thus, the deterministic noise analyzed in (3.4) and (3.5) is considered. As seen in Fig. 3.5(b), although

the optimum injection strength can be determined for the minimum integrated jitter given the timing mismatch, it is impossible to estimate the exact injection timing. In addition, variations of supply voltage and temperature make its estimation difficult as well. Therefore, to achieve the best performance in ILPLL, the injection strength should be chosen as large as possible and a continuous tracking mechanism of the injection timing under PVT variation must be incorporated.

## **3.3 Proposed ILPLL with Optimum Injection Timing**

As analyzed in Section 3.2, injection-timing mismatch impacts jitter performance critically. In this work, by inserting a divider in front of the pulse generator, being similar to a pulse-gating scheme in [28] and [32], one of two edges of the reference clock is skipped to detect the timing discrepancy between two different modulation paths and the delay through the injection path is adjusted to an optimum value with a minimal hardware overhead. Since the proposed scheme extracts the timing error at the rate of the slow reference clock rather than an oscillation clock, it achieves significant power efficiency compared with [26]–[27], [29], and [30].

#### 3.3.1 Half-Edge Injection and Detecting Injection Timing

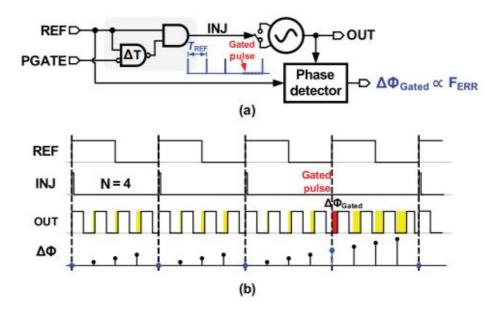

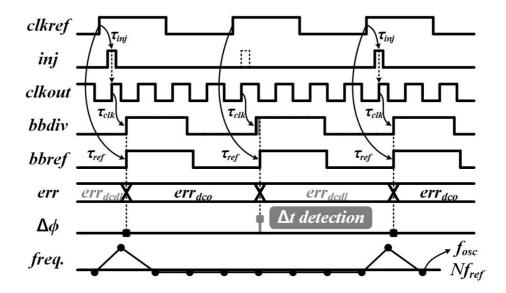

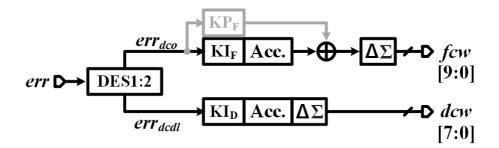

Fig. 3.6 illustrates the timing diagram where the injection is intentionally omitted every other cycle. The errors from the bang-bang phase and frequency detector (BBPFD) are de-serialized and forwarded as  $err_{dco}$  when the injection is enabled and  $err_{dcdl}$  when the injection is skipped. Owing to the all-digital PLL (ADPLL) loop adjusting the phase of the oscillator,  $err_{dco}$  might settle to zero average even if it has frequency error ( $\Delta f$ ). In this figure,  $err_{dco}$  is instantaneously zero assuming the loop has an exceptionally high gain for a simple explanation. For (N-1) cycles right after injection is applied,  $\Delta f$  due to  $\Delta t$  is accumulated, and this phase error is detected as  $err_{dcdl}$  as highlighted in the gray text box in Fig. 3.7. Because the frequency of injection is 0.5  $f_{ref}$ , deterministic noises come at this rate and its harmonics, and these results are presented in next Section 3.5.

Fig. 3.6 The conceptual timing diagram of the half-edge injection with proposed tracking loop disabled when multiplication factor (N) is 4.

Fig. 3.7 shows the block diagram of the digital loop filter that detects the timing error in ILPLL. The de-serialization is easily implemented by using a counter. The separated errors are individually accumulated and modulated by delta-sigma modulator to mitigate quantization noise.

Fig. 3.7 Block diagram of the digital loop filter.

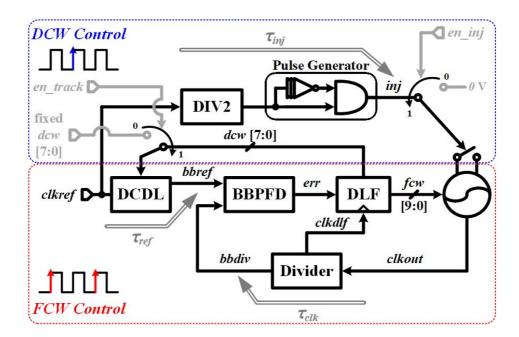

### **3.3.2** Overall Architecture and Operation Principle

Fig. 3.8 shows the block diagram and flowchart of the proposed ILPLL. The injection-timing mismatch defined in Section 3.2 is adjusted by 8-bit digitally controlled delay line (DCDL) until it comes to zero. The pulse-gating scheme in [28] and [32], though simplified for this work, is utilized to find the timing mismatch. By inserting a divider in front of the pulse generator as shown in Fig. 7(a),  $\Delta f$  is detected at the BBPFD because the phase error induced by  $\Delta t$  is accumulated over (N - 1) cycles. The propagation delay through injection path  $(\tau_{inj})$  and clock divider  $(\tau_{clk})$  is fixed and unavoidable. In this reason, adjusting the delay ahead of BBPFD  $(\tau_{ref})$  is selected to eliminate it to zero, not integer multiples of the target period as described in [33].

Fig. 3.8 Block diagram of the proposed ILPLL.

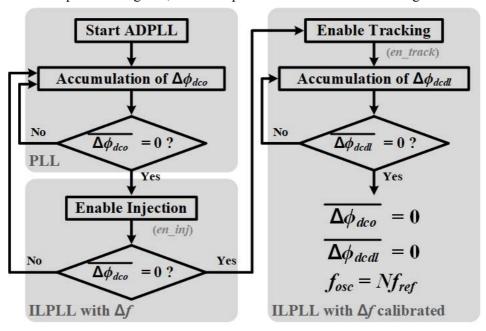

As depicted in Fig. 3.9, ADPLL operates at first for coarse tuning of the oscil-

Fig. 3.9 Flowchart of the proposed ILPLL.

lator. After ADPLL is locked, the pulsed injection is applied  $(en_inj)$  to operate as a conventional ILPLL. When initial  $\Delta f$  induced by  $\Delta t$  is within the locking range of ILPLL, it achieves a locked state; however, it may not be the optimum condition. Subsequently, the proposed tracking loop turns on  $(en_track)$ , and DCDL is adjusted to reduce the timing mismatch; thus,  $f_{osc}$  goes to the target frequency,  $Nf_{ref}$ . In other words, averaged errors of DCO ( $\Delta \phi_{dco}$ ) and DCDL ( $\Delta \phi_{dcdl}$ ) come to zero for both, which shows desired locking behavior.

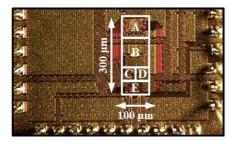

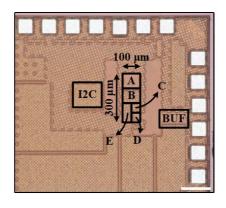

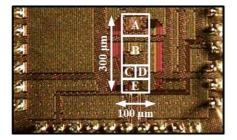

# **3.4 Measurements**

The prototype chip has been fabricated in 28-nm CMOS technology. The chip contains the proposed ILPLL, an open-drain clock driver for monitoring, and an I<sup>2</sup>C interface that controls operation mode and several configurable parameters such as injection strength or the loop-filter gain. The ILPLL occupies an active area of 0.03 mm<sup>2</sup> and consumes 5.65 mW with the 312.5-MHz reference clock and 0.9-V supply voltage at 5 GHz as described in Fig. 3.10. The reference clock is sourced from a vector signal generator, Agilent E8267D, through bias tee and output clock is measured by a spectrum analyzer, Agilent E4445A. A digital power source, Agilent B2926A, is also used to measure the total current of each power domain and supply-variation test as shown in Fig. 3.13.

|   | <b>Block Description</b> | Power (mW) |

|---|--------------------------|------------|

| A | Digital Loop Filter      | 2.6        |

| B | ILDCO                    | 3.38       |

| С | Pulse Gen. & DCDL        |            |

| D | PD & Deserializer        | 6.83       |

| E | Limiting Amplifier       | 1          |

Fig. 3.10 Chip photomicrograph, block description, and separated power consumption at 10 Gb/s with a 0.9-V supply voltage.

# 3.4.1 Noise Suppression using Injection and Timing Calibrator

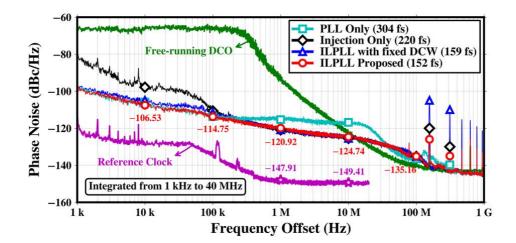

Fig. 3.11 shows the measured phase-noise curves with several different clock synthesizers. When an injection is applied without any loop, the noise under 100 kHz (1/*f* region) is not sufficiently filtered out since it operates as the first-order system offered by an injection locking. With PLL activated and injection with uncalibrated, fixed DCW, because there is a mismatch in injection timing, deterministic noise is shown at 156.25 MHz and its harmonics. The proposed ILPLL shows the lowest rms jitter integrated from 1 kHz to 40 MHz as 152 fs.

Fig. 3.11 Measured phase-noise curves of the output clock.

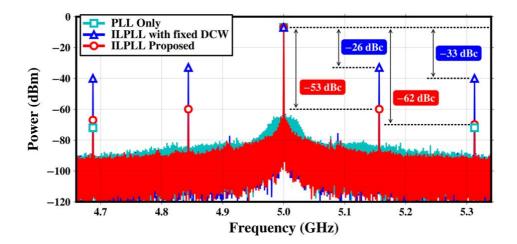

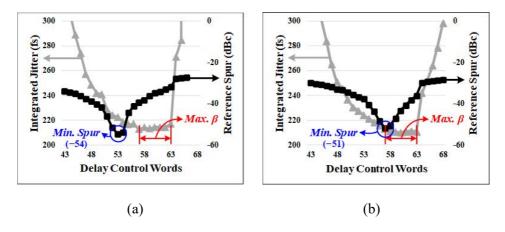

Although in-band noise suppression is almost the same as the ILPLL with fixed delay control word (DCW), the spurious tones at 156.25 MHz and its super-harmonics are reduced as much as 30 dB since  $\Delta t$  comes to zero in average by adapting the delay utilizing DCDL. In this result, it is demonstrated that the deterministic jitter induced by the timing mismatch is reduced, and it is more clearly found in the following spectrum analysis. Fig. 3.12 shows spectrum results with and without the timing calibrator when the injection is applied with PLL. The ILPLL with fixed DCW shows inferior reference spur compared with the proposed one. In this test of Fig. 3.11 and Fig. 3.12, normalized DCW is fixed to -15, which is equivalent to about 20-ps timing mismatch in SPICE simulation. As seen in Fig. 3.11, spurious tones at 156.25 MHz and 312.5 MHz show up, and the proposed tracking loop reduces these tones to -53 dBc and -62 dBc, respectively.

Fig. 3.12 Measured spectrums of the output clock.

#### 3.4.2 Verification of Timing Calibrator with Variations

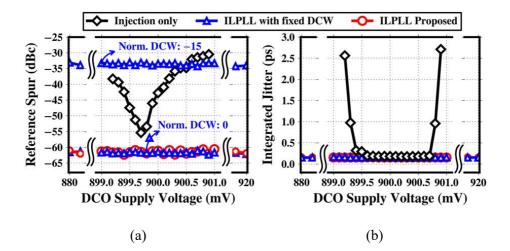

Fig. 3.13 shows the measured reference spur and integrated jitter of several different clock multipliers using injection with various supply voltage. This test is carried out using a digital power source, Agilent B2926A, which has a fine resolution of voltage less than 0.1 mV. With fixed  $f_{asc}$  and injection without any feedback loop, measured spur levels are susceptible to the supply-voltage variation, and the integrated jitter is abruptly increased at the edge of locking range. The ILPLL with fixed DCW shows constant spur values depending on DCW. Since  $\Delta t$  is fixed and not adjusted by the tracking loop, the deterministic noises are added when  $\Delta t$  is not zero. The proposed ILPLL shows consistent and minimum jitter performance for the supply-voltage variation irrespective of initial DCW.

Fig. 3.13 Measured (a) reference spur and (b) integrated jitter with different injection-locked clock multiplier architecture over supply-voltage variation.

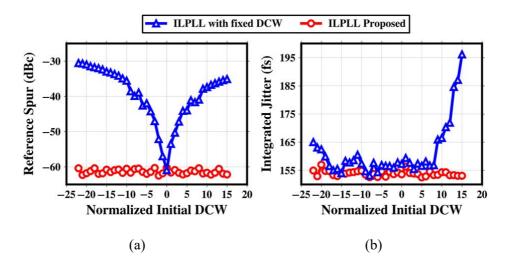

initial DCW controlled by I<sup>2</sup>C interface with fixed 0.9-V supply voltage. With ILPLL alone, reference spur is very sensitive to DCW as shown in Fig. 3.14(a). The center code for expressing normalized DCW is defined to the point where ILPLL without the calibrator shows minimum spur level. When the proposed tracking loop operates, initial DCW converges to the optimum point where the timing mismatch is minimized, resulting in constant and minimum values for both the spur level and the integrated jitter over various initial DCWs as shown in Fig. 14(a) and (b).

Fig. 3.14 Measured (a) reference spur and (b) integrated jitter with and without timing calibrator as a function of the normalized initial delay control word.

#### 3.4.3 Performance Summary and Comparison

Table 3.1 shows performance summary and comparison with recently published RO-based ILPLLs [27], [29]–[33]. This work shows the best-integrated jitter compared with them. From the measured integrated jitter and power consumption, the figure of merit (FoM) is defined as

FoM =

$$10 \log_{10} \left[ \left( \frac{\sigma_t}{1 \text{ s}} \right)^2 \left( \frac{P_{DC}}{1 \text{ mW}} \right) \right],$$

(3.1.2)

where  $\sigma_t$  is integrated jitter, and  $P_{DC}$  is power consumption [17]. The calculated FoM in this work is –248.8 dB that is state-of-the-art among the RO-based ILPLLs [26]– [27], [29]–[33]. Regarding energy cost, this work exhibit the power efficiency as 1.13 mW/GHz that is considerably efficient between RO-based ILPLLs. For the RObased ILPLLs which contain the timing-calibrator [26]–[27], [29]–[30], the proposed ILPLL shows much higher power efficiency since replica cells or decision circuits in [26]–[27], [29]–[30] operate at the frequency of oscillation which is the fastest rate in the whole chip. On the other hand, the proposed ILPLL adopts the architecture of conventional PLL except for the injection circuits and DCDL that are switched by the rate of the reference clock, thus, remarkable energy cost is obtained. Table 3.1 Performance Summary and Comparison.

| Half-Edge<br>Injection       | Γ.                                                  | Pulse Gating           | L.                     | TDDC                   | Replica-Delay<br>Cell     | Pulse-Position<br>Modulation | Injection-Timing (Δƒ')<br>Tracking            |

|------------------------------|-----------------------------------------------------|------------------------|------------------------|------------------------|---------------------------|------------------------------|-----------------------------------------------|

| -248.8                       | -243.6                                              | -242.4                 | -241.7                 | -242.8                 | -244.9                    | -234.8                       | FoM (dB)                                      |

| -62 @ fref<br>-53 @ 0.5 fref | -42 @ f <sub>ref</sub><br>-42.6 @ 2f <sub>ref</sub> | -45                    |                        | -65                    | -53                       | -48                          | Reference Spur (dBc)                          |

| 152<br>(1 kHz–40 MHz)        | 168<br>(1 kHz-40 MHz)                               | 340<br>(10 kHz-40 MHz) | 420<br>(10 kHz-10 MHz) | 198<br>(10 kHz-40 MHz) | 185<br>(10 kHz-40 MHz)    | 268<br>(100 kHz-1 GHz)       | Output Int. Jitter (fs)<br>(Range)            |

| -149 dBc/Hz<br>@ 10 MHz      | -165 dBc/Hz<br>@ 1 MHz                              | '                      | L.                     | r                      | 118 fs<br>(10 kHz-40 MHz) | -136.6 dBc/Hz<br>@ 10 MHz    | Reference Phase Noise<br>or Integrated Jitter |

| 1.13                         | 3.08                                                | 1.06                   | 4.22                   | 4. <mark>62</mark>     | 7.92                      | 3.08                         | Power Eff. (mW/GHz)                           |

| 5.65                         | 15.4                                                | 5.3 @ 5 GHz            | 3.8                    | 13.5                   | 9.5                       | 46.2                         | Power (mW)                                    |

| 16                           | 32                                                  | 20-46                  | 6                      | 16                     | 10                        | 8                            | Mult. Factor (N)                              |

| 5                            | 2.5-5.63                                            | 2.5-5.75               | 0.52-1.15              | 2.5                    | 0.96-1.44                 | 2-16                         | Output Freq. (GHz)                            |

| 312.5                        | 156.25                                              | 120                    | 150                    | 156.25                 | 120                       | 1875                         | Reference Freq. (MHz)                         |

| 0.9                          | 1.2                                                 | 1.0                    | 1.2                    | 1.2                    | 1.1                       | 1.25 / 1.1                   | Supply Voltage (V)                            |

| 0.03                         | 0.06                                                | 0.09                   | 0.028                  | 0.064                  | 0.06                      | 0.044                        | Active Area (mm <sup>2</sup> )                |

| 28                           | 65                                                  | 65                     | 65                     | 65                     | 65                        | 20                           | Technology (nm)                               |

| This Work                    | TCAS I'18 [7]                                       | ISSCC'17 [6]           | ISSCC'17 [5]           | ISSCC'17 [4]           | JSSC'16 [3]               | ISSCC'14 [2]                 |                                               |

# **Chapter 4**

# **ILPLL with Maximum Injection Strength**

## 4.1 Overview

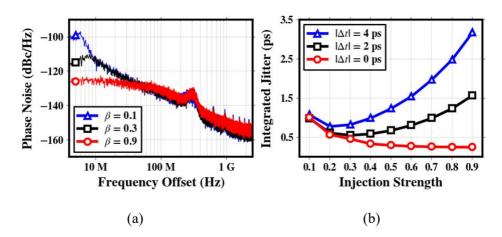

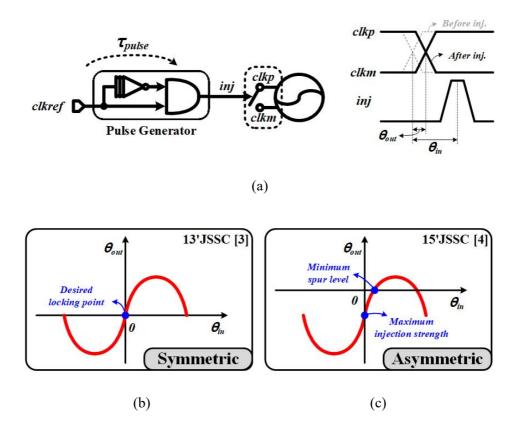

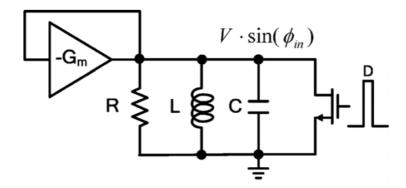

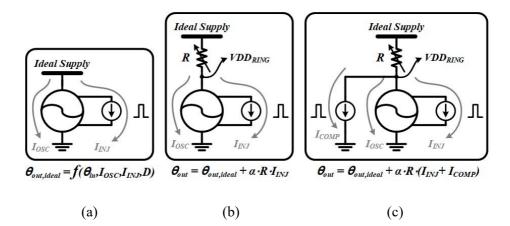

Injection-locked oscillators (ILOs) have been widely adopted in clock synthesis because of their superior jitter performance and simple implementation. Most analyses for the ILOs [14], [16], [25], and [28] have focused only on the relationship between the currents of the injection and the local oscillator. In addition, the analyses have been conducted in an over-simplified way ignoring the factors that may affect overall characteristics such as the injection duration or the voltage drop across the control circuit. In [28], the injection duration is considered as a variable for the overall phase domain response (PDR) showing asymmetry in certain cases.

Although the injection duration is considered in the analysis, it does not

Fig. 4.1 (a) Conventional injection-locked oscillator (ILO) with a pulse generator and its timing diagram. (b) Symmetric [25] and (c) asymmetric [28] phase domain response (PDR) analyses.

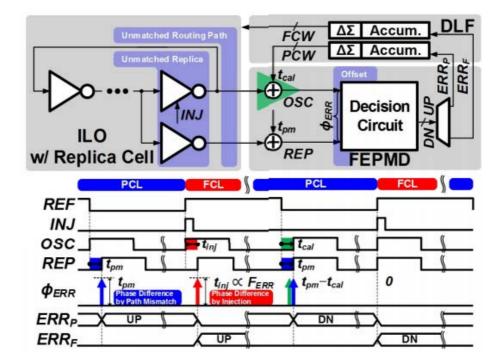

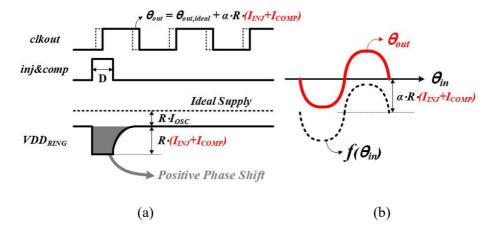

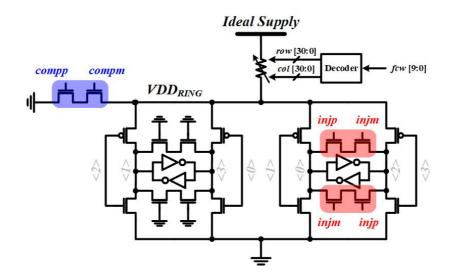

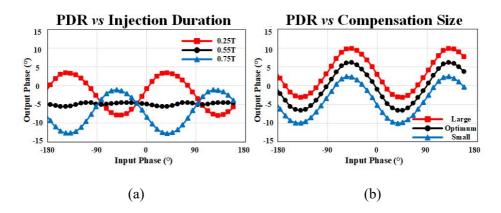

include the effects from the parasitics of the actual circuit elements such as resistors or current sources. In this work, including implemented circuits controlling the frequency of the oscillator, the PDR is re-derived and adjusted to have a symmetric characteristic to find the best locking point.