#### 저작자표시-비영리-변경금지 2.0 대한민국

#### 이용자는 아래의 조건을 따르는 경우에 한하여 자유롭게

• 이 저작물을 복제, 배포, 전송, 전시, 공연 및 방송할 수 있습니다.

#### 다음과 같은 조건을 따라야 합니다:

저작자표시. 귀하는 원저작자를 표시하여야 합니다.

비영리. 귀하는 이 저작물을 영리 목적으로 이용할 수 없습니다.

변경금지. 귀하는 이 저작물을 개작, 변형 또는 가공할 수 없습니다.

- 귀하는, 이 저작물의 재이용이나 배포의 경우, 이 저작물에 적용된 이용허락조건 을 명확하게 나타내어야 합니다.

- 저작권자로부터 별도의 허가를 받으면 이러한 조건들은 적용되지 않습니다.

저작권법에 따른 이용자의 권리는 위의 내용에 의하여 영향을 받지 않습니다.

이것은 이용허락규약(Legal Code)을 이해하기 쉽게 요약한 것입니다.

#### Ph.D. DISSERTATION

# The Effect of Interfacial Layer on the Electrical Properties of Atomic-Layer-Deposited p-Type SnO Thin-Film Transistors

by

Younjin Jang

February 2021

DEPARTMENT OF MATERIALS SCIENCE AND ENGINEERING

COLLEGE OF ENGINEERING

SEOUL NATIONAL UNIVERSITY

# The Effect of Interfacial Layer on the Electrical Properties of Atomic-Layer-Deposited p-Type SnO Thin-Film Transistors

Advisor: Prof. Cheol Seong Hwang

by

#### Younjin Jang

A thesis submitted to the Graduate Faculty of Seoul National

University in partial fulfillment of the requirements for the

Degree of Doctor of Philosophy

Department of Materials Science and Engineering

February 2021

Approved

by

Chairman of Advisory Committee:

Jin Young Kim

Vice-chairman of Advisory Committee:

Cheol Seong Hwan

Advisory Committee:

SangBum Kim

Advisory Committee:

Jeong Hwan Han

Advisory Committee:

Woojin Jeon

#### **Abstract**

This dissertation investigates the improvement of the electrical properties of thin-film transistor (TFT) devices using atomic-layer deposition (ALD)-based high-quality p-type SnO thin film, with the aim of securing research technology for next-generation semiconductor channels and dielectric film materials.

First, the origin of hysteresis in the drain-source current ( $I_{DS}$ ) – gate-source voltage (V<sub>GS</sub>) characteristics of ALD p-type SnO TFTs was examined by adopting ALD Al<sub>2</sub>O<sub>3</sub> interfacial layers (IL) between the SnO channel layer and the SiO<sub>2</sub> gate insulator (GI) layer. The SnO TFTs with SiO<sub>2</sub> GI exhibited a large hysteresis voltage (V<sub>hy</sub>) owing to the trap state density near the interface between the SnO active layer and the SiO<sub>2</sub> GI (border trap). Both the experimental results and the theoretical calculations showed that the origin of the border traps was the  $Sn_{Si}^{+0}$  gap states in SiO<sub>2</sub>, which was induced by the Sn diffusion into the SiO<sub>2</sub> layer. The adoption of Al<sub>2</sub>O<sub>3</sub> films as ILs suppressed the Sn diffusion. The effectiveness of IL, however, is dependent on the thickness, crystallinity, and density of the Al<sub>2</sub>O<sub>3</sub> films. The V<sub>hy</sub> of the SnO TFTs can be decreased when the thickness and density of the ILs increase as long as the amorphous structure of the Al<sub>2</sub>O<sub>3</sub> IL is maintained after the rapid thermal annealing (RTA) process. The p-type ALD SnO TFTs with optimum ILs exhibited a high on/off ratio of I<sub>DS</sub> (1.2×10<sup>5</sup>), high field effect mobility  $(1.6 \text{ cm}^2\text{V}^{-1}\text{s}^{-1})$ , and a small  $V_{hy}$  (0.2 V).

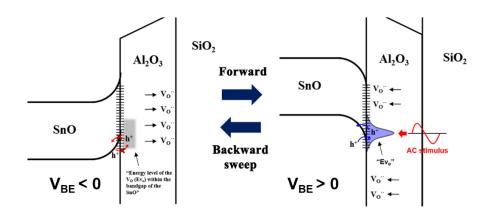

Second, abnormal electrical properties in SnO devices with  $Al_2O_3$  interfacial layer were examinated. An in-depth analysis was conducted on how mobile oxygen vacancies ( $V_0$ ) in the IL thin film affects three types of characteristics; the  $V_{GS}$  dependence, gate current characteristics, and capacitance characteristics.

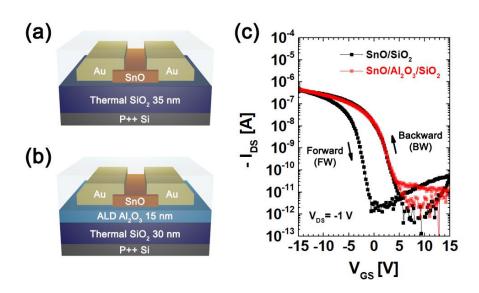

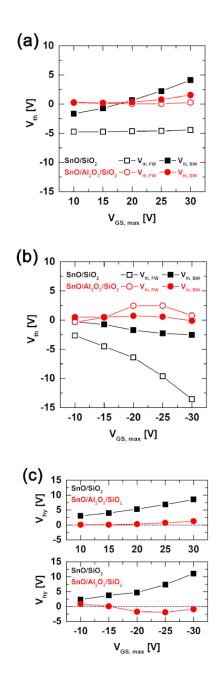

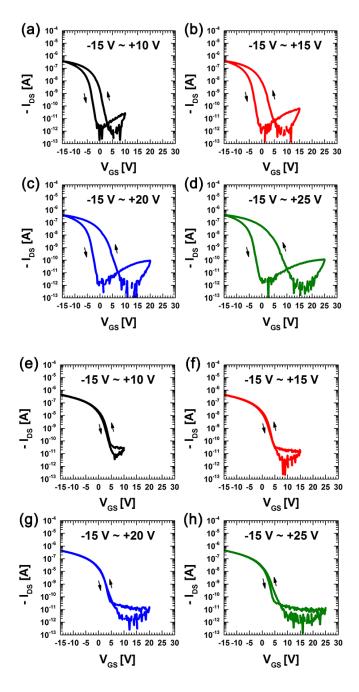

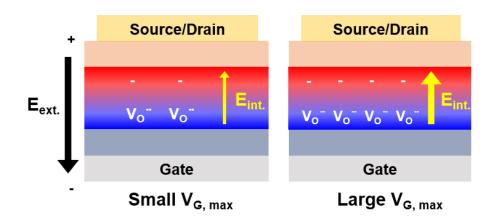

One of the abnormal characteristics is the  $V_{GS}$  dependence. The gate-induced electrical instability of SnO TFTs with SiO<sub>2</sub> and Al<sub>2</sub>O<sub>3</sub>/SiO<sub>2</sub> gate dielectric layers was evaluated. The  $V_{hy}$  and threshold voltage ( $V_{th}$ ) in the transfer characteristics of SnO TFTs depended on the sweep range and rate of  $V_{GS}$ . The TFT with an Al<sub>2</sub>O<sub>3</sub>/SiO<sub>2</sub> gate dielectric layer exhibited reduced  $V_{hy}$  and stable  $V_{th}$  compared to the device without an Al<sub>2</sub>O<sub>3</sub> layer. The introduction of an Al<sub>2</sub>O<sub>3</sub> layer between the SnO channel and the SiO<sub>2</sub> layer suppressed the electron and hole trapping at the channel/dielectric interface and contained  $V_{O}$ 's that counteracted the hole trapping effect.

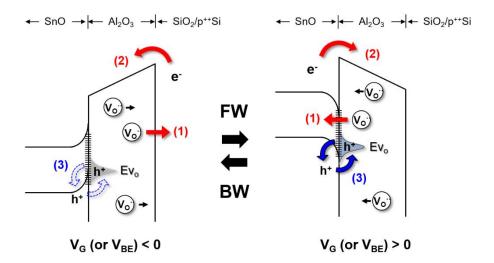

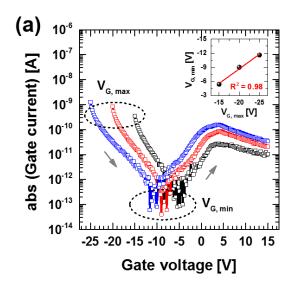

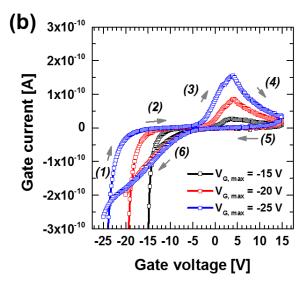

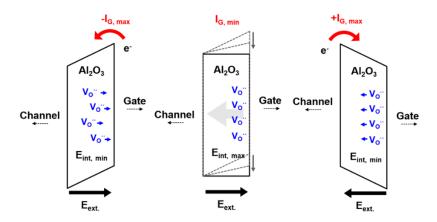

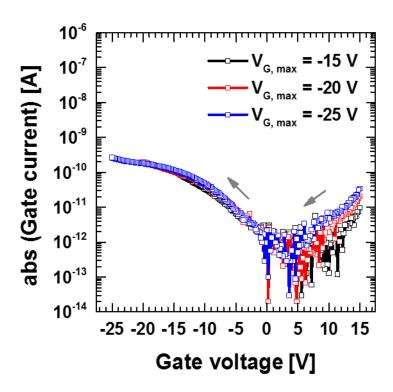

Another abnormal characteristics due to  $V_0$ 's inside the  $Al_2O_3$  IL is reflected in the gate current characteristic. A large  $I_{GS}$  is related to the field-induced migration of the  $V_0$ 's in the  $Al_2O_3$  layer. The  $V_0$  could produce an internal electric field that could balance with the external electric field. The charge transfer through the gate dielectric could be affected, and gate leakage can be dominant compared to the channel current in the depletion bias region. As a results, the hysteresis directions of I-V and C-V do not coincide with each other.

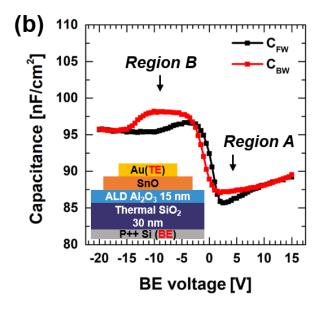

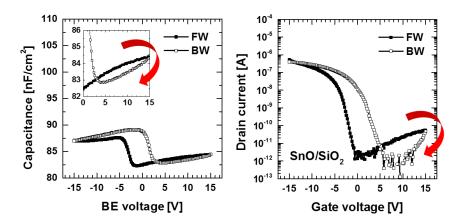

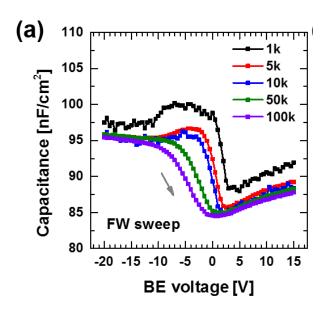

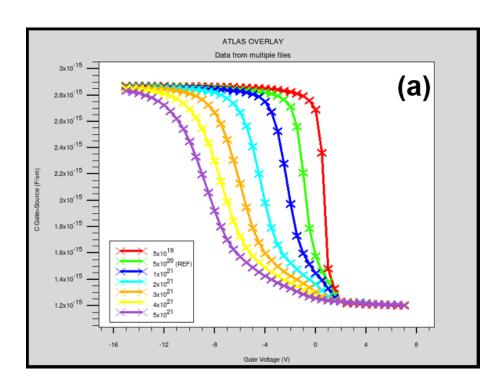

The other abnormal characteristics due to  $V_O$ 's inside the  $Al_2O_3$  IL is reflected in the capacitance characteristic. The additional capacitance is observed in the specific voltage. At the sufficiently negative  $V_{GS}$ , most of the  $V_O$  must be dragged toward the  $Al_2O_3/SiO_2$  interface, making them inactive to the AC stimulus (hole trapping/detrapping) in the accumulation bias region. It seems that the energy level of the  $V_O$  within the bandgap of the SnO is closer to the valence band, so it incurs the additional capacitance by hole trapping in the accumulation region. However, as the  $V_{GS}$  further decreased, the  $V_O$ 's are migrated toward the  $Al_2O_3/SiO_2$  interface again, which removed the additional capacitance at sufficiently negative  $V_{GS}$  region.

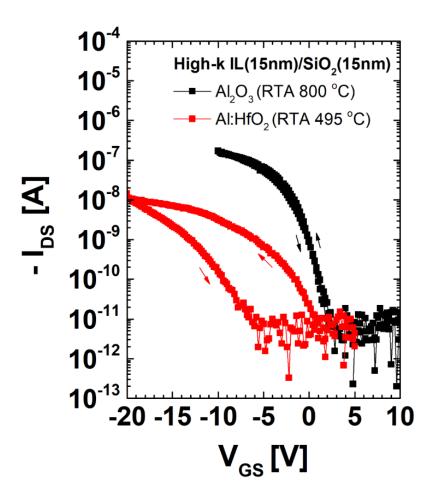

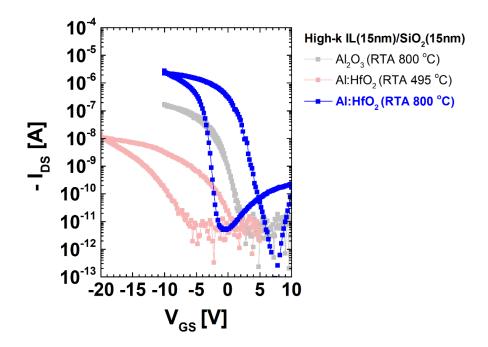

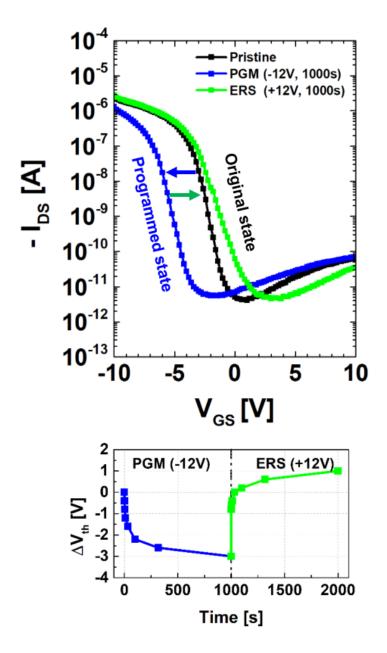

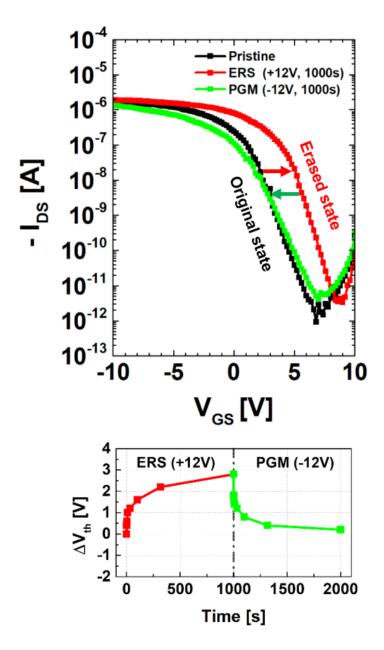

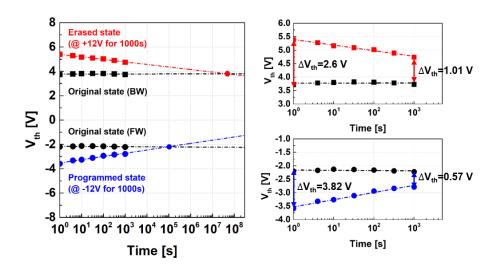

Third, in order to improve the performance of the SnO TFTs, an Al-doped HfO<sub>2</sub> (Al: HfO<sub>2</sub>) thin film having a high dielectric constant replacing the Al<sub>2</sub>O<sub>3</sub> thin film was adopted as an IL. Al doping can suppress the crystallization of HfO<sub>2</sub> thin film, but it acts as an obstacle to the thin film density, greatly deteriorating the performance of the SnO TFT device. On the other hand, when the crystallized Al: HfO<sub>2</sub> IL was adopted, a large  $V_{hy}$  (6.4 V) was shown, but excellent TFT device performance ( $\mu_{FE}$ = 5.7 cm<sup>2</sup>/V·s, SS= 0.39 V/dec.,  $I_{on}/I_{off}$ = 5.6×10<sup>5</sup>) were achieved due to the high dielectric constant of HfO<sub>2</sub>-based film ( $\epsilon_r$ =26). Although it was necessary to apply bias stress for a long time for program and erase operation, the SnO/Al:HfO<sub>2</sub>/SiO<sub>2</sub> stacked TFTs demonstrated electrical programmable and erasable characteristics as well as data retention capability. Therefore, SnO TFT devices can be used for memory devices as well as electronic circuits according to IL materials with different

hysteresis characteristics.

Keywords: p-type tin monoxide, atomic layer deposition, oxide thin-film

transistors, interfacial layer, diffusion barrier, high-k gate

dielectric, hysteresis voltage, threshold voltage, trap states, charge

trapping, oxygen vacancy, ionic charge effect

**Student Number: 2014-21554**

Younjin Jang

iv

## **Table of Contents**

|    | Abst  | racti                                                      |

|----|-------|------------------------------------------------------------|

|    | Table | e of Contentsv                                             |

|    | List  | of Figuresix                                               |

|    | List  | of Tablesxxviii                                            |

|    | List  | of Abbreviationsxxix                                       |

| 1. | In    | troduction1                                                |

|    | 1.1.  | Overview1                                                  |

|    | 1.2.  | Bibliography5                                              |

| 2. | Li    | terature 8                                                 |

|    | 2.1.  | The overview of p-type oxide semiconductors                |

|    | 2.2.  | The p-type SnO                                             |

|    | 2.3.  | The p-type SnO thin films grown by ALD and its application |

|    |       | to TFTs22                                                  |

|    | 2.4.  | Bibliography30                                             |

| 3. | Cł    | naracterizations of p-type SnO thin films grown by         |

|    | ato   | omic layer deposition (ALD) and its application to         |

|    | TF    | TTs                                                        |

| 3.1. Process development of the ALD SnO                          |

|------------------------------------------------------------------|

| 3.1.1. Introduction                                              |

| 3.1.2. Experimental procedure                                    |

| 3.1.3. Results and discussion                                    |

| 3.1.4. Summary                                                   |

| 3.2. ALD SnO thin film to channel layer of TFT device 55         |

| 3.2.1. Introduction                                              |

| 3.2.2. Experimental procedure                                    |

| 3.2.3. Results and discussion                                    |

| 3.2.4. Summary                                                   |

| 3.3. Bibliography                                                |

| Reduction of the Hysteresis Voltage in Atomic-layer-             |

| deposited p-Type SnO Thin-Film Transistors by                    |

| Adopting Al <sub>2</sub> O <sub>3</sub> Interfacial Layer TFTs74 |

| 4.1. Bulk effect on hysteresis behavior of ALD SnO TFTs 74       |

| 4.1.1. Introduction                                              |

| 4.1.2. Experimental procedure                                    |

| 4.1.3. Results and discussion                                    |

4.

|    | 4.1.4.                                                              | Summary76                                                                                                |

|----|---------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|

|    | 4.2.                                                                | Interfacial effect on hysteresis behavior of ALD SnO TFTs 78                                             |

|    | 4.2.1.                                                              | Introduction                                                                                             |

|    | 4.2.2.                                                              | Experimental procedure                                                                                   |

|    | 4.2.3.                                                              | Results and discussion                                                                                   |

|    | 4.2.4.                                                              | Summary                                                                                                  |

|    | 4.3.                                                                | Bibliography                                                                                             |

| 5. | Exa                                                                 | amination of Abnormal Electrical Properties in                                                           |

|    | Cm                                                                  | O deviges with Al-O- intenferial lever 122                                                               |

|    | Silv                                                                | O devices with Al <sub>2</sub> O <sub>3</sub> interfacial layer 122                                      |

|    |                                                                     | Effects of mobile oxygen vacancies within Al <sub>2</sub> O <sub>3</sub> film on gate                    |

|    |                                                                     |                                                                                                          |

|    | 5.1.                                                                | Effects of mobile oxygen vacancies within Al <sub>2</sub> O <sub>3</sub> film on gate                    |

|    | <ul><li>5.1.</li><li>5.1.1.</li></ul>                               | Effects of mobile oxygen vacancies within Al <sub>2</sub> O <sub>3</sub> film on gate voltage dependence |

|    | <ul><li>5.1.</li><li>5.1.1.</li><li>5.1.2.</li></ul>                | Effects of mobile oxygen vacancies within Al <sub>2</sub> O <sub>3</sub> film on gate voltage dependence |

|    | <ul><li>5.1.</li><li>5.1.1.</li><li>5.1.2.</li><li>5.1.3.</li></ul> | Effects of mobile oxygen vacancies within Al <sub>2</sub> O <sub>3</sub> film on gate voltage dependence |

|    | <ul><li>5.1.</li><li>5.1.1.</li><li>5.1.2.</li><li>5.1.3.</li></ul> | Effects of mobile oxygen vacancies within $Al_2O_3$ film on gate voltage dependence                      |

|    | 5.2.1 | . Introduction                                               |

|----|-------|--------------------------------------------------------------|

|    | 5.2.2 | . Experimental procedure                                     |

|    | 5.2.3 | . Results and discussion                                     |

|    | 5.2.1 | . Summary                                                    |

|    | 5.3.  | Bibliography                                                 |

| 6. | Im    | provement of Electrical Properties in SnO TFTs               |

|    | wit   | th HfO <sub>2</sub> -based interfacial layer176              |

|    | 6.1.  | A Study on the factors that determine the performance of SnO |

|    |       | TFTs adopting a high-k Al:HfO <sub>2</sub> IL                |

|    | 6.1.1 | . Introduction                                               |

|    | 6.1.2 | . Experimental procedure                                     |

|    | 6.1.3 | . Results and discussion                                     |

|    | 6.1.4 | . Summary                                                    |

|    | 6.2.  | Bibliography                                                 |

| 7. | Co    | onclusion203                                                 |

| Ał | strac | ct (in Korean)205                                            |

# **List of Figures**

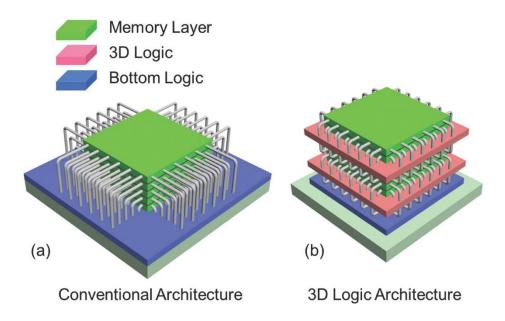

| Figure 2.1. Schematic diagrams of (a) a conventional and (b) a three-          |

|--------------------------------------------------------------------------------|

| dimensional stacked architecture between logic circuits and                    |

| memory layers11                                                                |

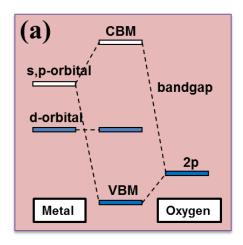

| Figure 2.2. Schematic energy diagrams of (a) n-type and (b) p-type oxide       |

| semiconductors                                                                 |

| Figure 2.3. Schematic diagram of sub-gap density of states for oxide           |

| semiconductors                                                                 |

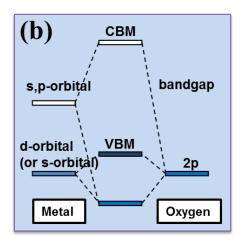

| Figure 2.4. Results of high-speed computational screening of two- and three-   |

| component substances using a hydrogen selector. FEH> -1 eV                     |

| region corresponds to the p-type oxide candidate group that                    |

| guarantees transparency                                                        |

| Figure 2.5. Simplified band structures of oxide semiconductors. (a) Typical n- |

| type oxide semiconductor, (b) Cu+-based p-type oxide                           |

| semiconductor, (c) Oxychalcogenide-based p-type oxide                          |

| semiconductor                                                                  |

| Figure 2.6. The crystal structure of SnO material                                       |

|-----------------------------------------------------------------------------------------|

| Figure 2.7. Band structure (left) and density of states (right) of the unit cell of     |

| the SnO perfect crystal                                                                 |

| Figure 2.8. Formation energies as a function of the Fermi level when SnO is in          |

| O-rich condition                                                                        |

| Figure 2.9. Phase diagram as function of temperature and atomic ratio between           |

| Sn and O                                                                                |

| Figure 2.10. (a) XRD spectra and (b) schematic phase classification of $\text{SnO}_{X}$ |

| films with different rf sputtering power, annealing temperature,                        |

| and atmosphere24                                                                        |

| Figure 2.11. Schematic diagram of the mechanism of ALD process 25                       |

| Figure 2.12. The first report on p-type SnO thin-film using ALD method 27               |

| Figure 2.13. Schematic summary of the potential instabilities in the oxide TFTs.        |

| 29                                                                                      |

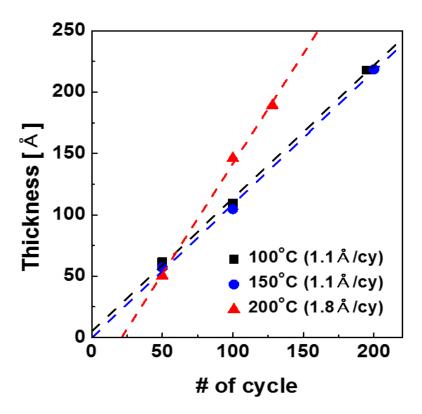

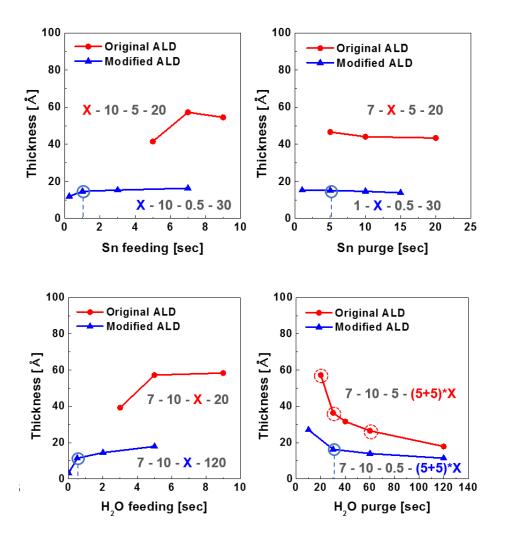

| Figure 3.1. Saturation behaviors of SnO ALD                                             |

| Figure 3.2. Growth rate of SnO thin film depending on the deposition                    |

| temperature44                                                                           |

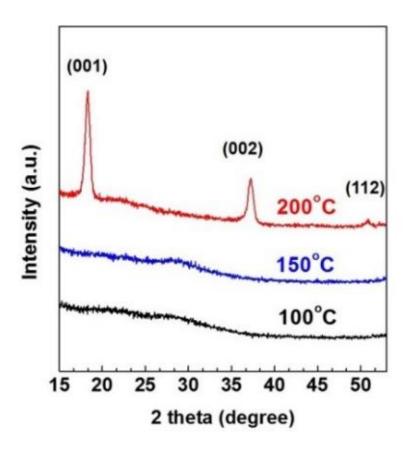

| Figure 3.3. GAXRD spectra of ALD SnO thin film depending on the depositio |

|---------------------------------------------------------------------------|

| temperature4                                                              |

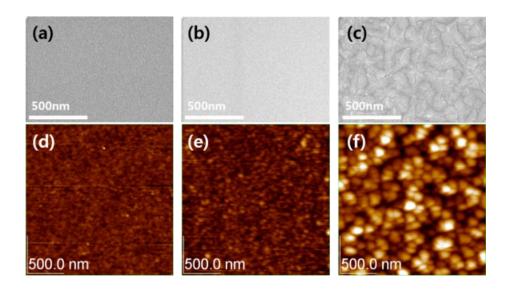

| Figure 3.4. Topological images by (a–c) SEM and (d–f) AFM of ALD SnO thi  |

| film depending on the deposition temperature of (a, d) 100 °C, (b         |

| e) 150 °C, and (c, f) 200 °C                                              |

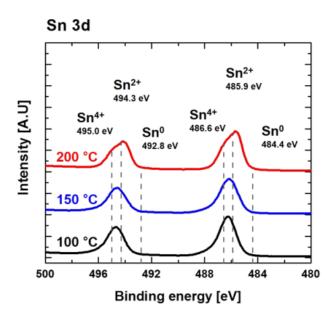

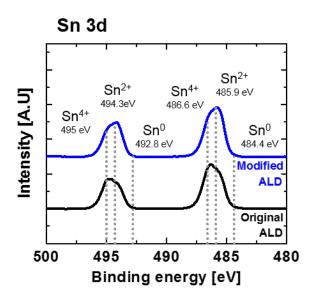

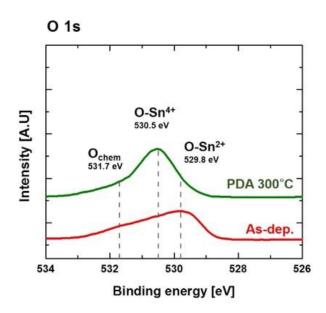

| Figure 3.5. XPS spectra of (a) Sn 3d and (b) O 1s of ALD SnO thin film    |

| depending on the deposition temperature 4                                 |

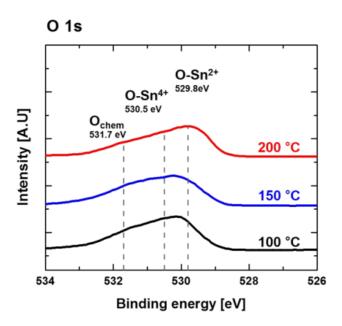

| Figure 3.6. AES analysis of ALD SnO thin film depending on the depositio  |

| temperature4                                                              |

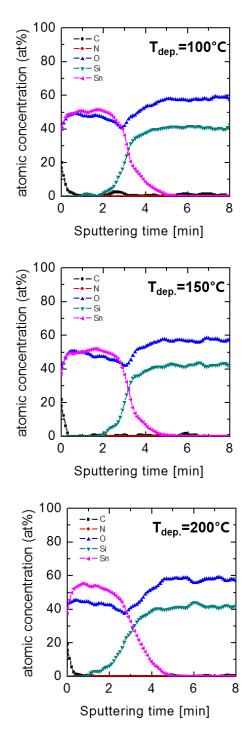

| Figure 3.7. XRR measurement of ALD SnO thin film depending on the         |

| deposition temperature4                                                   |

| Figure 3.8. Saturation behaviors of SnO thin film deposited at 200 °C     |

| depending on the injection time of both Sn precursor and oxyge            |

| source 5                                                                  |

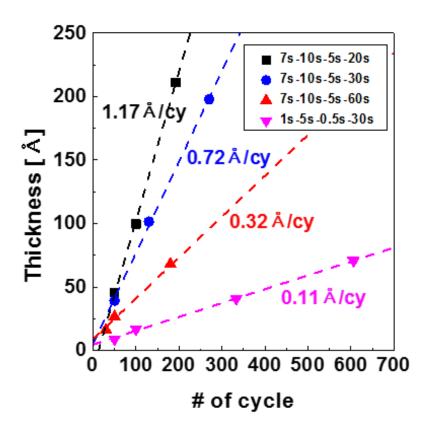

| Figure 3.9. The change of growth rate SnO thin film with various ALI      |

| sequence 5                                                                |

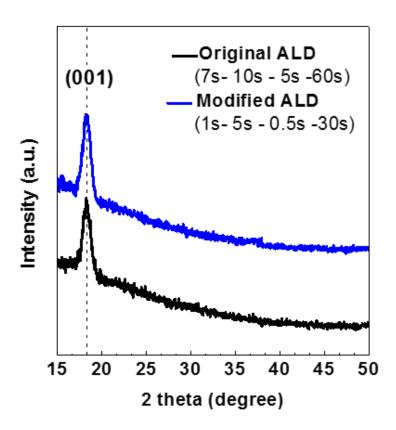

| Figure 3.10. GAXRD spectra of the SnO thin film with different ALI        |

| sequences                                                                                             |

|-------------------------------------------------------------------------------------------------------|

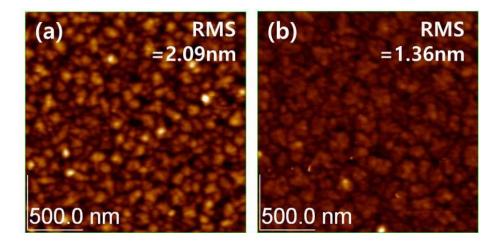

| Figure 3.11. Surface images of SnO thin film with different ALD sequence. (a)                         |

| the original sequence (7 s $-$ 10 s $-$ 5 s $-$ 60 s) and (b) modified                                |

| sequence (1 s – 5 s – 0.5 s – 30 s)                                                                   |

| Figure 3.12. XPS spectra of SnO thin film with different ALD sequence 54                              |

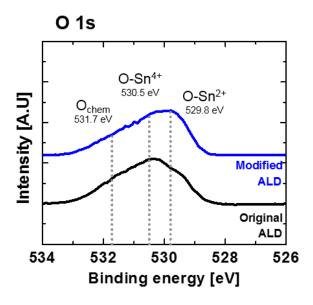

| Figure 3.13. Sheet resistance and the resistivity of ALD SnO thin film measured                       |

| by four-point probe                                                                                   |

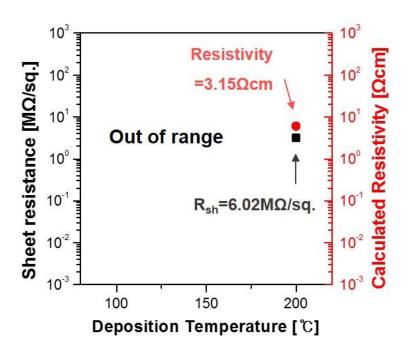

| Figure 3.14. Schematic diagram of the fabrication of ALD SnO TFT and optical                          |

| microscope image of the top view of the channel region of                                             |

| fabricated SnO TFT device                                                                             |

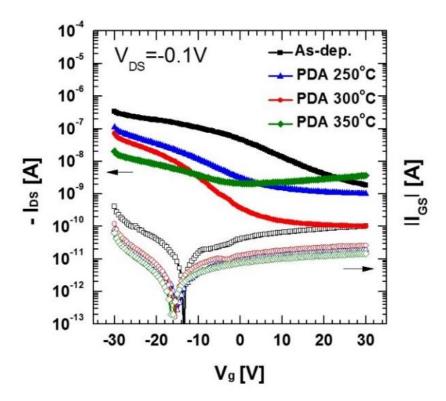

| Figure 3.15. $V_{\text{GS}}\text{-}I_{\text{DS}}$ characteristics of ALD SnO TFT depending on the PDA |

| temperature                                                                                           |

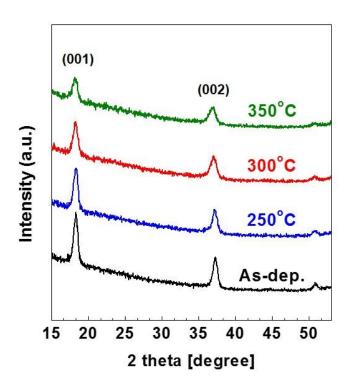

| Figure 3.16. GAXRD spectra of ALD SnO thin film depending on the PDA                                  |

| temperature67                                                                                         |

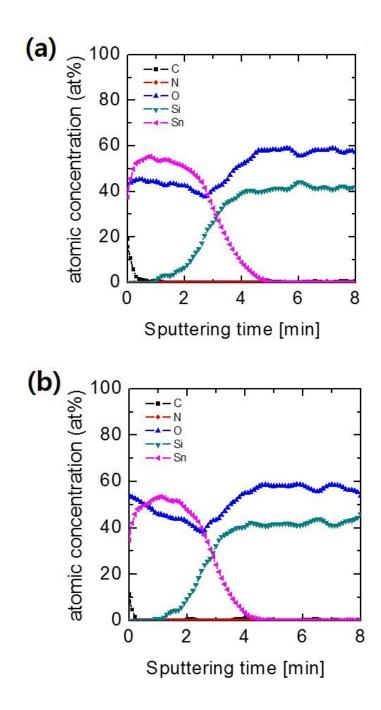

| Figure 3.17. AES spectra ALD SnO TFT (a) before PDA and (b) after PDA at                              |

| 300 °C                                                                                                |

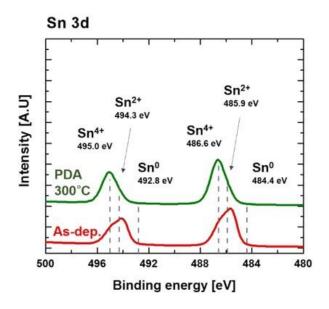

| Figure 3.18. XPS spectra of Sn 3d (upper) and O 1s (lower) of ALD SnO TFT                             |

|               | before and after PDA                                                                        |

|---------------|---------------------------------------------------------------------------------------------|

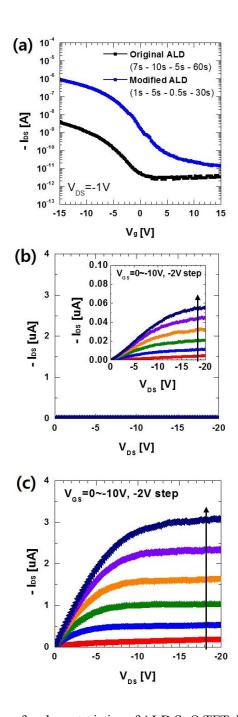

| Figure 3.19.  | (a) Transfer characteristics of ALD SnO TFT device with different                           |

|               | sequence, and its output characteristics fabricated by (b) original                         |

|               | sequence (7 s $-$ 10 s $-$ 5 s $-$ 60 s) and (c) modified sequence (1 s $-$                 |

|               | 5 s - 0.5 s - 30 s)                                                                         |

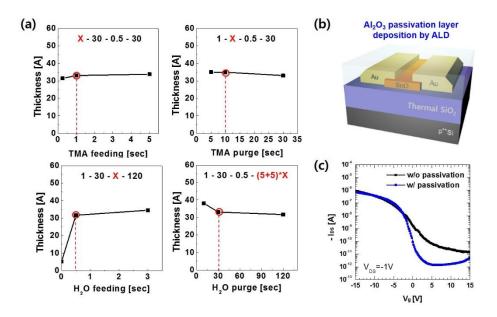

| Figure 3.20   | . (a) Saturation behavior of ALD Al <sub>2</sub> O <sub>3</sub> , (b) a schematic device of |

|               | of SnO TFT using ALD Al <sub>2</sub> O <sub>3</sub> as a passivation layer, and (c)         |

|               | transfer characteristics of SnO TFT device with and without ALD                             |

|               | Al <sub>2</sub> O <sub>3</sub> passivation layer                                            |

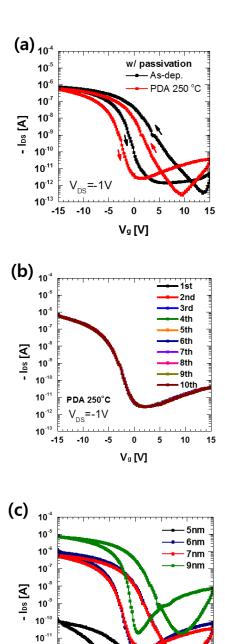

| Figure 4.1. ( | (a) Transfer curve of ALD SnO TFT before and after PDA at 250 °C                            |

|               | showing hysteresis behaviors, (b) multiple sweep of transfer curve,                         |

|               | and (c) the change of hysteresis behavior depending on the                                  |

|               | thickness of SnO channel                                                                    |

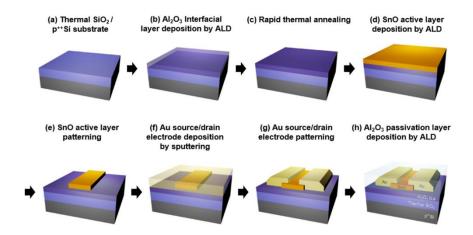

| Figure 4.2.   | Schematics of the fabrication process of ALD SnO thin film                                  |

|               | transistors, in which annealed Al <sub>2</sub> O <sub>3</sub> ILs were inserted between the |

|               | SnO active layer and the SiO <sub>2</sub> gate insulator                                    |

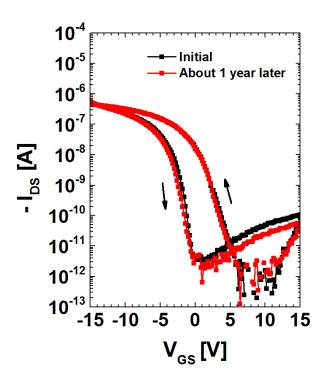

| Figure 4.3. 1 | Long-term stability of ALD SnO TFTs with a passivation layer. Here,                         |

the transfer characteristics of the SnO TFTs without ILs are shown. During each measurement, the devices were stored at room temperature. The passivated SnO TFTs exhibit remarkable stability over one year without degradation of on current and  $V_{th}$ . This result shows that the passivation layer effectively suppresses the oxidation reaction from SnO to SnO<sub>2</sub>, and TFT devices can maintain stable electrical characteristics for such a long period.

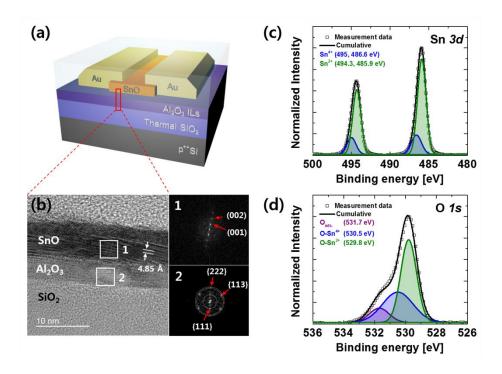

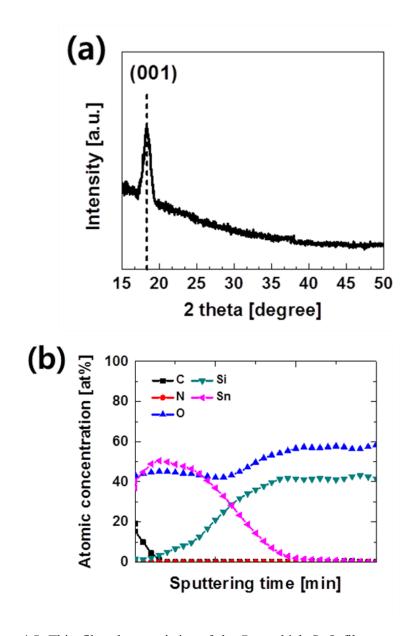

Figure 4.4. (a) Schematics of the ALD SnO TFTs with Al<sub>2</sub>O<sub>3</sub> ILs. (b) HRTEM images of the cross-section in the SnO(7 nm)/Al<sub>2</sub>O<sub>3</sub>(5 nm, RTA 1000 °C)/SiO<sub>2</sub> sample. 1 and 2 show the FFT patterns for a selected area corresponding to the tetragonal SnO, and partially crystallized Al<sub>2</sub>O<sub>3</sub>, respectively. XPS spectra of the (c) Sn *3d* and (d) O *1s* core levels for the 7-nm-thick SnO films grown on a

Figure 4.5. Thin film characteristics of the 7-nm-thick SnO films grown on SiO<sub>2</sub>/Si substrate measured by (a) GAXRD, (b) AES depth

SiO<sub>2</sub>/Si substrate......99

|             | profiling                                                                                |

|-------------|------------------------------------------------------------------------------------------|

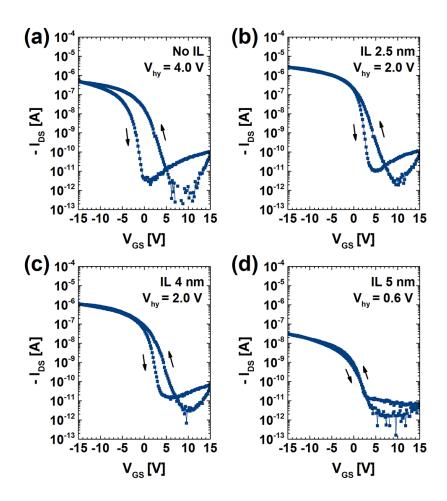

| Figure 4.6. | Transfer characteristics of the SnO TFTs (a) without ILs and with                        |

|             | (b) 2.5-nm-thick, (c) 4-nm-thick, and (d) 5-nm-thick Al <sub>2</sub> O <sub>3</sub> ILs, |

|             | respectively. In the cases where $Al_2O_3$ ILs were inserted, the ILs                    |

|             | were annealed at 1000 $^{\circ}\text{C}$ via RTA. The $V_{DS}$ was fixed at $-1~V$ in    |

|             | all the cases                                                                            |

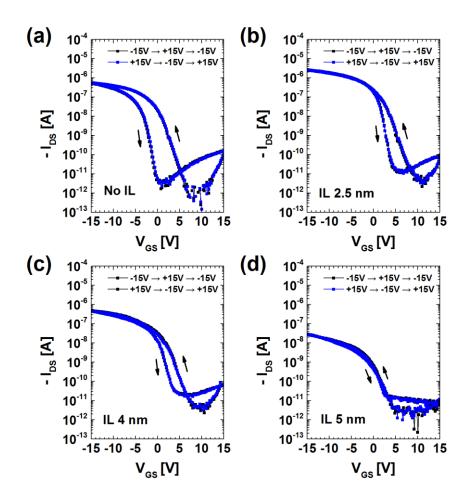

| Figure 4.7. | Transfer characteristics of the SnO TFTs measured with the different                     |

|             | starting $V_{GS}$ and a given $V_{DS}$ of $-1$ V. The devices (a) without ILs            |

|             | and with (b) 2.5-nm-thick, (c) 4-nm-thick, and (d) 5-nm-thick                            |

|             | Al <sub>2</sub> O <sub>3</sub> ILs                                                       |

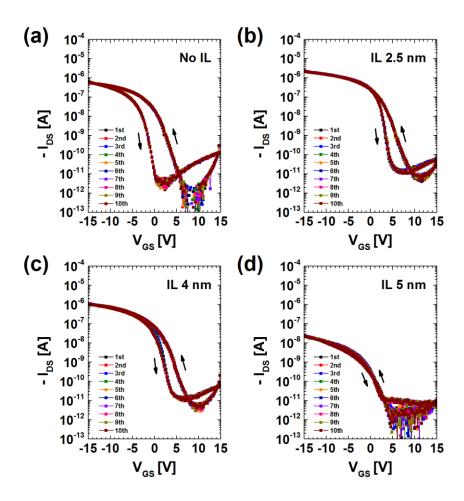

| Figure 4.8. | Transfer characteristics of the SnO TFTs measured by 10 times                            |

|             | repetition of the $V_{GS}$ sweep at $V_{DS}$ of $-1$ V. The devices (a) without          |

|             | ILs and with (b) 2.5-nm-thick, (c) 4-nm-thick, and (d) 5-nm-thick                        |

|             | Al <sub>2</sub> O <sub>3</sub> ILs                                                       |

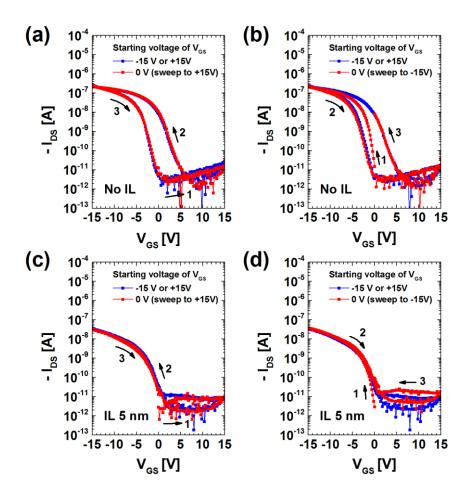

| Figure 4.9. | Transfer characteristics of the SnO TFTs measured with the 0 V                           |

|             | starting $V_{\text{GS}}$ and a given $V_{\text{DS}}$ of –1 V. The devices without ILs    |

|             | starting with (a) forward gate voltage sweep (0 V $\rightarrow$ +15 V $\rightarrow$ –    |

|              | 15 V $\rightarrow$ 0 V) and (b) backward gate voltage sweep (0 V $\rightarrow$ -15 V                            |

|--------------|-----------------------------------------------------------------------------------------------------------------|

|              | $\rightarrow$ +15 V $\rightarrow$ 0 V). The devices with 5-nm-thick Al <sub>2</sub> O <sub>3</sub> ILs starting |

|              | with (c) forward gate voltage sweep (0 V $\rightarrow$ +15 V $\rightarrow$ -15 V $\rightarrow$                  |

|              | 0 V) and (d) backward gate voltage sweep (0 V $\rightarrow$ –15 V $\rightarrow$ +15                             |

|              | $V \to 0 V$ )                                                                                                   |

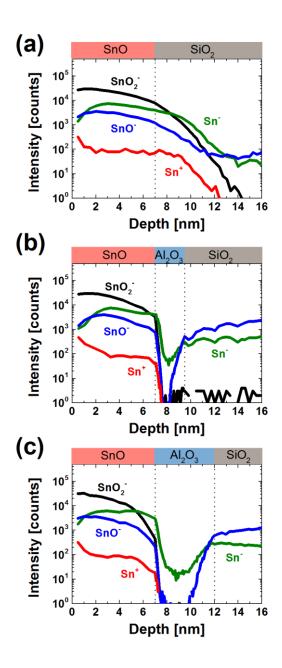

| Figure 4.10  | . TOF-SIMS depth profiles related to Sn of the SnO thin films (a)                                               |

|              | without an IL and with (b) a 2.5-nm-thick IL and (c) a 5-nm-thick                                               |

|              | IL annealed at 1000 °C via RTA                                                                                  |

| Figure 4.11. | TOF-SIMS depth profiles of the SnO thin films (a) without an IL                                                 |

|              | and with (b) a 2.5-nm-thick IL and (c) a 5-nm-thick IL annealed at                                              |

|              | 1000 °C via RTA, respectively                                                                                   |

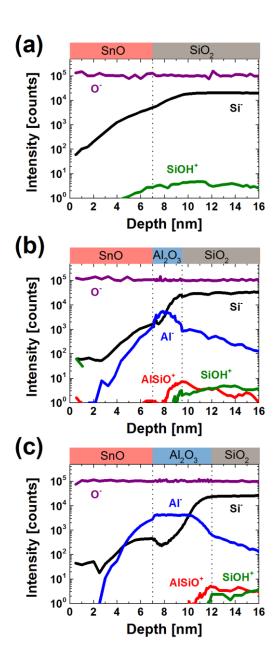

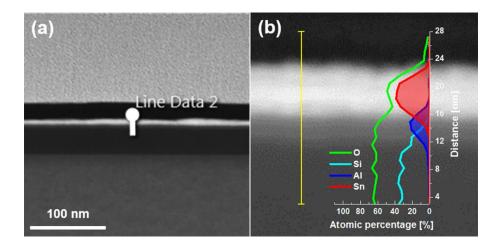

| Figure 4.12  | 2. Nanochemical analysis for the cross section in the SnO(7                                                     |

|              | nm)/Al $_2$ O $_3$ (5 nm, RTA 1000 °C)/SiO $_2$ sample. (a) STEM image                                          |

|              | showing a region where EDS line scan is performed. (b) The                                                      |

|              | elemental line profiles for O (green), Si (cyan), Al (blue), Sn (red)                                           |

|              | revealed by STEM-EDS measurement. The vertical axis is the                                                      |

|              | distance from the SiO <sub>2</sub> gate insulator to carbon-coated SnO layer,                                   |

|              | whereas the horizontal axis is the atomic fraction of each species.                                                                                     |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

|              |                                                                                                                                                         |

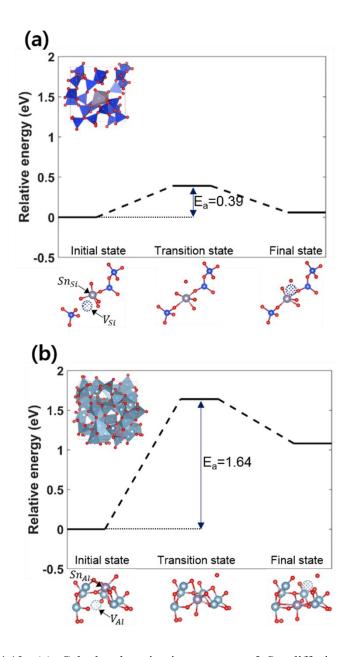

| Figure 4.13  | 3. (a) Calculated activation energy of Sn diffusion from one                                                                                            |

|              | substitutional site to the nearest substitutional site: (a) $Sn_{Si}^{+0}$ in                                                                           |

|              | am-SiO <sub>2</sub> and (b) $Sn_{Al}^{-1}$ in am-Al <sub>2</sub> O <sub>3</sub>                                                                         |

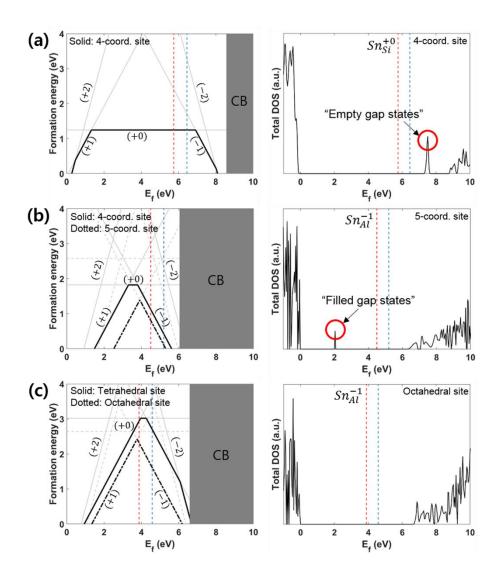

| Figure 4.14. | Calculated formation energy of the Sn substitutional defects in the                                                                                     |

|              | several charged states and density of states (DOSs) of the most                                                                                         |

|              | energetically stable charged state in the SnO bandgap range: (a)                                                                                        |

|              | $Sn_{Si}$ in am-SiO <sub>2</sub> ; (b) $Sn_{Al}$ in am-Al <sub>2</sub> O <sub>3</sub> ; and (c) $Sn_{Al}$ in $\gamma$ -Al <sub>2</sub> O <sub>3</sub> . |

|              | The dashed red and blue lines indicate the aligned VBM and CBM                                                                                          |

|              | of SnO, respectively110                                                                                                                                 |

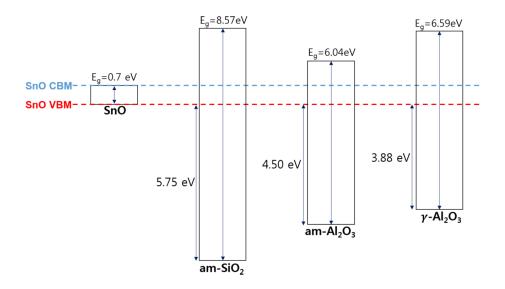

| Figure 4.15  | . Calculated band gap and band alignment of each oxide. Averaged                                                                                        |

|              | electrostatic potential (AEP) was calculated with respect to the                                                                                        |

|              | vacuum level in the slab structure using PBE functional, and the                                                                                        |

|              | position of VBM was calculated in the bulk structure using HSE                                                                                          |

|              | functional with the optimized fraction $\alpha$ of Fock exchange:                                                                                       |

|              | $\alpha=0.32$ for SnO $\alpha=0.45$ for SiO <sub>2</sub> and $\alpha=0.32$ for Al <sub>2</sub> O <sub>2</sub> . The                                     |

|              | validity and effectiveness of this calculation approach were                                                    |

|--------------|-----------------------------------------------------------------------------------------------------------------|

|              | reported in the previous literature111                                                                          |

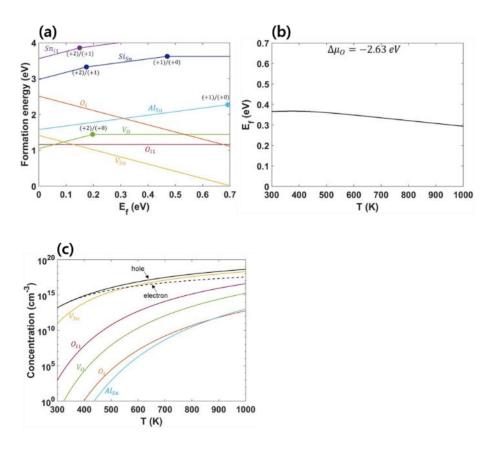

| Figure 4.16. | (a) Calculated formation energy of defects in SnO, (b) electronic                                               |

|              | potential satisfying charge neutrality in SnO at the fixed $\mu_0$ , and                                        |

|              | (c) concentration of defects and charge carriers in SnO. Two types                                              |

|              | of the interstitial site were considered following the previous                                                 |

|              | research: 4-coordinate site denoted as $O_i$ and 5-coordinate site                                              |

|              | denoted as $O_{i1}$ for oxygen interstitials. Note that interstitial                                            |

|              | defects generated by cation (Si or Al) diffusion from GI oxides to                                              |

|              | SnO channel, ex. $Al_i$ and $Al_{i1}$ , were also calculated but the                                            |

|              | interstitial defects were identified to have higher energy than                                                 |

|              | substitutional defects and not denoted in this figure112                                                        |

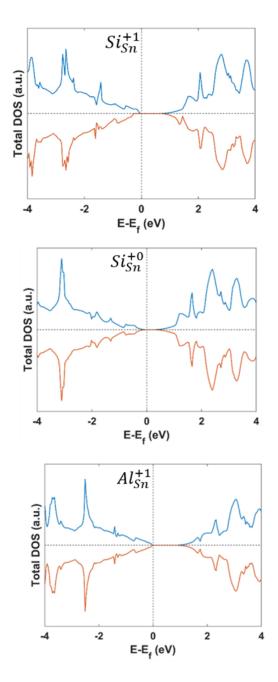

| Figure 4.17. | Calculated DOSs of substitutional defects generated by cation (Si                                               |

|              | or Al) diffusion from GI oxides to SnO active layer in the                                                      |

|              | energetically stable charged states113                                                                          |

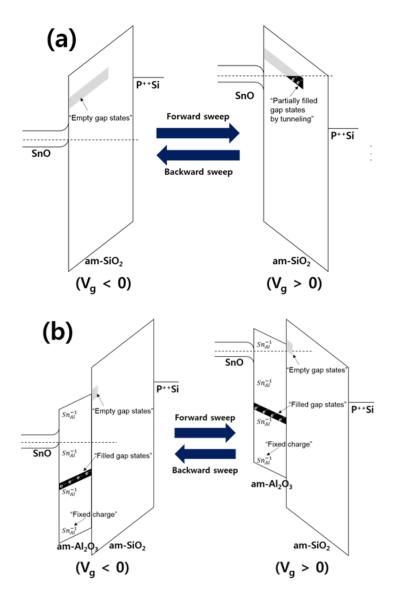

| Figure 4.18  | . Schematic band diagrams of (a) SnO/am-SiO <sub>2</sub> /p <sup>++</sup> Si and (b)                            |

|              | SnO/am-Al <sub>2</sub> O <sub>3</sub> /am-SiO <sub>2</sub> /p <sup>++</sup> Si. Note that the positions of VBM, |

|             | CBM, and the gap states of defects are aligned according to the                                             |

|-------------|-------------------------------------------------------------------------------------------------------------|

|             | band alignment and DOS calculations                                                                         |

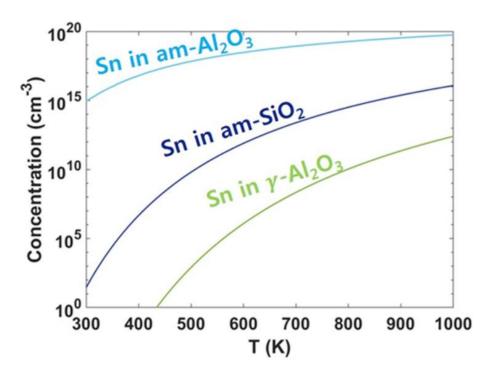

| Figure 4.19 | . Calculated defect concentration of $Sn_{Si}$ in am-SiO <sub>2</sub> , $Sn_{Al}$ in am-                    |

|             | $Al_2O_3$ , and $Sn_{Al}$ in $\gamma$ - $Al_2O_3$ in the electrochemical equilibrium                        |

|             | condition without gate bias: $E_f$ =[VBO of each oxide]+[electronic                                         |

|             | potential satisfying charge neutrality in SnO], and $\mu_{O(SnO)} =$                                        |

|             | $\mu_{O(SiO_2)} = \mu_{O(Al_2O_3)} = \frac{1}{2}\mu_{O_2(gas)} - 2.63 \text{ eV}.$ 115                      |

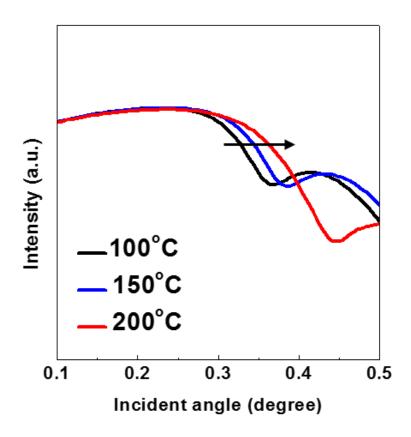

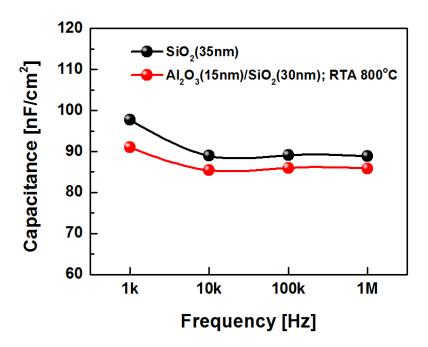

| Figure 4.20 | . Capacitance vs. frequency measured in the metal/dielectric/metal                                          |

|             | configuration using two different gate dielectrics: One is the SiO <sub>2</sub>                             |

|             | (35 nm), and the other is $Al_2O_3$ (15 nm)/SiO <sub>2</sub> (30 nm). In the cases                          |

|             | of the Al <sub>2</sub> O <sub>3</sub> /SiO <sub>2</sub> gate dielectrics, the films were annealed at 800 °C |

|             | via RTA116                                                                                                  |

| Figure 4.21 | . Transfer characteristics of the SnO TFT with 15-nm-thick ILs                                              |

|             | annealed at (a) 800 °C and (b) 1000 °C via RTA. (c) GAXRD                                                   |

|             | spectra of the 15-nm-thick Al <sub>2</sub> O <sub>3</sub> films by RTA temperature. (d) Al                  |

|             | 2n XPS spectra of the AlaOa(15 nm)/SiOa and SnO(7                                                           |

nm)/Al $_2O_3(15 \text{ nm})/SiO_2$  samples, in which the Al $_2O_3$  films were

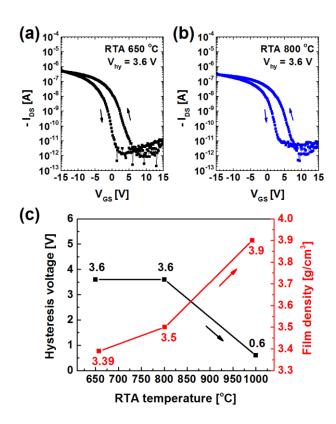

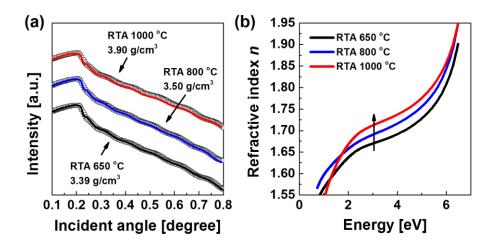

annealed at 800 °C (bottom) and 1000 °C (top), respectively..117 Figure 4.22. Transfer characteristics of the SnO TFT with a 5-nm-thick IL annealed at (a) 650 °C and (b) 800 °C via RTA. The result of the SnO TFT with an IL annealed at 1000 °C was not included in this figure. (c) Hysteresis voltage in the transfer characteristics and  $Al_2O_3$  film density of the 5-nm-thick ILs extracted from XRR fitting as a function of the RTA temperatures from 650 to 1000 °C.

Figure 5.1. Schematic diagrams of the p-type SnO TFTs with (a)  $SiO_2$  and (b)  $Al_2O_3/SiO_2$  gate dielectric layers. (c) The  $I_{DS}$ - $V_{GS}$  characteristics

|               | measured in the FW and BW sweeps for both the (a) and (b)                           |

|---------------|-------------------------------------------------------------------------------------|

|               | devices                                                                             |

| Figure 5.2. V | Variations in $V_{th}$ as a function of the sweep range of the (a) positive         |

|               | $V_{GS}$ with a fixed $-V_{GS,max}(-15~V)$ , and of the (b) negative $V_{GS}$ with  |

|               | a fixed $+V_{GS, max}$ (+15 V). (c) Calculated $V_{hy}$ from the data shown         |

|               | in (a) and (b) for each device                                                      |

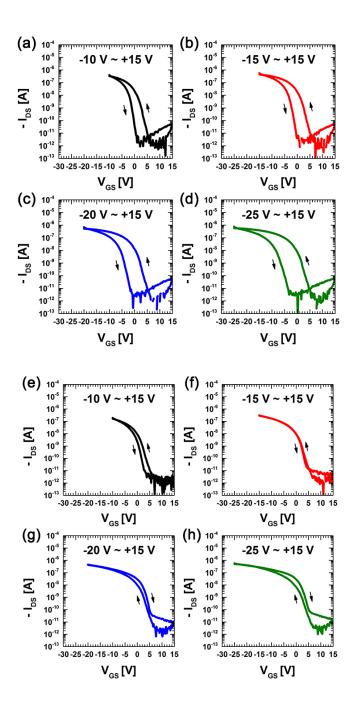

| Figure 5.3.   | Transfer characteristics of SnO TFTs with (a-d) SiO <sub>2</sub> and (e-h)          |

|               | $Al_2O_3/SiO_2$ gate dielectric layers, at drain voltage ( $V_{DS}$ )= -1 $V$ ,     |

|               | with the changes of the sweep range of the positive gate voltage                    |

|               | ( $V_{GS}$ ). The sweep range of the negative $V_{GS}$ was fixed at $-15~V_{\odot}$ |

|               |                                                                                     |

| Figure 5.4.   | Transfer characteristics of SnO TFTs with (a-d) SiO <sub>2</sub> and (e-h)          |

|               | $Al_2O_3/SiO_2$ gate dielectric layers, at $V_{DS}$ = -1 V, with the changes        |

|               | of the sweep range of the negative $V_{\text{GS}}$ . The sweep range of the         |

|               | positive V <sub>GS</sub> was fixed at +15 V                                         |

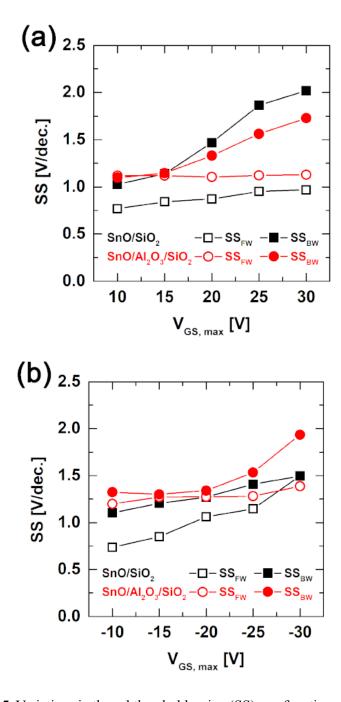

| Figure 5.5. V | /ariations in the subthreshold swing (SS) as a function of the sweep                |

|               | range of the (a) positive $V_{GS}$ with a fixed $-V_{GS, max}$ (-15 V), and of      |

| the (b) negative $V_{GS}$ with a fixed $+V_{GS, max}(+15 \text{ V})$                                    |

|---------------------------------------------------------------------------------------------------------|

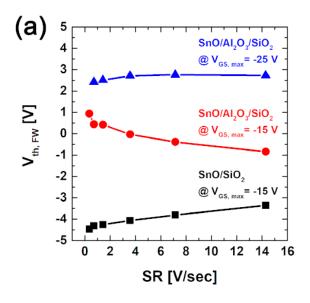

| Figure 5.6. (a) Plot of $V_{th,FW}$ as a function of $V_{GS}$ SR with a fixed $+V_{GS,max}$ (+15)       |

| V). (b) $V_{\text{th}}$ shift of two stacks as a function of stress time. Here, the                     |

| $V_{GS}$ was maintained at $-15\ V$ (black square, red dot) and $-25\ V$                                |

| (blue triangle), respectively, while the source and drain were                                          |

| grounded140                                                                                             |

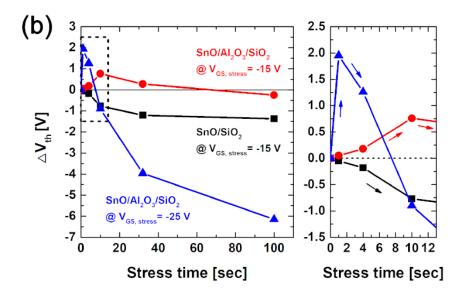

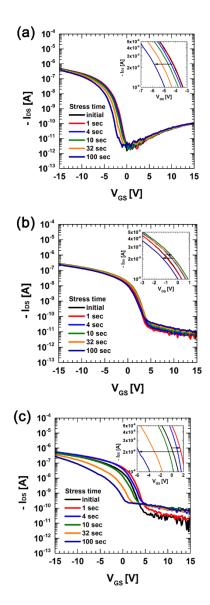

| Figure 5.7. Evolution of the transfer characteristics for SnO TFTs with (a) SiO <sub>2</sub>            |

| and (b, c) Al <sub>2</sub> O <sub>3</sub> /SiO <sub>2</sub> gate dielectric layers as a function of the |

| negative bias stress (NBS) time. Here, the $V_{\text{GS}}$ was maintained at                            |

| -15 V for (a) and (b), and -25 V for (c), while the source and drain                                    |

| were grounded. The insets in (a-c) show an enlarged view of the                                         |

| transfer curve, and arrows indicate the direction of movement of                                        |

| the curve                                                                                               |

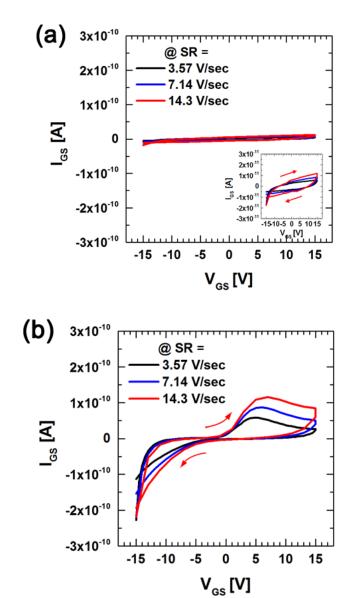

| Figure 5.8. Displacement current (I <sub>GS</sub> ) between the gate and a grounded source              |

| electrode vs. the applied $V_{GS}$ through the (a) $SnO/SiO_2$ and (b)                                  |

| $SnO/Al_2O_3/SiO_2$ stacks with different $V_{GS}$ SRs. The inset in (a)                                |

| shows an enlarged view of the curve, and the arrows show the                                            |

|               | direction of the curves according to the $V_{GS}$ sweep                                  |

|---------------|------------------------------------------------------------------------------------------|

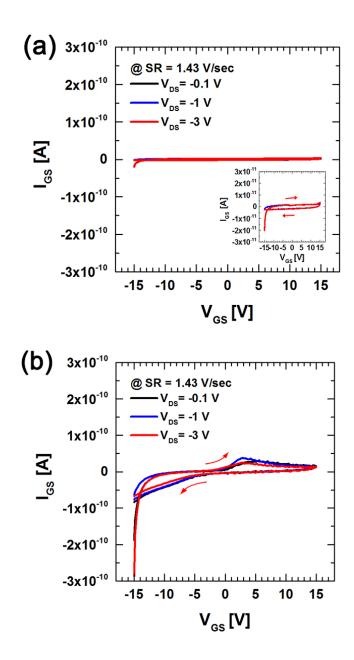

| Figure 5.9. I | Displacement current (I <sub>GS</sub> ) between the gate and a grounded source           |

|               | electrode vs. the applied $V_{GS}$ through the (a) $SnO/SiO_2$ and (b)                   |

|               | $SnO/Al_2O_3/SiO_2$ stacks with different $V_{DS}.$ The arrows show the                  |

|               | direction of the curves according to the $V_{GS}$ sweep                                  |

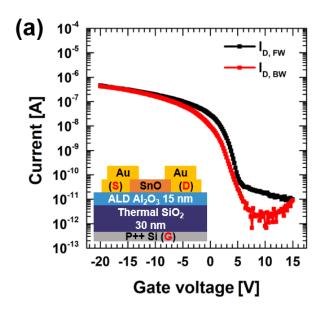

| Figure 5.10   | . (a) The transfer characteristic of the TFT device, and (b) the                         |

|               | capacitance voltage characteristic of MOSCAP device. The insets                          |

|               | in (a) and (b) show the schematic diagrams of the TFT and                                |

|               | MOSCAP structures used in this study, respectively 160                                   |

| Figure 5.11.  | The schematic band diagrams summarizing the possible charge                              |

|               | effects due to $V_{O}^{\cdot \cdot \cdot}$ migration in $SnO/Al_2O_3/SiO_2$ gate-stacked |

|               | devices. The red and blue arrows indicate charge behaviors                               |

|               | induced by DC and AC stimulus, respectively                                              |

| Figure 5.12.  | The gate current characteristics in (a) log- and (b) linear-scale of                     |

|               | the TFT devices. (a) Variation of the voltage position for a                             |

|               | minimum current ( $V_{G,min}$ ) in the FW sweep as a function of the                     |

|               | maximum gate voltage ( $V_{G,\ max}$ ), where inset exhibits a linear                    |

| relationship of $V_{G, min} - V_{G, max}$ curve. (b) Variation of the peak                  |

|---------------------------------------------------------------------------------------------|

| values of the current, and the arrows indicate the curve direction                          |

|                                                                                             |

| Figure 5.13. A schematic diagram of the change of E <sub>int.</sub> intensity depending on  |

| the $V_{G, max}$                                                                            |

| Figure 5.14. The schematic diagram of changes in the amount of electrons                    |

| flowing into/out of the gate (or BE) by forming $E_{int.}$ by $V_0^{\cdots}$ 164            |

| Figure 5.15. The gate current characteristics of BW sweep depending on the $V_{\text{G}}$ , |

| max                                                                                         |

| Figure 5.16. (a) The capacitance-voltage characteristic of SnO/SiO <sub>2</sub> stacked     |

| MOSCAP device, and (b) the transfer characteristic of the                                   |

| SnO/SiO <sub>2</sub> stacked TFT device. The insets in (a) and (b) show the                 |

| schematic diagrams of the MOSCAP and TFT structures,                                        |

| respectively166                                                                             |

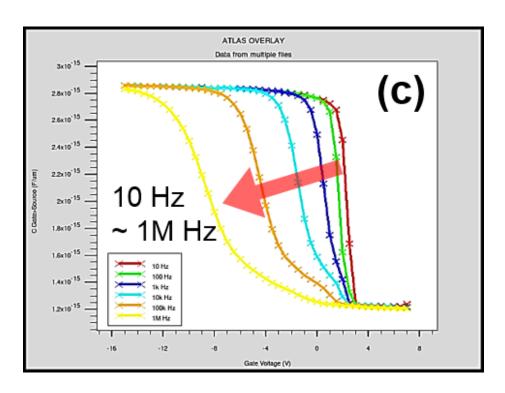

| Figure 5.17. Multi-frequency C-V characteristics for a MOSCAP devices                       |

| measured in (a) FW sweeps and (b) BW sweeps 167                                             |

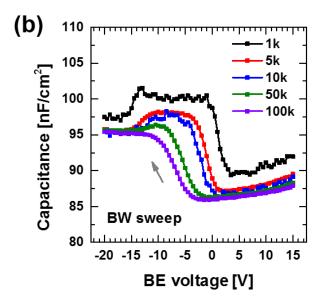

| Figure 5.18. The results of ATLAS simulation or C-V characteristics of ALD                  |

| SnO devices. Figure shows the C-V results according to the density                      |

|-----------------------------------------------------------------------------------------|

| of donor-like band-tail state at frequency of 1 MHz. The unit of                        |

| density in Figure is [cm <sup>-3</sup> ]169                                             |

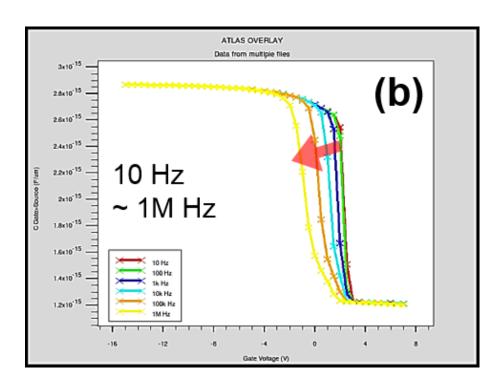

| Figure 5.19. The results of ATLAS simulation or C-V characteristics of ALD              |

| SnO devices. Figure shows the C-V results according to the                              |

| frequency from 10 Hz to 1 MHz with density of donor-like band-                          |

| tail state of $5 \times 10^{20} \text{ cm}^{-3}$                                        |

| Figure 5.20. The results of ATLAS simulation or C-V characteristics of ALD              |

| SnO devices. Figure shows the C-V results according to the                              |

| frequency from 10 Hz to 1 MHz with density of donor-like band-                          |

| tail state of $5 \times 10^{21} \text{ cm}^{-3}$                                        |

| Figure 5.21. The schematic diagram of changes in the AC reactivity of holes to          |

| the E <sub>VO</sub> according to the V <sub>O</sub> position                            |

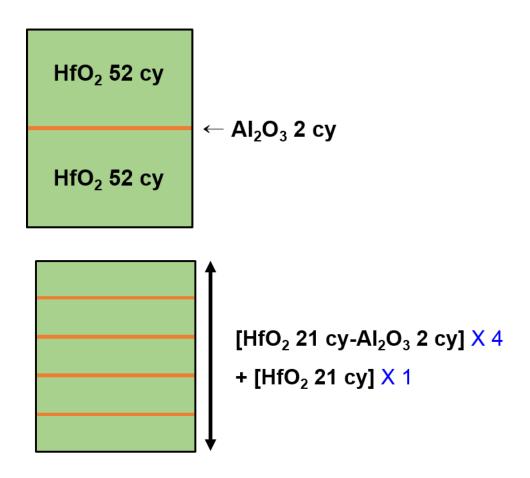

| Figure 6.1. The schematic diagram of Al doping into HfO <sub>2</sub> film using the ALD |

| method                                                                                  |

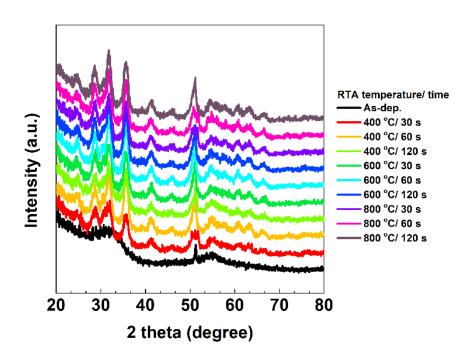

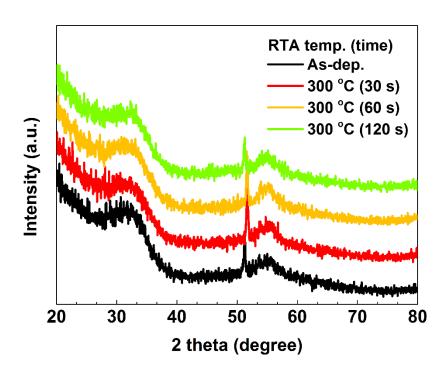

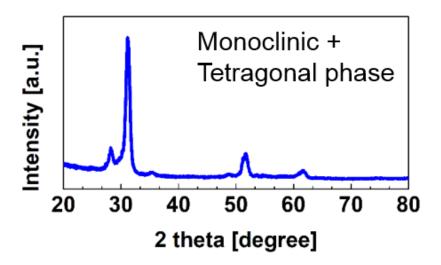

| Figure 6.2. GAXRD results of Al-doping in the center of HfO <sub>2</sub> film according |

| to the RTA temperature (400 – 800 °C) and process time (30 s –                          |

| 120 s)                                                                                                             |

|--------------------------------------------------------------------------------------------------------------------|

| Figure 6.3. GAXRD results of Al-doping in the center of HfO <sub>2</sub> film according                            |

| to the RTA temperature at 300 $^{\circ}$ C and process time (30 s – 120 s).                                        |

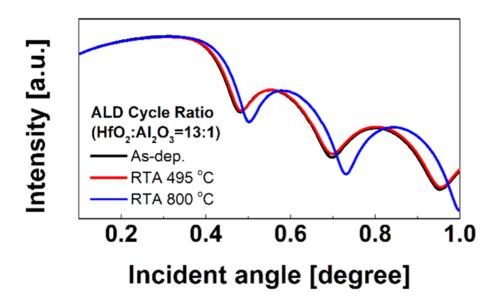

|                                                                                                                    |

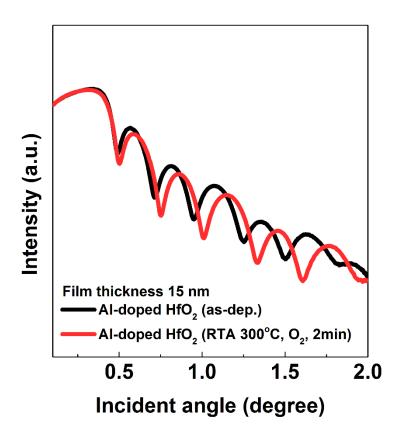

| Figure 6.4. XRR results of Al-doping in the center of HfO <sub>2</sub> film according to                           |

| the RTA temperature at 300 °C for process time of 120 s 188                                                        |

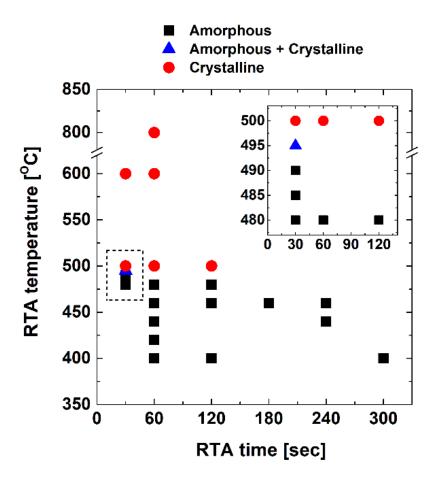

| Figure 6.5. The phase mapping based on GAXRD results of alternate doping of                                        |

| Al with HfO <sub>2</sub> film according to the RTA temperature and process                                         |

| time                                                                                                               |

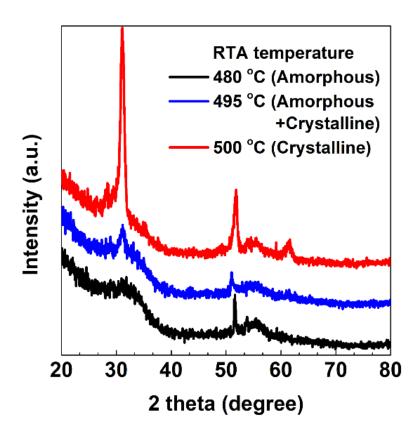

| Figure 6.6. GAXRD results of alternate doping of Al with HfO <sub>2</sub> film according                           |

| to the RTA temperature with process time of 30 s 190                                                               |

| Figure 6.7. The transfer characteristics of SnO TFT with Al <sub>2</sub> O <sub>3</sub> IL and Al:HfO <sub>2</sub> |

| IL. The Al <sub>2</sub> O <sub>3</sub> IL was underwent RTA at 800 °C and the Al:HfO <sub>2</sub>                  |

| IL was underwent RTA at 495 °C                                                                                     |

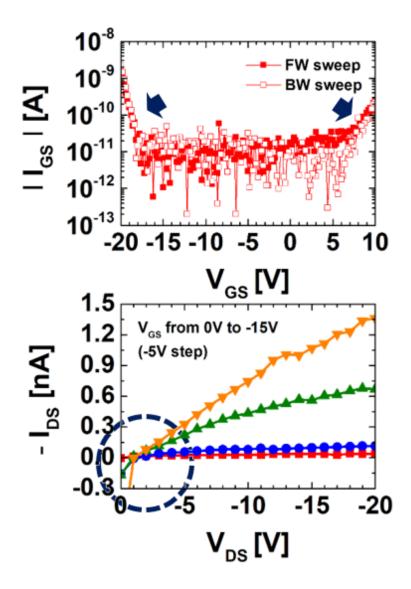

| Figure 6.8. The gate current and output characteristics of SnO TFT with                                            |

| Al:HfO <sub>2</sub> IL. The Al:HfO <sub>2</sub> IL was underwent RTA at 495 $^{\circ}$ C 192                       |

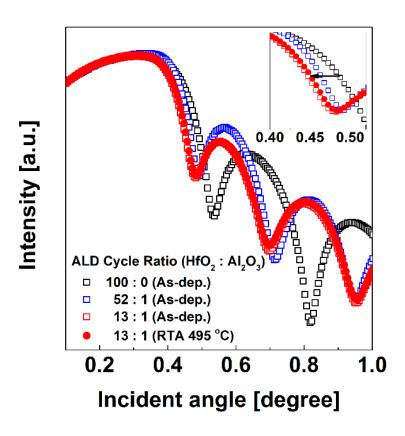

| Figure 6.9. The XRR results of Al:HfO <sub>2</sub> film according to ALD cycle ratio                               |

| between HfO <sub>2</sub> and Al <sub>2</sub> O <sub>3</sub>                            |

|----------------------------------------------------------------------------------------|

| Figure 6.10. The transfer characteristics of SnO TFT with different condition          |

| of IL. The $Al_2O_3$ IL was underwent RTA at 800 °C and the $Al:HfO_2$                 |

| IL was underwent RTA at 495 and 800 °C, respectively 194                               |

| Figure 6.11. The GAXRD results of Al:HfO₂ IL underwent RTA at 800 °C.195               |

| Figure 6.12. The XRR results of Al:HfO <sub>2</sub> film according to RTA temperature. |

|                                                                                        |

| Figure 6.13. The memory characteristics of programming operation for the               |

| SnO/Al:HfO <sub>2</sub> (RTA 800 °C)/SiO <sub>2</sub> stacked TFTs                     |

| Figure 6.14. The memory characteristics of erase operation for the                     |

| SnO/Al:HfO <sub>2</sub> (RTA 800 °C)/SiO <sub>2</sub> stacked TFTs                     |

| Figure 6.15. The retention characteristics of programming and erase operation          |

| for the SnO/Al:HfO <sub>2</sub> (RTA 800 °C)/SiO <sub>2</sub> stacked TFTs 199         |

### **List of Tables**

| Table 2.1. Reported electrical properties of the ALD SnO <sub>x</sub> films                  |

|----------------------------------------------------------------------------------------------|

| Table 2.2. Recent research on the p-type SnO                                                 |

| Table 4.1. Structure parameters calculated by HSE with the unified $\alpha$ =0.25. The       |

| amorphous supercell was generated by the melt-quenching technique                            |

| using ab-initio molecular dynamics with PBE functional, and the                              |

| atomic position was finally relaxed using HSE functional: melting                            |

| 7000 K $\rightarrow$ quenching 2500 K to 300 K (100 K/ps) $\rightarrow$ 0 K MD $\rightarrow$ |

| PBE relaxation $\rightarrow$ HSE relaxation at the fixed cell. The denoted                   |

| supercell was used to calculate defect formation energy using HSE                            |

| functional with $\alpha$ =0.25                                                               |

| Table 4.2. Main TFT parameters extracted from the transfer characteristics of                |

| each condition (all the parameters were calculated from the forward-                         |

| direction curves in the transfer characteristics)                                            |

| Table 5.1. Simulation parameters in DOS model for SnO 7 nm / $SiO_2$ 35 nm                   |

| TFTs with Au source/drain electrode for C-V results                                          |

#### List of Abbreviations

AES Auger electron spectroscopy

AFM Atomic Force Microscopy

AIMD ab initio molecular dynamics

ALD Atomic Layer Deposition

BE Bottom electrode

BW Backward

CBM Conduction band minimum

CCW Counterclockwise

CET Capacitance-equivalent thickness

CMOS Complementary metal oxide semiconductor

CVD Chemical vapor deposition

CW Clockwise

DFT Density functional theory

DOS Density of states

EDS Energy-dispersive spectroscopy

External electric field

E<sub>int</sub> Internal electric field

E<sub>ox</sub> Effective oxide electric field

$E_{VO}$  The energy level of the oxygen vacancy  $(V_0)$  within

the bandgap of the SnO

FE-SEM Field-emission scanning electron microscopy

FFT fast Fourier transform

FIB Focused ion beam

FW Forward

GAXRD Grazing-angle incidence X-ray diffraction

GI Gate insulator

GGA Generalized gradient approximation

HRTEM High-resolution transmission electron microscopy

HSE Heyd, Scuseria, and Ernzerhof

I<sub>DS</sub> Drain-source current

I<sub>GS.</sub> I<sub>G</sub> Gate-source current or gate current

IL Interfacial layer

I<sub>on/</sub>I<sub>off</sub> On-off ratio of drain-source current

NBS Negative Bias stress

N<sub>bt</sub> Border trap density

N<sub>it</sub> Interface trap density

PAW Projector-augmented wave

PBE Perdew, Burke, and Ernzerhof

PDA Post-deposition annealing

RTA Rapid thermal annealing

SE Spectroscopic ellipsometry

Sn(dmamp)<sub>2</sub> Bis(1-dimethylamino-2-methyl-2propoxy)tin(II)

SR Sweep rate

SS Subthreshold swing

STEM Scanning transmission electron microscopy

TFT Thin-film transistor

TMA Trimethyl aluminum

TOF-SIMS Time-of-flight secondary ion mass spectrometer

VASP Vienna Ab Initio Simulation Package

VBM Valence band maximum

V<sub>BE</sub> Bottom electrode voltage

$V_{DS}$  Drain-source voltage

$V_{GS}, V_{G}$  Gate-source voltage or gate voltage

V<sub>hy</sub> Hysteresis voltage

$V_0$ . Doubly ionized oxygen vacancy

V<sub>th</sub> Threshold voltage

XRF X-ray fluorescent spectroscopy

XRR X-ray reflectivity

XPS X-ray photoelectron spectroscopy

μ<sub>FE</sub> Field-effect mobility

#### 1. Introduction

#### 1.1. Overview

Semiconducting-oxide-based thin-film transistors (TFTs) have attracted for use in display, storage memory, and complementary logic circuits due to their properties, including transparency, low processing temperature, and high carrier mobility [1–3]. The fabrication of the complementary metal oxide semiconductor (CMOS) circuit, however, which is indispensable for a lowpower-consuming electronic circuit, has been deterred by the (i) unavailability of high-performance p-type semiconducting oxides and (ii) the low electrical characteristics of the p-type oxide TFTs compared to those of n-type ones [4,5]. As the valence band maximum (VBM) of the oxide semiconductor is located very deep from the vacuum level, it is difficult to find a suitable shallow acceptor, which makes p-type doping difficult [6]. Also, the VBM of the oxide semiconductor is mainly composed of localized O 2p orbitals, resulting in low hole mobility [6,7]. Therefore, increasing the energy level and the dispersion of VBM are the key factors to achieving high-performance p-type oxide semiconductors. Hybridization with a spherical metal orbital close to the O 2p energy level has been suggested to overcome these problems [7], and the p-type characteristics of various p-type oxide materials, such as Ag<sub>2</sub>O, Cu<sub>2</sub>O, CuAlO<sub>2</sub>, SnO, and NiO, were evaluated. According to Togo et al.[8] and Ogo et al.[9], Tin monoxide (SnO) could be the most promising p-type material because there

is a significant overlap of O 2p and Sn 5s orbitals in its valence band, which can induce high hole mobility. The simple layered structure of SnO is additional merit of such material.

SnO, however, is a meta-stable phase compared with the fully oxidized SnO<sub>2</sub>, and thus, it could be easily oxidized to SnO<sub>2</sub> through oxidation under an oxygen-abundant condition (SnO +  $O_2/2 \rightarrow SnO_2$ ) or disproportionation reaction even without oxygen (2SnO  $\rightarrow$  SnO<sub>2</sub> + Sn) [10,11]. Therefore, the process window for achieving phase-pure SnO is narrow and sensitive to the various process conditions, such as the pressure, deposition and post-deposition annealing (PDA) temperatures, gas atmosphere, passivation conditions [12–18]. Most of the past relevant researches in the field were conducted using the radio frequency (RF) sputtering method with an highpurity SnO target at a sufficiently low pressure to deposit the SnO thin films. Nonetheless, the sputtering technique is often inadequate for growing a highquality oxide semiconductor channel material due to the probable involvement of the damaging effect induced by the energetic ion bombardment. The chemical vapor deposition (CVD) process is thus more preferred considering its far less damaging growth condition. The strong tendency to form the more stable SnO<sub>2</sub> phase during the CVD process, however, hinders the growth of the SnO film [19–23].

It was recently reported that p-type SnO thin films were successfully fabricated using the atomic layer deposition (ALD) method when the Sn ion in

the Sn precursor (bis(1-dimethylamino-2-methyl-2-propoxy)tin(II), Sn(dmamp)<sub>2</sub>, which was also adopted in this work) has a +2 oxidation state, and H<sub>2</sub>O was adopted as the oxygen source [24,25]. Compared to the sputtering method, the ALD method has the advantages of highly conformal growth on a high-aspect-ratio structure and a low damage effect, which are suitable features for three-dimensionally stacked devices. Also, the optimal thickness of the SnO channel layer for the high-performance TFT device, especially with a high  $I_{on}/I_{off}$  current ratio of  $I_{DS}$ , is only ~5–10 nm, which can hardly be precisely controlled by the conventional sputtering technique or CVD. In ALD, the film thickness is determined by the number of ALD cycles, with a given growth per cycle of a highly saturated ALD process. Therefore, an accurate control of the film thickness with high uniformity at the atomic layer over a large wafer area can be achieved. Nevertheless, the research on the ALD SnO film is still at its early stage, and its electrical properties have not been sufficiently analyzed in many previous works.

In this dissertation, the high-performance SnO-based p-type TFTs with improved bias stability with low hysteresis voltage ( $V_{hy}$ ) was fabricated. For indepth analysis, the effects of the  $Al_2O_3$  barrier layer on the device performance of the p-type SnO TFT were further exploited, focusing on the threshold voltage ( $V_{th}$ ) instability, displacive gate current, and additional capacitance effect. In additon, a comparative study on electrical characteristics of p-type SnO TFTs with  $Al_2O_3$  and Al-doped  $HfO_2$  interfacial layer (IL) was conducted. This study

will be helpful to provide the useful design concept for high performance pchannel SnO devices.

The organization of this dissertation is as follows. Chapter 2 gives brief descriptions based on the relevant literatures reviewed. Descriptions about the overview of p-type metal oxide semiconductor, the p-type SnO, the p-type SnO thin films grown by ALD and its application to TFTs will be concerned. Chapter 3 explains the growth behavior and characterizations of p-type SnO thin films grown by ALD. In addition, optimization of fabrication process for ALD SnO TFT will be demonstrated. Chapter 4 presents electrical performances of ALD SnO TFTs with and without an Al<sub>2</sub>O<sub>3</sub> IL. It scrutinizes the influences about chemical reaction between the channel material and gate insulator (GI) depending on IL conditions. Chapter 5 provides in-depth analysis of IL-inserted SnO device with reduced V<sub>by</sub>, which show abnormal electrical properties. Chapter 6 explains the results of the investigations about the effect of different IL on the performance of SnO TFTs. Chapter 7 provides the conclusion of the dissertation.

## 1.2. Bibliography

- [1] A. Nathan, S. Lee, S. Jeon, J. Robertson, J. Disp. Technol. 2014, 10, 917.

- [2] E. S. Hwang, J. S. Kim, S. M. Jeon, S. J. Lee, Y. Jang, D.-Y. Cho, C.S. Hwang, *Nanotechnology* 2018, 29, 155203.

- [3] E. Fortunato, P. Barquinha, R. Martins, *Adv. Mater.* **2012**, *24*, 2945.

- [4] Z. Wang, H. A. Al-Jawhari, P. K. Nayak, J. A. Caraveo-Frescas, N. Wei, M. N. Hedhili, H. N. Alshareef, Sci. Rep. 2015, 5, 9617.

- [5] Y. Li, J. Yang, Y. Wang, P. Ma, Y. Yuan, J. Zhang, Z. Lin, L. Zhou, Q. Xin, A. Song, *IEEE Electron Device Lett.* 2018, 39, 208.

- [6] N. Sarmadian, R. Saniz, B. Partoens, D. Lamoen, Sci. Rep. 2016, 6, 20446.

- [7] T. Kamiya, H. Hosono, Int. J. Appl. Ceram. Technol. 2005, 2, 285.

- [8] A. Togo, F. Oba, I. Tanaka, K. Tatsumi, *Phys. Rev. B* **2006**, *74*, 195128.

- [9] Y. Ogo, H. Hiramatsu, K. Nomura, H. Yanagi, T. Kamiya, M. Hirano,H. Hosono, *Appl. Phys. Lett.* 2008, 93, 032113.

- [10] L. Y. Liang, Z. M. Liu, H. T. Cao, Z. Yu, Y. Y. Shi, A. H. Chen, H. Z. Zhang, Y. Q. Fang, X. L. Sun, J. Electrochem. Soc. 2010, 157, H598.

- [11] M. Batzill, U. Diebold, Prog. Surf. Sci. 2005, 79, 47.

- [12] J. A. Caraveo-Frescas, P. K. Nayak, H. A. Al-Jawhari, D. B. Granato, U. Schwingenschlogl, H. N. Alshareef, ACS Nano 2013, 7, 5160.

- [13] H. Luo, L. Y. Liang, H. T. Cao, Z. M. Liu, F. Zhuge, *ACS Appl. Mater. Interfaces* **2012**, *4*, 5673.

- [14] H. Luo, L. Y. Liang, Q. Liu, H. T. Cao, ECS J. Solid State Sci. Technol. 2014, 3, Q3091.

- [15] P.-C. Hsu, C.-C. Wu, H. Hiramatsu, T. Kamiya, H. Hosono, *ECS J. Solid State Sci. Technol.* **2014**, *3*, Q3040.

- [16] I.-T. Cho, M. U, S.-H. Song, J.-H. Lee, H.-I. Kwon, Semicond. Sci. Technol. 2014, 29, 045001.

- [17] H. Yabuta, N. Kaji, R. Hayashi, H. Kumomi, K. Nomura, T. Kamiya, M. Hirano, H. Hosono, Appl. Phys. Lett. 2010, 97, 072111.

- [18] H. Luo, L. Liang, H. Cao, M. Dai, Y. Lu, M. Wang, ACS Appl. Mater. Interfaces 2015, 7, 17023.

- [19] G. Sanon, R. Rup, A. Mansingh, *Thin Solid Films* **1990**, 190, 287.

- [20] R. Y. Korotkov, P. Ricou, A. J. E. Farran, *Thin Solid Films* **2006**, *502*,79.

- [21] J. Lančok, A. Santoni, M. Penza, S. Loreti, I. Menicucci, C. Minarini,

- M. Jelinek, Surf. Coat. Technol. 2005, 200, 1057.

- [22] J. Szuber, G. Czempik, R. Larciprete, D. Koziej, B. Adamowicz, *Thin Solid Films* **2001**, *391*, 198.

- [23] S. G. Ansari, S. W. Gosavi, S. A. Gangal, R. N. Karekar, R. C. J. Aiyer, Mater. Sci.: Mater. Electron. 1997, 8, 23.

- [24] J. H. Han, Y. J. Chung, B. K. Park, S. K. Kim, H. S. Kim, C. G. Kim, T. M. Chung, *Chem. Mater.* **2014**, *26*, 6088.

- [25] S. H. Kim, I.-H. Baek, D. H. Kim, J. J. Pyeon, T.-M. Chung, S.-H. Baek, J.-S. Kim, J. H. Han, S. K. Kim, J. Mater. Chem. C 2017, 5, 3139.

# 2. Literature

## 2.1. The overview of p-type oxide semiconductors

Figure 2.1 shows the schematic diagrams of a conventional architecture with bottom logic circuit only and a three-dimensional stacked architecture using CMOS logic circuits placed at each memory layer [1]. Since external circuit needed for connecting with stacked memory layer for conventional architecture, where the logic devices are on Si wafer, peripheral circuit area is increased. As a result, density efficiency decreases, and fabrication process becomes complex. In addition, circuit interference and RC delay are serious problems for device operations. Therefore, the logic device must be stacked together with memory device for integration efficiency, process simplicity, and circuit configuration to systematically operate the characteristics of the two connected devices.

This further emphasizes the need for process development of oxide semiconductors with high carrier mobility, low process temperature, and device uniformity characteristics. However, the technological development of logic devices consisting of oxide semiconductor-based transistors has reached its limit. This is because p-type oxide semiconductor, an essential component of CMOS logic devices, has lower electrical properties than n-type ones.

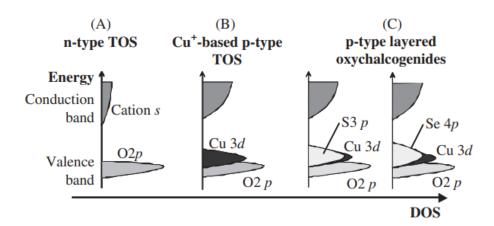

The reason for this is the inherent band characteristics of oxide semiconductors. As shown in **Figure 2.2**, the VBM is composed of localized oxygen 2p orbitals, so the hole mobility is low. In addition, the VBM is located

at a deep energy level, and there are high concentrations of deep states right above it (**Figure 2.3**) [2]. It makes p-type doping and the inversion operations difficult. Therefore, increasing the energy level of VBM or dispersing it through hybridization with metal orbital is a key factor for obtaining a high-performance p-type oxide semiconductor. To solve this problem, it is necessary to develop a new p-type oxide channel material having high hole mobility.

Recently, a high-speed computational screening method based on the first principle calculation has been actively conducted to find a new p-type oxide semiconductor (Figure 2.4). According to K. Yim et al. [3] and Y. Youn et al. [4], it is reported that the use of a hydrogen selector based on the formation energy of hydrogen interstitial defects can provide high accuracy and fast calculation speed in predicting hole concentration. According to the results, the proposed p-type oxide candidates are largely classified into three groups. The Cu bearing oxide, Pt-group bearing oxide, and multi-anion compound were proposed as candidate groups. In the case of Cu or Pt-based oxides, the hybridization of the d-orbital of the metal and the 2p orbital of oxygen constitutes the valence band and can exhibit p-type characteristics (**Figure 2.5**) [5]. However, the effective mass of hole is large, and it is difficult to expect excellent electrical characteristics. In the case of multi-anion compounds, the chalcogen anion raises the energy level of the valence band and has a low hole effective mass. Nevertheless, there is a limitation that it is difficult to produce a raw material possessing excellent chemical stability and reactivity. In particular, in the case of such a multi-component material, it is difficult to obtain the stable composition ratio and uniformity of the thin film. In addition, the problem of selecting the reactant gas for production of the material and process difficulties such as particle contamination in the chamber limits the actual application of the material. Meanwhile, SnO, which does not belong to the three representative groups, is the only binary material among the candidate groups. It is reported that it has a low hole effective mass because s orbital of tin is hybridized with the 2p orbital of oxygen. For this reason, SnO is attracting huge attention as the most promising material among p-type oxides because of its electrical properties and processability.

**Figure 2.1.** Schematic diagrams of (a) a conventional and (b) a three-dimensional stacked architecture between logic circuits and memory layers.

**Figure 2.2.** Schematic energy diagrams of (a) n-type and (b) p-type oxide semiconductors.

**Figure 2.3.** Schematic diagram of sub-gap density of states for oxide semiconductors.

**Figure 2.4.** Results of high-speed computational screening method of two- and three-component substances using a hydrogen selector. FEH> -1 eV region corresponds to the p-type oxide candidate group that guarantees transparency.

**Figure 2.5**. Simplified band structures of oxide semiconductors. (a) Typical n-type oxide semiconductor, (b) Cu<sup>+</sup>-based p-type oxide semiconductor, (c) Oxychalcogenide-based p-type oxide semiconductor.

# 2.2. The p-type SnO

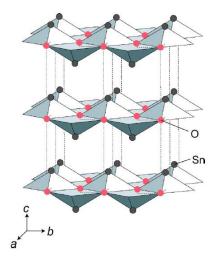

As shown in **Figure 2.6,** SnO is a material in which four oxygens and one Sn are arranged in a pyramid shape to form a layered structure [6]. It has a large optical band gap of about 2.7–3.0 eV and an electronic band gap of about 0.7 eV.

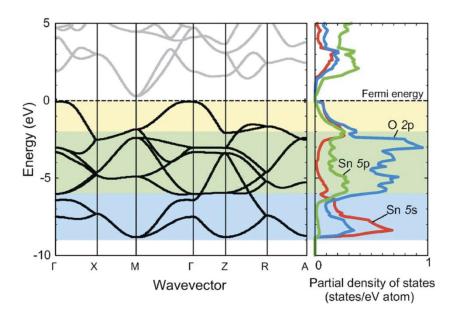

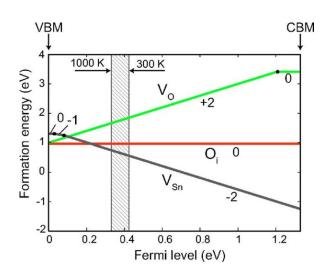

Based on the first principle calculation reported by Togo *et al*. [6], the origin for obtaining p-type conductivity of SnO are as follows. As mention above, the Sn 5s orbital near VBM can reduce the localization by O 2p orbital. This allows the SnO material to have high hole mobility (**Figure 2.7**). In addition to this, the film should be in an oxygen-rich condition where intrinsic defects such as  $V_{Sn}$  (Sn vacancy) and  $O_i$  (O interstitial) are easily formed. When these defects are completely ionized, they can act as acceptor-like defects and contribute to the p-type conductivity. However, since  $O_i$  is hardly ionized,  $V_{Sn}$  becomes a major defect that acts as a source of hole carriers (**Figure 2.8**). If the film is Snrich condition, intrinsic defects such as  $Sn_i$  (Sn interstitial) and  $V_O$  (O vacancy) are easily formed, contributing to n-type conductivity.

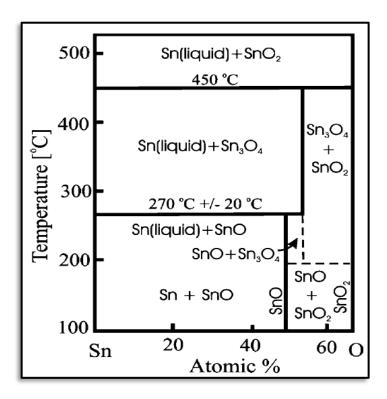

The most important point to consider obtaining p-type SnO is phase control. This is because the most common oxides of Sn at atmospheric pressure and room temperature have two forms: SnO and SnO<sub>2</sub> [7]. However, the problem comes from the fact that each material has p-type and n-type conductivity, respectively. Since p-type SnO is known to be thermodynamically unstable under ambient conditions, it can be easily converted into stable n-type SnO<sub>2</sub>

depending on factors such as temperature, gas atmosphere, and pressure [8–10]. As shown in **Figure 2.9**, the thermal stability of SnO materials is only achieved in the temperature range up to 270 °C [7]. Moreover, it has been found that the deposited films often show multi-phases containing metallic Sn, SnO<sub>2</sub>, or Sn<sub>3</sub>O<sub>4</sub> rather than pure SnO [11]. As a result, the p-type conductivity of SnO can only be obtained by carefully controlling deposition or heat treatment conditions [12].

Figure 2.6. The crystal structure of SnO material.

**Figure 2.7.** Band structure (left) and density of states (right) of the unit cell of the SnO perfect crystal.

**Figure 2.8.** Formation energies as a function of the Fermi level when SnO is in O-rich condition.

**Figure 2.9.** Phase diagram as function of temperature and atomic ratio between Sn and O.

# 2.3. The p-type SnO thin films grown by ALD and its application to TFTs

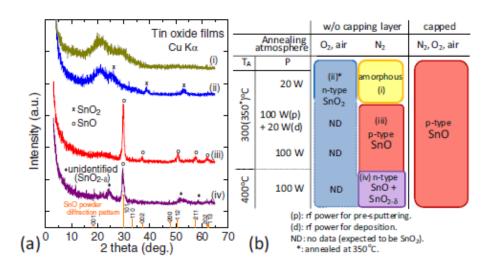

Despite such advantages, due to the thermodynamic metastable property of the SnO material, it is easily oxidized to SnO<sub>2</sub> with a lower energy level of n-type. Therefore, the process window for obtaining SnO is very narrow, and it is sensitive to the process conditions as shown in **Figure 2.10** [12]. In order to obtain a p-type thin film with excellent electrical properties, it is important to stably obtain a single SnO phase.

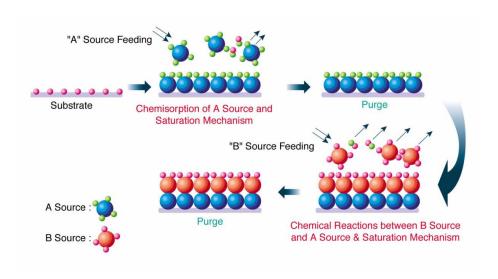

In this respect, ALD is the most appropriate method for obtaining meta-stable SnO. The ALD method does not have the problem of damage caused by high-energy ions, unlike the common process technology of sputtering method. Therefore, it is more suitable for growing high-quality oxide semiconductor channel materials. Moreover, unlike CVD, ALD is a method in which the reactants are separated and injected sequentially (**Figure 2.11**) [13]. However, research on ALD p-type oxide semiconductors is still at an early stage compared to its importance.

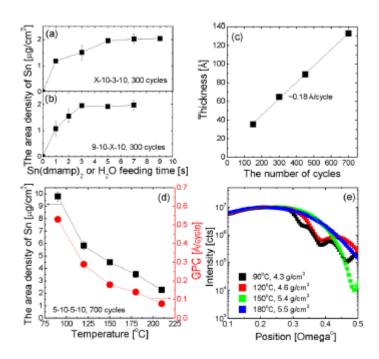

**Table 2.1** shows a summary of previous studies that reported electrical properties among tin oxide materials deposited by ALD method [14–26]. Many Sn precursors and oxygen source were used, but almost all of them were SnO<sub>2</sub> film with n-type characteristics. Among the studies on ALD SnO<sub>x</sub> thin films, only one research was reported as a p-type characteristic until 2017 (**Figure 2.12**) [20]. In addition, it was confirmed that even if the same Sn precursor

(Sn(dmamp)<sub>2</sub>) was used, the electrical type changed according to the degree of oxidation of the oxygen source [18–20]. Therefore, a selection of an oxidizing agent and process conditions is particularly important in conducting an experiment.

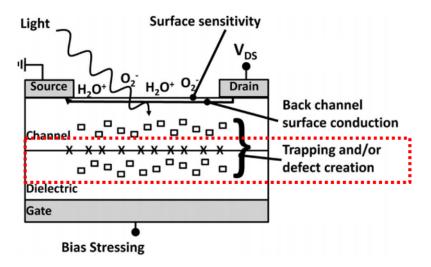

However, in most of the studies, SnO thin film deposition has been performed using the sputtering method. As a result, there was a limitation in that the on/off ratio was low as well as the hysteresis voltage was large due to carrier trapping at the interface (**Table 2.2**) [27–35]. It is known that the hysteresis is mainly caused by border traps. It is located slightly away from the channel interface and the energy level is deep within the dielectric band gap (**Figure 2.13**) [36]. It is caused by slowing the trapping and de-trapping of the carrier. In order to utilize SnO devices in real logic devices, this hysteresis problem must be solved, but no such analysis or improvement method has been suggested. Border traps are mainly caused by chemical interactions between the gate dielectric and the channel material. Therefore, when ALD SnO thin film is applied, it is expected that this hysteresis problem can be solved by securing not only high-quality channel film properties but also good interfacial properties.

The SnO TFT device fabricated by the ALD method is a technology with exceptional originality that has few reports on related contents. Developing the ALD process for p-type SnO and fabricating SnO TFT devices are essential for preoccupying research technology of the next-generation p-type material.

**Figure 2.10.** (a) XRD spectra and (b) schematic phase classification of  $SnO_X$  films with different rf sputtering power, annealing temperature, and atmosphere.

Figure 2.11. Schematic diagram of the mechanism of ALD process.

| Reagent 1<br>(Sn-containing) | Reagent 2<br>(oxidizer)             | Substrate                                 | Temperature (°C) | Resistivity             | Carrier type | Journal inform.                                                   |

|------------------------------|-------------------------------------|-------------------------------------------|------------------|-------------------------|--------------|-------------------------------------------------------------------|

|                              | 1                                   | Soda lime glass<br>Coming 7059 glass      | 200              | 0.06-0.20               | N-type       | H. Viirola et al., Thin Solid Films, 249, 144 (1994)              |

| ī                            | H <sub>2</sub> O +O <sub>3</sub>    | Soda lime glass                           | 200              | 0.1-89                  | N-type       | M. Utriainen et al., J. Electrochem. Soc., 146, 189 (1999)        |

| SnCl4                        |                                     |                                           | 300              | 0.01                    |              |                                                                   |

|                              | Ę                                   | sselp(001) i2                             | 350              | 90:0                    | N-t/no       | H. –E. Cheng et al., Procedia Engineering, 36, 510 (2012)         |

|                              | 2                                   | (100)glass                                | 400              | 0.11                    | ads, N       |                                                                   |

|                              |                                     |                                           | 450              | 90:0                    |              |                                                                   |

|                              |                                     |                                           | 400              | 0.21                    |              |                                                                   |

| TMT                          | NO <sub>2</sub>                     | ï⊼                                        | 425              | 0.17                    | ;            |                                                                   |

|                              |                                     |                                           | 450              | 0.13                    | N-type       | V.E. Drozd et al., Appl. Surf. Sci. 82/83, 591 (1994)             |

| ļ                            | :                                   | i                                         | 250              | 0.027                   |              |                                                                   |

| Ξ                            | NO <sub>2</sub>                     | <i></i>                                   | 290              | 0.012                   |              |                                                                   |

|                              | PEALD                               | Si/SiO <sub>2</sub> -200nm                | 130              | 0.37                    | N-type       | B.K. Lee et al., Mat. Res. Bulletin, 47, 3052 (2012)              |

| Sn(dmamp) <sub>2</sub>       | ő                                   | Si/SiO <sub>2</sub> -100nm, Si, TiN       | 100-230          | 1.3X10 <sup>-3</sup> ~1 | N-type       | MJ. Choi et al., Applied Surface Science, 320, 188 (2014)         |

|                              | H <sub>2</sub> O                    | Si/SiO <sub>2</sub> -300nm                | 150-210          | 4.9-14.5                | P-type       | Jeong Hwan Han et al., Chem. Mat., 26, 6088 (2014)                |

| Co/4pps)                     | H <sub>2</sub> O <sub>2</sub> (50%) | Si/SiO <sub>2</sub> , glass, SiN membrane | 100-220          | 0.015-0.025             | N ton        | J. Heo et al., Chem. Mater. 22, 4964 (2010)                       |

| Sn(tbba)                     | <u>Q</u>                            | silica glass                              | 250              | 0.008                   | adá-N        | J. Heo et al., J. Chem. Mater. 22, 4599 (2012)                    |