Ph.D. DISSERTATION

## Designing Scalable Computer Systems to Accelerate Heterogeneous NLP Models

이종 자연어 처리 모델을 위한 확장형 컴퓨터 시스템 설계

BY

Kim Joonsung

FEBRUARY 2021

DEPARTMENT OF ELECTRICAL ENGINEERING AND COMPUTER SCIENCE COLLEGE OF ENGINEERING SEOUL NATIONAL UNIVERSITY Ph.D. DISSERTATION

## Designing Scalable Computer Systems to Accelerate Heterogeneous NLP Models

이종 자연어 처리 모델을 위한 확장형 컴퓨터 시스템 설계

BY

Kim Joonsung

FEBRUARY 2021

DEPARTMENT OF ELECTRICAL ENGINEERING AND COMPUTER SCIENCE COLLEGE OF ENGINEERING SEOUL NATIONAL UNIVERSITY

## Designing Scalable Computer Systems to Accelerate Heterogeneous NLP Models

이종 자연어 처리 모델을 위한 확장형 컴퓨터 시스템 설계

지도교수 김 장 우 이 논문을 공학박사 학위논문으로 제출함

2020년 12월

서울대학교 대학원

전기 컴퓨터 공학부

## 김준성

## 김준성의 공학박사 학위 논문을 인준함

2020년 12월

## Abstract

Modern neural-network (NN) accelerators have been successful by accelerating a small number of basic operations (e.g., convolution, fully-connected, feedback) comprising the specific target neural-network models (e.g., CNN, RNN). However, this approach no longer works for the emerging full-scale natural language processing (NLP)-based neural network models (e.g., *Memory networks, Transformer, BERT*), which consist of different combinations of complex and heterogeneous operations (e.g., self-attention, multi-head attention, large-scale feed-forward). Existing acceleration proposals cover only the proposal-specific basic operations and/or customize them for specific models only, which leads to the low performance improvement and the narrow model coverage. Therefore, an ideal NLP accelerator should first identify all performance-critical operations required by different NLP models and support them as a single accelerator to achieve a high model coverage, and can adaptively optimize its architecture to achieve the best performance for the given model.

To address these scalability and model/config diversity issues, the dissertation introduces two novel projects (i.e., *MnnFast* and *NLP-Fast*) to efficiently accelerate a wide spectrum of full-scale NLP models. First, MnnFast proposes three novel optimizations to resolve three major performance problems (i.e., *high memory bandwidth*, *heavy computation*, and *cache contention*) in memory-augmented neural networks. Next, NLP-Fast adopts three optimization techniques to resolve the huge performance variation due to the model/config diversity in emerging NLP models. We implement both MnnFast and NLP-Fast on different hardware platforms (i.e., CPU, GPU, FPGA) and thoroughly evaluate their performance improvement on each platform. keywords: Hardware-Software Co-Design, Natural Language Processing (NLP), AI Accelerator, Machine Learning, Computer Architecture student number: 2017-36250

# Contents

| Al | ostrac  | et            |                                                          | i  |

|----|---------|---------------|----------------------------------------------------------|----|

| Co | onten   | ts            |                                                          | ii |

| Li | st of ' | <b>Fables</b> |                                                          | v  |

| Li | st of ] | Figures       |                                                          | vi |

| 1  | INT     | RODU          | CTION                                                    | 1  |

| 2  | Bac     | kgroun        | d                                                        | 6  |

|    | 2.1     | Memo          | ry Networks                                              | 6  |

|    | 2.2     | Deep l        | Learning for NLP                                         | 9  |

| 3  | A Fa    | ast and       | Scalable System Architecture for Memory-Augmented Neural |    |

|    | Net     | works         |                                                          | 14 |

|    | 3.1     | Motiva        | ation & Design Goals                                     | 14 |

|    |         | 3.1.1         | Performance Problems in MemNN – High Off-chip Memory     |    |

|    |         |               | Bandwidth Requirements                                   | 15 |

|    |         | 3.1.2         | Performance Problems in MemNN – High Computation         | 16 |

|    |         | 3.1.3         | Performance Problems in MemNN – Shared Cache Contention  | 17 |

|    |         | 3.1.4         | Design Goals                                             | 18 |

|    | 3.2     | MnnFa         | ast                                                      | 19 |

|   |                   | 3.2.1                                                                                  | Column-Based Algorithm                                      | 19                                                                                                                                 |

|---|-------------------|----------------------------------------------------------------------------------------|-------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|

|   |                   | 3.2.2                                                                                  | Zero Skipping                                               | 22                                                                                                                                 |

|   |                   | 3.2.3                                                                                  | Embedding Cache                                             | 25                                                                                                                                 |

|   | 3.3               | Impler                                                                                 | nentation                                                   | 26                                                                                                                                 |

|   |                   | 3.3.1                                                                                  | General-Purpose Architecture – CPU                          | 26                                                                                                                                 |

|   |                   | 3.3.2                                                                                  | General-Purpose Architecture – GPU                          | 28                                                                                                                                 |

|   |                   | 3.3.3                                                                                  | Custom Hardware (FPGA)                                      | 29                                                                                                                                 |

|   | 3.4               | Evalua                                                                                 | tion                                                        | 31                                                                                                                                 |

|   |                   | 3.4.1                                                                                  | Experimental Setup                                          | 31                                                                                                                                 |

|   |                   | 3.4.2                                                                                  | CPU                                                         | 33                                                                                                                                 |

|   |                   | 3.4.3                                                                                  | GPU                                                         | 35                                                                                                                                 |

|   |                   | 3.4.4                                                                                  | FPGA                                                        | 37                                                                                                                                 |

|   |                   | 3.4.5                                                                                  | Comparison Between CPU and FPGA                             | 39                                                                                                                                 |

|   | 3.5               | Conclu                                                                                 | usion                                                       | 39                                                                                                                                 |

|   |                   |                                                                                        |                                                             |                                                                                                                                    |

| 4 | ΛF                | ost Scal                                                                               | able and Flevible System for Large-Scale Heterogeneous NLP  |                                                                                                                                    |

| 4 |                   |                                                                                        | able, and Flexible System for Large-Scale Heterogeneous NLP |                                                                                                                                    |

| 4 | Mod               | lels                                                                                   |                                                             | 40                                                                                                                                 |

| 4 |                   | lels<br>Motiva                                                                         | ation & Design Goals                                        | <b>40</b><br>40                                                                                                                    |

| 4 | Mod               | lels<br>Motiva<br>4.1.1                                                                | ation & Design Goals                                        | <b>40</b><br>40<br>40                                                                                                              |

| 4 | Mod               | lels<br>Motiva                                                                         | ation & Design Goals                                        | <b>40</b><br>40<br>40<br>41                                                                                                        |

| 4 | Mod               | lels<br>Motiva<br>4.1.1                                                                | ation & Design Goals                                        | <b>40</b><br>40<br>40                                                                                                              |

| 4 | Mod               | lels<br>Motiva<br>4.1.1<br>4.1.2                                                       | ation & Design Goals                                        | <b>40</b><br>40<br>40<br>41                                                                                                        |

| 4 | Mod               | lels<br>Motiva<br>4.1.1<br>4.1.2<br>4.1.3                                              | Ation & Design Goals                                        | <b>40</b><br>40<br>40<br>41<br>42                                                                                                  |

| 4 | Mod               | lels<br>Motiva<br>4.1.1<br>4.1.2<br>4.1.3<br>4.1.4                                     | ation & Design Goals                                        | <ul> <li>40</li> <li>40</li> <li>40</li> <li>41</li> <li>42</li> <li>43</li> </ul>                                                 |

| 4 | <b>Mod</b><br>4.1 | lels<br>Motiva<br>4.1.1<br>4.1.2<br>4.1.3<br>4.1.4<br>4.1.5                            | ation & Design Goals                                        | <ul> <li>40</li> <li>40</li> <li>40</li> <li>41</li> <li>42</li> <li>43</li> <li>43</li> </ul>                                     |

| 4 | <b>Mod</b><br>4.1 | lels<br>Motiva<br>4.1.1<br>4.1.2<br>4.1.3<br>4.1.4<br>4.1.5<br>NLP-F                   | ation & Design Goals                                        | <ul> <li>40</li> <li>40</li> <li>40</li> <li>41</li> <li>42</li> <li>43</li> <li>43</li> <li>44</li> </ul>                         |

| 4 | <b>Mod</b><br>4.1 | lels<br>Motiva<br>4.1.1<br>4.1.2<br>4.1.3<br>4.1.4<br>4.1.5<br>NLP-F<br>4.2.1          | ation & Design Goals                                        | <ul> <li>40</li> <li>40</li> <li>40</li> <li>41</li> <li>42</li> <li>43</li> <li>43</li> <li>44</li> <li>44</li> </ul>             |

| 4 | <b>Mod</b><br>4.1 | lels<br>Motiva<br>4.1.1<br>4.1.2<br>4.1.3<br>4.1.4<br>4.1.5<br>NLP-F<br>4.2.1<br>4.2.2 | ation & Design Goals                                        | <ul> <li>40</li> <li>40</li> <li>40</li> <li>41</li> <li>42</li> <li>43</li> <li>43</li> <li>44</li> <li>44</li> <li>47</li> </ul> |

|    | 4.4    | Implementation                           | 59  |

|----|--------|------------------------------------------|-----|

|    |        | 4.4.1 General-Purpose Architecture – CPU | 59  |

|    |        | 4.4.2 General-Purpose Architecture – GPU | 61  |

|    |        | 4.4.3 Custom Hardware (FPGA)             | 62  |

|    | 4.5    | Evaluation                               | 64  |

|    |        | 4.5.1 Experimental Setup                 | 65  |

|    |        | 4.5.2 CPU                                | 65  |

|    |        | 4.5.3 GPU                                | 67  |

|    |        | 4.5.4 FPGA                               | 69  |

|    | 4.6    | Conclusion                               | 72  |

| 5  | Rela   | ited Work                                | 73  |

|    | 5.1    | Various DNN Accelerators                 | 73  |

|    | 5.2    | Various NLP Accelerators                 | 74  |

|    | 5.3    | Model Partitioning                       | 75  |

|    | 5.4    | Approximation                            | 76  |

|    | 5.5    | Improving Flexibility                    | 78  |

|    | 5.6    | Resource Optimization                    | 78  |

| 6  | Con    | clusion                                  | 80  |

| Al | bstrac | et (In Korean) 1                         | .06 |

# **List of Tables**

| 2.1 | Representative models in emerging NLP models and their key compu- |    |  |  |  |

|-----|-------------------------------------------------------------------|----|--|--|--|

|     | tational components.                                              | 10 |  |  |  |

| 3.1 | Memory networks configuration for the evaluation.                 | 32 |  |  |  |

| 4.1 | Time and space complexity of each key operation commonly used in  |    |  |  |  |

|     | emerging NLP models.                                              | 45 |  |  |  |

| 4.2 | Base configurations of each NLP model                             | 64 |  |  |  |

# **List of Figures**

| 1.1 | (a) shows an example story with a question. (b) shows where the mem-   |    |

|-----|------------------------------------------------------------------------|----|

|     | ory network stores the story, and how it processes the question to de- |    |

|     | rive the answer.                                                       | 2  |

| 2.1 | Computational steps of memory networks (MemNN). MemNN con-             |    |

|     | sists of embedding, input memory representation, output memory rep-    |    |

|     | resentation and output calculation. nw means the maximum number of     |    |

|     | words in a sentence. nq and ns are the number of questions and given   |    |

|     | story sentences, respectively. <i>ed</i> is the embedding dimension    | 7  |

| 2.2 | Computational steps of key components used in state-of-the-art NLP     |    |

|     | models                                                                 | 11 |

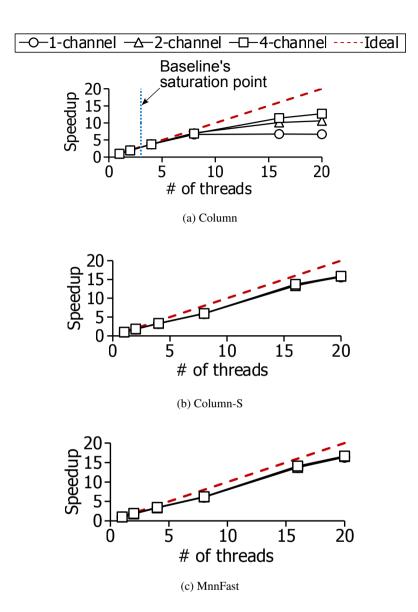

| 3.1 | Limited scalability due to memory bandwidth. The speedup results       |    |

|     | of each channel configuration are normalized to the corresponding      |    |

|     | single-thread result.                                                  | 15 |

| 3.2 | Performance degradation due to co-executed embedding threads. The      |    |

|     | slowdown results are relative to the corresponding 1-embedding thread  |    |

|     | cases. Embedding threads contend with inferencing threads for shared   |    |

|     | memory system, thus reducing the performance of MemNN                  | 17 |

| 3.3 | Dataflow comparison betweeen the baseline and the column-based al-     |    |

|     | gorithm.                                                               | 20 |

| 3.4  | Probability value distribution. Each column represents the probability    |    |

|------|---------------------------------------------------------------------------|----|

|      | vector to each question. We use the Facebook bAbi dataset and test-       |    |

|      | set [135]                                                                 | 22 |

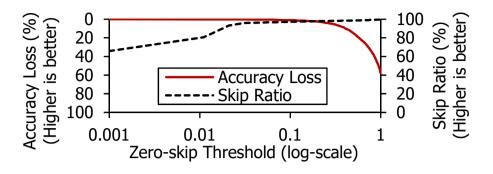

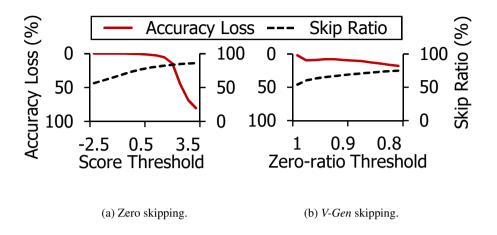

| 3.5  | Tradeoffs between accuracy loss and computation reduction according       |    |

|      | to the skip threshold.                                                    | 24 |

| 3.6  | A high-level architecture of FPGA-based MnnFast                           | 30 |

| 3.7  | Performance of column-based algorithm on CPU                              | 33 |

| 3.8  | Scalability of column-based algorithm on CPU                              | 35 |

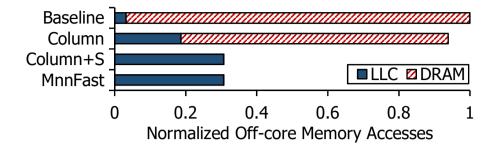

| 3.9  | The number of off-chip memory accesses on CPU                             | 36 |

| 3.10 | Scalability of column-based algorithm on GPU                              | 37 |

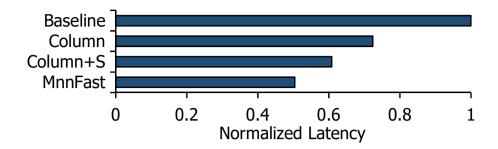

| 3.11 | Latency reduction of FPGA-based MnnFast. Each latency is normal-          |    |

|      | ized to the baseline                                                      | 38 |

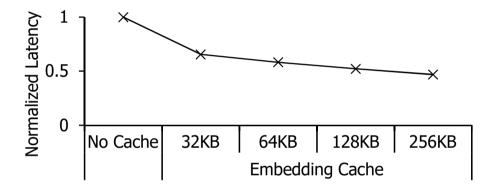

| 3.12 | Effectiveness of embedding cache in FPGA-based MnnFast. Each la-          |    |

|      | tency result is normalized to the No Cache.                               | 38 |

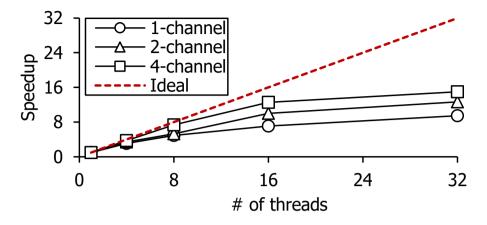

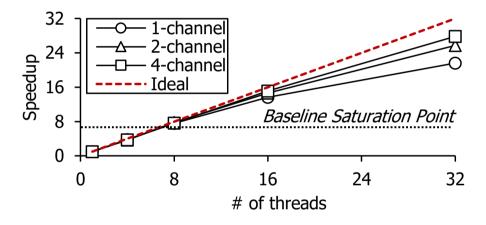

| 4.1  | Limited scalability due to memory bandwidth. The speedup results          |    |

|      | of each channel configuration are normalized to the corresponding         |    |

|      | single-thread result                                                      | 41 |

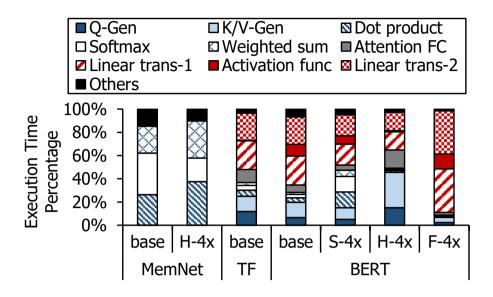

| 4.2  | Performance breakdown of NLP models with various parameter con-           |    |

|      | figurations. base configurations are in the evaluation section (i.e., ex- |    |

|      | perimental setup), and S/H/F-4x are configurations with a fourfold in-    |    |

|      | crease of $s$ , $d_H$ , and $d_{FF}$ , respectively                       | 46 |

| 4.3  | Dataflow comparison between baseline and our optimizations: partial-      |    |

|      | head update (P), column-based algorithm (C), and feed-forward split-      |    |

|      | <i>ting</i> (F)                                                           | 48 |

| 4.4  | Probability value distribution. Each column is the probability vector     |    |

|      | of each query. We randomly choose 512 queries in BERT during in-          |    |

|      | ference on SQuAD.                                                         | 51 |

| 4.5  | Tradeoffs between accuracy loss and computation reduction according          |    |

|------|------------------------------------------------------------------------------|----|

|      | to the skip threshold.                                                       | 52 |

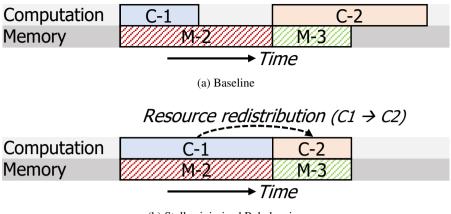

| 4.6  | Stall-minimized resource rebalancing. C-n and M-n represent the exe-         |    |

|      | cution time of compute and memory parts in $n^{th}$ operation, respectively. | 56 |

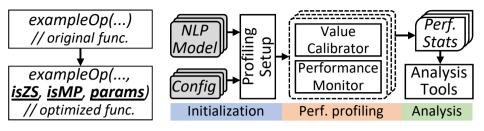

| 4.7  | The overview of our NLP-Fast toolkit. The left figure shows an exam-         |    |

|      | ple of applying NLP-Fast's optimizations by using the pre-implemented        |    |

|      | NLP-Fast libraries. The right figure presents the overview of bottle-        |    |

|      | neck analysis for given NLP models with various configurations               | 57 |

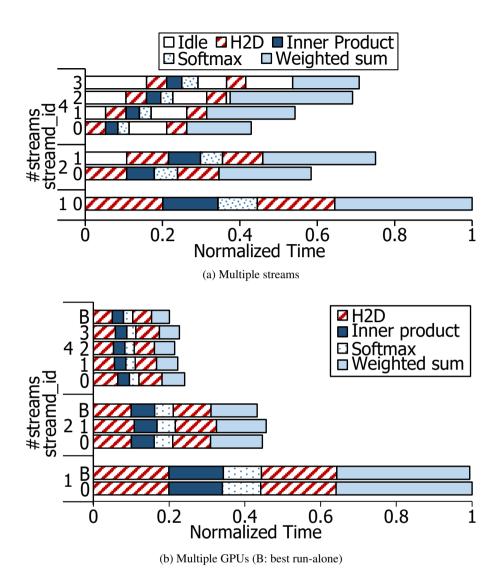

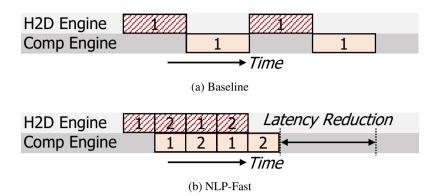

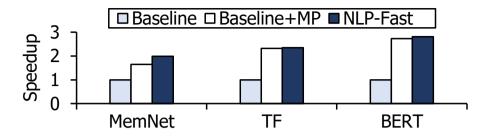

| 4.8  | Performance improvement on a single GPU with multiple CUDA streams.          |    |

|      | NLP-Fast's model partitioning enables GPU to exploit CUDA streams.           | 61 |

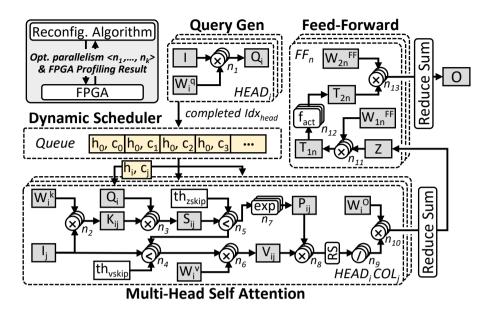

| 4.9  | The architecture of FPGA-based NLP-Fast.                                     | 63 |

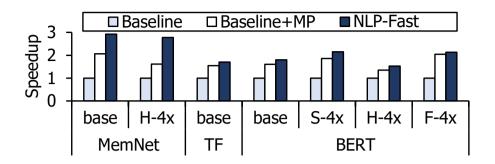

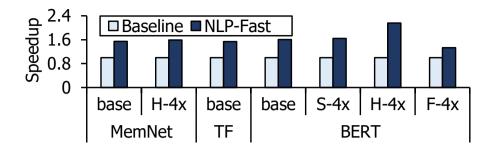

| 4.10 | Performance improvement of CPU-based NLP-Fast on various NLP                 |    |

|      | models and configurations. MP means model partitioning                       | 66 |

| 4.11 | Scalability on different memory bandwidth.                                   | 66 |

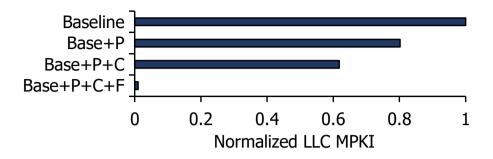

| 4.12 | Normalized LLC MPKI for each partitioning optimization. P/C/F means          |    |

|      | partial-head update, column-based algorithm, and feed-forward splitting.     | 67 |

| 4.13 | Single-GPU performance improvement of GPU-based NLP-Fast on                  |    |

|      | various NLP models.                                                          | 68 |

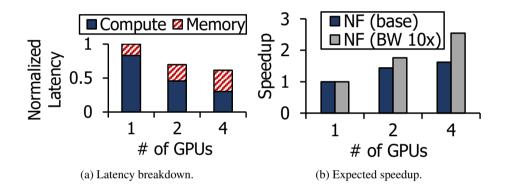

| 4.14 | The overhead analysis of multi-GPU version of NLP-Fast (NE) and              |    |

|      | the expected speedup of NLP-Fast with high bandwidth (e.g., NVLink           |    |

|      | 2.0)                                                                         | 68 |

| 4.15 | Performance of FPGA-based NLP-Fast on various models. MP means               |    |

|      | model partitioning.                                                          | 69 |

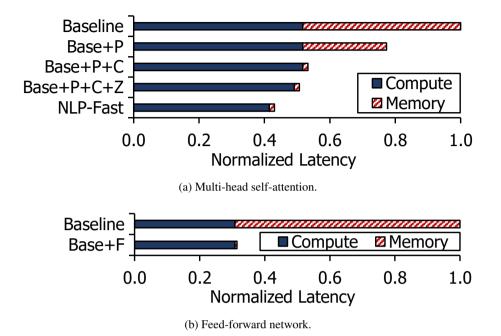

| 4.16 | Latency reduction of FPGA-based NLP-Fast on BERT. Each latency is            |    |

|      | normalized to baseline. P/C/Z/F represents partial-head update/column-       |    |

|      | based algorithm/zero skipping/feed-forward splitting, respectively           | 70 |

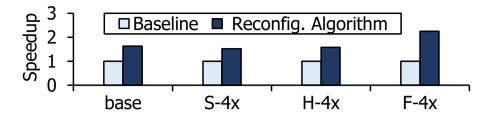

| 4.17 | Effectiveness of <i>adaptive hardware reconfiguration</i> on various config- |    |  |  |

|------|------------------------------------------------------------------------------|----|--|--|

|      | urations of BERT. S/H/F-4x are parameter configurations with a four-         |    |  |  |

|      | fold increase of s, $d_H$ , and $d_{FF}$ , respectively                      | 71 |  |  |

### Chapter 1

## **INTRODUCTION**

Recently, the rapid advancement of natural language processing (NLP) attracts massive attention from both industry and research as the technology enhancement unlocks some new products and services. For example, big technology companies (e.g., Google, Facebook) continuously develop new types of NLP workloads, which leads to technological breakthroughs. Also, many researchers and open-source communities propose specific NLP workloads for their own purpose.

*Memory-augmented neural networks* (MemNN) are getting more attention from NLP researchers as they dramatically increase the accuracy of state-of-the-art NLP tasks [130, 101, 100]. In contrast to typical neural networks (e.g., DNNs, CNNs, RNNs), these memory-augmented neural networks can discretely read and write to-kens (e.g., words, sentences) from and to an external memory, which provides the capability to make an inference with the previous history stored in memory. Also, the memory-augmented neural networks exploit the *attention mechanism* which allows a model to learn interdependence between input and output tokens. Thanks to these powerful context-aware information processing capabilities, the attention-based neural networks successfully become one of the most popular neural networks for NLP researchers.

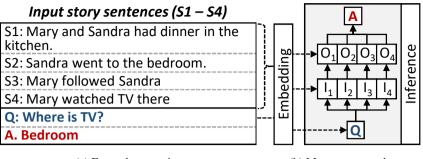

Figure 1.1 shows how MemNN processes a story with a question and an answer. In

(a) Example scenario

(b) Memory network

Figure 1.1: (a) shows an example story with a question. (b) shows where the memory network stores the story, and how it processes the question to derive the answer.

this example, MemNN first receives a four-sentence story and stores it in its memory. Next, it receives a question asking the location of TV, which can be answered only by understanding the story (e.g., the order of sentences, the relation of words across the sentences). To enable such context-aware information processing, MemNN performs an inference by utilizing the information stored in the memory against the question. In this process, the question and input sentences are converted into internal state values (i.e., Q,  $I_i$ ,  $O_i$ ), and these values are stored into memory components.

To improve the reasoning power, MemNN needs to increase the size of memory and train the network with a large-scale dataset. In fact, recent studies propose *largescale memory networks* to support growing demands for large-scale question answering tasks, but performed within the target latency [17].

These increasing demands to perform a *large-scale* Q/A task within the target latency require a *fast* and *scalable* computer infrastructure; however, the current system architecture does not provide the expected scalability due to the following reasons. First, a large-scale MemNN can suffer from the increasing number of cache misses as the data do not fit into the cache. Second, when MemNN goes through a memoryintensive phase (i.e., the embedding operation), the increased number of DRAM accesses can degrade the overall performance significantly. Third, when MemNN goes through a compute-intensive phase (i.e., the inference operation), the infrastructure can be short of the required computing resources. Lastly, a large-scale MemNN can suffer from a significant number of cache conflicts when different operations contend for the shared cache (e.g., embedding vs. inference).

In addition to this scalability issue, recent emerging NLP workloads have huge *model/config diversity* as researchers propose various types of network models according to different purposes. For example, Memory networks, developed by Facebook, is used in a simple language question answering system and language modeling tasks. Transformer, developed by Google, is proposed to solve many sequence transduction tasks (e.g., language translation). BERT, also proposed by Google, causes a stir in the NLP community by providing state-of-the-art results in a wide variety of NLP tasks (e.g., question answering, natural language inference, GLUE benchmarks).

This huge model/config diversity makes the current computer infrastructure difficult to provide enough scalability due to the follwing reasons. First, there is no work endeavoring to *holistically* optimize all operations in the NLP workloads. Second, a wide variety of parameter configurations incurs a huge *performance variation*, which makes the current system architecture difficult to find out an optimal design point. *Therefore, we need a fast, scalable, and flexible system architecture for emerging heterogeneous NLP workloads.*

In this dissertation, we introduce two novel schemes (i.e., *MnnFast*, *NLP-Fast*) to address aforementioned scalability and diversity problems in recent NLP models. We first present MnnFast a novel large-scale MemNN system architecture to achieve fast and scalable reasoning performance. MnnFast adopts three novel optimizations: *column-based algorithm with streaming*, *zero-skipping*, and *embedding cache*. To reduce the memory bandwidth overhead, MnnFast applies a modified memory-access algorithm (called *column-based algorithm*) to minimize the size of data spills and enable more efficient data chunking by transforming a large-scale memory access to many parallelized small-scale memory accesses. With the column-based algorithm ap-

plied, MnnFast can further improve its performance by performing data computation and prefetching data required for the next calculation in parallel (called *streaming optimization*). To reduce the computation overhead, MnnFast applies an optimization technique (called *zero-skipping*) to bypass computations dealing with zero or near-zero numbers stored in the memory. To solve the cache contention problem, MnnFast can make memory-intensive embedding operations either bypass the cache or stored in a dedicated memory (called *embedding cache*).

Next, we show NLP-Fast, a novel *fast*, *scalable*, and *adaptive* system architecture for the emerging NLP workloads. To cover various types of emerging NLP workloads, we extract common operations used in the NLP workloads by conducting extensive profiling and static analysis. Then, we propose three novel optimizations: *holistic* model partitioning, cross-operation zero-skipping, and model/config-adaptive hardware reconfiguration. To holistically reduce the memory accessing overhead, NLP-Fast applies three novel model partitioning techniques (i.e., partial-head update, columnbased algorithm, feed-forward splitting), which can cover all types of operations in state-of-the-art NLP workloads. These model partitioning techniques minimize the size of data spills and enable the current infrastructure to hide most memory accessing overhead by significantly reducing the working set size. To reduce the computation overhead, NLP-Fast applies an optimization technique (called cross-operation zero *skipping*) to bypass computations dealing with zero or near-zero values stored in the memory. Also, NLP-Fast carefully manages an execution time skewness caused by the zero-skipping optimization to maximize resource utilization. To increase the system flexibility, we provide further optimization (called model/config-adaptive hardware reconfiguration) to fully leverage hardware accelerators. Our adaptive hardware reconfiguration helps an HW accelerator to achieve full potential performance by finding an optimal design point.

For the evaluation, we implement both MnnFast and NLP-Fast on top of various platforms: CPU, GPU, and FPGA. For MnnFast, we first present the results of CPU-

based MnnFast with extensive profiling and analysis: memory throttling test and cache statistics. Next, we implement GPU-based MnnFast and show that our optimizations can improve single-GPU performance as well as achieve the scalable performance in the multi-GPU environment. Lastly, we build FPGA-based MnnFast with the embedding cache and measure its performance and energy efficiency.

For NLP-Fast, we present the similar results for CPU-based and GPU-based NLP-Fast (i.e., extensive profiling and analysis for CPU, scalable performance improvement for GPU). Here, we highlight the results of FPGA-based NLP-Fast with the model/config-adaptive hardware reconfiguration and measure its performance.

The rest of the dissertation is organized as follows. Chapter 2 explains the characteristics of memory networks and the state-of-the-art deep learning approaches for NLP workloads. Chapter 3 describes how MnnFast solves the performance problems to achieve the scalable performance in memory networks. Chapter 4 shows how NLP-Fast provides enough scalability for heterogeneous NLP models on various hardware platforms. Finally, Section 5 and Section 6 provide related work and conclusion, respectively.

### **Chapter 2**

### Background

In this section, we introduce a representative memory-augmented neural network, *memory networks* developed by Facebook [125, 136] (Section 2.1). We then provide state-of-the-art neural networks (including memory networks) widely used in NLP field (Section 2.2).

#### 2.1 Memory Networks

Neural networks have shown high accuracy comparable to the human on image classification and speech recognition. Recurrent neural networks (RNNs), designed to work on sequence prediction problems, derive an answer to a question from the previous reasonings [86, 57]. However, RNNs cannot memorize the previous history for a long time [15] nor handle a large amount of history due to their small memory [136]. Therefore, they cannot perform sophisticated tasks requiring a large amount of memory, such as a task which comprehends a series of books to provide useful information to users.

*Memory networks* (MemNNs), developed by Facebook, solve the problem of RNNs by augmenting neural networks with external memory [136, 125]. The large-scale external memory allows MemNN to solve the sophisticated tasks. Nowadays, thanks to its huge reasoning power, MemNN is widely used in various fields from simple dialog

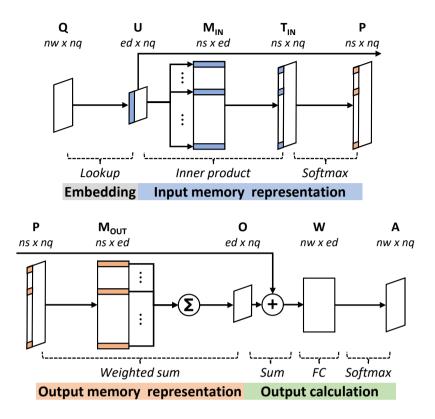

Figure 2.1: Computational steps of memory networks (MemNN). MemNN consists of embedding, input memory representation, output memory representation and output calculation. *nw* means the maximum number of words in a sentence. *nq* and *ns* are the number of questions and given story sentences, respectively. *ed* is the embedding dimension.

comprehension to large-scale question & answering system using a large-scale dataset (e.g., Wikipedia) [134, 125, 55, 34, 87]

Figure 2.1 shows a high-level overview of MemNN's computational structure. MemNN consists of two major operations: *embedding* and *inference*. The embedding operation converts a given sentence into an internal state. MemNN first converts story and question sentences into internal states, and these states are stored into input/output memory ( $M_{IN}/M_{OUT}$ ) and question state memory (U), respectively. The inference operation calculates answers to each question by going through multiple different types of computational layers: *input memory representation*, *output memory representation*, and *output calculation*. By doing so, MemNN successfully reasons out answers by exploiting the large-scale memory components. The following paragraphs describe each operation and their characteristics in more details.

**Embedding operation.** The main purpose of the embedding operation is converting an input sentence into a representative internal state vector (of size  $1 \times ed$ ). First, MemNN extracts features from texts by using a bag-of-words (BoW) model [109]. By following the BoW model, MemNN embeds each word by looking up a vector from an embedding matrix (of size  $ed \times V$ , V is the number of words in a dictionary) and sums the resulting vectors.<sup>1</sup> Internal state vectors of story sentences are stored into matrices  $M_{IN}$  and  $M_{OUT}$ , and question sentences are also embedded in a matrix U (Figure 2.1).

**Inference operation.** With the extracted internal states, MemNN calculates an answer during the inference operation which consists of three computational steps: input memory representation, output memory representation, and output calculation.

First, in the input memory representation step, MemNN calculates a probability vector, *p-vector*, which represents the correlation between the given question and each story sentence.

$$p = Softmax(u \times M_{IN}) \tag{2.1}$$

Equation (2.1) shows how to compute the p-vector. MemNN computes the p-vector by calculating dot product of the internal state vector of a question (*u*) and each memory state vector in the input matrix (M<sub>IN</sub>) and applying a softmax function (*Softmax*( $x_i$ ) =  $e^{x_i}/\sum_j e^{x_j}$ ) to the results of the dot products. By doing so, MemNN can extract the correlation of questions and sentences.

Second, in the output memory representation step, MemNN calculates a weighted sum of an output memory. The output memory  $(M_{OUT})$  holds internal state vectors corresponding to given story sentences. MemNN computes a sum over these output

<sup>&</sup>lt;sup>1</sup>Some studies multiply position weights to vectors before the sum of all vectors to preserve the order of words in the sentence.

vectors  $(m_i^{OUT})$  weighted by the probability value  $(p_i)$  extracted from the previous step:

$$o = \sum_{i} p_{i} m_{i}^{OUT} \tag{2.2}$$

The resulting vector *o* is called a response vector, and the response vector is delivered to the output calculation step to make the final answer.

In the output calculation step, MemNN generates the final prediction for the given question. It computes the sum of the response vector o and the question vector u, and the outcome passes through the fully connected (FC) layer with a weight matrix (W). Depending on the applications, the input memory and output memory representation steps iterate over several times for better results, followed by the FC layer and the softmax function.

#### 2.2 Deep Learning for NLP

Recently, neural networks have risen as new information processing paradigms in natural language processing (NLP) as they break records on many NLP tasks. In the early period, *simple* neural networks (e.g., RNNs) are used for NLP tasks; however, they cannot perform sophisticated tasks due to their limited capability of memorizing the previous history. To resolve these limitations, big technology companies (e.g., Google, Facebook, Microsoft) and open-source research communities (e.g., OpenAI) actively propose new types of *complex* NLP models (e.g., memory-augmented neural networks [136, 125], attention-based neural networks [128, 32]). Nowadays, these complex emerging NLP models are widely used in various NLP tasks from simple dialog comprehension to large-scale question & answering system using a large-scale dataset (e.g., Wikipedia) [134, 55, 34, 87].

We group emerging NLP models into three representative models (i.e., Memory networks, Transformer, BERT) and classify their key computational components by conducting extensive profiling and static analysis. Table 2.1 shows the category of

|                            | Key Computational Components |            |                |         |

|----------------------------|------------------------------|------------|----------------|---------|

|                            | Attention                    | Multi-head | Multi-head     | Feed    |

|                            | mechanism                    | attention  | self-attention | forward |

| Memory networks            | (                            |            |                |         |

| [136, 125, 17, 87, 72]     | v                            |            |                |         |

| Transformer                |                              | <b>/</b> † | (              |         |

| [128, 29, 141, 98, 12, 68] |                              | V          | V              | v       |

| BERT                       |                              |            | 1              |         |

| [32, 73, 79, 149, 28, 66]  |                              |            | ✓              | ✓       |

Table 2.1: Representative models in emerging NLP models and their key computational components.

<sup>†</sup> Encoder-decoder attention layer in the transformer decoder.

recent NLP models and their key computational components: *attention mechanism*, *multi-head attention*, *multi-head self-attention*, and *feed-forward network*.

*Memory networks* consists of multiple consecutive attention mechanisms followed by a simple fully-connected layer with softmax. *Transformer* has an encoder-decoder structure. The encoder consists of two components (i.e., multi-head self-attention, feed-forward network), and the decoder comprises three components: two components in the encoder with an additional component (i.e., multi-head attention). *BERT* consists of multiple Transformer encoders. Different from the Transformer, BERT uses GELU (not ReLU) as an activation function in the feed-forward network.

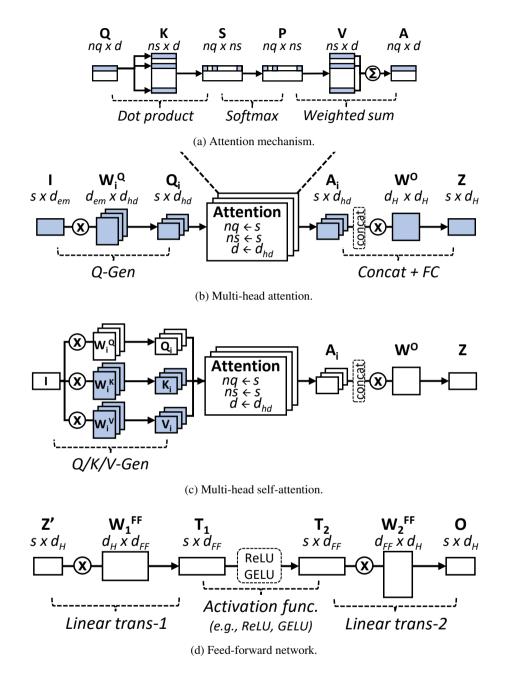

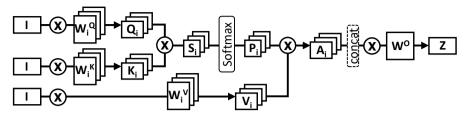

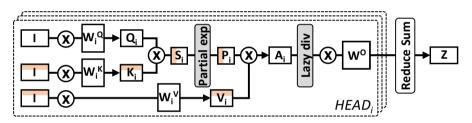

In Figure 2.2, we illustrate how each computational component operates. Figure 2.2a shows the *attention mechanism*. There are three input matrices in the attention mechanism: a query matrix ( $\mathbf{Q} \in \mathbb{R}^{nq \times d}$ ), a key matrix ( $\mathbf{K} \in \mathbb{R}^{ns \times d}$ ), and a value matrix ( $\mathbf{V} \in \mathbb{R}^{ns \times d}$ ). Here, nq and ns represent the number of queries and key-value pairs respectively, and d is the dimension of internal states. The query matrix passes through

Figure 2.2: Computational steps of key components used in state-of-the-art NLP models.

three operations (i.e., *dot product, softmax, weighted sum*) to calculate an attention result for each query. Equation (2.3) shows how to compute the attention result (A).

$$A = Attention(Q, K, V) = Softmax(Q \times K^{T}) \times V$$

(2.3)

The attention mechanism first computes a score matrix (S) by computing dot products of each query with all keys. Next, it calculates a probability matrix (P) by applying a softmax function ( $Softmax(x_i) = e^{x_i} / \sum_j e^{x_j}$ ) to the score matrix. Then, the attention mechanism computes a sum of values weighted by these probabilities to calculate the attention result (A).

Figure 2.2b illustrates how the *multi-head attention* works. The multi-head attention computes different versions of attention results ( $A_i$ ) for each head, concatenates the attention results, and applies a fully-connected (FC) operation (called *attention FC*) to the concatenated results for calculating the final output (Z). Equation (2.4) shows the details.

$$Z = MultiHead(I, K, V) = Concat(\{head_i\}_{i=1}^h) \times W^O$$

$$head_i = Attention(I \times W_i^Q, k_i, v_i)$$

(2.4)

There are three input matrices in the multi-head attention: an input matrix ( $\mathbf{I} \in \mathbb{R}^{s \times d_{em}}$ ), a key matrix ( $\mathbf{K} \in \mathbb{R}^{s \times d_H}$ ), and a value matrix ( $\mathbf{V} \in \mathbb{R}^{s \times d_H}$ ). Both key and value matrices are split into *h* sub-key/value matrices ( $k_i \in \mathbb{R}^{s \times d_{hd}}$ ,  $v_i \in \mathbb{R}^{s \times d_{hd}}$ ), respectively. Here, *h* is the number of heads, *s* means a sequence length in the model, and  $d_{em}$  and  $d_H$  are the dimensions of input and internal states, respectively. For each attention head,  $d_H$  is mapped into the lower dimension of size  $d_{hd}$ . Different from the attention mechanism, the multi-head attention conducts a query generation (*Q*-*Gen*) to calculate the query matrix from an input ( $I \times W_i^Q$ ).

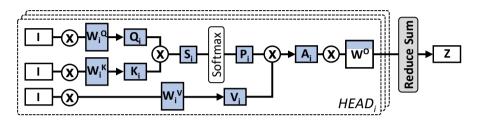

Figure 2.2c shows the *multi-head self-attention*. Compared to the multi-head attention (which needs three input matrices), the multi-head self-attention requires only one input matrix (I). Instead, it generates query/key/value matrices from the input matrix (Q/K/V-Gen) as Equation (2.5).

$$Z = MultiHeadSelf(I) = Concat(\{head_i\}_{i=1}^h) \times W^O$$

$$head_i = Attention(I \times W_i^Q, I \times W_i^K, I \times W_i^V)$$

(2.5)

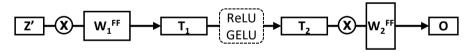

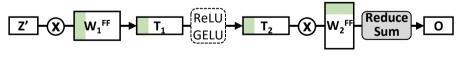

In addition to attention components, state-of-the-art NLP models also contain a *feed-forward network*. Figure 2.2d shows the high-level overview of the feed-forward network (FFN) commonly used in NLP models. There are two weight matrices for two linear transformations ( $W_1^{FF} \in \mathbb{R}^{d_H \times d_{FF}}$ ,  $W_2^{FF} \in \mathbb{R}^{d_{FF} \times d_H}$ ). Equation (2.6) shows the details.

$$O = FFN(Z') = ActFunc(Z' \times W_1^{FF}) \times W_2^{FF}$$

(2.6)

An activation function (*ActFunc*) may differ for each type of NLP models. For example, the Transformer uses *ReLU* as the activation function while BERT uses *GELU*.

### Chapter 3

## A Fast and Scalable System Architecture for Memory-Augmented Neural Networks

#### 3.1 Motivation & Design Goals

Researchers start exploiting the huge reasoning power of MemNN to solve sophisticated problems such as large-scale question answering tasks. To solve such complex problems, MemNN becomes bigger and turns into a large-scale memory network, demanding larger embedding dimension (*ed*) and more input sentences (*ns*) [17, 18, 55, 34, 87, 76]. The large-scale memory networks require high-scalability to handle the increasing computation and memory demands. The current MemNN, however, cannot achieve scalability for three reasons: *high memory bandwidth, heavy computation*, and *cache contention*.

In this section, we show the major performance bottlenecks in the state-of-the-art MemNN [125]. We first explain how memory bandwidth affects the overall performance (Section 3.1.1). Next, we provide the characteristics of MemNN computation, which requires huge compute resources (Section 3.1.2). Lastly, we show cache contention between the inference and embedding operations and quantify its performance impacts (Section 3.1.3).

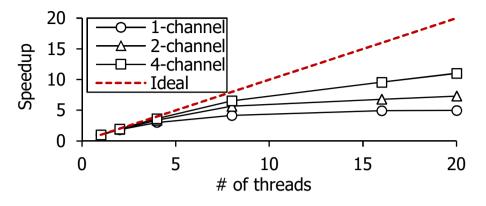

Figure 3.1: Limited scalability due to memory bandwidth. The speedup results of each channel configuration are normalized to the corresponding single-thread result.

### 3.1.1 Performance Problems in MemNN – High Off-chip Memory Bandwidth Requirements

MemNN requires a significant amount of memory bandwidth. For example, during the embedding operation, MemNN looks up the embedding matrix to convert input sentences into internal state vectors. Larger embedding dimension is good at solving complicated questions [17] but incurs higher memory pressure. Not only the embedding operation, but also the inference operation causes high memory traffic (e.g., input/output memory accesses, intermediate data spills). In the inference operation, MemNN has to load the whole input and output memory ( $M_{IN}$  and  $M_{OUT}$ , respectively) whose size is proportionate to the embedding dimension (ed) and the number of story sentences (*ns*). As the networks are getting larger, the size of these in/out memory is rapidly increasing. Furthermore, MemNN spills a large amount of intermediate data between each layer: *Inner product, Softmax*, and *Weighted sum* (Figure 2.1). These data spills are proportionate to *ns* as well. Therefore, their overheads will continuously increase.

Figure 3.1 shows how available memory bandwidth affects the scalability of MemNN. To prove the high memory bandwidth requirement is one of the key limiting factor, we measure the performance speedup with multiple threads, reducing memory bandwidth (# of memory channels). Here, our experimental environment has enough CPU cores (i.e., Xeon E5-2650 v4 12C/24T 2x), so the computation does not be a performance bottleneck. We can observe that MemNN quickly reaches a performance saturation point as the bandwidth decreases; in other words, a large amount of memory bandwidth requirements prevent MemNN from achieving scalable performance.

To overcome the memory bandwidth problem, we need more efficient memory management mechanisms to achieve good scalability. Fortunately, we find out a novel method to reduce memory bandwidth requirements and hide memory accessing overheads in the background. We propose a new computation algorithm (called *columnbased algorithm*) which minimizes the size of data spills, provides more efficient data chunking, and enable MemNN to hide most memory accessing overheads. We explain the algorithm in Section 3.2.1 for more details.

#### 3.1.2 Performance Problems in MemNN – High Computation

MemNN is not only memory-intensive but also compute-intensive application. Analyzing the characteristics and types of computation, we find out MemNN consists of a few compute-intensive operations. For example, MemNN requires multiple matrix multiplication operations (i.e., *Inner product, Weighted sum, FC layer*) known as compute-intensive tasks. Also, the *Softmax* function uses exponentiation requiring a large number of integer multiplications.

Therefore, MemNN is challenging to achieve scalable performance due to its substantial computational overheads. The amount of computation in MemNN superlinearly increases as its time complexity is  $O(n^a)$  (where  $a \ge 2.375$ ) [137]. So, even if the number of CPU cores increases, the overall system will show sublinear performance. Also, we cannot easily scale-up CPU performance due to technology constraints; the overall performance will be quickly saturated.

To overcome the high computation problem, we need more powerful computing units (e.g., GPU, FPGA, ASIC) and optimization techniques to reduce the amount of

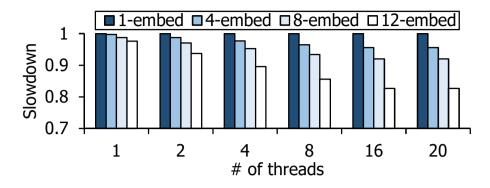

Figure 3.2: Performance degradation due to co-executed embedding threads. The slowdown results are relative to the corresponding 1-embedding thread cases. Embedding threads contend with inferencing threads for shared memory system, thus reducing the performance of MemNN.

computation. From an in-depth analysis, we find out the high potential for reducing the computation in the output memory representation step. The probability vector p represents the correlation between a question sentence and story sentences, and only a few story sentences are related to the given question; therefore, most values are close to zero. So, we propose a *zero-skipping* optimization to bypass a large amount of output computation. We explain the optimization in Section 3.2.2 for more details.

#### 3.1.3 Performance Problems in MemNN – Shared Cache Contention

MemNN consists of the embedding and inference operations, and these two operations exhibit different characteristics: memory-intensive and compute-intensive, respectively. The inference operation has a large amount of computation; to efficiently handle such a large amount of computes with high throughput, they need to keep their necessary data in a shared cache as much as possible [49]. However, as multiple question answering tasks are executed simultaneously (multi-tenant setting), two operations contend for the shared cache, which results in the cache contention problem. The embedding operation accesses a large amount of data, polluting the shared cache. Since the inference operation heavily uses the shared cache (e.g., OpenBLAS [49], Intel MKL [131]), the cache contention results in significant performance degradation.

Figure 3.2 shows the performance degradation due to the cache contention. We measure the cache contention's impact on different scales of MemNN by varying the number of simultaneously-executed embedding operations. The impact increases with the scale of MemNN and the number of embedding operations, which indicates that we cannot simply scale up MemNN to meet the increasing demands due to the contention.

To overcome the cache contention problem, we should isolate memory accesses during the embedding operation from the entire memory accesses. We can simply apply cache bypassing techniques for CPU; however, it results in high latency overheads to the embedding operation and more memory pressure on off-chip DRAM. To minimize these overheads, we propose an *embedding cache* dedicated to efficiently cache the embedding matrix. We describe a caching policy and an architecture of the embedding cache in Section 3.2.3 for more details.

#### 3.1.4 Design Goals

Based on the discussion of the performance problems so far, we set our key design goals and provide a brief description of our key ideas to achieve the scalable largescale memNN.

- Efficient memory management algorithm. It should minimize the memory bandwidth requirements. We propose the *column-based algorithm* to eliminate the intermediate data spills.

- **Reduction of computation.** It should reduce the amount of computation. We propose the *zero-skipping* optimization to decrease the output computation by skipping output operations of near-zero probability values.

- Shared cache isolation. It should avoid cache contention between the embedding and inference operations. We propose the *embedding cache* dedicated for the embedding matrix.

#### 3.2 MnnFast

#### 3.2.1 Column-Based Algorithm

MemNN suffers from a large amount of off-chip memory bandwidth (Section 3.1.1), which results in poor scalability. The current algorithm (*baseline*) consecutively calculates each layer (i.e., in-memory dot product (*Inner product*), softmax for p-value (*Softmax*), weighted sum with out-memory (*Weighted sum*)), which generates a number of intermediate data spills between each layer. Since shared cache cannot afford to hold these intermediate data, the baseline MemNN necessarily flushes and re-reads those temporary data to and from off-chip DRAM. Not only intermediate data spills but the baseline MemNN also suffers from inefficient data chunking of current matrix multiplication libraries (e.g., OpenBLAS) as their data chunking mechanisms are not MemNN-friendly.

$$o = \sum_{i} Softmax(u \times m_{i}^{IN})m_{i}^{OUT} = \sum_{i} \frac{e^{u \times m_{i}^{IN}}m_{i}^{OUT}}{\sum_{j} e^{u \times m_{j}^{IN}}}$$

(3.1)

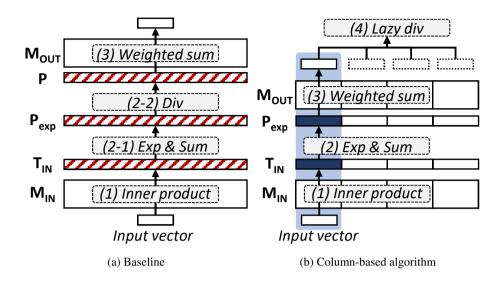

Equation (3.1) shows how baseline MemNN computes the output vector. The baseline first calculates a probability vector (p) by calculating the dot product between an input vector (u) and each in-memory vector  $(m_i^{IN})$  followed by applying the softmax function. Next, the baseline computes the sum of weighted values multiplying each output-memory vector  $(m_i^{OUT})$  by a corresponding probability value  $(p_i)$ . Figure 3.3a describes dataflow of these computational steps. The baseline generates three temporary vectors (i.e.,  $T_{IN}$ ,  $P_{exp}$ , P) for each question, and the size of these vectors is proportionate to the number of story sentences (ns) which continuously increases to support more complex question answering tasks. For example, when MemNN uses Wikipedia for training, the number of story sentences are around 200M [7]. In this case, the size of each intermediate vector is 800MB (use float data type) per each question, which easily exceeds the size of the typical shared cache (8MB – 40MB). Therefore, these temporary data are spilled to off-chip DRAM, incurring huge memory traffic and ex-

Figure 3.3: Dataflow comparison betweeen the baseline and the column-based algorithm.

acerbating the overall performance.

To reduce the size of temporary data, we propose a *column-based algorithm* enabling MemNN to partially calculate output vectors. The key idea of the proposed algorithm is a *lazy softmax calculation*, which computes the *Softmax*'s division operation at last, not in the middle.

$$o = \frac{1}{\sum_{j} e^{u \times m_{j}^{lN}}} \sum_{i} e^{u \times m_{i}^{lN}} m_{i}^{OUT}$$

(3.2)

Equation (3.2) shows how the column-based algorithm calculates the output vector. Compared to the baseline, the column-based algorithm pulls the sum  $(\sum_{j} e^{u \times m_{j}^{IN}})$  out of the outer summation  $(\sum_{i})$ . Since the sum does not depend on the index *i*, the column-based algorithm generates the same results to the baseline. By doing so, the column-based MemNN does not need to wait for the sum of entire values in the *Softmax* function and possible to calculate a part of the output vector.

Figure 3.3b describes the computational steps of the column-based algorithm and its dataflow. The column-based MemNN partitions input/output memory into multi-

ple *chunks*, and calculates partial output vectors for each chunk. The column-based MemNN computes dot products of the input vector with each in-memory vector and applies exponential function to the results, similar to the baseline. Here, in contrast to the baseline, the column-based MemNN directly calculates the weighted sum. The column-based MemNN iterates above operations over multiple chunks and accumulates each weighted sum into the output vector. After the end of the iteration, the column-based MemNN divides the output vector by the sum ( $\sum_{j} e^{u \times m_{j}^{IN}}$ ) calculated in the second step (*lazy softmax calculation*).

By doing so, the column-based MemNN can successfully reduce the size of temporary data to fit those into the cache. For example, when the chunk size is 1K, the total amount of intermediate vectors (i.e.,  $T_{IN}$ ,  $P_{exp}$ ) is 8KB per each chunk calculation; therefore, we can eliminate the entire off-chip DRAM accesses for intermediate vectors. In addition, the column-based MemNN facilitates input/output memory streaming to hide the memory access overheads. In contrast to the baseline, which cannot load input/output memory into caches due to their enormous size, the column-based MemNN can load those memory into the cache because it partially loads input/output memory per each chunk operation. We show the performance impacts of both temporary data reduction and input/output memory streaming in Section 3.4.2.

Also, the column-based MemNN can reduce the amount of computation (i.e., softmax's division operation). In the baseline, the number of division operations is proportionate to the number of story sentences *ns* (step 2-2 in Figure 3.3a). However, the column-based MemNN requires the division operations in the size of the embedding dimension *ed* (step 4 in Figure 3.3b). Since the typical size of *ed* (32 – 256) is much smaller than *ns* (i 100M), the column-based MemNN can significantly reduce the amount of computation.

Lastly, the column-based algorithm enables MemNN to achieve scale-out architecture. As the baseline computes each layer step-by-step, it cannot split each layer into multiple sub-layers due to enormous synchronization overheads. Therefore, to improve

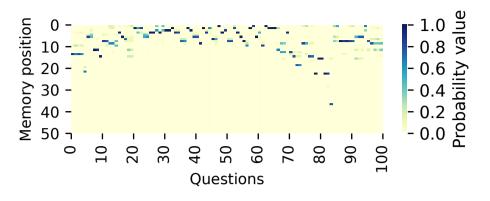

Figure 3.4: Probability value distribution. Each column represents the probability vector to each question. We use the Facebook bAbi dataset and testset [135].

the overall performance, the system should be scaled-up. Instead, the column-based MemNN can partition each layer into multiple sub-layers based on the chunk and merge the results at once. Here, synchronization overheads are negligible because the size of output results are proportionate to *ed*. Therefore, the column-based MemNN can distribute these sub-tasks into multiple compute units (e.g., CPU, GPU, FPGA) and fully utilize these resources. We evaluate this scale-out characteristic in Section 3.4.3.

#### 3.2.2 Zero Skipping

Increasing demands for large-scale MemNN result in significant computation overheads because its computation algorithm shows super-linear complexity. As described in Section 3.1.2, MemNN's compute-intensive phase (the inference operation) consists of three core computation steps: inner product, softmax, and weighted sum. For inner product and weighted sum, we need to calculate matrix multiplication known for super-linear time complexity. In this section, to reduce these computation overheads, we propose a *zero-skipping* technique and show its tradeoff between accuracy loss and the ratio of computation reduction.

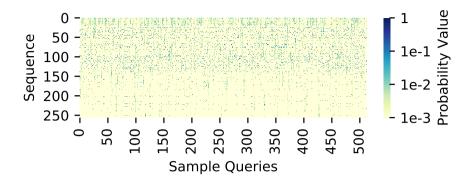

The key observation for the zero-skipping technique is that the probability vector, calculated from the inner product between a question vector and in-memory matrix,

```

Algorithm 1: MnnFast's zero-skipping algorithm.

```

```

input : The skip threshold th_{skip}

```

**input** : The probability vector *P*.

input : The output memory  $M_{IN}$

```

output: The weighted sum O.

```

$/\star\,$  Calculate the weighted sum of the output memory with the

\*/

\*/

\*/

probability values.

1  $O = [0] / \star$  Initialize the output vector.

2 foreach i < ns do

$/\star$  ns is the number of story sentences.

3 if  $p_i > th_{skip}$  then

```

4 O = O + p_i m_i^{OUT}

```

- 5 end

- 6 return O

shows a huge imbalance. Specifically, only a few values are non-zero and others are close to zero.<sup>1</sup> Figure 3.4 shows the probability value distribution. We use Facebook bAbi tasks and its dataset [135] and measure probability values to each question. In this evaluation, MemNN gets up to 50 story sentences followed by a question, and we show probability vectors for randomly chosen 100 questions. The results show that *only a few probability values are activated and most values are close to zero*. It is because the probability vector means the correlation of question sentence with story sentences, and only a few story sentences are related to the given question.

By using this characteristic, we propose the *zero-skipping* optimization to bypass a large amount of output computation. Algorithm 1 shows how MnnFast reduces the quantity of output memory computation by using the zero-skipping optimization. In contrast to the baseline which calculates all multiplications between probability values

<sup>&</sup>lt;sup>1</sup>Note that the sum of all values in the probability vector is one because these values are normalized by the softmax function.

Figure 3.5: Tradeoffs between accuracy loss and computation reduction according to the skip threshold.

and output memory vectors, the zero-skipping algorithm only computes the multiplication when the probability value is larger than a threshold value  $(th_{skip})$  (line 3 and 4). By doing so, MnnFast can skip some portions of output memory computation.

The zero-skipping optimization can significantly reduce the amount of output memory computation; however, it also sacrifices the prediction accuracy. If the skip threshold is too high, we can skip an enormous amount of computation; however, its prediction accuracy will dramatically decrease. On the other hands, if the skip threshold is too low, we cannot get enough opportunity to reduce the quantity of computation.

To quantify tradeoffs between accuracy loss and computation reduction, we measure both the accuracy loss and the ratio of computation reduction according to the different skip thresholds. We use Facebook's bAbi dataset and 20 QA tasks and get an average among the QA tasks. Both accuracy loss and computation reduction are measured by comparing with the baseline's accuracy and the amount of computation respectively.

Figure 3.5 shows the results of the evaluation. The results show that the zeroskipping optimization can achieve 97% reduction of output computation while sacrificing 0.87% of accuracy when the skip threshold is 0.1. When the skip threshold is 0.01, our optimization shows 81% reduction without any accuracy loss. Note that probability values in MemNN represent the correlation between a question and story sentences, and generally few story sentences are related to the given question; therefore, the zero-skipping optimization is highly promising for MemNN to reduce the amount of computation.

## 3.2.3 Embedding Cache

As described in Section 3.1.3, the large-scale MemNN suffers from huge cache contention between the embedding and inference operations. While the inference operation actively uses the shared cache to maximize CPU utilization, the embedding operation generates a large quantity of memory requests and pollutes the shared cache. This cache contention dramatically increases the number of cache misses for the inference operation, which results in huge performance degradation. In this section, we provide some techniques (i.e., cache bypassing, embedding cache) to solve the cache contention problem in various hardware architectures.

In the CPU environment, we can simply apply a cache bypassing technique for embedding's memory requests. By using non-temporal memory instructions [9] for the embedding operation, we can achieve the memory isolation between the inference and embedding operations. However, the bypassing techniques has two major drawbacks. First, memory access overheads of the embedding operation are limited to DRAM access latencies, which increases the execution latency of the embedding operation significantly. Second, the technique raises the amount of memory pressure as the number of DRAM accesses increases.

To overcome these limitations, we propose an *embedding cache*. The embedding cache is a dedicated cache for storing internal state vectors during the embedding operation. As explained in Section 2.1, during the embedding operation, MemNN looks up a vector from the embedding matrix per each word in a sentence. Here, the embedding cache stores pairs of word ID (represented by the BoW model) and a corresponding internal state vector. Since each access loads the vectors whose size is the embedding dimension, we set the word size of our embedding cache as the embedding dimension. With the embedding cache, we can perfectly eliminate the cache contention.

In addition, the embedding cache reduces the quantity of off-chip DRAM memory requests because of a high word locality. Linguistics researchers show that the high word locality exists in from daily conversations to literature [30]. Therefore, most lookup operations load coresponding internal vectors from the embedding cache, which leads to reducing the number of DRAM accesses.

## 3.3 Implementation

To show the effectiveness of our idea MnnFast across various platforms, we implement the baseline MemNN and MnnFast on CPU, GPU, and FPGA. While specialized architectures are getting lots of attention for machine learning, general-purpose CPU and GPU are still popular. Thus, we first validate our idea on CPU and GPU first, then we elaborate on the possible specialized hardware design, which is based on the analysis of the general-purpose architecture.

#### 3.3.1 General-Purpose Architecture – CPU

We first implement the baseline MemNN [125] and MnnFast on CPU. In Section 3.4.2, we elaborate on the potential effect of column-based MemNN based on this implementation.

**Baseline Implementation (MemNN).** We implement MemNN in C++ with opensource BLAS library, OpenBLAS [132, 140]. We implement each operation (described in Section 2.1) as a single function. Our implementation takes three input data: input memory, output memory, and question sentences. The input and output memory are usually provided by the system while users give the question sentences to the system. For interactive applications, users could provide necessary sentences to build the input and output memory containing user-specific contextual database (e.g., the book contents a user has read). We assume that all the input and output memory have already been converted into the internal data format as the data would be prepared from an external database in advance. On the other hand, as questions are generated on-the-fly by users, we assume each question is in a raw format, Bag-of-Words.

First, we convert a given question into an internal representation. The operation consists of *lookup* operations. For each word in the question, we find the corresponding embedding vector from an embedding matrix (an embedding dictionary) and sum up the vectors into a single vector to represent the question. We implement the embedding matrix as an array to retrieve embedding vectors in O(1).

Then, we inference the corresponding answer from the given knowledge database, input and output memory. The remaining computational steps (input and output memory representation and output calculation) consist of a series of *Inner product*, *Softmax*, *Weighted sum*, *Vector sum*, and *FC*. All operations excluding *Softmax* are represented in vector operations (Section 2.1). For example, *Inner product* and *Weighted sum* are implemented as matrix-vector (vector-matrix) multiplications. To implement them, we rely on OpenBLAS for efficient computation.

We parallelize each operation in a lock-step manner. To parallelize the BLASbased operations, we exploit the multi-threading feature of BLAS library. To parallelize *Softmax*, which does not rely on BLAS operations, we divide it into three steps: (1) applying the natural exponential function on the elements of a vector, (2) calculating the sum of the exponential results, and (3) normalizing the exponential results with the summation. We exploit data-level parallelization of each step with PThread.

**Column-based algorithm & zero-skipping.** The column-based algorithm simultaneously applies the inference operation on sub-chunks of the given knowledge database. We divide the knowledge database into sub-chunks, each of which contains 1000 sentences, and then make multiple worker threads to process them independently. Unlike MemNN, each thread performs a series of inference operations on only a given subchunk, not on the entire data.

27

To perform inference on sub-chunks in parallel, we use *Partial softmax* we propose in Section 3.2.1. The other operations are implemented in a similar way to the baseline MemNN. Compared to the baseline MemNN, column-based algorithm parallelizes operations not only within a single operation but also across multiple operations.

As only a few sentences of the output memory are related to a given question, we apply zero-skipping (Section 3.2.2) to *Weight sum* operation. Our implementation skips adding up output sentences whose weight (or probability) is lower than 0.1.

## 3.3.2 General-Purpose Architecture – GPU

As an intermediate step before we move on to the FPGA implementation, we evaluate the proposed algorithm on GPUs. As discussed earlier, *column-based algorithm* changes the following four consecutive steps, namely Inner product, Softmax, Weighted sum, and Sum. Therefore, we make these four steps into GPU kernels and perform memory copy from/to GPUs between kernel invocations if needed.

**GPU kernel implementation.** We use cuBLAS [1] provided with CUDA Toolkit 10.0 to perform matrix-matrix multiplications. By using the state of the art GPU BLAS library, we try to avoid any inefficiency incurred by unoptimized kernel implementation. All steps except Softmax is implemented by calling a cuBLAS function, while Softmax is implemented as one custom kernel followed by a cuBLAS function. The custom kernel of Softmax calculates exponential value of each input value, which is too simple to be further optimized, as threads are regularly mapped to one input/output memory address. The other three steps are simply translated into cuBLAS calls; specifically, Inner product is multiplication of two matrices  $M_{IN}$  and U, Weighted sum is multiplication of  $P^T$  (transpose of T) and  $M_{OUT}$ , and Sum is multiplication of a vector filled with ones and the result of the previous step.

**Column-based algorithm.** To apply column-wide data partition, we use multiple CUDA streams with one GPU, or multiple GPUs each with one stream. Each stream/GPU processes sub-matrices consisting of smaller number of sentences. Thanks

to the *column-based algorithm*, the first three steps are executed in parallel. Only the last step, which serves as reducing the partial results from different streams/GPUs, is executed by one stream/GPU. Fortunately, this step takes a negligible portion of the entire latency, as it sums up small matrices  $(ed \times nq)$  whose count equals the number of streams/GPUs.

**Zero skipping.** A pruning scheme like zero skipping is ineffective or even harmful for GPUs [91, 56]. The reason is that a warp cannot complete early unless *all* 32 threads in the warp are zero skipped, which is very unlikely. To eliminate the poor utilization problem, we can compact the pruned matrix into a sparse matrix, but the transformation itself is costly again. We implement the transformation by following an example of the official cuSPARSE document, but the latency of transforming  $M_{OUT}$ is comparable to Weighted sum stage. This means that even with an unrealistic assumption such as 100% skip ratio cannot justify the use of the sparse matrix multiplication at Weighted sum step. Even worse, sparse matrices are basically much slowly processed due to indirect memory accesses.

Currently, we consider DeftNN [56], a recently proposed GPU compaction scheme for CNNs, as the most promising option, but it is effective only for an extreme case (small nq). By adopting DeftNN, we have to eliminates the same number of rows from P and  $M_{OUT}$  from our Weighted sum stage. Meanwhile, we need sufficiently high nq to prevent the host-to-GPU memcpys from taking an excessive portion of the execution time (Section 3.4.3). As a result, we can hardly find all-zero rows, as a row of P has nq probabilities relying on *independent* questions.

#### **3.3.3** Custom Hardware (FPGA)

We design and implement an FPGA-based accelerator for MnnFast by using Vivado High-Level Synthesis (HLS). We create MnnFast's IP core from Vivado HLS and use the IP core in Xilinx Vivado Design Suite to generate a bitstream file for ZedBoard Zynq-7020 FPGA. In this section, we omit the baseline implementation because its

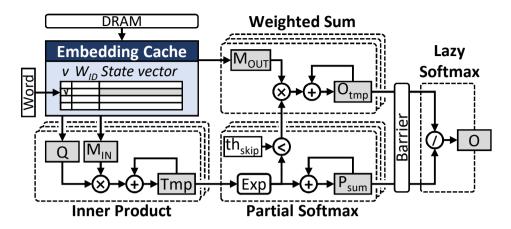

Figure 3.6: A high-level architecture of FPGA-based MnnFast.

design is straightforward.

**Column-based algorithm.** Figure 3.6 shows a high-level architecture of our FPGAbased accelerator design. First, each word in a sentence passes through the embedding cache to calculate a corresponding internal state vector. During embedding, MnnFast converts a question and new incoming story sentences into internal state vectors, and the state vectors of story sentences are appended to the input and output memory:  $M_{IN}$ and  $M_{OUT}$ , respectively.

Next, MnnFast partitions a number of story sentences ns into multiple chunks to reduce the size of intermediate data between each computational layer. For each chunk, MnnFast calculates the inner product between question vectors Q and each story vector  $m_i^{IN}$ . The resulting vector Tmp, whose size is same as ns, is delivered to the partial softmax.

In contrast to the baseline which is blocked until calculating the inner product over all chunks, MnnFast partially computes the softmax function followed by the weighted sum. During the partial softmax, MnnFast applies an exponential function to each value in the vector Tmp and accumulates the exponential results into  $P_{sum}$ . The exponential results are also delivered to the weighted sum to calculate a partial output vector  $O_{tmp}$ . After the end of the iteration over all chunks, MnnFast applies a remaining part of the softmax function, lazy softmax. MnnFast divides each value in  $O_{tmp}$  by  $P_{sum}$  and returns the final output vector O.

**Zero skipping.** To implement the zero-skipping optimization, MnnFast compares the exponential results with the skip threshold  $th_{skip}$ . If the skip threshold is larger than an exponential result, MnnFast does not calculate the weighted sum and only adds the result into  $P_{sum}$ .

As multiple partial softmax units are parallelly executed at runtime, all exponential results may not be lower than the skip threshold. In this case, we calculate the weighted sum with those values although only a few values are higher than the skip threshold. We believe that this case does not frequently occur because most probability values are zero in general. As a result, MnnFast can reduce the amount of output computation significantly.

**Embedding cache.** We design the embedding cache as a direct mapped cache. Each entry in the embedding cache consists of three fields: a valid bit (1 bit), a word ID (log2(# words in dictionary) bits), and a state vector (32 \* ed bits). By using the embedding cache, MnnFast can achieve memory isolation between the inference and the embedding operation and reduce the number of DRAM accesses, which improves the performance of the embedding operation. We show the performance impact of the embedding cache according to different cache sizes in Section 3.4.4.

## 3.4 Evaluation

## 3.4.1 Experimental Setup

We implement the baseline, the baseline with each optimization (i.e., column-based algorithm, column-based with streaming, zero-skipping, embedding cache), and Mnn-Fast in various hardware platforms: CPU, GPU, and FPGA.

CPU configuration. We compare the baseline with MnnFast on a 24-core dual-

| Entry                         | CPU  | GPU      | FPGA |

|-------------------------------|------|----------|------|

| Embedding dimension (# entry) | 48   | 64       | 25   |

| Database size (# sentences)   | 100M | 100M     | 1000 |

| Chunk-size (# sentences)      | 1000 | Variable | 25   |

Table 3.1: Memory networks configuration for the evaluation.

socket Xeon CPU system with DDR4-2400MHz 256GB memory. We run our implementation on Ubuntu 16.04 LTS and use OpenBLAS [132, 140] for BLAS operations. For evaluation, we use the following network configuration, described in Table 3.1.

**GPU configuration.** We use a SUPERMICRO SuperServer 4028GR-TRT with two Intel Xeon CPU E5-2650 v4 and six Nvidia TITAN Xp GPUs. We measure the performance of GPU-based MnnFast with Linux kernel version (4.4.0-89-generic) and CUDA Toolkit version 10.0.

**FPGA configuration.** We implement FPGA-based MnnFast on ZedBoard featuring Xilinx Zynq-7020 Soc and DDR3 memory by using Vivado HLS. Our implementation on the programmable logic (PL) runs at 100MHz with DDR3 memory operating at 533MHz. The memory has 32-bit effective width. To control MnnFast implemented on the PL, we build a monitoring program executed on the ARM Cortex-A9 processor of Zyng SoC.

**Memory network configuration.** Table 3.1 shows the configuration parameters of MemNN for the evaluation. We use a similar configuration for CPU and GPU but scale it down for FPGA due to lack of available logic cells. The embedding dimension of GPU is different to that of CPU to fully utilize streaming multiprocessors (SMs) in GPUs.

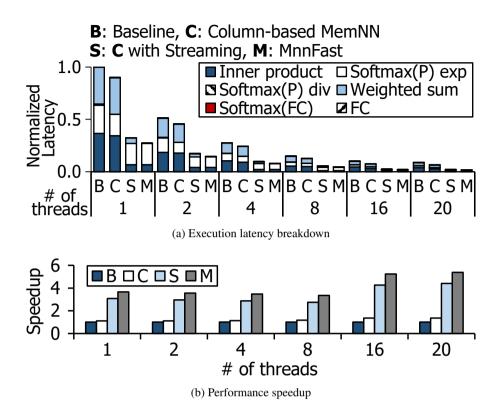

Figure 3.7: Performance of column-based algorithm on CPU.

## 3.4.2 CPU

This section shows the performance and its scalability of MnnFast compared to the baseline MemNN. To validate the key idea of our proposal, we compare the results from 1) the baseline MemNN, 2) Column-based MemNN, 3) Column-based MemNN with data streaming, and 4) MnnFast.