#### 저작자표시 2.0 대한민국

#### 이용자는 아래의 조건을 따르는 경우에 한하여 자유롭게

- 이 저작물을 복제, 배포, 전송, 전시, 공연 및 방송할 수 있습니다.

- 이차적 저작물을 작성할 수 있습니다.

- 이 저작물을 영리 목적으로 이용할 수 있습니다.

#### 다음과 같은 조건을 따라야 합니다:

저작자표시. 귀하는 원저작자를 표시하여야 합니다.

- 귀하는, 이 저작물의 재이용이나 배포의 경우, 이 저작물에 적용된 이용허락조건

을 명확하게 나타내어야 합니다.

- 저작권자로부터 별도의 허가를 받으면 이러한 조건들은 적용되지 않습니다.

저작권법에 따른 이용자의 권리는 위의 내용에 의하여 영향을 받지 않습니다.

이것은 <u>이용허락규약(Legal Code)</u>을 이해하기 쉽게 요약한 것입니다.

Disclaimer 🗖

#### M.S. DISSERTATION

# Transient Program Operation Model Considering Distribution of Electrons in 3D NAND Flash Memories

3D 낸드 플래시 메모리에서의 전자 분포를 고려한 프로그램 동작 모델링

> By Dong Chan Lee

February 2021

DEPARTMENT OF ELECTRICAL AND COMPUTER ENGINEERING SEOUL NATIONAL UNIVERSITY

# Transient Program Operation Model Considering Distribution of Electrons in 3D NAND Flash Memories

3D 낸드 플래시 메모리에서의 전자 분포를 고려한 프로그램 동작 모델링

지도 교수 신형철

이 논문을 공학석사 학위논문으로 제출함 2021 년 2 월

> 서울대학교 대학원 전기정보공학부 이 동 찬

이동찬의 공학석사 학위논문을 인준함 2021 년 2월

위 원 장 \_\_\_\_ 김 상 범

부위원장 \_\_\_\_ 신 형 철

위 원 강명곤

**Abstract**

In this paper, a new compact model for program operation of 3D

NAND flash memory was presented. Based on the understanding of the

charge trapping mechanism, an analysis of the electron distribution was

presented. A modified 1-D Poisson equation was proposed that shows better

accuracy than the existing model by reflecting the spatial distribution of

electrons trapped by the program operation. Under various conditions of

program voltage  $(V_{PGM})$  and program time  $(t_{PGM})$ , the threshold voltage shift

$(\Delta V_t)$  was extracted by TCAD (Technology Computer-Aided Design)

simulation, and we used this data to validate our new model. It also provides

validity of the model for program operation in 3D NAND flash memory along

with various TCAD analysis data.

**Keywords**: 3D NAND Flash memory, program operation, electron

distribution, charge-trap nitride

**Student Number : 2019-23620**

i

# **Contents**

| 1. I | ntroduction1                                                |

|------|-------------------------------------------------------------|

| 2. S | Simulation Setup3                                           |

| 3. F | Program operation in 3D NAND6                               |

|      | 3.1. Charge Trapping Mechanism6                             |

|      | 3.2. Parameters that affects the distribution of electrons7 |

|      | 3.3. Characteristics of ISPP                                |

| 4. F | Electrostatic Solution11                                    |

| 5. T | Transient Dynamics of Program Operation19                   |

| 6. F | Results and Discussion22                                    |

|      | 6.1. Validation of models with fixed electron charge        |

|      | 6.2. Model verification using transient program dynamics 23 |

|      | 6.3. Modeling results                                       |

| 7. ( | Conclusion33                                                |

| 8. F | Reference35                                                 |

| 9. : | 초록38                                                        |

# **Tables**

| [Table 1][Table 2] |    |

|--------------------|----|

| Figures            |    |

| [Figure 1]         | 5  |

| [Figure 2]         | 6  |

| [Figure 3]         | 7  |

| [Figure 4]         | 8  |

| [Figure 5]         | 9  |

| [Figure 6]         | 9  |

| [Figure 7]         | 10 |

| [Figure 8]         | 12 |

| [Figure 9]         |    |

| [Figure 10]        |    |

| [Figure 11]        |    |

| [Figure 12]        |    |

| [Figure 13]        | 22 |

| [Figure 14]        |    |

| [Figure 15]        |    |

| [Figure 16]        | 26 |

| [Figure 17]        |    |

| [Figure 18]        | 30 |

| [Figure 19]        | 31 |

| [Figure 20]        | 32 |

#### **Chapter 1**

#### Introduction

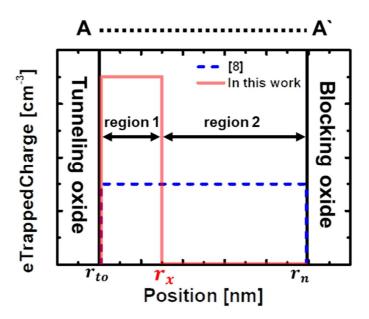

3D NAND Flash memory is considered as a promising memory technology by reducing bit cost and storing more data than NAND Flash memory with 2D planar structure and floating gate [1-3]. Since it has a gateall-around (GAA) structure, program dynamics are improved due to the high electric field at the substrate/tunneling oxide interface compared to planar devices [4-6]. To reflect structural characteristics, previous studies have analyzed transient program operation through the 1-D Poisson equation with radial coordinates [7,8]. In these existing models, the spatial distribution of trapped electrons in charge-trap nitride (CTN) was not considered, and it was assumed that the trapped electron density is uniform in all CTN regions or all electrons are located at the center of the CTN. However, according to several papers and Technology Computer-Aided Design (TCAD) simulation, electrons tunneled by transient program operation are trapped from the region close to the tunneling oxide in the CTN [9, 10]. Therefore, when using the existing model, the distribution of trapped electrons is not properly

considered, so the number of electrons and threshold voltage shift  $(\Delta V_t)$  calculation results are different from the TCAD simulation data.

In this paper, it is assumed that CTN is divided into two regions: region 1 where electron trapping occurs (close to tunneling oxide), and region 2 where electrons are not trapped, in order to reflect the distribution of trapped electrons in a compact model. A modified Poisson equation is presented accordingly, and the boundary of the regions in the CTN is determined at the point that showing best fits with the  $\Delta V_t$  value obtained through TCAD simulation. Various program voltage ( $V_{PGM}$ ) conditions are used for the model, and several TCAD analysis data were presented. The time dependence of the program operation was also considered, and the boundary setting that could reflect the variation in the distribution of electrons was also presented.

# Chapter 2

# **Simulation Setup**

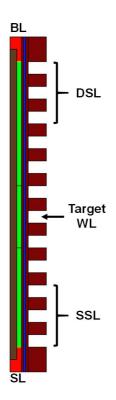

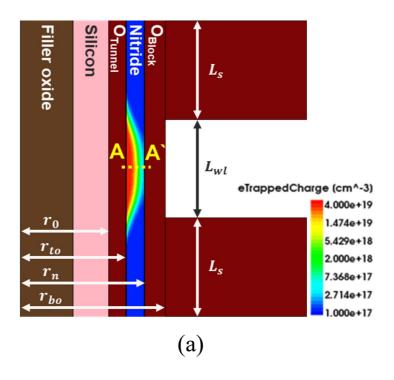

Technology computer aided design (TCAD) simulation was conducted using Synopsys Sentaurus. The device parameters used in the TCAD simulation are specified in Table 1. Fig. 1 shows the string structure of the 3D NAND Flash memory used in the TCAD simulation of this study. The string consists of 6 word-line (WL), drain selected line (DSL), source selected line (SSL), bit line (BL) and source line (SL). To reflect only the effect of the distribution of trapped electrons, the substrate was assumed to be single crystal silicon without grain boundaries. The effects of interface trap and electron emission were not considered. In this study, the program operation of 3D NAND Flash memory was assumed. The pass voltage of the unselected word lines was 6V and the voltage of the SSL was 2.4V [11]. The voltage applied to BL, SL and SSL is 0V. The voltage applied to the target word line was 12V, 14V, 16V, 18V. All voltages take a rising time of 1µs, and the simulation was performed with a total time of 9µs. The work function of the gate metal was set to 4.6 eV. Since it is important to describe the situation in the conduction band in the program operation, only the acceptor-liked trap was considered. As a tunneling mechanism, Fowler-Nordheim (FN) tunneling was used, not non-local tunneling. Since non-local tunneling includes many tunneling mechanisms such as trap assisted tunneling (TAT) and band to band tunnelling (BTBT), it is difficult to analyze only the effects of electron distribution. Shockley-Read-Hall (SRH) recombination model was used. A mobility model considering Enormal and High field saturation was also used. The threshold voltage  $(V_t)$  was defined as the voltage when a 10nA bit line current occurs by applying a constant current method [12], and  $\Delta V_t$  was defined as the difference between  $V_t$  in the initial state without trapped electrons and  $V_t$  in the programmed state with trapped electrons.

**Table 1**. Device parameters used in this work.

| Symbol                              | Definition                                     | Value                      |

|-------------------------------------|------------------------------------------------|----------------------------|

| $L_{wl}$                            | Word-line length                               | 28nm                       |

| $L_s$                               | Spacer length                                  | 28nm                       |

| $r_0$                               | Substrate radius                               | 25nm                       |

| $T_{to}$                            | Tunneling oxide thickness $(r_{to} - r_0)$     | 5nm                        |

| $T_n$                               | Charge-trap nitride thickness $(r_n - r_{to})$ | 5nm                        |

| $T_{bo}$                            | Blocking oxide thickness $(r_{bo} - r_n)$      | 6nm                        |

| $\varepsilon_{to}/\varepsilon_{bo}$ | Tunneling/Blocking oxide dielectric            | $3.9\varepsilon_0$         |

|                                     | constant                                       |                            |

| $\varepsilon_{\mathrm{n}}$          | Charge-trap nitride dielectric constant        | $7\varepsilon_0$           |

| $V_{PGM}$                           | Program voltage                                | 12V/14V/16V/18V            |

| $t_{PGM}$                           | Program time                                   | 0s to 9μs                  |

| $t_r$                               | Rising time at $t_{PGM}$                       | 1μs                        |

|                                     | Total trap density                             | $4 \times 10^{19} cm^{-3}$ |

| $rac{N_t}{\sigma_n^0}$             | Capture cross-section                          | $10^{-14} cm^2$            |

Figure 1. Cross-sectional view of string structure of 3D NAND Flash memory used in this work.

# **Chapter 3**

# **Program operation in 3D NAND**

#### 3.1. Charge Trapping Mechanism

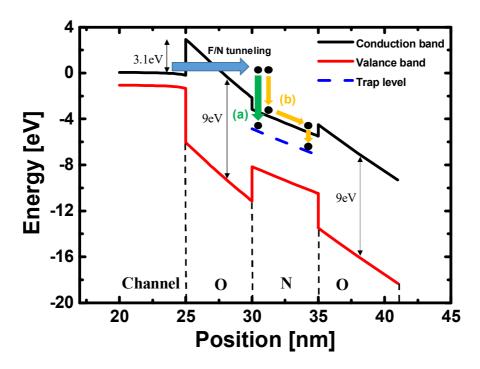

Figure 2. Tunneling and charge trapping mechanism of 3D NAND Flash memory. (a) Electrons trapped in a region close to tunneling oxide. (b) Electrons that are not trapped immediately after tunneling and are trapped by the energy barrier of the CTN layer and blocking oxide.

Fig. 2 shows tunneling and charge trapping mechanism of 3D NAND Flash memory. Tunneled electrons are probabilistically trapped by parameters such as capture cross-section and trap density. Some untrapped electrons

move within the conduction band of the CTN layer. And it is trapped by the energy barrier with the blocking oxide.

#### 3.2. Parameters that affects the distribution of electrons

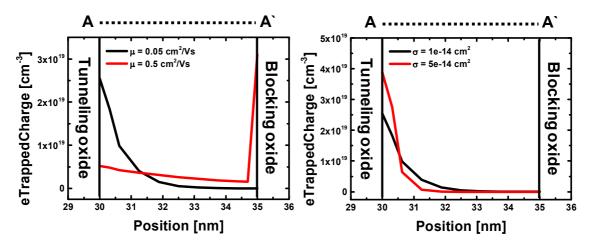

Figure 3. (a) Distribution of electrons according to mobility during program operation. (b) Distribution of electrons according to capture cross-section during program operation.

The movement of electrons in the conduction band is determined by the mobility and capture cross-section of the CTN layer. Mobility and capture cross-section eventually affect the distribution of electrons. Fig. 3 (a) is the electron distribution of the CTN layer according to mobility in the program operation. The greater the mobility, the stronger the movement of electrons by the field in the conduction band. Therefore, electrons are mainly distributed in the region near the blocking oxide. Conversely, in the case of

small mobility, electrons are mainly distributed in the region near the tunneling oxide because the tendency to be captured is stronger. Fig. 3 (b) is the distribution of electrons according to the capture cross-section. The larger the capture cross-section, the greater the probability of electron trapping and the electron distribution is formed in the region near the tunneling oxide.

#### 3.3. Characteristics of ISPP.

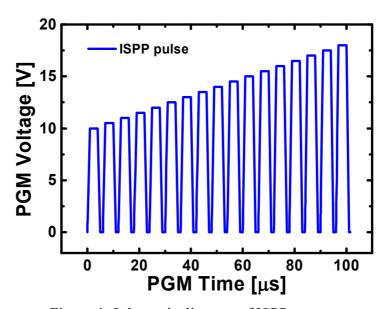

Figure 4. Schematic diagram of ISPP.

Fig. 4 shows the pulse shape of the Incremental step pulse program (ISPP). In the real industry, 3D NAND Flash memory is programmed through ISPP [13-17]. Through this, it is possible to narrow the distribution of  $V_t$ , thereby improving reliability.

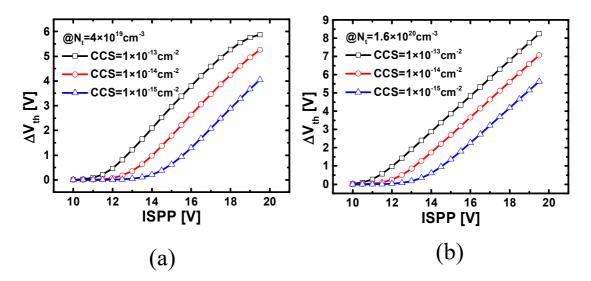

Figure 5.  $V_t$  shift by ISPP at (a)  $N_t = 4 \times 10^{19}$  and (b)  $N_t = 1.6 \times 10^{20}$

Figure 6. Program efficiency at (a)  $N_t = 4 \times 10^{19}$  and (b)  $N_t = 1.6 \times 10^{20}$

Fig. 5 shows  $V_t$  shift by ISPP. The higher the  $N_t$ , the more the  $V_t$  shift occurs because the trapping probability increases. Also, the larger the capture

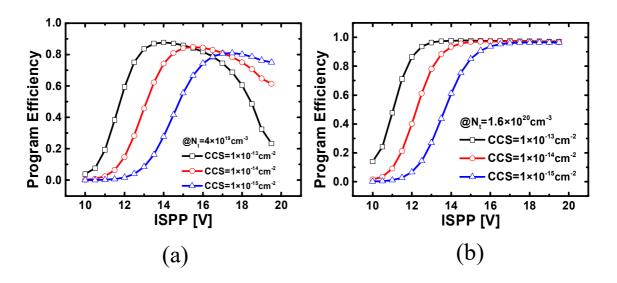

cross-section (CCS), the more trapping occurs. Therefore, a lot of  $V_t$  shift appears. Fig. 6 shows the program efficiency in ISPP operation. When  $N_t$  is small, the number of empty traps rapidly decreases during program operation. Therefore, even if the ISPP voltage increases, the program efficiency decreases. Conversely, when  $N_t$  is large, since the number of empty traps is relatively large, a decrease in program efficiency occurs at a higher voltage. Fig. 5 and Fig. 6 are derived using differential equations associated with trapping in ref [8]. As a result of reflecting only the parameters that directly affect in trapping mechanism, a graph similar to the program efficiency was derived as shown in Fig. 7.

Figure 7. Results due to parameters related to program efficiency at (a)  $N_t = 4 \times 10^{19}$  and (b)  $N_t = 1.6 \times 10^{20}$

# **Chapter 4**

# **Electrostatic Solution**

Table 2 shows the number of trapped electrons and the results of  $\Delta V_t$  calculations derived from the TCAD simulation and the previous model given in [8]. When substrate effect (potential drop due to channel potential  $(V_{ch})$  and flat band voltage  $(V_{fb})$ ) is considered, the voltage applied only to the tunneling oxide/CTN/blocking oxide (ONO) layer is reflected in the model, and the  $\Delta V_t$  calculation result becomes similar to TCAD simulation data, but there are still errors. The reason for these errors is that the previous study [8] modeled assuming uniform trapped electron density  $(n_t; \text{units:cm}^{-3})$  for all regions in CTN without considering the spatial distribution and number of electrons.

**Table 2.** The number of trapped electrons and  $\Delta V_t$  at  $V_{PGM}$ =14V,  $t_{PGM}$ =9 $\mu$ s

|                              | # of eTrappedCharge | $\Delta V_t$ [V] |

|------------------------------|---------------------|------------------|

| TCAD                         | 59                  | 0.301            |

| [8] without substrate effect | 145                 | 0.751            |

| [8] with substrate effect    | 68                  | 0.35             |

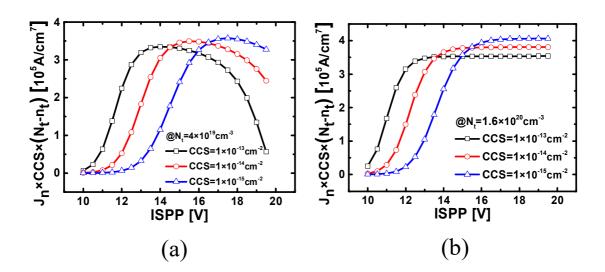

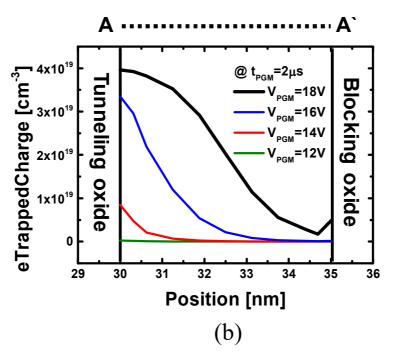

Figure 8. TCAD simulation results of 3D NAND Flash memory .(a) Cross-sectional view of unit cell structure in the programmed state. (b) Trapped electron density according to the program voltage  $(V_{PGM})$  along the direction of A-A` (middle position of the target cell).

Fig. 8 (a) is a result of the transient simulation of program operation in TCAD, showing that the electrons are mainly trapped in the CTN region close to the tunneling oxide. Also, Fig. 8 (b) shows that the trapped electron distribution changes as  $V_{PGM}$  increases, but still shows the same tendency. Therefore, the errors occur in the calculated number of electrons and  $\Delta V_t$ , because of the assumption of the previous model. To solve this problem, we divided CTN into two regions as shown in Fig. 9: region 1 where electron trapping occurs, and region 2 that does not.

Figure 9. Conceptual image of the trapped electron distribution in CTN assumed in [8] (dash) and in this work (line).

This assumption allows the spatial distribution of trapped electrons to be reflected in the model so that the number of electrons and  $\Delta V_t$  can be calculated accurately. The boundary-value of region 1 and region 2 was set to a new parameter  $r_x$  as follows:

$$r_{x} = r_{to} + \eta T_{n} \tag{1}$$

where  $\eta$  is a proportional factor associated with the thickness of the nitride  $(T_n)$ , with a value between 0 and 1. The value of  $\eta$  will be determined when fitting the  $\Delta V_t$  with TCAD data by applying transient dynamics in results section. The electrostatics of the 3D NAND flash memory can be calculated by solving a modified 1-D Poisson equation in radial coordinates that considering the distribution of trapped electrons is taken into account:

$$\frac{1}{r}\frac{\partial}{\partial r}\left(r\frac{\partial V(r)}{\partial r}\right) = -\frac{qn_t}{\varepsilon_n}\left[H(r-r_{to}) - H(r-r_{\chi})\right] \tag{2}$$

where V(r) is the electrostatic potential, and q is the electron charge. The Heaviside step function was used to assume that uniform  $n_t$  exists only in region 1. By solving the modified Poisson equation at (2), we can obtain expressions for V(r) and electric field F(r) in four regions:

$$V(r) = \begin{cases} C_1 \ln \frac{r}{r_0} & (r_0 < r < r_{to}) \\ \frac{qn_t}{4\varepsilon_n} (r^2 - r_{to}^2) + C_2 \ln \frac{r}{r_{to}} + C_1 \ln \frac{r_{to}}{r_0} & (r_{to} < r < r_x) \\ C_1 \ln \frac{r_{to}}{r_0} + C_2 \ln \frac{r_x}{r_{to}} + C_3 \ln \frac{r}{r_x} + \frac{qn_t}{4\varepsilon_n} (r_x^2 - r_{to}^2) & (r_x < r < r_n) \end{cases}$$

$$(V_{PGM} - V_{ch} - V_{fb}) - C_4 \ln \frac{r_{bo}}{r} & (r_n < r < r_{bo})$$

$$(3)$$

$$F(r) = -\frac{\partial V(r)}{\partial r} = \begin{cases} -\frac{C_1}{r} & (r_0 < r < r_{to}) \\ -\frac{qn_t}{2\varepsilon_n} r - \frac{C_2}{r} & (r_{to} < r < r_{\chi}) \\ -\frac{C_3}{r} & (r_{\chi} < r < r_{\eta}) \\ -\frac{C_4}{r} & (r_{\eta} < r < r_{bo}) \end{cases}$$

(4)

Note that the setting of the boundary condition is the same as [8], except for the substrate effect is reflected in the model. The expression for constants  $(C_1 \sim C_4)$  and  $\alpha$  is defined as follows:

$$C_{1} = \frac{V_{PGM} - V_{ch} - V_{fb}}{\alpha} + \frac{qn_{t}}{2\alpha} \left[ \frac{1}{\varepsilon_{n}} r_{to}^{2} \ln \frac{r_{x}}{r_{to}} - \left( \frac{1}{\varepsilon_{ho}} \ln \frac{r_{bo}}{r_{n}} + \frac{1}{\varepsilon_{n}} \ln \frac{r_{n}}{r_{x}} + \frac{1}{2\varepsilon_{n}} \right) (r_{x}^{2} - r_{to}^{2}) \right]$$

$$(5)$$

$$C_2 = \frac{\varepsilon_{to}}{\varepsilon_n} C_1 - \frac{q n_t}{2\varepsilon_n} r_{to}^2 \tag{6}$$

$$C_3 = \frac{\varepsilon_{to}}{\varepsilon_n} C_1 + \frac{q n_t}{2\varepsilon_n} (r_x^2 - r_{to}^2) \tag{7}$$

$$C_4 = \frac{\varepsilon_{to}}{\varepsilon_{ho}} C_1 + \frac{q n_t}{2\varepsilon_{ho}} (r_x^2 - r_{to}^2)$$

(8)

$$\alpha = \ln \frac{r_{to}}{r_0} + \frac{\varepsilon_{to}}{\varepsilon_n} \ln \frac{r_n}{r_{to}} + \frac{\varepsilon_{to}}{\varepsilon_{bo}} \ln \frac{r_{bo}}{r_n}$$

(9)

where  $\alpha$  is same formula as [8]. In equation (5), values calculated through TCAD simulation were applied to  $V_{ch}$  and  $V_{fb}$ . These values should be subtracted from the total  $V_{PGM}$  to reflect only the electrostatic potential across the ONO layer. The values of  $V_{ch}$  and  $V_{fb}$  are extracted through TCAD simulation.

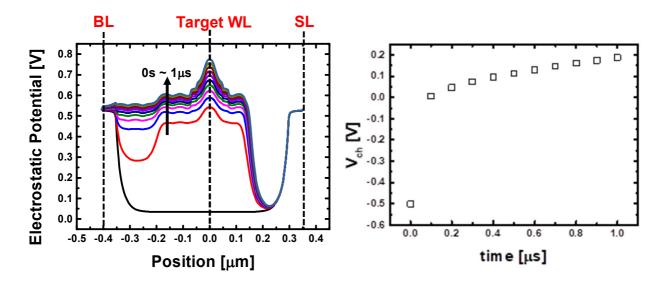

Figure 10. (a) Electrostatic potential of string structure in 3D NAND Flash memory at rising time. (b) Channel potential calculated based on (a)

Figure 11. Flat voltage extraction process according to  $V_{PGM}$  change using TCAD simulation.

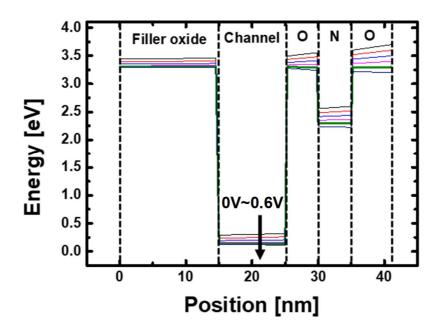

Fig. 10 (a) shows electrostatic potential of string structure in 3D NAND Flash memory at rising time. Based on (a),  $V_{ch}$  is calculated and it is shown in Fig. 10 (b). Since it is a string structure, the  $V_{ch}$  is calculated as the potential difference between the target WL and BL.  $V_{ch}$  was reflected to increase linearly within rising time. The  $V_{ch}$  after rising time is assumed to have a constant value because there is no significant change. Fig. 11 shows  $V_{fb}$  extraction process according to  $V_{PGM}$  change using TCAD simulation. From (4) and (5),  $\Delta V_t$  is calculated as the amount of change in  $V_{PGM}$  required to recover the electric field of the substrate/tunneling oxide interface  $(F_t)$  when  $n_t$ =0, and the following equation is obtained:

$$\Delta V_t = -\frac{qn_t}{2} \left[ \frac{1}{\varepsilon_n} r_{to}^2 \ln \frac{r_x}{r_{to}} - \left( \frac{1}{\varepsilon_{top}} \ln \frac{r_{bo}}{r_n} + \frac{1}{\varepsilon_n} \ln \frac{r_n}{r_x} + \frac{1}{2\varepsilon_n} \right) (r_x^2 - r_{to}^2) \right]$$

(10)

# Chapter 5

# **Transient Dynamics of Program Operation**

The FN equation was used as a theoretical expression for tunneling current density  $(J_n)$  [18, 19].

$$J_n = AF_i^2 exp\left[-\frac{B}{F_i}\right] \tag{11}$$

$$A = \frac{q^3 m_{si}}{16\pi^2 \hbar m_{ox} q \phi_B} \tag{12}$$

$$B = -\frac{4\sqrt{2m_{ox}(q\phi_B)^3}}{3\hbar qF_{ox}} \tag{13}$$

where A and B were determined by considering the potential barrier ( $\emptyset_B=3.1eV$ ), effective tunneling mass of the electron ( $m_{ox}=0.42m_0$ ), and electron mass in silicon ( $m_{si}=0.26m_0$ ). Same values were used for both TCAD simulation and the model ( $A=3.07\times 10^{-7}~\text{A/V}^2$ ,  $B=2.41\times 10^{-7}~\text{A/V}^2$ ).

10<sup>8</sup> V/cm). The transient dynamics of program operation is expressed by the following equation [20]:

$$\frac{dn_t}{dt} = \frac{J_n}{q} \left( \frac{r_{to}}{r_{to} + \gamma t_n} \right) \sigma_n^0 (N_t - n_t) \tag{14}$$

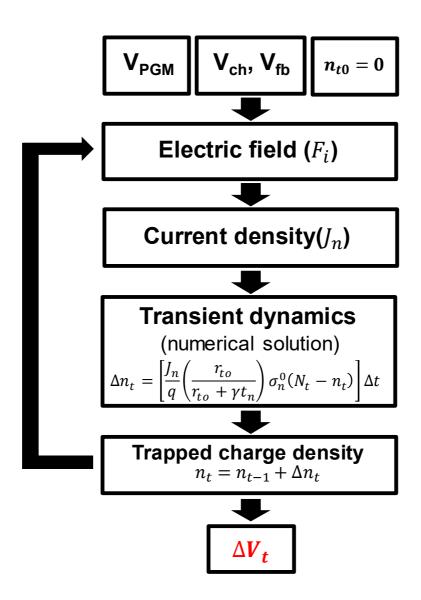

Here, the new parameter  $\gamma$  is a charge centroid factor related to region 1 where electron trapping occurs in CTN and corresponds to  $\eta/2$ . In [8], the value of  $\gamma$  was a constant of 1/2 because electron trapping was assumed in all areas within the CTN. Since the effects caused by electron emission were not considered in this study, the related formula was excluded from (14). Fig. 12 shows the modeling methodology in this study. Since there is no analytical solution for (14), we calculated it numerically for discontinuous time. Program voltage and substrate effect were considered. Starting from the initial condition of  $n_t = 0$ ,  $F_i$  and  $J_n$  were calculated, and then the increase in trapped electron density  $(\Delta n_t)$  was calculated. The  $\Delta V_t$  was derived by the modified  $\,n_t\,$  value, and all of the processes were repeated with increasing time step ( $\Delta t$ ). This allows  $\Delta V_t$  characteristics for time to be derived from 3D NAND flash memory. The value of  $\Delta t$  is  $2 \times 10^{-10}$ s, and the smaller the time step, the more accurate the results can be obtained.

Figure 12. Modeling methodology for transient program operation. The numerical solution is derived as parameters are calculated repeatedly for each time step ( $\Delta t = 2 \times 10^{-10}$ s).

# Chapter 6

#### **Results and Discussion**

In this chapter, before using the modelling results, verification of the existing model [8] by TCAD simulation was done first. Subsequently, the data of  $\Delta V_t$  derived through TCAD simulation was fitted using modelling results. The value of  $\eta$  was used for fitting, and the fitting result showg good agreement with TCAD simulation data.

#### 6.1. Validation of Models with Fixed Electron Charge

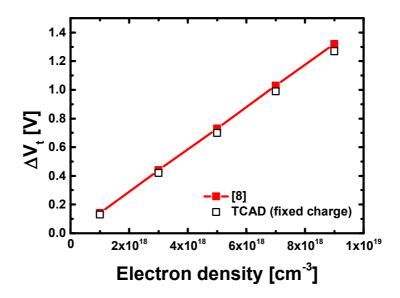

Figure 13. Modeling methodology for transient program operation. The numerical solution is derived as parameters are calculated repeatedly for each time step ( $\Delta t = 2 \times 10^{-10}$ s).

Through TCAD simulation and previous model [8], model suitability in uniform electron distribution was determined. Fig. 13 shows the  $\Delta V_t$  calculated according to the electron density through the previous model in [8] and TCAD simulation. In TCAD simulation, a fixed electron density was set by assuming uniform electron distribution in all regions of the CTN in the target cell. Since the spatial distribution and the number of the electrons were set the same, a slight error was caused by physical phenomena that reflected only in TCAD simulation. However, it is negligible because it is not large enough to affect the modeling process.

#### **6.2. Model Verification Using Transient Program Dynamics**

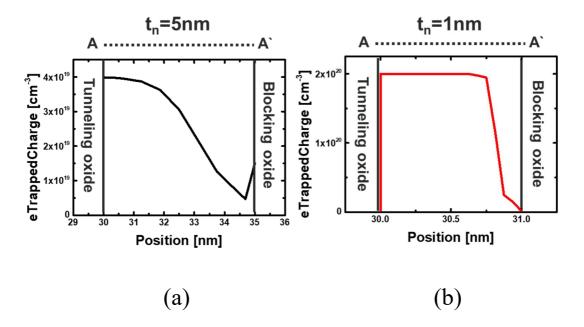

The effects of electron distribution in transient dynamics were also analyzed as well as setting fixed electron density. Fig. 14 (a) shows the electron distribution when the nitride thickness is 1 nm, and Fig. 14 (b) shows that of 5nm. As the nitride thickness decreases, the total number of traps decreases. Thus, the total trap density was set to increase for equalize the total number

of traps. When the nitride thickness was 1 nm, the trap density was set to  $2 \times 10^{20} cm^{-3}$ . As the nitride thickness decreases, the effect of word line voltage on the channel increases. Therefore, the electric field is formed stronger on the channel/tuning oxide and the current density increases. This causes more trapping of electrons, and the distribution of electrons is closer to the uniform distribution condition.

Figure 14. Electron distribution relating to the thickness of nitride at  $V_{PGM}$ = 18V. (a) 5 nm (b) 1 nm

Figure 15. Result of program with different thickness of nitride. (a) 5nm (b) 2.5nm (c) 1nm

Fig. 15 shows the program results when the thickness of the nitride is different. The model of [8] is used here. In [8], uniform electron distribution was assumed without considering the distribution of electrons. Therefore, the model is similar to the TCAD data when the most similar nitride thickness is 1 nm. The error rate is 19% at  $t_n$ =5nm, 12% at  $t_n$ =2.5nm, and 5% at  $t_n$ =1nm.

From this, it can be seen that the distribution of electrons is a matter to be considered in the program model.

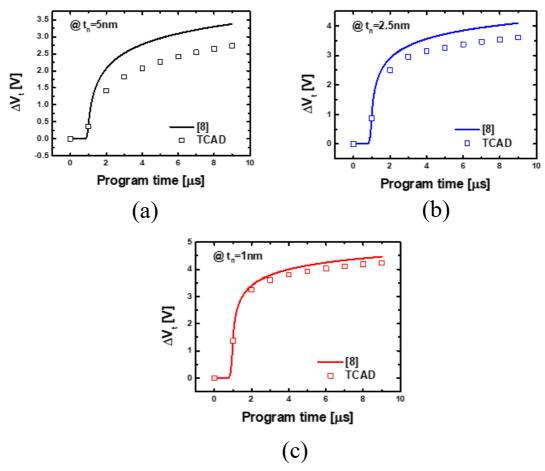

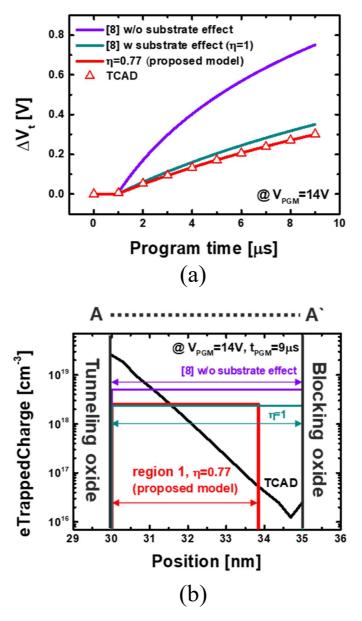

Figure 16. Modeling results at  $V_{PGM}=14V$ .

- (a) (Symbols)TCAD data and (lines)calculated result for [8],  $\eta$ =1 and  $\eta$  =0.77(proposed model)

- (b) Trapped electron density at  $9\mu$ s in (a).

#### **6.3. Modeling Results**

Fig. 16 (a) shows the  $\Delta V_t$  calculated by applying transient dynamics. In the case of  $\eta = 0.77$  that using our model, the results are consistent with the TCAD data at all  $t_{PGM}$ , and it is more accurate than the previous model in [8]. For reference, when  $\eta = 1$  is applied to our model, the calculation results are the same as the results of [8] with considering the substrate effect. Fig. 16 (b) shows the  $n_t$  according to the position in CTN, and it was calculated by TCAD and model when  $t_{PGM} = 9\mu s$  in Fig. 16 (a). In our proposed model,  $r_{x}$  and region 1 were set according to the value of  $\eta$ , and the  $n_{t}$  was determined by the solution of the modified 1-D Poisson equation. The number of trapped electrons calculated based on  $n_t$  and the volume of the CTN layer in the proposed model ( $\eta = 0.77$ ) was 55, which is closer to TCAD data than the results calculated through [8] in Table 2.

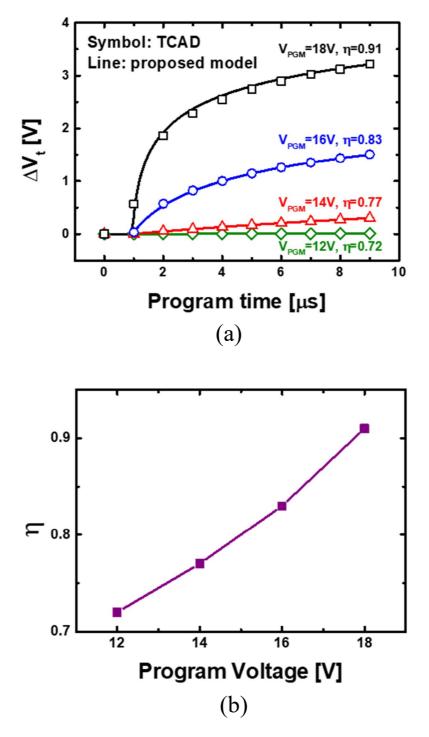

Figure 17. Modeling results at various  $V_{PGM}$

- (a) (Symbols)TCAD data and (lines) Proposed model that corrected the value of  $\eta$ .

- (b) Best fitting result of  $\eta$  for each program voltage.

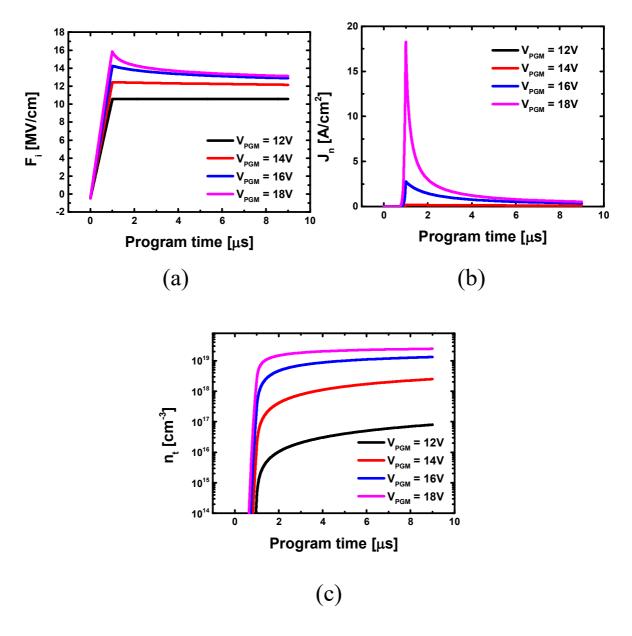

Fig 17 (a) shows the  $\Delta V_t$  fitted for the  $t_{PGM}$  in various  $V_{PGM}$ . It is shown that the model considering the distribution of electrons agrees well with the TCAD simulation data. Fig. 17 (b) shows the value of  $\eta$  with the best fitting result for each  $V_{PGM}$  in Fig. 17 (a), where its values are proportional to  $V_{PGM}$ . This indicates that the proposed model could reflects the tendency for the expansion of the trapped electron distribution according to  $V_{PGM}$  as mentioned in Fig. 8 (b). Fig. 18 (a) shows the electric field when the proposed model reflecting the transient program operation is applied. It was calculated by equation (4). Fig. 18 (b) shows the calculation result of the current density, which was calculated by Equation (11). The electric field and current density show the greatest values at 1µs at the end of the rising time. The reason for this is that after the rising time, the  $V_{PGM}$  is constant and the electric field decreases as the trapped electrons increase. Fig. 18 (c) is the calculation result of trapped electron density, and was calculated by Equation (14).

Figure 18. The results calculated by the proposed model.

- (a) Electric field

- (b) Current density

- (c) Trapped electron density

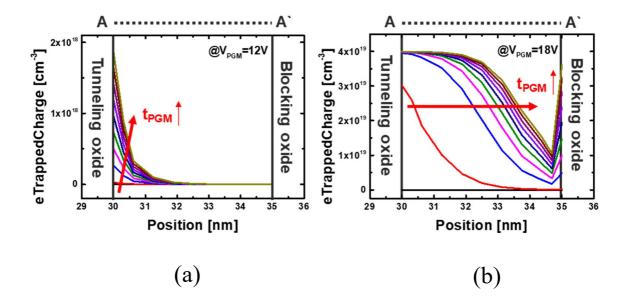

Figure 19. The variation in trapped electron density as the program time( $t_{PGM}$ ) increases.

- (a)  $V_{PGM} = 12V$

- (b)  $V_{PGM} = 18V$

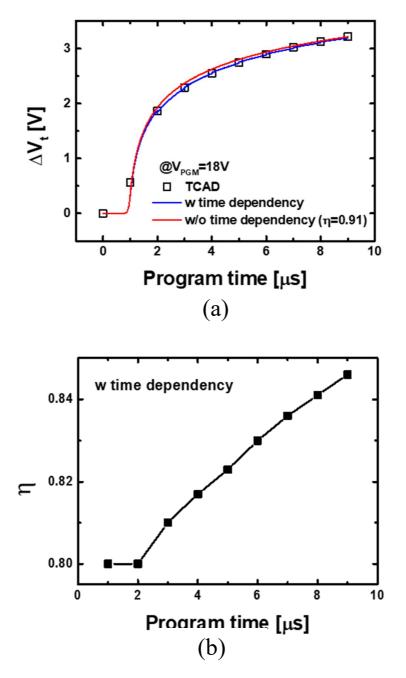

Fig. 19 is a TCAD simulation results showing the distribution and amount of trapped electrons with increasing  $t_{PGM}$  at (a) $V_{PGM}$ =12V and (b) $V_{PGM}$ =18V. Because  $F_i$  and  $J_n$  are small in low  $V_{PGM}$ , fewer electron trapping occurs, resulting in less variation in the distribution of trapped electrons over  $t_{PGM}$ . Conversely, in high  $V_{PGM}$ , there is a large variation in trapped electrons distribution. In order to reflect this characteristic more accurately, at high  $V_{PGM}$ ,  $\eta$  should be set to increase in proportion to  $t_{PGM}$ . Fig 20 (a) shows a  $\Delta V_t$  fitted over  $t_{PGM}$  at  $V_{PGM}$ =18V and the result is more accurate when

time dependency is considered. Here, the value of  $\eta$  changed in proportion to the  $t_{PGM}$  is shown in Fig. 20 (b).

Figure 20. (a) (Symbols)TCAD data and (lines) the proposed model for the case where  $\eta$  is time-dependent and when it is time-independent at  $V_{PGM}=18V$ . (b) the best fitting result of  $\eta$  for each  $t_{PGM}$ . The  $\eta$  was set for every  $1\mu$ s

# Chapter 7

#### **Conclusions**

In this study, a compact model for transient program dynamics in 3D NAND Flash memories was presented. The simulation setup and basic charge trapping mechanism were described. Mobility and capture cross-section in the CTN layer are parameters that affect electron distribution. These parameters were evaluated by TCAD simulation. The effect of trap density on program efficiency was also investigated. The effect of electron distribution on the program model was also analyzed. Through TCAD simulation, it was assumed that the fixed electron density was uniform in the CTN layer, and the accuracy of the existing model was verified. In addition, by controlling the thickness and trap density of the CTN layer in transient simulation, it was proved that the closer the uniform electron distribution is, the more the existing model is consistent with the TCAD simulation results. This suggests that electron distribution should be considered in the modeling process of transient program dynamics. The 1-D Poisson equation was modified so that our model reflects the trapped electron distribution in CTN layer effectively.

The CTN was divided into two regions, and it was assumed that electron trapping occurred only in the region close to the tunneling oxide. The parameter for determining the boundary value of the two regions were used to fit the  $\Delta V_t$  correctly. The model was verified at various program voltages. The current density, interface field, and trapped electron density, which are also derived in the process of deriving the delta  $\Delta V_t$ , are also presented. Lastly, the program time dependence was considered, and the accuracy was improved.

#### Reference

- [1] TANAKA, H., et al. Bit cost scalable technology with punch and plug process for ultra high density flash memory. In: 2007 IEEE Symposium on VLSI Technology. IEEE, 2007. p. 14-15.

- [2] KATSUMATA, Ryota, et al. Pipe-shaped BiCS flash memory with 16 stacked layers and multi-level-cell operation for ultra high density storage devices. In: 2009 Symposium on VLSI Technology. IEEE, 2009. p. 136-137.

- [3] JANG, Jaehoon, et al. Vertical cell array using TCAT (Terabit Cell Array Transistor) technology for ultra high density NAND flash memory. In: 2009 Symposium on VLSI Technology. IEEE, 2009. p. 192-193.

- [4] HSU, Tzu-Hsuan, et al. A high-speed BE-SONOS NAND flash utilizing the field-enhancement effect of FinFET. In: 2007 IEEE International Electron Devices Meeting. IEEE, 2007. p. 913-916.

- [5] HSU, Tzu-Hsuan, et al. Physical model of field enhancement and edge effects of FinFET charge-trapping NAND Flash devices. IEEE transactions on electron devices, 2009, 56.6: 1235-1242.

- [6] NOWAK, Emmanuel, et al. In-depth analysis of 3D silicon nanowire SONOS memory characteristics by TCAD simulations. In: 2010 IEEE International Memory Workshop. IEEE, 2010. p. 1-4.

- [7] KIM, Doo-Hyun, et al. Program/erase model of nitride-based NAND-type charge trap flash memories. *Japanese Journal of Applied Physics*, 2010, 49.8R: 084301.

- [8] AMOROSO, Salvatore Maria, et al. Semi-analytical model for the transient operation of gate-all-around charge-trap memories. IEEE transactions on electron devices, 2011, 58.9: 3116-3123.

- [9] KANG, Ho-Jung, et al. Space program scheme for 3-D NAND flash memory specialized for the TLC design.

In: 2018 IEEE Symposium on VLSI Technology. IEEE, 2018. p. 201-202.

- [10] OH, Dongyean, et al. TCAD simulation of data retention characteristics of charge trap device for 3-D NAND flash memory. In: 2015 IEEE International Memory Workshop (IMW). IEEE, 2015. p. 1-4.

- [11] . KANG, Myounggon; KIM, Yoon. Natural local self-boosting effect in 3D NAND flash memory. IEEE Electron Device Letters, 2017, 38.9: 1236-1239.

- [12] Bazigos, Antonios, et al.: "An adjusted constant-current method to determine saturated and linear mode threshold voltage of MOSFETs." IEEE Transactions on Electron Devices 58.11 (2011): 3751-3758.

- [13] Lue, Hang-Ting, et al. "Study of incremental step pulse programming (ISPP) and STI edge effect of BE-SONOS NAND flash." 2008 IEEE International Reliability Physics Symposium. IEEE, 2008.

- [14] Suh, Kang-Deog, et al. "A 3.3 V 32 Mb NAND flash memory with incremental step pulse programming scheme." *IEEE Journal of Solid-State Circuits* 30.11 (1995): 1149-1156.

- [15] Miccoli, Carmine, et al. "Investigation of the programming accuracy of a double-verify ISPP algorithm for nanoscale NAND Flash memories." 2011 International Reliability Physics Symposium. IEEE, 2011.

- [16] Lue, Hang-Ting, et al. "Understanding STI edge fringing field effect on the scaling of charge-trapping (CT) NAND Flash and modeling of incremental step pulse programming (ISPP)." 2009 IEEE International Electron Devices Meeting (IEDM). IEEE, 2009.

- [17] Zheng, Hao-Xuan, et al. "Reducing forming voltage by applying bipolar incremental step pulse programming in a 1T1R structure resistance random access memory." *IEEE Electron Device Letters* 39.6

(2018): 815-818.

- [18] LENZLINGER, M.; SNOW, E. H. Fowler-Nordheim tunneling into thermally grown SiO2. *Journal of Applied physics*, 1969, 40.1: 278-283.

- [19] CHIOU, Y. L.; GAMBINO, J. P.; MOHAMMAD, M. Determination of the Fowler–Nordheim tunneling parameters from the Fowler–Nordheim plot. *Solid-State Electronics*, 2001, 45.10: 1787-1791.

- [20] COMPAGNONI, Christian Monzio, et al. Physical modeling for programming of TANOS memories in the Fowler–Nordheim regime. IEEE transactions on electron devices, 2009, 56.9: 2008-2015.

#### 초 록

본 논문에서는 3D NAND Flash memory에서 비트 라인 (BL) 스트링 레벨에서 3D 전하 트랩 NAND 플래시의 프로그램 과도 시뮬레이션을위한 컴팩트 모델을 소개했다.

첫째, 트랩 된 전하 매개 변수와 수정 된 1D 포아송 방정식에서 얻은 솔루션을 단위 셀 모델에 적용함으로서 모델이 기존 모델에 비해더 나은 정확도를 보여주는 것을 제시하였다. Technology Computer-Aided Design (TCAD) 시뮬레이션 결과, 실제 프로그램 동작에 의하여 트랩된 전자는 nitride 층에서도 tunneling oxide에 가까이 분포하였다. 따라서이러한 전자의 분포를 모델에 반영하기 위해 기존 연구와 달리 nitride 내부를 2개의 구간으로 나누었다. 한쪽 구간에만 trap이 존재한다고 가정하였고 이를 기반으로 포아송 방정식을 수정하였다.

둘째, nitride의 경계를 나타내는 파라미터를 새로 설정하였고, 이를 통해 TCAD 시뮬레이션 결과에 효과적으로 피팅 하였다. 그 결과, 모든 전압에 대하여 프로그램 동작에 대한 threshold voltage 변화가 정확하게 예측되었다.

셋째, 시간에 따라 변화되는 전자의 분포가 고려될 수 있다는 것이 제시되었다. 높은 전계에서는 시간에 따른 전자 분포의 변화가 크기 때문에 높은 전압일수록 전자 분포의 변화를 더 정확하게 반영할 수 있어야한다. 일정 시간 구간마다 threshold voltage 변화량에 대하여 피팅한 결과, 전자의 분포가 넓어지는 것을 모델이 반영할 수 있는 것이 제시되었다.

주요어 : 3D NAND Flash memory, 프로그램 동작, 전자의 분포, 포아송 방정식

학 번:2019-23620