공학박사 학위논문

# Capacitive Isolated Class E Converter Design Considering Touch Current and Electromagnetic Interference

접촉 전류와 전자파 방해를 고려한 정전식 절연형 클래스 E 컨버터 설계

2021년 8월

서울대학교 대학원

전기정보공학부

민 건 홍

Capacitive Isolated Class E Converter Design Considering Touch Current and Electromagnetic Interference

지도 교수 하정 익

이 논문을 공학박사 학위논문으로 제출함 2021 년 7월

> 서울대학교 대학원 전기정보공학 민 건 홍

민건홍의 공학박사 학위논문을 인준함 2021년 7월

| 위 원 | 년 장 _ | 설 승 기 |

|-----|-------|-------|

| 부위  | 원장 _  | 하 정 익 |

| 위   | 원 _   | 오 정 석 |

| 위   | 원 _   | 이 동 영 |

| 위   | 원     | 최 성 진 |

# Abstract

This dissertation studies a method to reduce the common-mode current in capacitive isolated class E converter. Removing a transformer from a galvanically isolated converter has been researched a lot to design a high power density DC/DC converter. One way to remove the transformer is to use a capacitor instead of a transformer for galvanic isolation. However, using a capacitor increases the common-mode current, which can cause high touch current and conduction EMI (Electromagnetic Interference). Due to a user's safety and compatibility with other electronic devices, all electronic devices' touch current and EMI are strictly regulated. Therefore, methods to reduce a commonmode current in a capacitive isolated DC/DC converter are studied in this dissertation.

In this dissertation, common-mode current in the grid frequency band and switching frequency band are analyzed separately. A common-mode current in the grid frequency band is related to touch current, while the switching frequency component of a common-mode current is responsible for conduction EMI. Since grid frequency is relatively lowfrequency, the impedance of a capacitor is high at this frequency range. This dissertation, thus, calculates a maximum capacitance allowed to meet the touch current regulation. For DC/DC converter topology, a class E converter is chosen since this topology is suitable for operating in high frequency and reduce the capacitor to block touch current. A balanced class E converter is proposed for lowering the common-mode current in the switching frequency band. The converter's balanced structure can eliminate the common-mode voltage and thus decrease the common-mode current. A common-mode current in class E DC/DC converter with LC series network and Tnetwork is analyzed in this dissertation. T-network is used to set the voltage gain between input and output voltage of the DC/DC converter, and the design method for this network is also

i

written in this dissertation. The common-mode current in a conventional and a balanced class E converter is compared. The effect of parameter error on a common-mode current in a balanced class E converter is also analyzed. Lastly, a self-powered gate driver circuit for providing power to gate drive is presented. Since a high side switch needs to be placed to operate a balanced class E converter, a circuit providing stable power to a gate driver is necessary. Therefore, a self-powered gate across the switch is proposed.

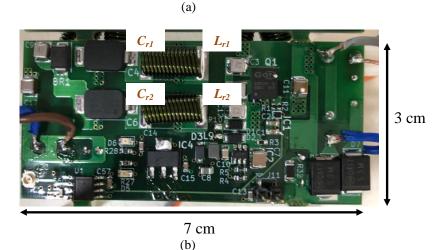

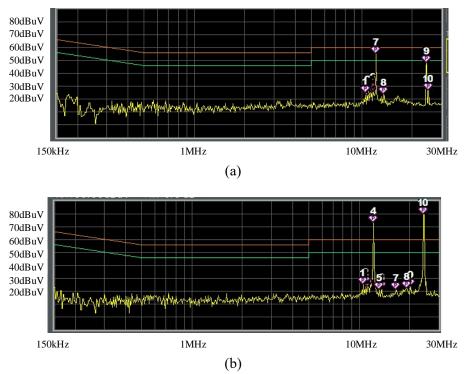

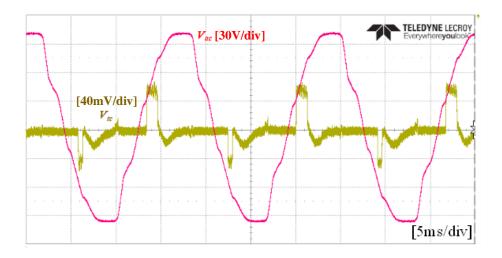

Conduction EMI and touch current are measured using 40W 7cm by 3cm converter prototype. From the experiment, the proposed balanced class E converter has lower EMI noise compare to the conventional class E converter. Also, the measured touch current satisfies the regulation ensuring the safety of a proposed capacitive isolated converter.

**Keywords**: Capacitive Isolation, High-Frequency Converter, Touch Current, Electromagnetic Interference, Common-mode Current **Student No.**: 2016-20896

ii

# Table of Contents

| Abstra | acti                                                                                                                                                                                                                                                  |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.     | Introduction11.1 Research Background11.2 Research Objective111.3 Thesis Composition12                                                                                                                                                                 |

| 2.     | Capacitive Isolated Converter Design142.1 Modeling of Capacitive Isolated Converter142.2 Grid Frequency Component Analysis162.3 High-Frequency Converter Topology262.3.1 Class E Converter Operation302.3.2 Inverter and Rectifier Voltage Analysis35 |

| 3.     | Class E Converter with LC Series Network                                                                                                                                                                                                              |

| 4.     | Class E Converter with T-model Network834.1 Two-port Network Design834.2 Common Mode Current in Class E Converter1004.3 Common Mode Current in Balanced Class E Converter1064.4 Experimental Result117                                                |

| 5.     | Self-powered Gate Driver Circuit                                                                                                                                                                                                                      |

| 6.     | Conclusion and Future Research                                                                                                                                                                                                                        |

| Α.     | ndix                                                                                                                                                                                                                                                  |

| Refer  | ence146                                                                                                                                                                                                                                               |

| 국문 콜   | 초록155                                                                                                                                                                                                                                                 |

# List of Tables

| [Table 1-1]IEC 60950 Standard                           |

|---------------------------------------------------------|

| [Table 3-1]Class E converter with LC series network     |

| parameters used in simulation and experiments           |

| [Table $3-2$ ] Experimental result when Zb = high       |

| impedance                                               |

| [Table $3-3$ ] Experimental result when $Zb = 0$ $80$   |

| [Table 3-4] Comparison between estimation, simulation,  |

| and experimental result when $Zb = 0$                   |

| [Table 4–1] Class E converter with two-port network     |

| parameters used in simulation and experiments107        |

| [Table $4-2$ ] Experimental result when Zb = High       |

| impedance118                                            |

| [Table 4–3] Experimental result when $Zb = 0 \dots 119$ |

| [Table 4-4] Comparison between estimation, simulation,  |

| and experimental result when $Zb = 0$ 119               |

| [Table A-1] IEC 60601 Leakage current standard for      |

| medical equipment140                                    |

| [Table A-2] Withstand voltage test according to IEC     |

| 60950-1143                                              |

| [Table A-3] Capacitor rating according to IEC 60384144  |

# List of Figures

| [Figure 1–7] Current path of (a) Differential mode current     |

|----------------------------------------------------------------|

| (b) Common mode current                                        |

| [Figure 1–8] Circuit of a typical EMI filter                   |

| [Figure 2-1] Block diagram of capacitive isolated DC/DC        |

| converter14                                                    |

| [Figure 2-2] Grid frequency modeling of the capacitive         |

| isolated converter (a) equivalent circuit depending on the     |

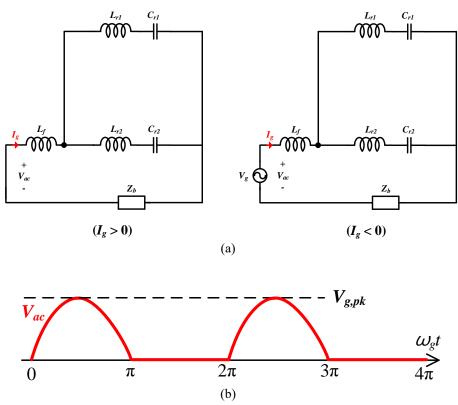

| direction of $I_g$ (b) voltage waveform of $V_{ac}$            |

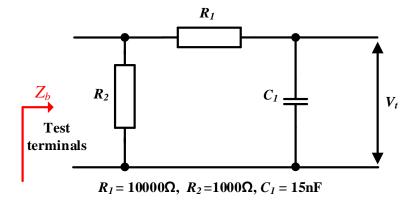

| [Figure 2–3] Body impedance model circuit diagram in IEC       |

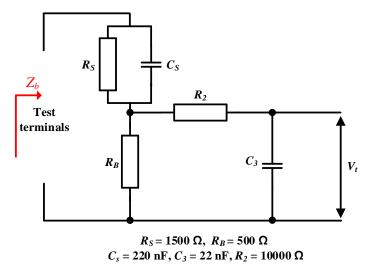

| 6099017                                                        |

| [Figure 2–4] Bode plot of body impedance model18               |

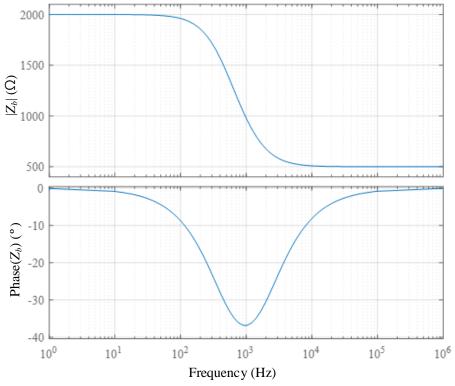

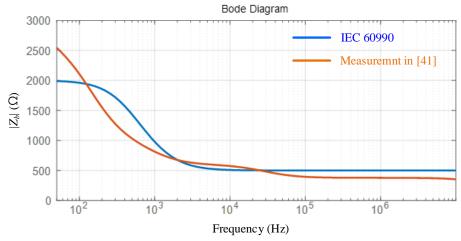

| [Figure 2–5] Impedance magnitude comparing the body            |

| impedance model in IEC 60990 and measurement in                |

| [42]19                                                         |

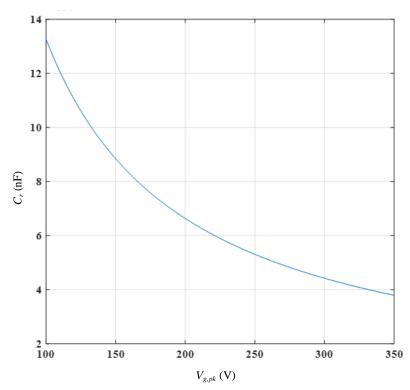

| [Figure 2–6] Maximum capacitance allowed for meeting           |

| touch current regulation20                                     |

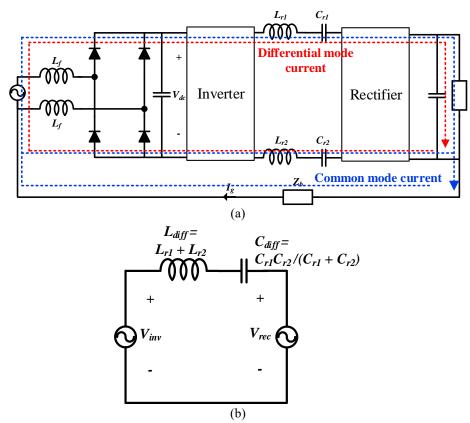

| [Figure 2–7] Capacitive isolated converter (a) Direction of    |

| differential and common-mode currents (b) Differential         |

| mode equivalent circuit22                                      |

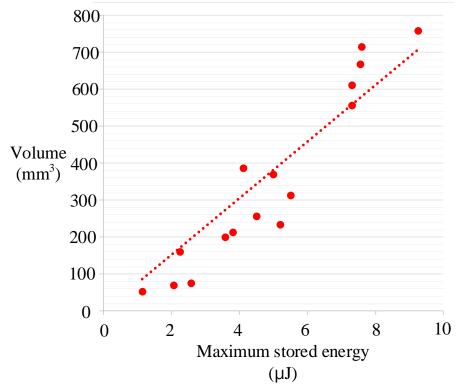

| [Figure 2–8] Volume of a commercial air-core inductor          |

| depending on the maximum inductor stored energy                |

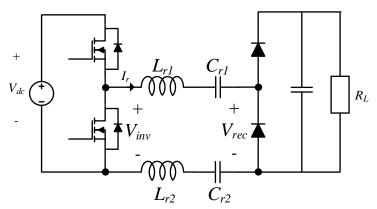

| [Figure 2–9] Capacitive Isolated series resonant               |

| converter                                                      |

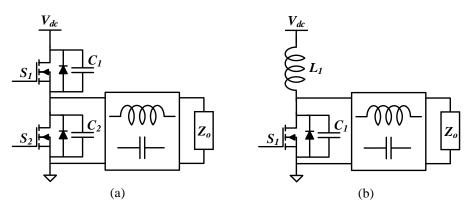

| [Figure $2-10$ ] High frequency inverter topology (a) bridge   |

| type (b) single-ended type                                     |

| [Figure 2–11] Basic structure of class E DC/DC                 |

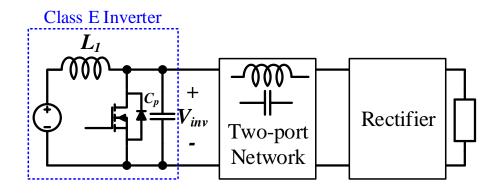

| converter                                                      |

| [Figure $2-12$ ] High frequency rectifier topology (a) class   |

| D (b) class E                                                  |

| [Figure 2–13] Operation of a class E inverter (a) switch $S_1$ |

| on (b) switch $S_1$ off                                        |

| [Figure $2-14$ ] Voltage and current waveforms of a class E    |

| inverter                                                       |

| [Figure 2–15] Class E inverter voltage and current             |

| waveforms when (a) $dv/dt < 0$ (b) $dv/dt = 0$                 |

| [Figure 2–16] The operation of class E rectifier (a) Mode      |

| I diode D1 turn on (b) Mode II diode D1 turn off               |

| [Figure $2-17$ ] Voltage and current waveforms of class E      |

| rectifier                                                      |

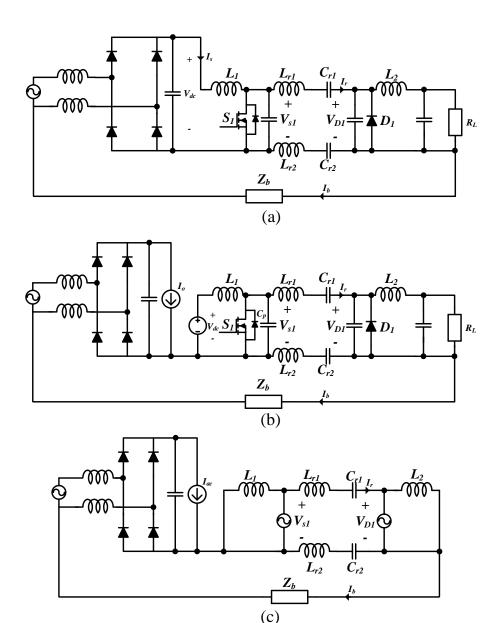

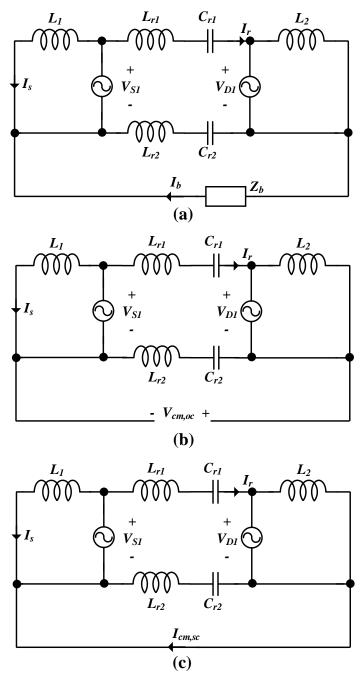

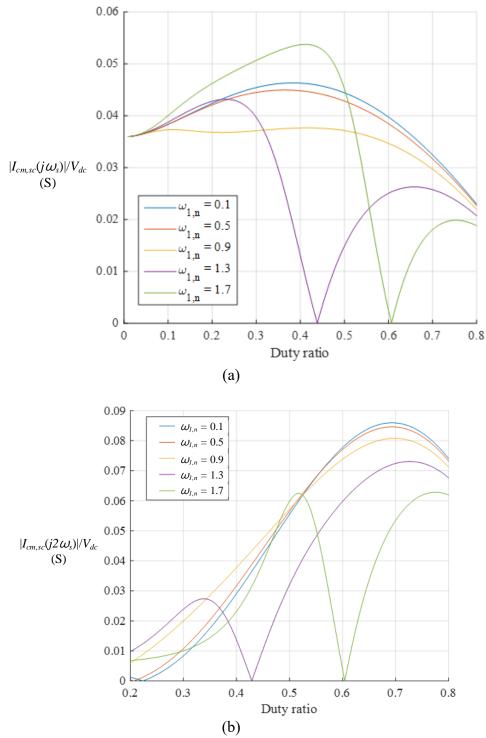

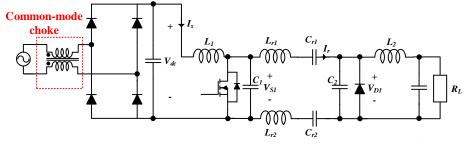

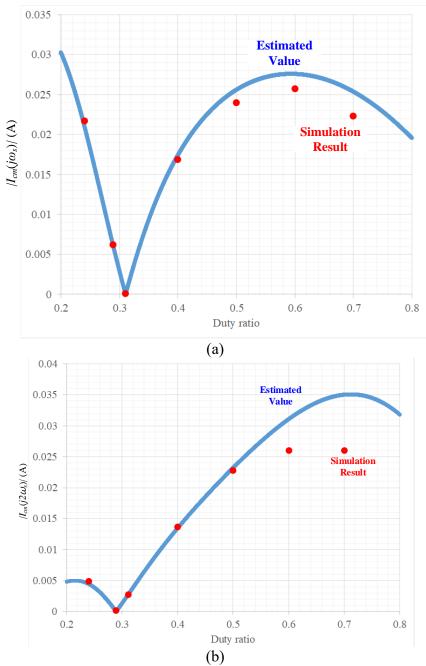

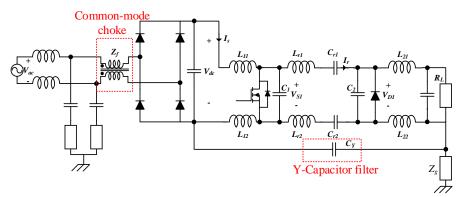

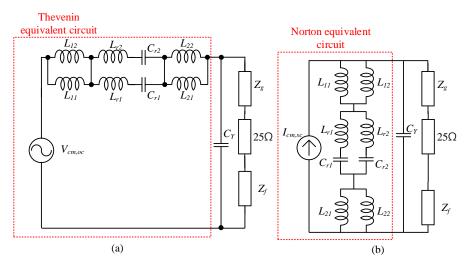

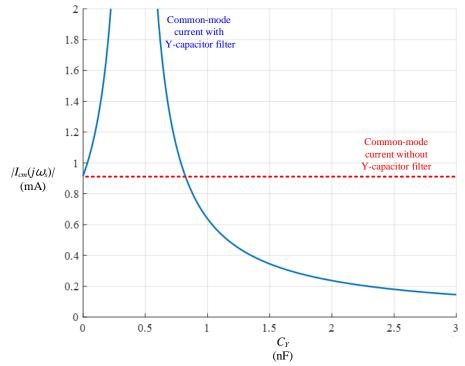

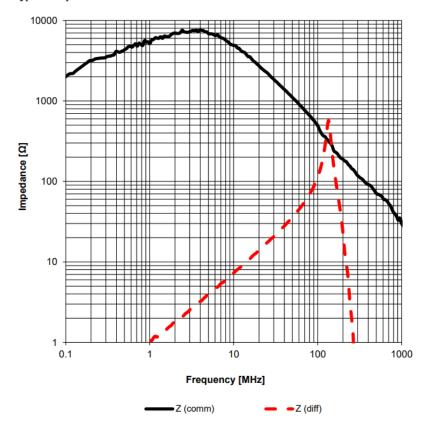

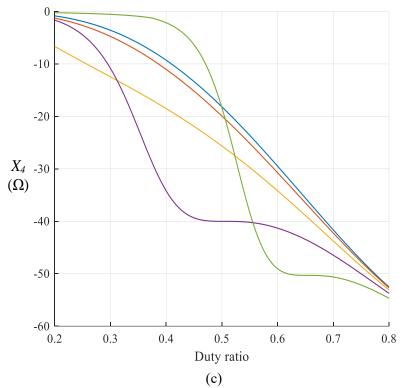

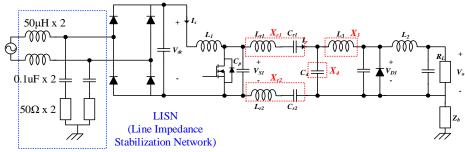

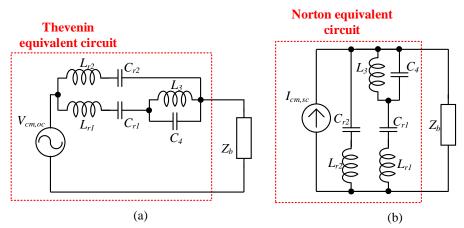

[Figure 2–18] Capacitive Isolated class E DC/DC [Figure 2–19] Class E inverter output voltage magnitude (a) fundamental term (b) 2nd harmonic term (c) 3rd [Figure 2-20] 2nd, 3rd, and 4th harmonic terms of a class E inverter output voltage normalized by fundamental [Figure 2–21] Maximum voltage across switch S1 during [Figure 2-22] Phase of the inverter output voltage (a) [Figure 2–23] Magnitude of rectifier voltage (a) [Figure 2-24] Phase of rectifier voltage (a) fundamental [Figure 3–1] Modeling procedure of class E capacitive isolated converter (a) capacitive isolated converter with LC series network (b) dividing AC/DC rectifier part and DC/DC converter part (c) active components modeling for common [Figure 3–2] Calculating common–mode Thevenin equivalent circuit (a) common-mode modeling (b) open circuit voltage calculation (c) short circuit current [Figure 3-3] Common mode equivalent circuit (a) Thevenin equivalent circuit (b) Norton equivalent circuit 52 [Figure 3–4] Transconductance of common–mode current [Figure 3–5] Common-mode choke placed between AC [Figure 3–6] Comparison between estimated common– mode current and simulated value (a) fundamental (b) 2nd [Figure 3–7] Comparison between estimated common– mode current and simulated value with small Cr (a) [Figure 3-8] Circuit diagram of balanced class E

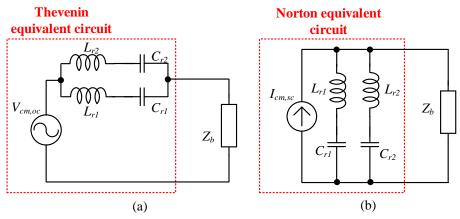

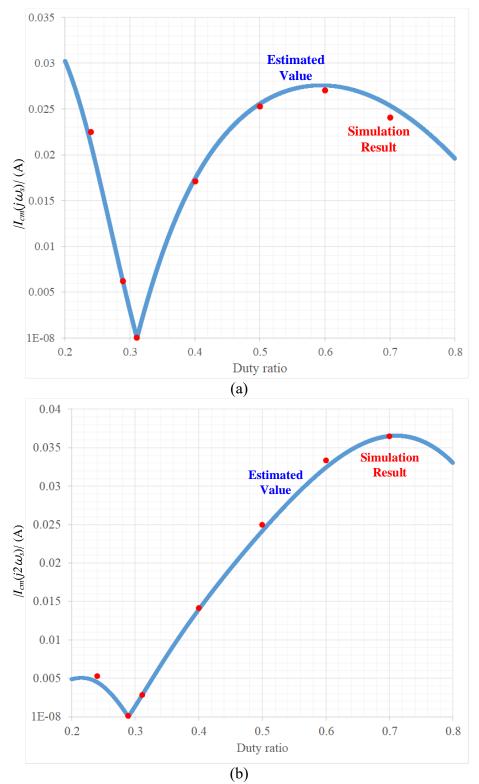

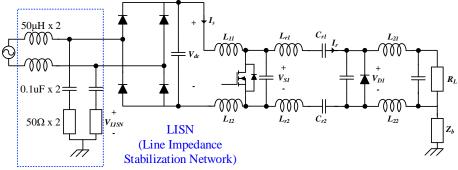

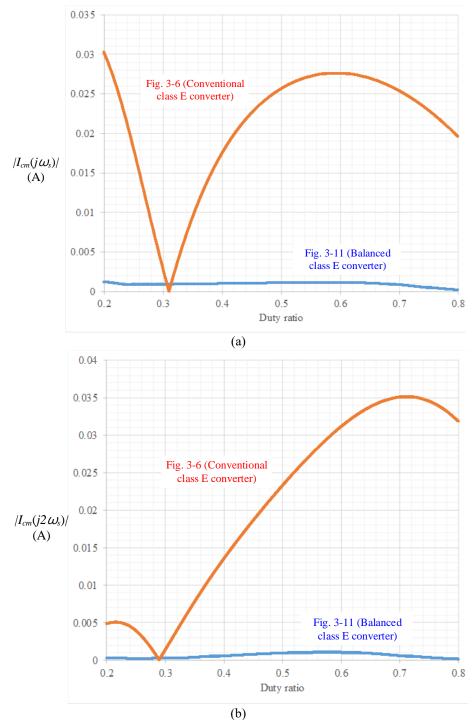

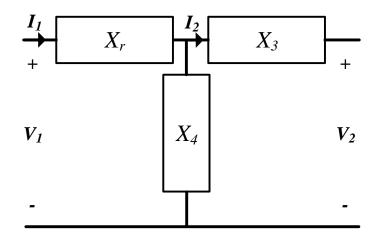

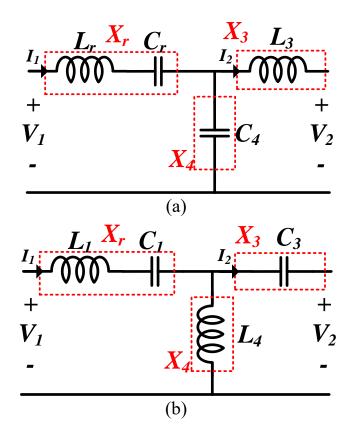

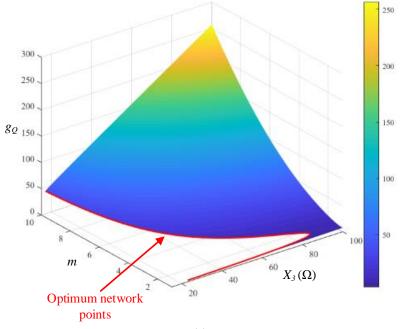

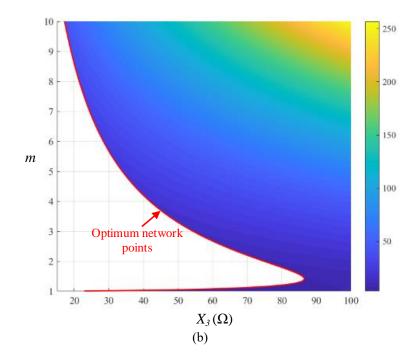

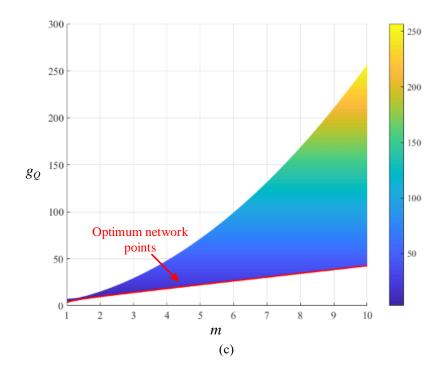

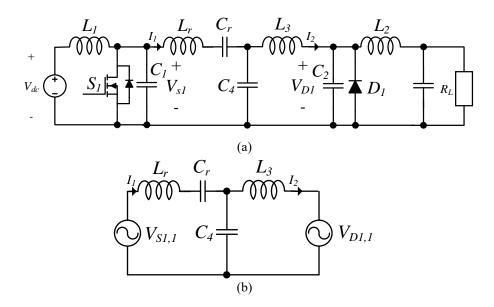

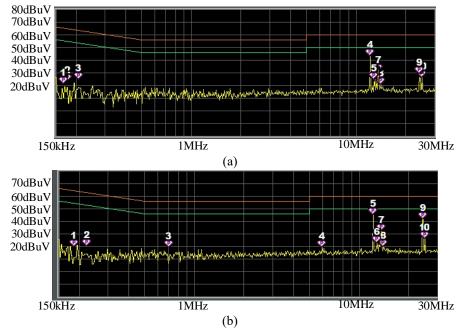

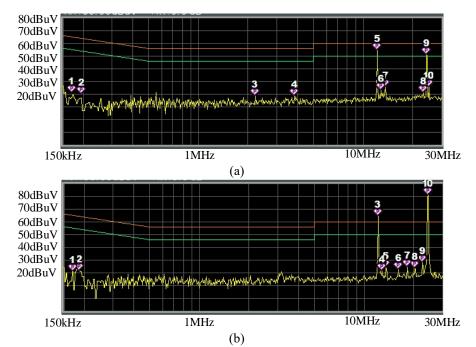

[Figure 3–9] Common-mode equivalent circuit (a) Thevenin equivalent circuit (b) Norton equivalent circuit 60 [Figure 3–10] Histogram of root mean square value of [Figure 3–11] Estimation and simulated value of a maximum common-mode mode current with parameter tolerance of  $\pm 2\%$  (a) fundamental (b) 2nd harmonic ....... 69 [Figure 3–12] Comparison of an estimated common–mode current in a conventional class E converter and a balanced class E converter (a) fundamental (b) 2nd harmonic ...... 71 [Figure 3–13] Balanced class E converter with common– mode filter. Y-capacitor filter and common-mode choke are placed......72 [Figure 3–14] Common-mode equivalent circuit with common mode filter (a) Thevenin equivalent circuit (b) [Figure 3–15] Estimated common-mode current with different Y-capacitor ......74 [Figure 3-16] Impedance of common mode filter WE-SL5 [Figure 3–17] Experimental prototype (a) front side (b) back side.....76 [Figure 3-18] Balanced class E converter with commonmode filter. Y-capacitor filter and common-mode choke [Figure 3-19] Conduction EMI when Zb is high impedance (a) balanced class E converter (b) conventional class E [Figure 3-20] Conduction EMI when load is shorted to Earth (a) balanced class E converter (b) conventional class [Figure 4-3] Size index gQ for different conversion gain m and X3 branch reactance (a) x-axis is set to X3, y-axis is set to m and z-axis is set to gQ (b) plot seen from z-axis [Figure 4-4] (a) A class E converter with two-port

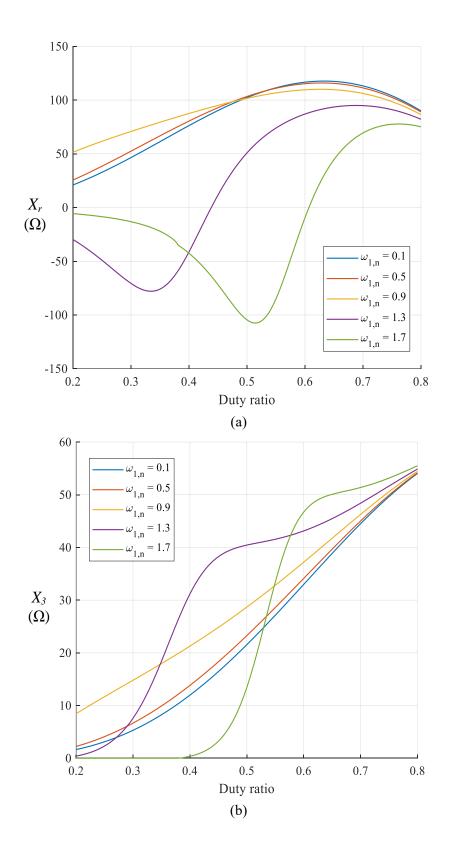

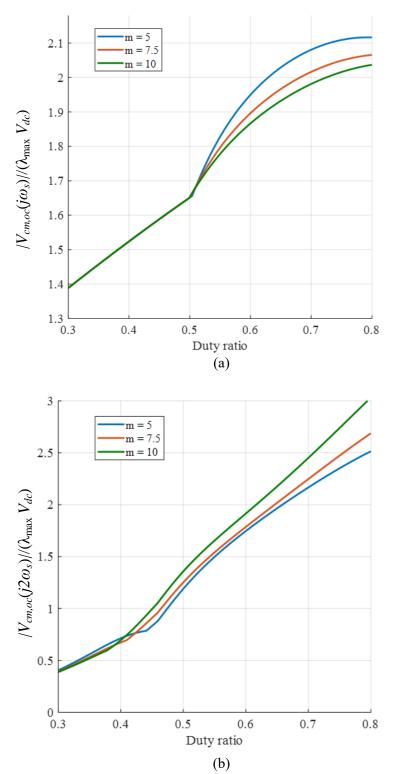

| network (b) the fundamental term modeling of (a)                                                                 |

|------------------------------------------------------------------------------------------------------------------|

| network elements placed in each branch (a) X <sub>r</sub> (b) X <sub>3</sub> (c)<br>X <sub>4</sub>               |

| [Figure 4–7] Capacitive Isolated Class E Converter with<br>two-port network                                      |

| [Figure $4-8$ ] Common mode equivalent circuit (a)                                                               |

| Thevenin equivalent circuit (b) Norton equivalent circuit 101                                                    |

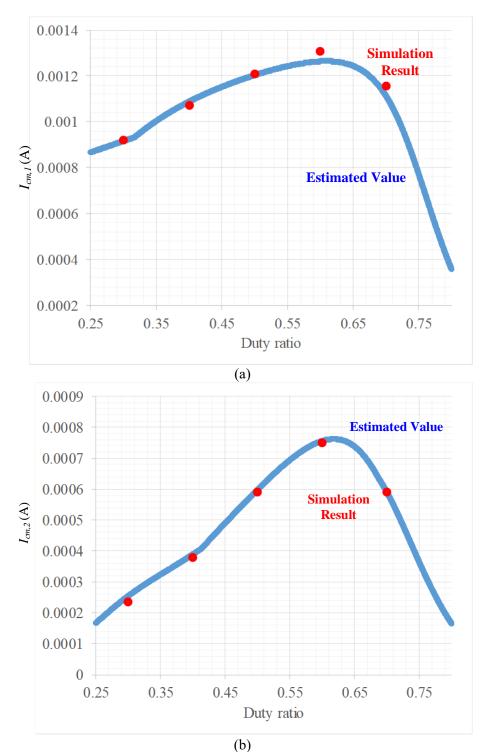

| [Figure 4–9] Common-mode short circuit current in class<br>E converter with two-port network (a) fundamental (b) |

| 2nd harmonic                                                                                                     |

| [Figure $4-10$ ] Common-mode current in class E converter with two-port network (a) fundamental (b) 2nd          |

| harmonic105                                                                                                      |

| [Figure 4–11] Balanced class E converter with two-port                                                           |

| network                                                                                                          |

| [Figure 4–12] Common-mode equivalent circuit of a                                                                |

| balanced class E converter with two-port network. Xth is                                                         |

| calculated in equation $(4-39)$ (a) Thevenin equivalent                                                          |

| circuit (b) Norton equivalent circuit                                                                            |

| [Figure 4-13] Histogram of common-mode current in a balanced class E converter with two-port network when        |

| parameter tolerance is considered                                                                                |

| [Figure 4–14] Maximum common–mode open–circuit                                                                   |

| voltage in a balanced class E converter with two-port                                                            |

| network (a) fundamental (b) 2nd harmonic                                                                         |

| [Figure 4–15] Maximum common–mode current in a                                                                   |

| balanced class E converter with two-port network (a)                                                             |

| fundamental (b) 2nd harmonic114                                                                                  |

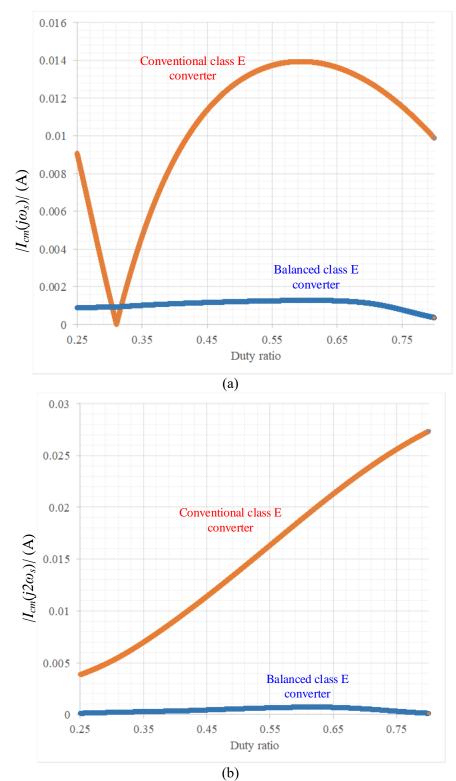

| [Figure 4–16] Comparison of an estimated common–mode                                                             |

| current in a conventional class E converter and a balanced                                                       |

| class E converter (a) fundamental (b) 2nd harmonic 116                                                           |

| [Figure 4–17] Conduction EMI measurement of a balanced                                                           |

| [Figure 4–18] Conduction EMI measurement of a balanced           |

|------------------------------------------------------------------|

| class E converter when $Zb = 0$ (a) with Y-capacitor (b)         |

| without Y-capacitor                                              |

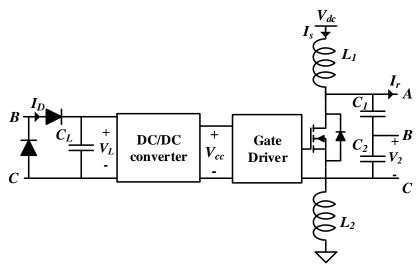

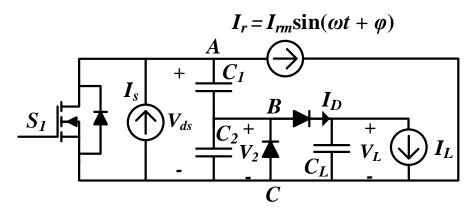

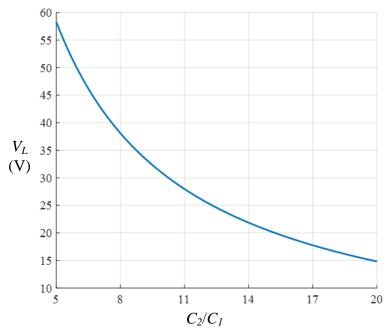

| [Figure 5–1] Self-powered gate driver circuit                    |

| topology                                                         |

| [Figure 5–2] Simplified model of self–powered gate driver        |

| circuit converter                                                |

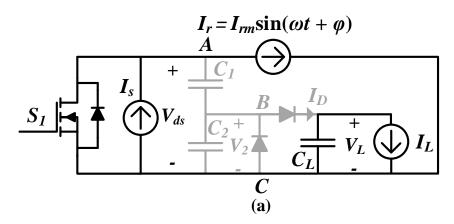

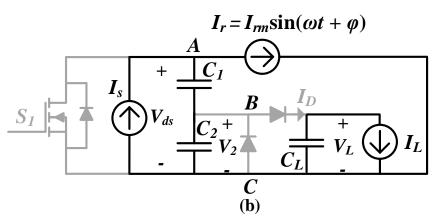

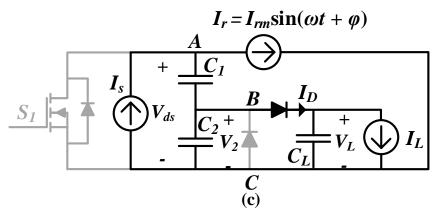

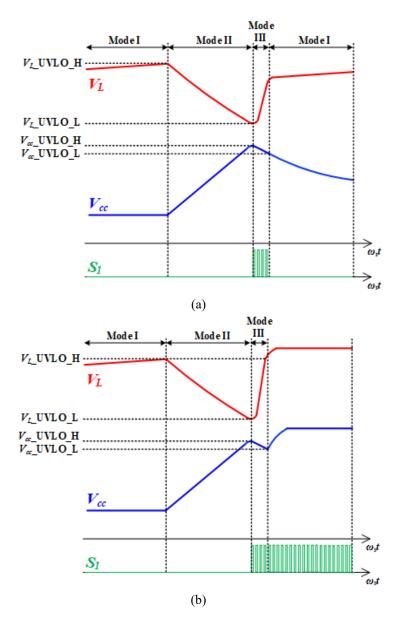

| [Figure 5-3] Operation mode of self-powered gate driver          |

| circuit (a) Mode I when the switch is turned on (b) Mode II      |

| switch is turned on, but diode is turned off (c) Mode III        |

| diode is turned on                                               |

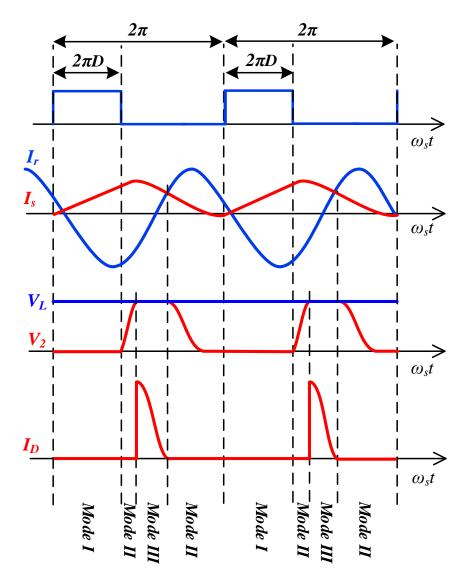

| [Figure 5-4] Voltage and current waveforms of self-              |

| powered gate driver circuit                                      |

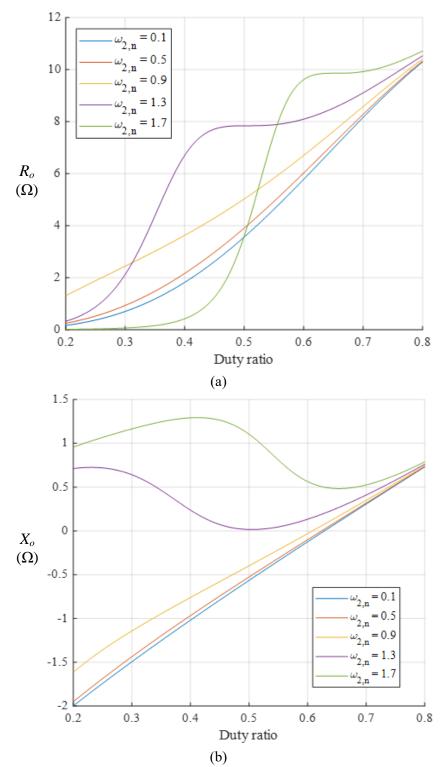

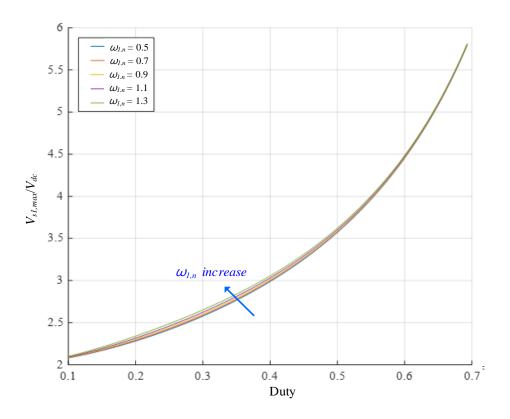

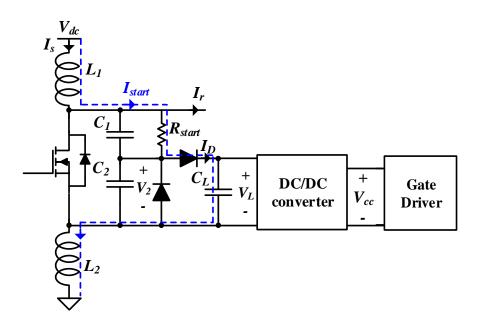

| [Figure 5–5] Maximum switch voltage versus duty                  |

| ratio                                                            |

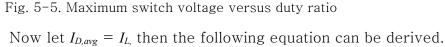

| [Figure 5–6] DC/DC converter input voltage versus duty           |

| ratio when $Po = 1W$                                             |

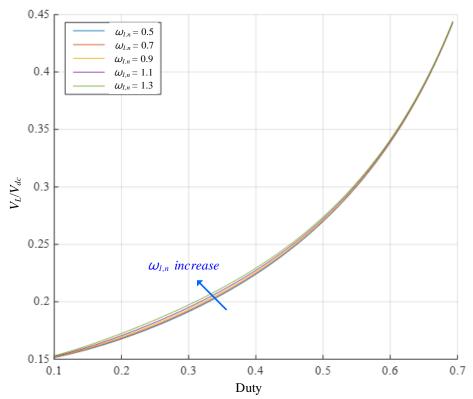

| [Figure 5–7] DC/DC converter input voltage versus duty           |

| ratio when $w \ln = 1.3$                                         |

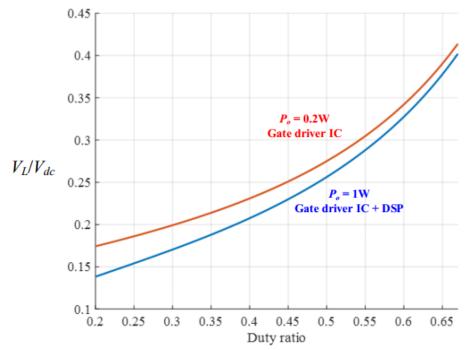

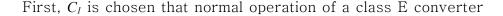

| [Figure 5–8] Minimum DC–link input voltage required to           |

| operate self-powering gate driver circuit when w1n =             |

| 1.3                                                              |

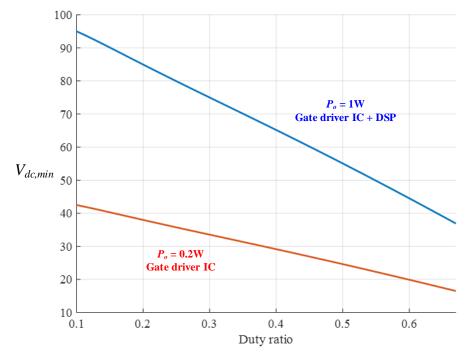

| [Figure 5–9] DC/DC converter input voltage V <sub>L</sub> versus |

| $C_2/C_1$                                                        |

| [Figure 5-10] Start-up resistor placed in the proposed           |

| self-powered gate driving circuit                                |

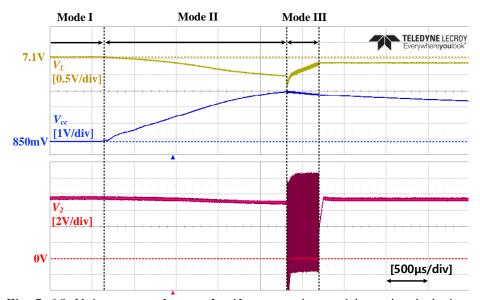

| [Figure 5-11] The voltage waveforms during start-up              |

| operation of the self-powered gate driver (a) start-up           |

| fails (b) start-up successful                                    |

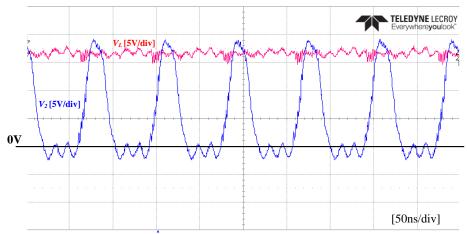

| [Figure 5–12] Voltage waveforms of self-powered gate             |

| driver circuit during steady-state operation                     |

| [Figure 5-13] Voltage waveforms of self-powered gate             |

| driver circuit during start-up operation                         |

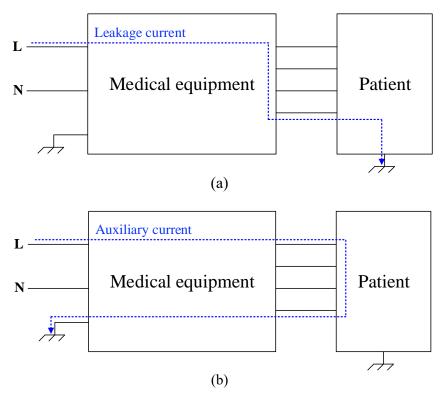

| [Figure A-1] Leakage current measuring circuit in IEC            |

| 60601                                                            |

| [Figure A-2] Typical current direction of (a) leakage            |

| current (b) auxiliary current between medical equipment          |

| and patient141                                                   |

# **1. Introduction**

## **1.1 Research Background**

Designing a high power density isolated converter is being widely researched with advanced high bandgap devices such as GaN (Gallium Nitride) and SiC (Silicon Carbide) [1] – [4]. GaN devices, in particular, have higher saturated velocity and electron mobility compared to Si (Silicon) and SiC devices allowing highfrequency switching. Therefore, with the help of these devices, the switching frequency of the DC/DC converter can be increased up to a few MHz increasing the power density of the converter.

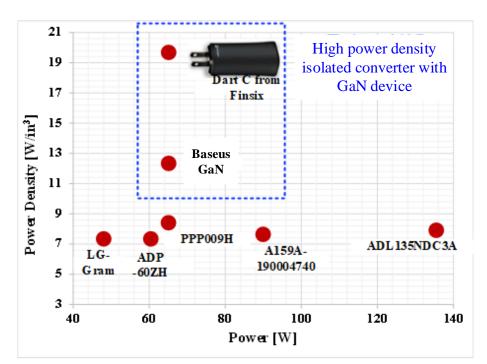

Fig. 1-1. The power density of commercial laptop chargers. Recently, high power density laptop chargers such as Dart C from Finsix [5] is being developed.

Fig. 1–1 shows the power density of commercial laptop chargers. In this figure, the galvanically isolated converter with the highest power density is Dart C from Finsix. It has a power density of 19.5 W/in<sup>3</sup> with a nominal output power of 65W. A laptop charger from Baseus also has a high power density, with a power density of 12.2 W/in<sup>3</sup>. The reason for the high power density for both chargers is the use of a GaN switching device, allowing high switching frequency operation. With such high power density laptop chargers in the market, interest in designing galvanically isolated converters with high power density increases.

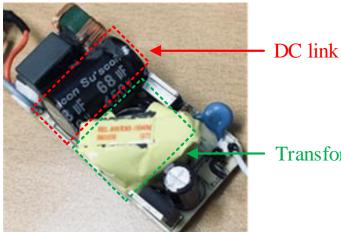

Most DC/DC converter uses magnetic coupling for galvanic isolation. Therefore, DC/DC converter topologies that use transformers such as flyback converter and LLC converter are widely used. For example, Fig. 1-2 shows a tear-down image

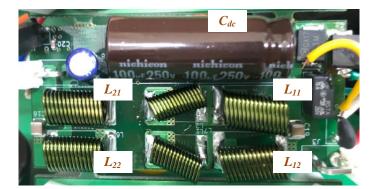

## DC link capacitor

Transformer

Fig. 1-2. Inside of the commercial laptop charger. Passive elements such as DC-link capacitor and transformer take up most spaces.

of a commercial laptop charger. This charger is a flyback converter with 40W nominal output power. In this image, passive elements such as DC-link capacitor and transformer take most of the DC/DC converter space. Therefore, reducing the size of these passive elements, especially a transformer, is key to increasing an isolated converter's power density. This dissertation uses capacitive isolation to remove the transformer from a DC/DC converter to achieve galvanic isolation. Most importantly, regulations for an isolated converter such as touch [6] - [9]and conduction EMI current (Electromagnetic Interference) [10] - [17] are studied to design a safe and compatible DC/DC converter.

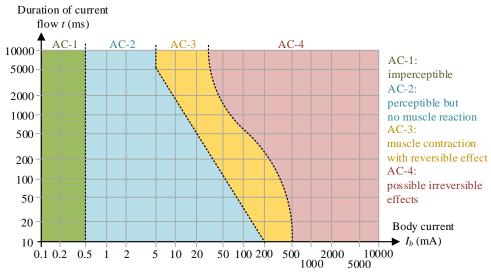

When working with IT equipment, the safety of users is one of the most important factors to be considered when designing electronic devices. Therefore, many restrictions are placed to limit the touch current to ensure the safety of users from electric shock. Fig.1-3 shows the effect of touch current on the human body according to the current flow's current magnitude and duration. It can be seen that the human body can perceive current with a magnitude higher than 0.5 mA. Therefore, standard such as IEC 60950 restricts the magnitude of touch current. Table 1-

Fig.1–3. Effect of touch current to human body.

| Equipment     | Condition               | Leakage current<br>limit (mA <sub>rms</sub> ) |

|---------------|-------------------------|-----------------------------------------------|

| All equipment | No protective<br>ground | 0.25                                          |

| Handheld      | Protective<br>ground is | 0.75                                          |

| Portable      |                         | 3.5                                           |

| Stationary    | present                 | 3.5                                           |

TABLE 1-1. IEC 60950 STANDARD<sup>[6]</sup>

1 shows the maximum leakage current allowed according to the standard IEC60950. It can be seen that the touch current is limited to 0.25 mA for the equipment without any protective ground connected to accessible parts. In medical equipment, stricter regulation is in place to protect patients from an electric shock. The standard for medical electrical equipment is IEC60601-1 [8]. In this standard, patient leakage current is restricted to 100  $\mu$ A in AC and 10  $\mu$ A in DC. Therefore, when

building medical equipment, limiting a leakage current is a highly critical issue. A more detailed explanation of IEC60601 is written in Appendix 1.

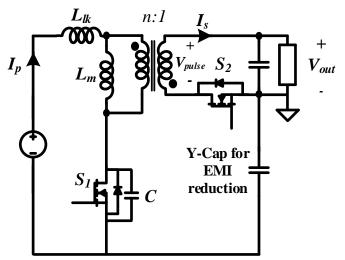

In conventional devices using magnetic coupling, the primary and secondary sides are electrically disconnected. Therefore, ideally, the touch current should be zero when the transformer is in place. However, the capacitor is often added between primary and secondary sides in many cases, as shown in Fig. 1–4, increasing the touch current. This capacitor is added to create a high-frequency current path and reduce the converter's EMI (Electromagnetic Interference). A Y-rated capacitor with more than 300 V rated voltage, and 5 kV instantaneous voltage is used for the user's safety since the failure of this capacitor may lead to an electric shock.

Fig. 1-4. Flyback converter with a Y-capacitor. The capacitor is used for reducing EMI of the converter.

(a)

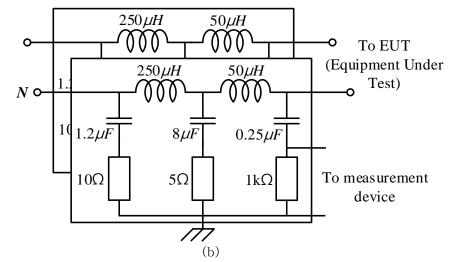

Fig. 1-5. Line Impedance Stabilization Network used for measuring conduction EMI (a) photo of LISN (b) circuit diagram.

EMI regulations are also crucial when designing electronic devices connected to the AC grid. Every electronic device can radiate electromagnetic power that can impede other electronic devices from operating normally. Therefore, regulations such as CISPR 22 restricts EMI caused by an electronic device. There are two different types of EMI to be considered. One is conduction EMI caused by high-frequency current traveling along the power line. This EMI is measured using LISN (Line Impedance Stabilization Network) shown in Fig 1-5, and frequency components between 150 kHz and 30 MHz are measured. This conduction EMI should not exceed the value shown in Fig. 1-6, where Class A is for a non-residential application, and Class B is for a residential application. Here both QP (quasi-peak) and AVG (average) values of EMI noise are restricted. Another type of EMI is radiated EMI measured using a radiation measuring probe. In most applications, radiated EMI is measured above 30 MHz. However, in some applications such as induction cooking equipment or wireless power transfer for an electric vehicle, where high radio-frequency energy is radiated, radiation EMI is also measured in frequency between 9 kHz and 30 MHz.

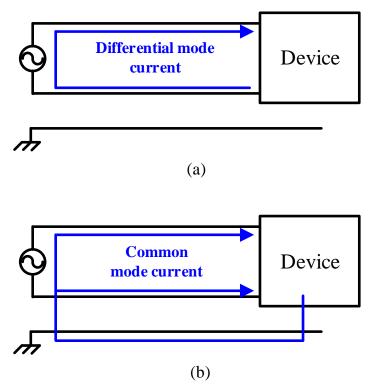

In most cases, the EMI filter is often designed using passive components to meet the EMI regulation. Since different EMI filter types are used for different EMI noises, the types and magnitude of EMI sources must be thoroughly analyzed. There are two EMI sources, a common-mode EMI and differential mode EMI, as shown in Fig. 1–7. It can be seen that differential-mode EMI is caused by a high-frequency current that flows on the same path as the supply current, while the high-frequency current across the Earth causes common-mode EMI. A typical EMI filter used in electronic devices is shown in Fig. 1–8. Each component has

Fig. 1–7. Current path of (a) Differential-mode current (b) Commonmode current.

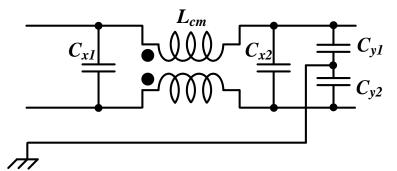

Fig. 1-8. Circuit of a typical EMI filter.

a different purpose for reducing overall EMI noises. Capacitor  $C_{xl}$ and  $C_{x2}$  are placed between two power supply lines and implemented to reduce the differential-mode EMI noise by creating a differential noise path. Typically, a capacitor with type X safety classification is placed between line-to-line. In order to mitigate common-mode EMI noise, common-mode choke L<sub>cm</sub> is placed at a power supply line, and capacitors  $C_{yl}$  and  $C_{y2}$  are placed between the power supply line and Earth. A commonmode choke increases the impedance at the common-mode side, reducing the common-mode current. Capacitors across the power line and Earth create an additional common-mode noise path reducing the common-mode current flowing to the grid. Typically, a capacitor with type Y safety classification is placed between line-to-earth. For a two-wire system, a different EMI filter should be used since earth reference is not available. Therefore, instead of connecting a capacitor to Earth, Y-

capacitor is connected between DC/DC converter grounds, as shown in Fig. 1-4.

However, the addition of this Y-capacitor harms touch current. High-frequency current flows through the Y-capacitor instead of traveling to the power line, thereby reducing the conduction EMI of the electronic device. However, the addition of a Y-capacitor creates a touch current path and therefore increases the touch current. Thus, careful Y-capacitor selection is needed to reduce the EMI noises while ensuring leakage current is beyond the limit [11], [12]. Typically, few nano-Farad capacitors are used. Although this conventional method allows mitigation of both touch current and EMI noise, it also has some disadvantages. The most critical issue is the bulky size of magnetic components, especially in high switching frequency. Since high magnetic coupling between the primary and secondary sides is essential to transfer power efficiently, a large magnetic component is used, becoming a bottleneck for designing a high power density converter. Increasing switching frequency can reduce the size of the transformer; however, it has a limit due to a lack of a high-frequency magnetic component. In fact, at a frequency higher than 10 MHz, increasing the switching frequency increases the inductor's size since a larger size is

10

needed to dissipate the heat caused by core loss [21]. Air core inductor can be used instead, but it isn't easy to create high magnetic coupling with air core. Therefore, other means of isolation methods should be researched for high frequency and high-power density converter design.

## **1.2 Research Objective**

In this research, isolated converter design using capacitive coupling is used to design high frequency and high-power density converters. A capacitor has an advantage in volume compared to a transformer, especially at the high switching frequency. In fact, many commercially available capacitors have high energy density compared to commercial air-core inductors [23].

A capacitive isolated converter is researched to replace the transformer in an isolated converter [24]-[28]. Most of the research, however, implements capacitive isolation where leakage current standard is not considered. Many researches focus on using capacitive isolation for stacking and building input parallel output series (IPOS) converter [24] - [26]. In these applications, a capacitor as large as a few  $\mu$ F is used, which is beneficial for transferring high power efficiently but cannot be

11

used in an application where leakage current standard should be met. Some research has also considered the safety and touch current limitation of capacitive isolated converter [27], [28]. In these researches, Y-capacitor is used for isolation to meet isolation voltage standards. However, the high-frequency common-mode current responsible for conduction EMI noise is not seriously considered in previous researches. Instead, a simple common-mode filter is added to remove common-mode noise. Therefore, this paper analyzes sources of common-mode current and proposes the common-mode current mitigation method in the capacitive isolated converter to meet the touch current and conduction EMI regulation.

#### **1.3 Thesis Composition**

In this paper, common-mode current in the capacitive isolated converter is studied. In section 2, capacitive isolated converter design to regulate touch current is studied. Maximum allowed capacitance is defined to restrict a touch current that satisfies safety regulations. Also, the class E inverter and class E rectifier operation are analyzed to calculate the highfrequency common-mode current. In section 3, common-mode current in capacitive isolated class E converter with LC series network is calculated, and balanced class E converter is proposed to reduce common-mode current. In section 4, a capacitive isolated class E converter with a T-model-based network for different input to output voltage gain is analyzed. Similarly, the common-mode current is calculated, and the conduction EMI of a balanced class E converter with a T-model-based network is measured. In section 5, a self-powered gate driver circuit to operate a balanced class E converter is proposed.

#### 2. Capacitive Isolated Converter Design

## 2.1 Modeling of Capacitive Isolated Converter

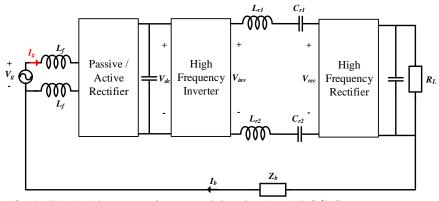

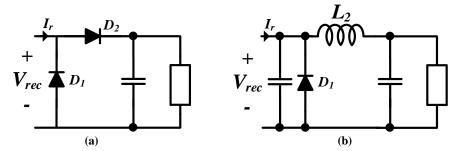

Three sources create a common mode current in the capacitive isolated converter shown in Fig.2-1. One is AC grid  $(V_g)$ , and the other two are high-frequency inverter  $(V_{inv})$  and rectifier  $(V_{rec})$  in DC/DC converter. AC grid voltage  $V_g$  is low frequency (around 50 – 60 Hz) while frequency of  $V_{inv}$  and  $V_{rec}$  depends on switching frequency of DC/DC converter, which can go up to a few MHz in high frequency switching converters. Typically,  $V_g$  creates touch current, and  $V_{inv}$  and  $V_{rec}$  are responsible for conduction EMI noise.

First, capacitor values  $C_{r1}$  and  $C_{r2}$  will be decided by assuring the grid frequency component of the common-mode current to satisfy the touch current standard. Since capacitors  $C_{r1}$  and  $C_{r2}$

Fig. 2-1. Block diagram of a capacitive isolated DC/DC converter

have high impedance at grid frequency, low-frequency touch current can easily be reduced by adjusting the capacitance value. Then switching frequency  $f_{sw}$  is decided that is suitable to transfer power with capacitor  $C_{r1}$  and  $C_{r2}$ . For a high-frequency common-mode current, the impedance of  $C_{r1}$  and  $C_{r2}$  is too low and therefore needs an alternative common mode current reduction method. In this paper, a balanced converter design [35]-[39] is implemented to reduce high-frequency commonmode current.

## 2.2 Grid Frequency Component Analysis

First, the grid frequency component is analyzed. If PFC (Power factor correction) is used as an active rectifier, grid current  $I_g$  is a continuous sinusoidal wave. In this case, Fig. 2–1 can be redrawn to Fig. 2–2(a), where other frequency voltage sources  $V_{inv}$  and  $V_{rec}$  are set to zero to analyze only low-frequency common-mode current. Since  $I_g$  is a sinusoidal wave in phase with grid voltage  $V_g$ ,  $V_{ac}$  is a half-wave sine waveform where the Fourier transform equation is

Fig. 2–2. Grid frequency modeling of the capacitive isolated converter (a) equivalent circuit depending on the direction of  $I_g$  (b) voltage waveform of  $V_{ac}$

$$V_{ac} = V_{g,pk} \left\{ \frac{1}{\pi} + \frac{1}{2} \sin(\omega_g t) - \frac{2}{\pi} \sum_{n=1}^{\infty} \left( \frac{1}{4n^2 - 1} \cos(2n\omega_g t) \right) \right\}, \quad (2-1)$$

where  $V_{g,pk}$  is a peak grid voltage, and  $\omega_g$  is a grid frequency. To calculate the leakage current with the above  $V_{ac}$ , body impedance  $Z_b$  is required.

The circuit used to measure the touch current of IT equipment according to the IEC 60990 standard is shown in Fig. 2-3. One side of the test terminal is connected to the load, and the other is connected to the Earth. From the test terminal side, body impedance  $Z_b$  is around 2000  $\Omega$  at low frequency (<< 480 Hz) and 500  $\Omega$  at high frequency (>>480 Hz), as shown in Fig.

Fig. 2-3. Body impedance model circuit diagram in IEC 60990

Fig. 2-4. Bode plot of body impedance model.

2-4. The validity of this body impedance model has been widely studied to accurately measure the touch current [39]-[41]. In [41], the body impedance model in IEC 60990 is compared with the impedance of the actual body measured (from hand to foot) using an impedance analyzer. The effect of skin condition (dry or wet), gender (male or female), ground insulation (with shoes or bare feet), and contact with a device (with a finger or fully grasp) are compared. According to work in [41], the impedance of the body is lowest when the impedance of a male body is measured with wet skin and barefoot while fully grasping the measuring device. The measured lowest impedance is compared

Fig. 2-5. Impedance magnitude comparison between a body impedance model in IEC 60990 and measurement in [41]

with the body impedance model from IEC 60990 in Fig. 2-5. At 50 Hz, the measured body impedance in [41] is 2530  $\Omega$ , while the body impedance model from IEC 60990 is 2000  $\Omega$  at 50 Hz. At 10 MHz, the measured body impedance is 356  $\Omega$ , while the body impedance model from IEC 60990 is 500  $\Omega$ . Although the model from IEC 60990 has some errors compared to actual measurement, it is helpful due to its simple structure. A more complex body impedance model is proposed in [40] and [41] if a highly accurate touch current should be measured.

In this paper, the impedance model from IEC 60990 will be used to measure the touch current. Using equation (2-1), leakage current can be calculated. Assuming inductor  $L_r$  and  $L_f$ have low impedance at low-frequency touch current,  $I_g$  can be calculated as

$$|I_{g,rms}|^{2} = \frac{V_{g,pk}^{2} \left(\omega_{g} C_{r}\right)^{2}}{8} \left[g(1) + \frac{16}{\pi^{2}} \sum_{n=1}^{\infty} \left\{ \left(\frac{2n}{4n^{2}-1}\right)^{2} g(n) \right\} \right], \qquad (2-2)$$

$$g(n) = \left(1 + n^{2} \omega_{g}^{2} C_{r}^{2} R_{B}^{2} \frac{n^{2} \omega_{g}^{2} C_{s}^{2} R_{s}^{2}}{1 + n^{2} \omega^{2} C^{2} R^{2}}\right)^{-1}.$$

where  $C_r = C_{r1} + C_{r2}$ . Here touch current  $I_{g,rms}$ , should be smaller than 0.25 mA<sub>rms</sub> to meet the standard IEC60950. The condition  $I_{g,rms} < 0.25$  mA<sub>rms</sub> is satisfied when  $C_r$  is small enough to block leakage current. Using parameters from Fig. 2–3 and setting grid frequency to 60 Hz, it can be seen that g(n) < 1 for all n values. Therefore, if  $C_r$  satisfies the below inequality equation, touch current standard is satisfied.

Fig. 2-6. Maximum capacitance allowed for meeting touch current regulation

$$I_{g,rms} < \sqrt{\frac{V_{g,pk}^{2} (\omega_{g} C_{r})^{2}}{8}} \left[ 1 + \frac{16}{\pi^{2}} \sum_{n=1}^{\infty} \left( \frac{2n}{4n^{2} - 1} \right)^{2} \right] < I_{TC,max} .$$

(2-3)

$$C_{r} < \frac{I_{TC,\max}}{\sqrt{\frac{V_{g,pk}^{2}\omega_{g}^{2}}{8} \left[1 + \frac{16}{\pi^{2}}\sum_{n=1}^{\infty} \left(\frac{2n}{4n^{2} - 1}\right)^{2}\right]}} \cong \frac{2I_{TC,\max}}{\omega_{g}V_{g,pk}}$$

(2-4)

where  $I_{TC,max}$  is a maximum touch current of the system. Setting maximum touch current to 0.25 mA, the maximum value of  $C_r$  that satisfies touch current limitation for different AC grid voltage values is shown in Fig. 2–6. When peak AC grid voltage is 350 V,  $C_r$  should be smaller than 3.8 nF to reduce the touch current below 0.25 mA. Next, switching frequency is decided to design a converter that can effectively transfer power with above  $C_{r1}$  and  $C_{r2}$  value. The capacitor is connected in parallel for common-mode while the capacitor is connected in series in differential mode. Thus, a differential mode equivalent circuit can be drawn as Fig. 2-7 (b). Setting  $C_r = 3.3$  nF, the maximum value  $C_{diff}$  can have is  $C_r/4 =$ 825 pF when  $C_{r1} = C_{r2}$ . Assuming the switching frequency is 1 MHz, the inductance  $L_{diff}$  required to set the resonant frequency at 1 MHz is 30  $\mu$ H, which is too large a value for designing a high

Fig. 2-7. Capacitive isolated converter (a) Direction of differentialmode and common-mode currents (b) Differential-mode equivalent circuit

power density DC/DC converter. In this dissertation, switching frequency is decided considering the volume of the resonant inductor. According to [23], the volume of an inductor has a strong relationship with maximum stored energy defined as  $LI_{rms,max}^2$  where L is an inductance and  $I_{rms,max}$  is a root mean square value of the rated current of the inductor defined in the datasheets. Fig. 2–8 shows the volume versus maximum stored energy of commercial air-core inductors. An air-core inductor is used due to the high core loss of magnetic core material when switching frequency is higher than a few megahertz [21]. Using

Fig. 2-8. Volume of a commercial air-core inductor depending on the maximum inductor stored energy

this plot, the size of the air-core inductor can be roughly estimated if an inductance and rated current are given. For comparison, the size of the transformer in a laptop charger is found. For the 40 W laptop charger shown in Fig. 1-2, RM 8 size transformer ferrite core is used. The size of this transformer is roughly 4800 mm<sup>3</sup>. In a laptop charger from FINSIX, RM 6 size transformer ferrite core is used, which is 2000 mm<sup>3</sup> in size. In a capacitive isolated converter topology, multiple inductors and capacitors are used to create a resonant current. Therefore, the size of the inductor should be much smaller than the conventionally used transformer to design a high power density isolated converter. If the size of the inductor is set to 500 mm<sup>3</sup>, then the rough estimation of maximum stored energy is  $6.67 \mu$ J. The current rating depends on the nominal output power of the isolated converter, input voltage, and topology of the converter.

Fig. 2-9. Capacitive isolated series resonant converter.

For instance, assuming a simple 65 W SRC (series resonant converter) with half-bridge inverter and 100 V input voltage ( $V_{dc}$ ) as shown in Fig. 2-9. Then maximum fundamental input voltage across the series network is  $V_{imy,l} = 2V_{dc}/\pi = 64$  V, where  $V_{imy,l}$  is a fundamental component of half-bridge inverter output voltage. Then, the resonant current  $I_r$  can be calculated as  $I_r = 2P_o/V_{imy,l} = 2.04$  A. If this current value is set as a rated current of the inductor, the maximum inductance in the series network considering maximum stored energy can be calculated as  $L_{diff,max} = 3.2 \mu$ H. Using this inductance value, the minimum switching frequency required can be calculated as

$$f_{sw} > \frac{1}{2\pi \sqrt{L_{diff} C_{diff}}} = 3.1 \text{ MHz}.$$

(2-5)

Although the maximum inductance value will differ from the converter's topology and rated output power, this value gives a rough estimation. It can be seen from the equation, converter topology suitable for high-frequency switching with more than a few MHz should be used to design a capacitive isolated converter that can satisfy the leakage current standard.

### **2.3 High-Frequency Converter Topology**

For switching frequency higher than few megahertz, switching losses become a dominant cause of efficiency reduction. Therefore, in high frequency, converter topology with low switching losses is often chosen. A resonant converter is one of the most widely used converters for high-frequency switching. A resonant converter can achieve ZVS (zero voltage switching) using resonant current, reducing the switching losses dramatically. There are two types of resonant converter, a bridge-type resonant converter and a single-ended type resonant converter, as shown in Fig. 2–10. A bridge-type uses a half-bridge or full-bridge inverter combined with a resonant network and rectifier. Using a resonant current, the charge stored in the output capacitor  $C_1$  and  $C_2$  of switches are transferred during a dead-time. When charges are fully

Fig. 2-10. High frequency inverter topology (a) bridge type (b) singleended type

transferred during a converter, a switch can be turned on when the voltage across the switch is zero achieving ZVS. Therefore, this topology is widely used when switching frequency is around a few hundred kHz to a few MHz. However, this bridge-type resonant converter has some limitations for operating at a higher switching frequency. First, the dead time effects required for achieving ZVS are more severe at high frequency [64]. Since the dead time needed for ZVS is fixed if the resonant current magnitude is unchanged, the proportion of time when both switches are off becoming more prominent as the switching period decreases. This dead time effects result in smaller inverter output voltage affecting the output power. To reduce the dead time, a larger resonant current is required; however, this increases conduction losses. Also, a precise gate signal is required for driving multiple switches in the bridge-type inverter. In order to accurately control the dead time to achieve ZVS, exact gate signaling is necessary. This requires a high resolution and low jitter gate signaling device, making it challenging to operate at high frequency.

For these reasons, a single-ended converter shown in Fig. 2-10 (b) is preferred when the switching frequency is higher than a few MHz. Since it only has one switch, the dead time effect

27

Fig. 2–11. Basic structure of class E DC/DC converter does not need to be considered, simplifying the gate drive circuit. Also, since it has an inductor placed between the input voltage source and drain of the switch  $S_I$ , it can absorb any parasitic inductance between an input voltage source and switch, reducing the possible effect of parasitic components. Due to these advantages, a single-ended type converter, class E converter, in particular, is chosen as a topology for this paper.

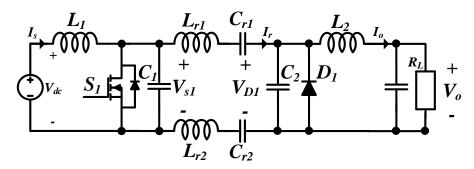

The basic structure of a class E converter is shown in Fig. 2-11. Followed by the class E inverter, a two-port network composed of passive components is placed. A simple LC series network is placed for a class E converter with the same input and output voltage value. A rectifier is then connected to transform high-frequency power to DC. Typically, a half-bridge rectifier or class E type rectifier is used, as shown in Fig. 2-12. While a half-bridge rectifier is simple and requires diodes with less

Fig. 2-12. High frequency rectifier topology (a) class D (b) class E voltage stress, a class E type rectifier creates less EMI noise and less transition loss. In this paper, a class E type rectifier is used to reduce high-frequency common-mode current. The basic operation and analysis of the class E converter are explained in the next section.

#### **2.3.1 Class E Converter Operation**

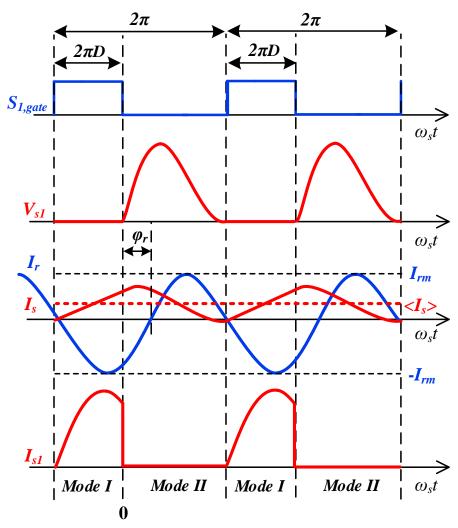

The operation of the class E converter can be divided into two modes, as shown in Fig. 2-13. The voltage and current waveforms at each mode during the steady-state are demonstrated in Fig. 2-14. Here D is the duty ratio of the converter, and  $T_s$  is the switching period. It is assumed that the network contains LC series network with high Q, and therefore, current  $I_r$  is sinusoidal. In mode I, switch  $S_I$  is turned on, increasing the input current  $I_s$ . At this mode, the voltage across the switch  $S_l$  is zero. In mode II, switch  $S_l$  is turned off, increasing the voltage across the switch. At this mode, input current  $I_s$ stored at inductor  $L_1$  charges capacitor  $C_1$  placed across the switch. The voltage Vsi continually increases until inductor current  $I_s$  reaches resonant current  $I_r$ .  $V_{SI}$  is at its maximum when  $I_s$  equals  $I_r$ . After this point, resonant current  $I_r$  is larger than

Fig. 2-13. Operation of a class E inverter (a) switch  $S_1$  on (b) switch  $S_1$  off

inductor current  $I_s$ , discharging the capacitor  $C_l$ . If  $C_l$  is fully discharged before the switch is turned on, ZVS (zero voltage switching) is achieved, eliminating switching loss. In addition to the ZVS condition, the derivative of switch voltage dv/dt at switch turn on is also an essential condition when designing a class E converter. Fig. 2–15 shows the voltage and current waveforms when dv/dt is smaller than zero, and dv/dt equals zero. When dv/dt

Fig. 2-14. Voltage and current waveforms of a class E inverter

is smaller than zero, negative current flows through the switch  $S_I$ . At this point, the body diode of switch  $S_I$  starts conducting. Since the body diode of GaN MOSFET typically has poor conduction performance, reducing time when the body diode is conducting is vital for increasing the efficiency of the class E converter. Thus, many class E converter is designed to achieve ZVS, and dv/dt equals zero.

Fig. 2-15. Class E inverter voltage and current waveforms when (a) dv/dt < 0 (b) dv/dt = 0

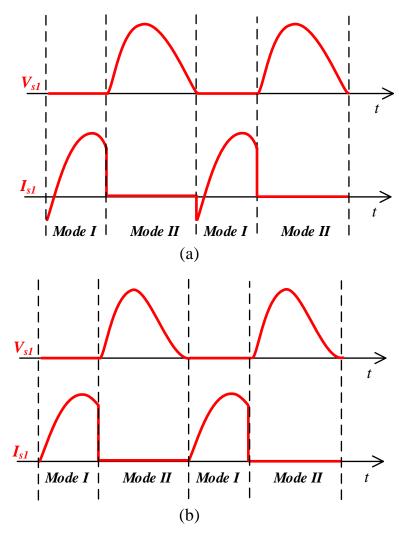

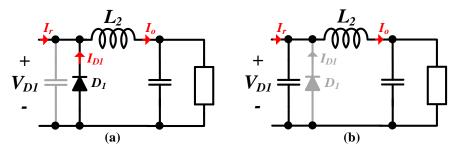

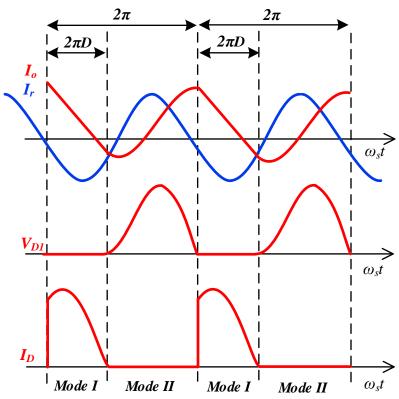

Fig. 2-16. The operation of class E rectifier (a) Mode I diode  $D_I$  turn on (b) Mode II diode  $D_I$  turn off.

The operation of the class E rectifier is also divided into two modes, as shown in Fig. 2–16. In mode I, the diode conducts the current reducing the current  $I_o$ . When diode current  $I_{DI}$ reaches zero, the diode stops conducting, increasing the voltage across the diode  $V_{DI}$ . The voltage and current waveforms of the

Fig. 2-17. Voltage and current waveforms of class E rectifier

Fig. 2–18. Capacitive Isolated class E DC/DC converter class E diode are shown in Fig. 2–17. A class E converter with both class E inverter and class E rectifier with a simple LC series network is shown in Fig. 2–18.

#### **2.3.2 Inverter and Rectifier Voltage Analysis**

In this section, the voltage across the active component of the converter  $V_{SI}$  and  $V_{DI}$  are calculated. These values will be later used to estimate the common-mode current. Since many factors affect the switch voltage  $V_{SI}$ , some constraints are made to analyze the switch voltage according to duty ratio. First, to simplify the calculation, it is assumed that resonant current  $I_r$  is sinusoidal, and other harmonic terms are neglected.

$$I_r = I_{rm} \sin(\omega_s t + \varphi_r). \qquad (2-6)$$

Here  $I_{rm}$  is the magnitude, and  $\varphi_r$  is a phase of resonant current as depicted in Fig. 2–14. Also, switch voltage when ZVS and dv/dtequals zero conditions are both satisfied will be calculated.

In mode II,  $V_{SI}$  and  $I_s$  can be written as

$$\begin{cases} L_1 \frac{dI_s}{dt} = V_{dc} - V_{S1} \\ C_1 \frac{dV_{S1}}{dt} = I_s - I_{rm} \sin(\omega_s t + \varphi_r) \end{cases} \quad 0 < \omega_s t \le 2\pi (1 - D) \ . \tag{2-7}$$

After solving the above differential equations,  $V_{SI}$  can be rewritten as

$$V_{S1} = V_{dc} - V_{dc} \cos(\omega_{l}t) - \frac{Z_{1}I_{rm}(\omega_{l}/\omega_{s})\sin(\varphi_{r})}{1 + (\omega_{l}/\omega_{s})}\sin(\omega_{l}t) + Z_{1}I_{s}(0)\sin(\omega_{l}t) + \frac{Z_{1}I_{rm}(\omega_{l}/\omega_{s})}{1 - (\omega_{l}/\omega_{s})^{2}} \{\cos(\omega_{s}t + \varphi_{r}) - \cos(\omega_{l}t + \varphi_{r})\}, \quad (2-8)$$

where  $\omega_l = 1/\sqrt{L_l C_l}$  and  $Z_l = \sqrt{L_l / C_l}$ . Using equations (2-7)

and (2-8),  $I_s$  can be expressed as

$$I_{s} = \frac{V_{dc}}{Z_{1}} \sin(\omega_{1}t) - \frac{(\omega_{1}/\omega_{s})I_{rm}\sin(\varphi_{r})}{1 + (\omega_{1}/\omega_{s})} \cos(\omega_{1}t) + I_{s}(0)\cos(\omega_{1}t) + \frac{I_{rm}(\omega_{1}/\omega_{s})}{1 - (\omega_{1}/\omega_{s})^{2}} \{\sin(\omega_{1}t + \varphi_{r}) - (\omega_{1}/\omega_{s})\sin(\omega_{s}t + \varphi_{r})\}$$

$$(2-9)$$

To achieve zero voltage switching (ZVS) and dv/dt = 0 conditions,  $V_{SI}$  should be zero, and  $I_s$  should equal to  $I_r$  at switch turn-on. Then following equations can be derived

$$1 - \cos(B) - \frac{\omega_{1,n} K \sin(\varphi_r)}{1 + \omega_{1,n}} \sin(B) + \frac{Z_1 I_s(0)}{V_{dc}} \sin(B) + \frac{K \omega_{1,n}}{1 - \omega_{1,n}^2} \{\cos(A + \varphi_r) - \cos(B + \varphi_r)\} = 0 \qquad (2 - 10)$$

$$\sin(B) - \frac{\omega_{1,n} K \sin(\varphi_r)}{1 + \omega_{1,n}} \cos(B) + \frac{Z_1 I_s(0)}{V_{dc}} \cos(B) + \frac{K \omega_{1,n}}{1 - \omega_{1,n}^2} \{ \sin(B + \varphi_r) - \omega_{1,n} \sin(A + \varphi_r) \} = 0$$

(2-11)

where  $\omega_{1,n} = (\omega_1/\omega_s), A = 2\pi(1-D), B = 2\pi\omega_{1,n}(1-D), K = Z_1 I_m/V_{dc}$ .

At mode I, the switch is turned on, and the voltage across the switch equals zero if the ideal switch is assumed. Therefore,  $V_{SI}$  and  $I_s$  can be written as

$$\begin{cases} L_1 \frac{dI_s}{dt} = V_{dc} & 2\pi (1 - D) < \omega_s t \le T_s. \\ V_{s_1} = 0 & (2 - 12) \end{cases}$$

Solving the above differential equation,  $I_s$  can be expressed as

$$I_{s} = \frac{V_{dc}}{\omega_{1}L_{1}}(\omega_{1}t - B) + I_{rm}\sin(A + \varphi_{r})$$

(2-13)

where it is assumed that  $I_s$  is equals to  $I_{rm}\sin(A + \varphi_r)$  at  $\omega_s t = 2\pi(1-D)$ to achieve dv/dt = 0 condition. Also, assuming a steady-state operation,  $I_s(T_s)$  should be equals to  $I_s(0)$ . Therefore, according to equation (2-13)

$$I_{s}(0) = \frac{V_{dc}}{Z_{1}} (2\pi\omega_{1,n} - B) + I_{rm} \sin(A + \varphi_{r}). \qquad (2-14)$$

Using above equations (2-10), (2-11) and (2-14),  $\varphi_r$  and K according to D and  $\omega_{I,n}$  can be calculated as

$$\tan(\varphi_r) = -\frac{n(D, \omega_{1,n})}{d(D, \omega_{1,n})}$$

(2-15)

$$n(D, \omega_{1,N}) = \left(\sin(B) + (2\pi\omega_{1,N} - B)\cos(B)\right) \left[\sin(A)\sin(B) - \frac{\omega_{1,N}\left(\cos(A) - \cos(B)\right)}{1 - {\omega_{1,N}}^2}\right] - \left(1 - \cos(B) + (2\pi\omega_{1,N} - B)\sin(B)\right) \left[\sin(A)\cos(B) - \frac{\sin(A) - \omega_{1,N}\sin(B)}{1 - {\omega_{1,N}}^2}\right]$$

$$d(D, \omega_{1,N}) = \left(\sin(B) + (2\pi\omega_{1,N} - B)\cos(B)\right) \left[\cos(A)\sin(B) - \frac{\omega_{1,N}\sin(B)}{1 + \omega_{1,N}} - \frac{\omega_{1,N}\left(\sin(A) - \sin(B)\right)}{1 - \omega_{1,N}^{2}}\right] - \left(1 - \cos(B) + (2\pi\omega_{1,N} - B)\sin(B)\right) \left[\cos(A)\cos(B) - \frac{\omega_{1,N}\cos(B)}{1 + \omega_{1,N}} - \frac{\cos(A) - \omega_{1,N}\cos(B)}{1 - \omega_{1,N}^{2}}\right]$$

$$K = \frac{-\left(\sin(B) + 2\pi\omega_{1,N}D\cos(B)\right)}{\sin(A + \varphi_r)\cos(B) - \frac{\omega_{1,N}\cos(B)\sin(\varphi_r)}{1 + \omega_{1,N}} - \frac{\sin(A + \varphi_r) - \omega_{1,N}\sin(B + \varphi_r)}{1 - \omega_{1,N}^2}} (2-16)$$

Using the above equations, fundamental and harmonic components of the output voltage of class E inverter  $V_{SI}$  can be

calculated. Here  $V_{SI,n}$  is defined as an  $n^{th}$  harmonic term of  $V_{SI}$ . Then  $V_{SI,n}$  can be written as

$$V_{S1,n}(t) = |V_{S1,n}| \sin(n\omega_s t + \varphi_r + \psi_n)$$

=  $|V_{S1,n}|_{sin} \sin(n\omega_s t + \varphi_r) + |V_{S1,n}|_{cos} \cos(n\omega_s t + \varphi_r)$  (2-17)

where  $|V_{S1,n}| = \sqrt{|V_{S1,n}|_{\cos}^2 + |V_{S1,n}|_{\sin}^2}$  and  $\tan(\psi_n) = |V_{S1,n}|_{\sin} / |V_{S1,n}|_{\cos}$ . Using

a Fourier series,  $|V_{\mathit{SI},n}|_{\rm cos}$  and  $|V_{\mathit{SI},n}|_{\rm sin}$  can be calculated as

$$\left| V_{S1,n} \right|_{\cos} = \frac{1}{\pi} \int_0^{2\pi} V_{S1}(t) \cos(n\omega_s t + \varphi_r) d(\omega_s t) , \qquad (2-18)$$

$$\left|V_{S1,n}\right|_{\sin} = \frac{1}{\pi} \int_0^{2\pi} V_{S1}(t) \sin(n\omega_s t + \varphi_r) d(\omega_s t) . \qquad (2-19)$$

Utilizing inverter output voltage  $V_{SI}$  equation (2–8), the solution for the above Fourier series equations can be calculated as

$$\frac{\left|V_{S1,n}\right|_{\sin}}{V_{dc}} = \frac{1}{n\pi} \left\{ \cos(\varphi_r) - \cos(nA + \varphi_r) \right\} - K_{p1,n} + K_{p2,n} \left\{ K \sin(A + \varphi_r) + 2\pi \omega_{1,N} D - \frac{K \omega_{1,N} \sin(\varphi_r)}{1 + \omega_{1,N}} \right\} + \frac{K \omega_{1,N}}{1 - \omega_{1,N}^{2}} (K_{p3,n} - K_{p4,n})$$

(2 - 20)

$$2\pi K_{p1,n} = \frac{\cos(\varphi_r) - \cos(nA + B + \varphi_r)}{n + \omega_{1,N}} + \frac{\cos(\varphi_r) - \cos(nA - B + \varphi_r)}{n - \omega_{1,N}}$$

$$2\pi K_{p2,n} = -\frac{\sin(nA+B+\varphi_r) - \sin(\varphi_r)}{n+\omega_{1,N}} + \frac{\sin(nA-B+\varphi_r) - \sin(\varphi_r)}{n-\omega_{1,N}}$$

$$2\pi K_{p3,n} = \frac{\cos(2\varphi_r) - \cos((n+1)A + 2\varphi_r)}{n+1} + \frac{\cos((n-1)A) - 1}{n-1}$$

$$2\pi K_{p4,n} = \frac{\cos(2\varphi_r) - \cos(nA + B + 2\varphi_r)}{n + \omega_{1,N}} + \frac{\cos(nA - B) - 1}{n - \omega_{1,N}}$$

$$\frac{\left|V_{s1,n}\right|_{\cos}}{V_{dc}} = \frac{1}{n\pi} \left\{ \sin(nA + \varphi_r) - \sin(\varphi_r) \right\} - K_{q1,n} + K_{q2,n} \left\{ K \sin(A + \varphi_r) + 2\pi \omega_{1,N} D - \frac{K \omega_{1,N} \sin(\varphi_r)}{1 + \omega_{1,N}} \right\} + \frac{K \omega_{1,N}}{1 - \omega_{1,N}^2} (K_{q3,n} - K_{q4,n})$$

(2-21)

$$2\pi K_{q1,n} = \frac{\sin(nA + B + \varphi_r) - \sin(\varphi_r)}{n + \omega_{1,N}} + \frac{\sin(nA - B + \varphi_r) - \sin(\varphi_r)}{n - \omega_{1,N}}$$

$$2\pi K_{q2,n} = \frac{\cos(\varphi_r) - \cos(nA + B + \varphi_r)}{n + \omega_{1,N}} - \frac{\cos(\varphi_r) - \cos(nA - B + \varphi_r)}{n - \omega_{1,N}}$$

$$2\pi K_{q3,n} = \frac{\sin((n+1)A + 2\varphi_r) - \sin(2\varphi_r)}{n+1} + \frac{\sin((n-1)A) - 1}{n-1}$$

$$2\pi K_{q4,n} = \frac{\sin(nA + B + 2\varphi_r) - \sin(2\varphi_r)}{n + \omega_{1,N}} + \frac{\sin(nA - B)}{n - \omega_{1,N}}$$

Fig. 2–19. Class E inverter output voltage magnitude (a) fundamental term (b)  $2^{nd}$  harmonic term (c)  $3^{rd}$  harmonic term

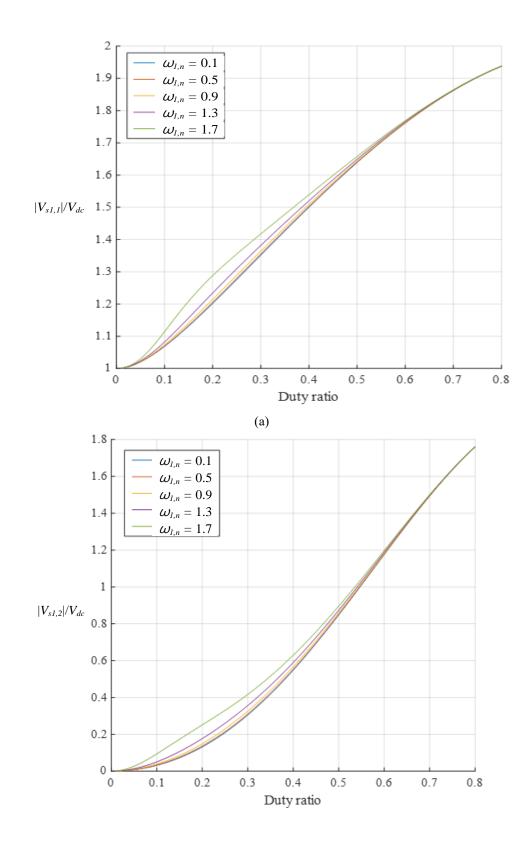

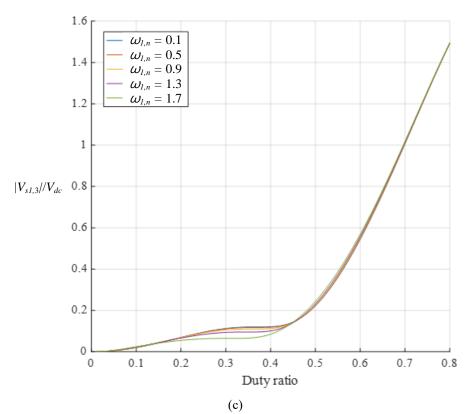

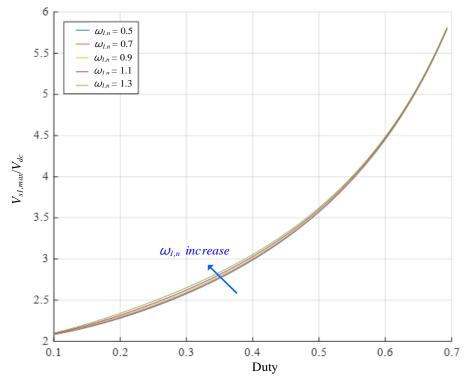

Using these equations, the fundamental term and harmonic terms of the inverter output voltage can be calculated. Fig. 2–19 shows the fundamental,  $2^{nd}$  harmonic, and  $3^{rd}$  harmonic terms of inverter output voltage for different  $\omega_{I,n}$  and duty ratio. It can be seen that both fundamental and harmonic terms increase as the duty ratio

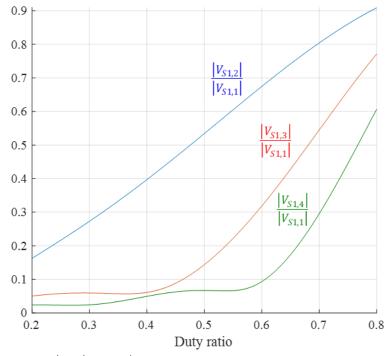

increases. Fig. 2–20 shows the 2<sup>nd</sup>, 3<sup>rd,</sup> and 4<sup>th</sup> harmonic terms compared to fundamental components when  $\omega_{I,n} = 1.4$ . In this figure, 3<sup>rd</sup> and 4<sup>th</sup> harmonic terms have small values when the duty ratio is below 0.5. Compared to the 2<sup>nd</sup> harmonic term, higher harmonic terms are more than five times smaller in most duty ratios below 0.5. However, at a high duty ratio, higher harmonic terms are comparable to 2<sup>nd</sup> harmonic and cannot be ignored. Nonetheless, in most class E converter designs, a high duty ratio above 0.5 is often not used since the maximum voltage across the switch  $S_I$  increases as the duty ratio increases, shown

Fig. 2–20.  $2^{nd}$ ,  $3^{rd}$  and  $4^{th}$  harmonic terms of a class E inverter output voltage normalized by fundamental term.

in Fig. 2–21. Here  $V_{SI,max}$  is a peak voltage across the switch  $S_I$  during steady-state operation. According to this figure, when the duty ratio equals 0.5, the maximum voltage across switch  $S_I$  is 3.6 times the DC-link input voltage  $V_{dc}$ . When the duty ratio equals 0.6, the maximum voltage is more than 4.5 times the DC input voltage. Therefore, to reduce the voltage stress of the switch  $S_I$ , a class E converter is designed to operate at lower duty. Thus, in this paper, fundamental and  $2^{nd}$  harmonic terms are primarily analyzed since these terms are dominant compared to other harmonic terms in low duty ratio. The phase of the

Fig. 2- 21. Maximum voltage across switch  $S_l$  during steady-state operation at different duty ratio.

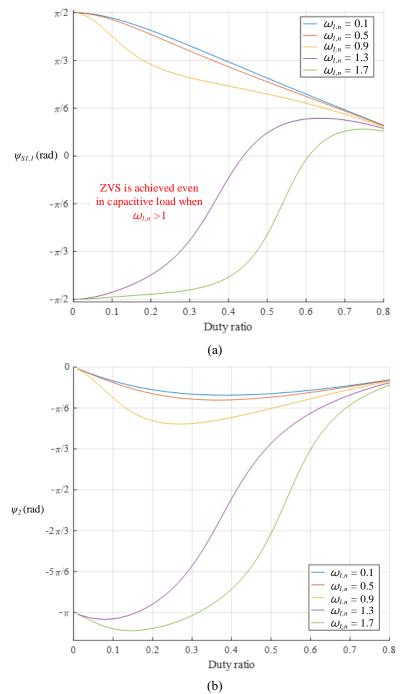

inverter output voltage  $\Psi_{Sl,1}$  and  $\Psi_{Sl,2}$  is shown in Fig. 2–22. From the figure, if  $\omega_{l,n}$  is designed below one,  $\Psi_{Sl,l}$  is consistently between zero and  $\pi/2$ . This means a resonant current  $I_r$  should be lagging compared to  $V_{Sl,l}$  to achieve ZVS. If  $\omega_{l,n}$  is above one, however, there is a region where  $\Psi_{Sl,l}$  lies between zero and  $-\pi/2$ . This means that ZVS can still be achieved at some duty ratios even if  $I_r$  is leading compared to  $V_{Sl,l}$ . The reason for this result is due to a small inductance of  $L_l$  at large  $\omega_{l,n}$ . At large  $\omega_{l,n}$ inductor  $L_l$  is small and resonates with capacitor  $C_l$  creating resonant current in  $I_s$ . These currents help the class E converter achieve ZVS and set the phase of the voltage  $V_{Sl,l}$  between zero and  $-\pi/2$ .

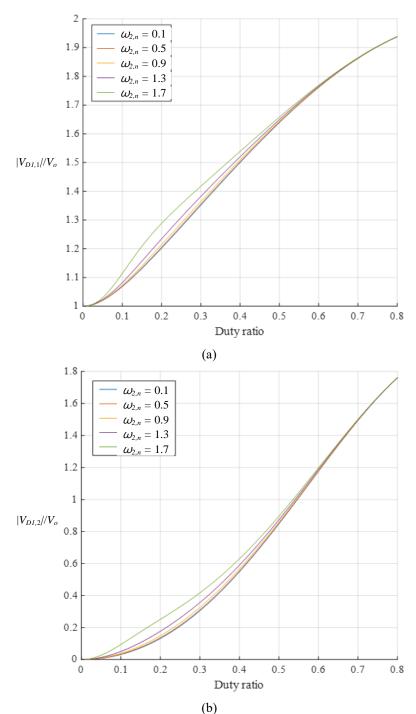

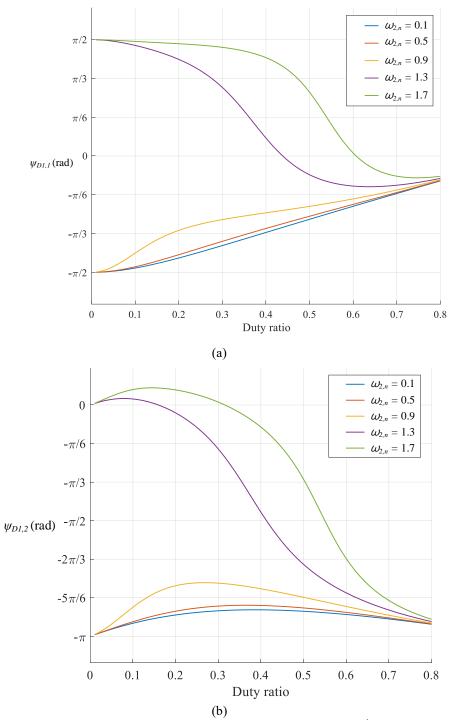

A class E rectifier works in duality with a class E inverter [65]. Assuming diode forward voltage drop is small, the magnitude of rectifier voltage  $V_{DI}$  can be calculated with the same result with an inverter by replacing parameters  $L_I$ ,  $C_{I_i}$  and  $V_{dc}$  in

Fig. 2-22 Phase of the inverter output votlage (a) fundamental (b)  $2^{\rm nd}$  harmonic term

equations (2-7) - (2-21) with  $L_2$ ,  $C_2$ , and  $V_o$ . Let  $\omega_{2,N} = \left(\omega_s \sqrt{L_2 C_2}\right)^{-1}$ , Fig. 2-23 shows the magnitude of fundamental

Fig. 2–23. Magnitude of rectifier voltage (a) fundamental (b)  $2^{nd}$  harmonic term

$|V_{DI,I}|$  and  $2^{nd}$  harmonic term  $|V_{DI,2}|$  of rectifier voltage, and Fig. 2–24 shows the phase of fundamental  $\Psi_{D1,1}$  and second harmonic

Fig. 2-24. Phase of rectifier voltage (a) fundamental (b)  $2^{nd}$  harmonic term

$\Psi_{D1,2}$  term of rectifier voltage. The forward drop of diode  $D_1$  is neglected in this equation. If  $\omega_{1,n} = \omega_{2,n}$ , the relationship between

class E inverter output voltage and class E rectifier output voltage can be simplified. The magnitude and phase  $V_{SI}$  and  $V_{DI}$ satisfies the below equation when  $\omega_{I,n} = \omega_{2,n}$

$$\frac{|V_{S1,n}|}{V_{dc}} = \frac{|V_{D1,n}|}{V_o}$$

(2-22)

$$\psi_{S1,1} = -\psi_{D1,1}, \ \psi_{S1,2} = -\psi_{D1,2} + \pi \tag{2-23}$$

These results will be used to analyze the fundamental and harmonic terms of common-mode current in the class E converter.

# 3. Class E Converter with LC Series Network 3.1 Common Mode Current in Class E Converter with LC Series Network

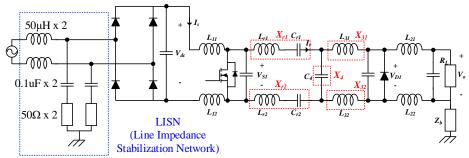

Fig. 3-1. Modeling procedure of class E capacitive isolated converter (a) capacitive isolated converter with LC series network (b) dividing AC/DC rectifier part and DC/DC converter part (c) active components modeling for common mode current estimation

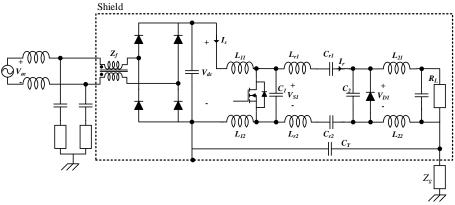

In order to analyze the common-mode current in the class E DC/DC converter, the circuit model shown in Fig. 3–1 is used. First, AC/DC rectifier part and DC/DC converter part are divided as shown in Fig. 3–1 (b). Next, assuming common mode current is small compared to the differential mode current, active components are modeled as a voltage source where  $V_{SI}$  and  $V_{DI}$  are a voltage across the switch  $S_I$  and diode  $D_I$ . Also, since DC voltage sources do not contribute to common mode current, input and output of the DC/DC converter are shorted to simplify the model, as shown in Fig. 3–1 (c).

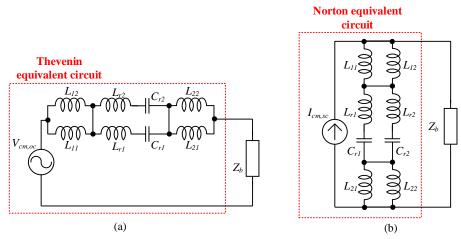

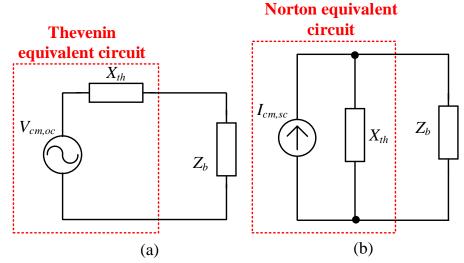

Using this model, a high-frequency common mode current can be calculated. Simplifying Fig. 3-1(c) such that only the high-frequency component remains, Thevenin and Norton equivalent circuit seen from the common-mode side can be drawn. Fig. 3-2 shows the process of drawing a common-mode equivalent circuit. The resulting Thevenin and Norton equivalent circuit is shown in Fig. 3-3. where open circuit voltage  $V_{cm,oc}$ , and short circuit current  $I_{cm,sc}$  can be calculated as

Fig. 3-2. Calculating common-mode Thevenin equivalent circuit (a) common-mode modeling (b) open circuit voltage calculation (c) short circuit current calculation

Fig. 3-3. Common-mode equivalent circuit (a) Thevenin equivalent circuit (b) Norton equivalent circuit

$$V_{cm,oc}(s) = \frac{\left(sL_{r2} + \frac{1}{(sC_{r2})}\right)\left(V_{s1}(s) - V_{D1}(s)\right)}{s(L_{r1} + L_{r2}) + (C_{r1} + C_{r2}) / (sC_{r1}C_{r2})}$$

(3-1)

$$I_{cm,sc}(s) = \frac{V_{s1}(s) - V_{D1}(s)}{sL_{r1} + 1/(sC_{r1})}.$$

(3-2)

Applying results from Fig. 2–19 – Fig. 2–24, the common-mode current at each frequency can be calculated. The magnitude of  $I_{cm,sc}$  at switching frequency  $\omega_s$  and  $2\omega_s$ , can be written as

$$\left|I_{cm,sc}(j\omega_{s})\right| = \left|\frac{|V_{S1,1}| \angle \psi_{S1,1} - |V_{D1,1}| \angle \psi_{D1,1}}{\{\omega_{s}L_{r1} - 1/(\omega_{s}C_{r1})\}}\right|$$

(3-3)

$$\left|I_{cm,sc}(j2\omega_{s})\right| = \left|\frac{|V_{S1,2}| \angle \psi_{S1,2} - |V_{D1,2}| \angle \psi_{D1,2}}{\{2\omega_{s}L_{r1} - 1/(2\omega_{s}C_{r1})\}}\right|$$

(3-4)

If  $L_l$  is equal to  $L_2$  and  $C_l$  is equal to  $C_2$ , both inverter and rectifier operate in the same duty ratio and  $\omega_{l,n} = \omega_{2,n}$ . Also, the inverter and rectifier's fundamental and harmonic voltage magnitude becomes the same. At this condition, the equation (3-3) and (3-4) then can be rewritten as

$$\left|I_{cm,sc}(j\omega_{s})\right| = \frac{\left|V_{S1,1}\right| \sqrt{2(1 - \cos(2\psi_{S1,1}))}}{\left|\omega_{s}L_{r1} - 1/(\omega_{s}C_{r1})\right|}$$

(3-5)

$$\left|I_{cm,sc}(j2\omega_{s})\right| = \frac{\left|V_{s1,2}\right|\sqrt{2(1+\cos(2\psi_{s1,2}))}}{\left|2\omega_{s}L_{r1}-1/(2\omega_{s}C_{r1})\right|}$$

(3-6)

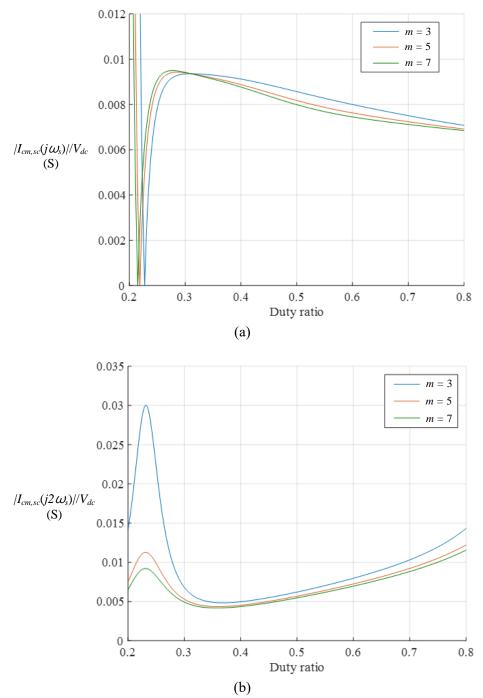

Fig. 3-4 shows the plot of the transconductance of commonmode current magnitude  $|I_{cm,sc}|/V_{dc}$  at frequency  $\omega_s$  and  $2\omega_s$  when  $L_{r1}$ = 0 and  $C_{r1}$  = 220 pF. From the figure, there exists a point where  $I_{cm,sc}$  is equal to zero.  $I_{cm,sc}(j\omega_s)$  is equal to zero when  $\Psi_{SI,1}$  is equal to zero and  $I_{cm,sc}(j2\omega_s)$  is equal to zero when  $\Psi_{SI,2}$  is equal to  $\pi/2$ . This point can only exist when class E inverter and rectifiers are designed such that both  $\omega_{I,n}$  and  $\omega_{2,n}$  are greater than one, as mentioned in the previous section.

Fig. 3–4. Transconductance of common-mode current (a) fundamental (b)  $2^{nd}$  harmonic term

Using Norton equivalent circuit in Fig. 3–3, the common-mode current  $I_{cm}$  can be calculated using a short circuit common-mode current  $I_{cm,sc}$  value using the equation below

$$\left|I_{cm}(jn\omega_{s})\right| = \left|\frac{I_{cm,sc}(jn\omega_{s})\left\{Z_{b}(jn\omega_{s}) \parallel jX_{th}(jn\omega_{s})\right\}}{Z_{b}(jn\omega_{s})}\right|, \quad (3-7)$$

where  $jX_{th}$  is a Thevenin impedance, also equal to Norton impedance, calculated as  $V_{cm,oc}/I_{cm,sc}$ . In capacitive isolated class E converter with LC series network in Fig. 3–1,  $X_{th}$  is equal to a parallel of two LC series as shown in equivalent circuit in Fig. 3– 3. Following impedance  $X_{th}$  can be calculated as

$$X_{th}(jn\omega_{s}) = \frac{(n\omega_{s})^{2}L_{r1}L_{r2} + \frac{1}{(n\omega_{s})^{2}C_{r1}C_{r2}} - \frac{L_{r1}C_{r1} + L_{r2}C_{r2}}{C_{r1}C_{r2}}}{(n\omega_{s})(L_{r1} + L_{r2}) - \frac{C_{r1} + C_{r2}}{(n\omega_{s})C_{r1}C_{r2}}}.$$

(3-8)

$Z_b$  is an impedance of a common-mode current path. It is different depending on how the load is connected to the ground. For example, if the load and ground have no physical connection,  $Z_b$  has a very high impedance and vice versa. Also, if a common-

Fig. 3-5. Common-mode choke placed between AC input and AC/DC converter

mode choke filter is placed between AC input and AC/DC converter, as shown in Fig. 3-5, the impedance of the common-mode choke is included in  $Z_b$ .

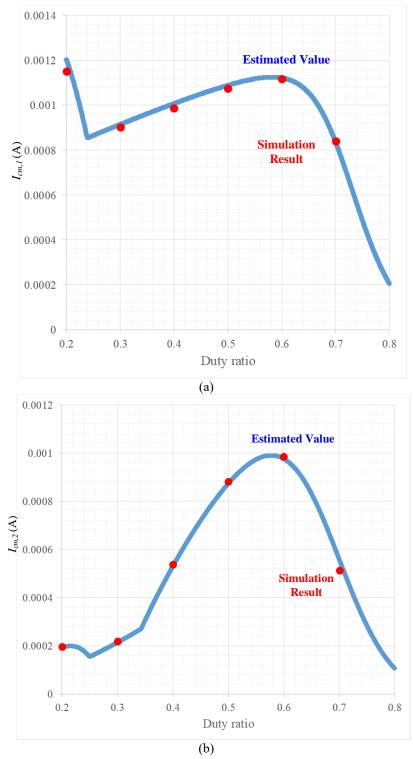

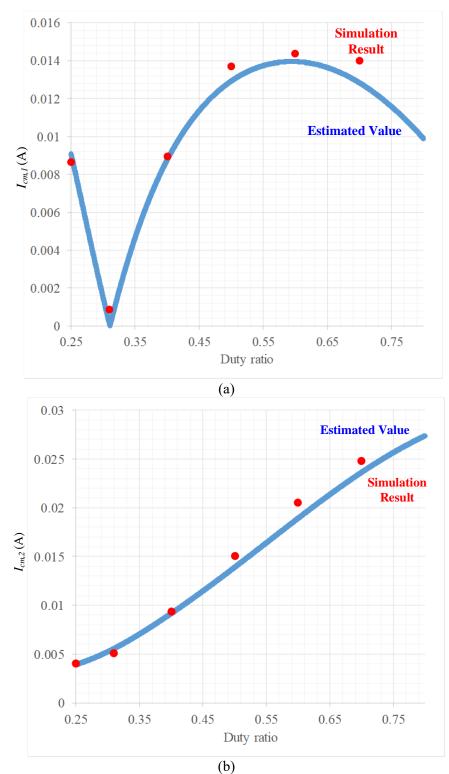

Fig. 3–6 compares the estimated common mode current using equation (3-5) - (3-7) and simulation result value. In this figure, fundamental  $|I_{cm}(j\omega_s)|$  and second harmonic term  $|I_{cm}(j2\omega_s)|$  when  $\omega_{I,n}$  $= \omega_{2,n} = 1.14$  and  $Z_b = 3000 \Omega$  are compared. The capacitor value  $C_{r1}$  and  $C_{r2}$  is set to 220 pF, and inductor  $L_{r1}$  and  $L_{r2}$  are set such that ZVS and dv/dt equals zero condition is satisfied. The estimated and simulated results are almost identical, but errors increase as the duty ratio increases. This error is caused by the increase in harmonic current in  $I_r$  as the duty ratio increases. In section 2, the output voltage equation of the class E inverter is calculated assuming resonant current  $I_r$  is sinusoidal with no harmonic component. However, as the duty ratio increases, the harmonic current appears in  $I_r$  due to the high-frequency component of inverter output voltage, increasing the estimation error. Fig. 3-7 shows the change in estimation and simulation value when small  $C_{r1}$  and  $C_{r2}$  is used for high-quality factor LC series circuit. In this result,  $C_{rl}$  and  $C_{r2}$  are set to 50 pF. From the figure, the estimation and simulation value is very close even in

Fig. 3–6. Comparison between estimated common-mode current and simulated value (a) fundamental (b)  $2^{nd}$  harmonic term

a high duty ratio. However, such a high-quality factor LC series circuit requires a large inductor, and therefore, is not always a feasible option.

Fig. 3–7. Comparison between estimated common-mode current and simulated value with small  $C_r$  (a) fundamental (b) 2<sup>nd</sup> harmonic term

When the duty ratio is around 0.3, a common-mode current is almost zero. This is possible because the common-mode current is proportional to the difference between inverter output voltage  $V_{SI}$  and rectifier voltage  $V_{DI}$ . Therefore, if  $V_{SI}$  and  $V_{DI}$  can negate each other in a common-mode voltage, common-mode current can be eliminated. In fundamental component, a common-mode current is zero when  $\Psi_{SI,I} = \Psi_{DI,I} = 0$ . In 2<sup>nd</sup> harmonic term, a common-mode current is zero when  $\Psi_{SI,2} - \Psi_{DI,2} = \pi$ . However, these two points are not the same, and therefore, other frequency components of common-mode current still remain, so reducing this common-mode current is necessary.

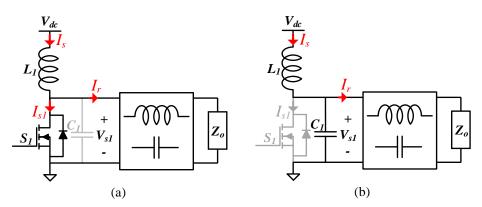

## **3.2 Balanced Class E Converter Design and Analysis**

In this paper, the balanced class E converter shown in Fig. 3-8 is proposed to reduce the high-frequency common-mode

Fig. 3-8. Circuit diagram of balanced class E converter

Fig. 3-9. Common-mode equivalent circuit (a) Thevenin equivalent circuit (b) Norton equivalent circuit

current. In order to estimate and analyze the common mode current of balanced class E converter, the same modeling method is used that analyzes common mode current in conventional capacitive isolated class E converter. Thevenin and Norton equivalent circuit is drawn as shown in Fig. 3–9. The calculated  $V_{cm,oc.}$  and  $I_{cm,sc}$  is

$$V_{cm,oc}(s) = \left\{ \frac{sL_{r2} + 1/(sC_{r2})}{s(L_{r1} + L_{r2}) + (C_{r1} + C_{r2})/(sC_{r1}C_{r2})} - \frac{L_{12}}{L_{11} + L_{12}} \right\} V_{S1}(s) - \left\{ \frac{sL_{r2} + 1/(sC_{r2})}{s(L_{r1} + L_{r2}) + (C_{r1} + C_{r2})/(sC_{r1}C_{r2})} - \frac{L_{22}}{L_{21} + L_{22}} \right\} V_{D1}(s)$$

$$(3-9)$$

$$I_{cm,sc}(s) = \left(\frac{sL_{11}L_{12}}{L_{11} + L_{12}} + \frac{sL_{21}L_{22}}{L_{21} + L_{22}} + \frac{(sL_{r1} + 1/(sC_{r1}))(sL_{r2} + 1/(sC_{r2}))}{s(L_{r1} + L_{r2}) + (C_{r1} + C_{r2})/sC_{r1}C_{r2}}\right)^{-1}V_{cm,oc}(s)$$

$$(3-10)$$

It can be seen from equations (3-9) and (3-10), common-mode

current is completely removed for all frequency components if converter is perfectly balanced, meaning  $L_{11} = L_{12}$ ,  $L_{21} = L_{22}$ ,  $L_{r1} = L_{r2}$ and  $C_{r1} = C_{r2}$ .

A common-mode current can be eliminated if an exact parameter value can be used to design a balanced class E converter. However, it is impossible to develop a perfectly balanced converter in the real world due to the manufacturing error of each passive element and parasitic inductor and capacitor. Due to manufacturing errors, commercial inductors and capacitors have slightly different parameter values even if bought from the same manufacturer. For instance, the air core inductor from coil craft [46] has a minimum stock tolerance of 2%. Although it is still possible to put a special order to buy elements with lower tolerance value, such an order is much more expensive and requires a longer shipping time. Also, parasitic inductance and capacitance depending on PCB layout [47] – [51] also contribute to parameter difference in balanced class E converter. Therefore, effects of parameter error to common mode current in balanced class E converter should be analyzed

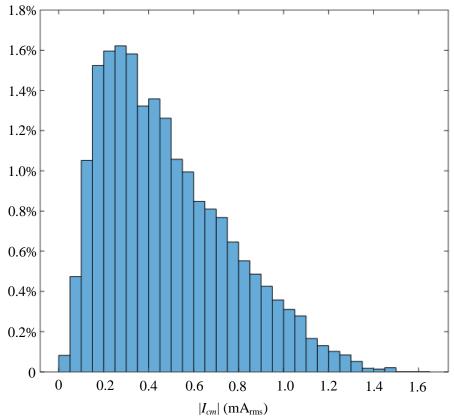

Monte-Carlo simulation is done to examine the effects of parameter error on common-mode current. Fig 3-10 shows a

61

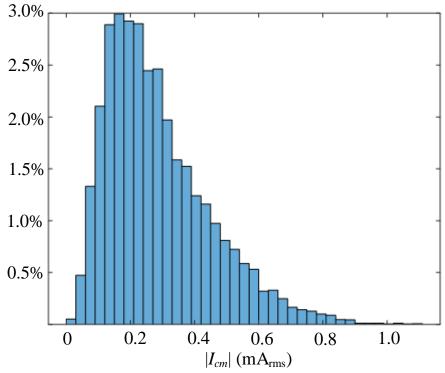

Fig. 3-10. Histogram of root mean square value of common-mode current

| Parameters          | Value       | Parameter<br>Tolerance |

|---------------------|-------------|------------------------|

| $L_{11} \& L_{12}$  | 300 [nH]    | $\pm 2\%$              |

| $L_{r1}$ & $L_{r2}$ | 798 [nH]    | $\pm 2\%$              |

| $C_{rl}$ & $C_{r2}$ | 220 [pF]    | $\pm 10\%$             |

| $L_{21} \& L_{22}$  | 300 [nH]    | $\pm 2\%$              |

| $C_1$ & $C_2$       | 200 [pF]    |                        |

| $f_s$               | 12.14 [MHz] |                        |

| $R_L$               | 300 [Ω]     |                        |

TABLE 3-1. CLASS E CONVERTER WITH LC SERIES NETWORKPARAMETERS USED IN SIMULATION AND EXPERIMENTS

histogram of the root mean square value of common-mode current when the simulation is run 10,000 times. Parameters and their tolerance used in the simulation are shown in Table 3-1. Here inductors have 2% parameter tolerance, and capacitors have 10% parameter tolerance based on the actual parameter tolerance value stated in the datasheet [46] and [60]. This simulation parameter is assumed to be uniformly distributed among parameter tolerance values, and common-mode current path impedance is set to 3000  $\Omega$ . The maximum common-mode current caused by parameter tolerance is 1.62 mA, while the most probable common-mode current value is between 250  $\mu$ A and 300  $\mu$ A from the histogram.

In order to mathematically estimate the effect of parameter error in a balanced converter, the maximum common-mode current of a balanced class E converter within a given parameter tolerance range is calculated. It is assumed that parameter error is small such that it does not affect voltage  $V_{SI}$  and  $V_{DI}$ . Then using parameters  $|V_{SI,n}|$ ,  $|V_{DI,n}|$ ,  $\Psi_{SI,n}$  and  $\Psi_{DI,n}$  calculated in previous section, equation (3–9) can be rewritten as

$$\left|V_{cm,oc}(jn\omega_{s})\right|^{2} = \left(K(jn\omega_{s}) - \frac{L_{12}}{L_{11} + L_{12}}\right)^{2} |V_{S1,n}|^{2} + \left(K(jn\omega_{s}) - \frac{L_{22}}{L_{21} + L_{22}}\right)^{2} |V_{D1,n}|^{2} - 2 |V_{S1,n}| |V_{D1,n}| \left(K(jn\omega_{s}) - \frac{L_{12}}{L_{11} + L_{12}}\right) \left(K(jn\omega_{s}) - \frac{L_{22}}{L_{21} + L_{22}}\right) \cos(\psi_{S1,n} - \psi_{D1,n})$$

$$(3-11)$$

$$K(jn\omega_s) = \frac{1 - (n\omega_s)^2 C_{r_2} L_{r_2}}{(1 + C_{r_2}/C_{r_1}) - (n\omega_s)^2 C_{r_2} (L_{r_1} + L_{r_2})}$$

If both inverter and rectifier operates in same duty ratio and  $\omega_{I,n}$  equals  $\omega_{2,n}$ ,  $|V_{SI,n}|$  is equal to  $|V_{DI,n}|$ .

$$\frac{\left|V_{cm,oc}(jn\omega_{s})\right|^{2}}{\left|V_{s1,n}\right|^{2}} = \left(\frac{X_{r2}}{X_{r1} + X_{r2}} - \frac{L_{12}}{L_{11} + L_{12}}\right)^{2} + \left(\frac{X_{r2}}{X_{r1} + X_{r2}} - \frac{L_{22}}{L_{21} + L_{22}}\right)^{2} (3-12)$$

$$-2\left(\frac{X_{r2}}{X_{r1} + X_{r2}} - \frac{L_{12}}{L_{11} + L_{12}}\right)\left(\frac{X_{r2}}{X_{r1} + X_{r2}} - \frac{L_{22}}{L_{21} + L_{22}}\right)\cos(\psi_{s1,n} - \psi_{D1,n})$$

where  $X_{rl} = \omega L_{rl} - 1/(\omega C_{rl})$  and  $X_{r2} = \omega L_{r2} - 1/(\omega C_{r2})$ . To observe the parameter error effect on  $V_{cm,oc}$ , each parameter is rewritten as below

$$L_{11} = L_1(1 + \lambda_{11}), L_{12} = L_1(1 + \lambda_{12}), L_{21} = L_2(1 + \lambda_{21}), L_{22} = L_2(1 + \lambda_{22})$$

$$X_{r1} = X_r(1 + \lambda_{r1}), X_{r2} = X_r(1 + \lambda_{r2})$$

(3-13)

where  $\lambda$  is a parameter error tolerance often with a few hundredths value. Then using polar coordinates, the parameter tolerance value is altered to

$$\lambda_k = \sqrt{\lambda_{k1}^2 + \lambda_{k2}^2}, \tan(\theta_k) = \frac{\lambda_{k2}}{\lambda_{k1}} (k = 1, 2, r)$$

(3-14)

Using equation (3-13) and (3-14),  $V_{cm,oc}$  equation (3-12) can be rewritten as

$$\frac{\left|V_{cm,oc}(jn\omega_{s})\right|^{2}}{\left|V_{S1,n}\right|^{2}} = \left(\frac{1+\lambda_{r}\sin(\theta_{r})}{2+\lambda_{r}(\sin(\theta_{r})+\cos(\theta_{r}))} - \frac{1+\lambda_{1}\sin(\theta_{1})}{2+\lambda_{1}(\sin(\theta_{1})+\cos(\theta_{1}))}\right)^{2} + \left(\frac{1+\lambda_{r}\sin(\theta_{r})}{2+\lambda_{r}(\sin(\theta_{r})+\cos(\theta_{r}))} - \frac{1+\lambda_{2}\sin(\theta_{2})}{2+\lambda_{2}(\sin(\theta_{2})+\cos(\theta_{2}))}\right)^{2} - 2\left(\frac{1+\lambda_{r}\sin(\theta_{r})}{2+\lambda_{r}(\sin(\theta_{r})+\cos(\theta_{r}))} - \frac{1+\lambda_{1}\sin(\theta_{1})}{2+\lambda_{1}(\sin(\theta_{1})+\cos(\theta_{1}))}\right) \\ \left(\frac{1+\lambda_{r}\sin(\theta_{r})}{2+\lambda_{r}(\sin(\theta_{r})+\cos(\theta_{r}))} - \frac{1+\lambda_{2}\sin(\theta_{2})}{2+\lambda_{2}(\sin(\theta_{2})+\cos(\theta_{2}))}\right)\cos(\psi_{S1,n}-\psi_{D1,n})$$

$$(3-15)$$

Then calculating the derivative of equation (3–15) with  $\theta_k$  yields

$$\frac{d(|V_{cm,oc}|^{2} / |V_{S1,n}|^{2})}{d\theta_{1}} \approx 2 \frac{-\lambda_{1}(\cos(\theta_{1}) + \sin(\theta_{1}) + \lambda_{1})}{\left\{2 + \lambda_{1}(\sin(\theta_{1}) + \cos(\theta_{1}))\right\}^{2}} \left\{ \left(\frac{1 + \lambda_{r}\sin(\theta_{r})}{2 + \lambda_{r}(\sin(\theta_{r}) + \cos(\theta_{r}))} - \frac{1 + \lambda_{1}\sin(\theta_{1})}{2 + \lambda_{1}(\sin(\theta_{1}) + \cos(\theta_{1}))}\right) - \left(\frac{1 + \lambda_{r}\sin(\theta_{r})}{2 + \lambda_{r}(\sin(\theta_{r}) + \cos(\theta_{r}))} - \frac{1 + \lambda_{2}\sin(\theta_{2})}{2 + \lambda_{2}(\sin(\theta_{2}) + \cos(\theta_{2}))}\right) \cos(\psi_{S1,n} - \psi_{D1,n}) \right\}$$

$$(3-16)$$

$$\frac{d(|V_{cm,oc}|^{2} / |V_{S1,n}|^{2})}{d\theta_{2}} = 2 \frac{-\lambda_{2}(\cos(\theta_{2}) + \sin(\theta_{2}) + \lambda_{2})}{\left\{2 + \lambda_{2}(\sin(\theta_{2}) + \cos(\theta_{2}))\right\}^{2}} \left\{ \left(\frac{1 + \lambda_{r}\sin(\theta_{r})}{2 + \lambda_{r}(\sin(\theta_{r}) + \cos(\theta_{r}))} - \frac{1 + \lambda_{2}\sin(\theta_{2})}{2 + \lambda_{2}(\sin(\theta_{2}) + \cos(\theta_{2}))}\right) - \left(\frac{1 + \lambda_{r}\sin(\theta_{r})}{2 + \lambda_{r}(\sin(\theta_{r}) + \cos(\theta_{r}))} - \frac{1 + \lambda_{1}\sin(\theta_{1})}{2 + \lambda_{r}(\sin(\theta_{r}) + \cos(\theta_{r}))}\right) \cos(\psi_{S1,n} - \psi_{D1,n}) \right\}$$

$$(3-17)$$

$$\frac{d(|V_{cm,oc}|^2 / |V_{S1,n}|^2)}{d\theta_r} = 2 \frac{\lambda_r \left\{ (\sin(\theta_r) + \cos(\theta_r)) + \lambda_r \right\}}{\left\{ 2 + \lambda_r (\sin(\theta_r) + \cos(\theta_r)) \right\}^2} \\ \left\{ \left( 2 \frac{1 + \lambda_r \sin(\theta_r)}{2} - \frac{1 + \lambda_2 \sin(\theta_2)}{2} - \frac{1 + \lambda_1 \sin(\theta_1)}{2} \right) (1 - \cos(\psi_{S1,n} - \psi_{D1,n})) \right\}$$

$$(3-18)$$

65