## 저작자표시-비영리-변경금지 2.0 대한민국

## 이용자는 아래의 조건을 따르는 경우에 한하여 자유롭게

• 이 저작물을 복제, 배포, 전송, 전시, 공연 및 방송할 수 있습니다.

## 다음과 같은 조건을 따라야 합니다:

저작자표시. 귀하는 원저작자를 표시하여야 합니다.

비영리. 귀하는 이 저작물을 영리 목적으로 이용할 수 없습니다.

변경금지. 귀하는 이 저작물을 개작, 변형 또는 가공할 수 없습니다.

- 귀하는, 이 저작물의 재이용이나 배포의 경우, 이 저작물에 적용된 이용허락조건 을 명확하게 나타내어야 합니다.

- 저작권자로부터 별도의 허가를 받으면 이러한 조건들은 적용되지 않습니다.

저작권법에 따른 이용자의 권리는 위의 내용에 의하여 영향을 받지 않습니다.

이것은 이용허락규약(Legal Code)을 이해하기 쉽게 요약한 것입니다.

## Ph. D. DISSERTATION

# Self-Heating and Electrothermal Properties of Sub-5-nm 3-D Transistors

5nm 이하 3D Transistors 의 Self-Heating 및 전열특성 분석 연구

## $\mathbf{BY}$

## **ILHO MYEONG**

August 2021

AND COMPUTER SCIENCE

COLLEGE OF ENGINEERING

SEOUL NATIONAL UNIVERSITY

# Self-Heating and Electrothermal Properties of Sub-5-nm 3-D Transistors

5nm 이하 3D Transistors 의 Self-Heating 및 전열특성 분석 연구

指導教授 신 형 철

이 論文을 工學博士 學位論文으로 提出함. 2021年 8月

서울大學校 大學院 電氣컴퓨터工學部 明 一 鎬

明一鎬의 工學博士 學位論文을 認准함. 2021年8月

委員長 <u>김수환</u> 副委員長 <u>신형철</u>

委 員 최우석

委 員 강명곤

委 員 송익현

# Self-Heating and Electrothermal Properties of Sub-5-nm 3-D Transistors

Ilho Myeong

School of Electrical Engineering and Computer Science

College of Engineering

Seoul National University

In this thesis, Self-Heating Effect (SHE) is investigated using TCAD simulations in various Sub-10-nm node Field Effect Transistor (FET). As the node decreases, logic devices have evolved into 3D MOSFET structures from Fin-FET to Nanosheet-FET. In the case of 3D MOSFET, there are thermal reliability issues due to the following rea sons: i) The power density of the channel is high, ii) The channel structure surrou nded by SiO<sub>2</sub>, iii) The overall low thermal conductivity characteristics due to scaling down. Many papers introduce the analysis and prediction of temperature rise by SHE in the device, but there are no papers presenting the content of mitigation of temperature rise. Therefore, we have studied the methods of decreasing the maximum lattice temperature (T<sub>L,max</sub>) such as shallow trench isolation (STI) composition engineering in Fin-FET, thermal analysis according to DC/AC/duty cycle in nanowire-FET, and active region

( e.g., gate metal thickness, channel width, channel number etc..) optimization in

nanosheet-FET. In addition, lifetime affected by hot carrier injection (HCI) /

bias-temperature instability (BTI) is also analyzed according to various thermal relaxation

methods presented.

Keywords: Self-Heating Effect (SHE), Nanoplate-FET, Nanowire-FET, FinFET,

Vertical-FET, Thermal resistance, Temperature, Time delay, Bias Temperature Instability

(BTI), Hot Carrier Injection (HCI).

**Student Number:** 2016-20893

- ii -

## **CONTENTS**

| Abstract                                                            | i          |

|---------------------------------------------------------------------|------------|

| Contents                                                            | iii        |

| Chapter 1                                                           |            |

| Introduction                                                        |            |

| 1.1. Development of Semconductor structure                          | 1          |

| 1.2. Self-Heating Effect issues in semiconductor devices -          | 3          |

| Chapter 2                                                           |            |

| Thermal-Aware Shallow Trench Isolation Design Opt                   | timization |

| for Minimizing $I_{\text{off}}$ in Various Sub-10-nm 3-D Transistor | ı          |

| 2.1. Introduction                                                   | 7          |

| 2.2. Device Structure and Simulation Condition                      | 7          |

| 2.3. Results and Discussion                                         | 12         |

| 2.4. Summary                                                        | 27         |

| Chapter 3                                                           |            |

| Analysis of Self Heating Effect in DC/AC Mode in Multi-             | channel    |

| <b>GAA-Field Effect Transistor</b>                                  |            |

| 3.1. Introduction                                                   | 32         |

| 3.2. Multi-Channel Nanowire FET and Back End Of Line                     | 33    |

|--------------------------------------------------------------------------|-------|

| 3.3. Work Flow and Calibration Process                                   | 35    |

| 3.4. More Detailed Thermal Simulation of Nanowire-FET                    | 37    |

| 3.5. Performance Analysis by Number of Channels                          | 38    |

| 3.6. DC Characteristic of SHE in Nanowire-FETs                           | 40    |

| 3.7. AC Characteristics of SHE in Nanowire-FETs                          | 43    |

| 3.8. Summary                                                             | 51    |

| Chapter 4 Self-Heating and Electrothermal Properties of Adva             | nced  |

| Sub-5-nm node Nanoplate FET                                              | inccu |

| -                                                                        |       |

| 4.1. Introduction                                                        | 56    |

| 4.2. Device Structure and Simulation Condition                           | 57    |

| 4.3. Thermal characteristics by channel number and width                 | 62    |

| 4.4. Thermal characteristics by inter layer-metal thickness $(T_M)$      | 64    |

| 4.5. Life Time Prediction                                                | 65    |

| 4.6. Summary                                                             | 67    |

| Chapter 5 Study on Self Heating Effect and life time in Vertical-channel |       |

| Field Effect Transistor                                                  |       |

| 5.1. Introduction                                                        | 72    |

| 5.2. Device Structure and Simulation Condition                           | 72    |

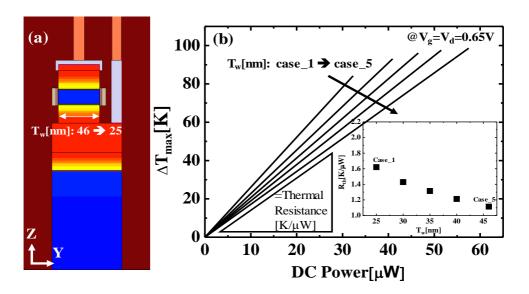

| 5.3. Temperature and R <sub>TH</sub> according to channel width(T <sub>w</sub> ) 76                                                                                                                                                                |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5.4. Thermal properties according to air spacers and air gap 77                                                                                                                                                                                    |

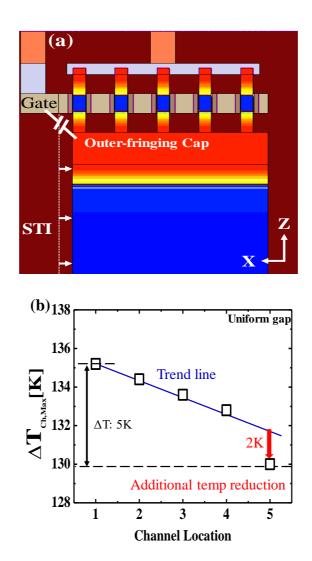

| 5.5. I <sub>on</sub> boosting according to Channel numbers81                                                                                                                                                                                       |

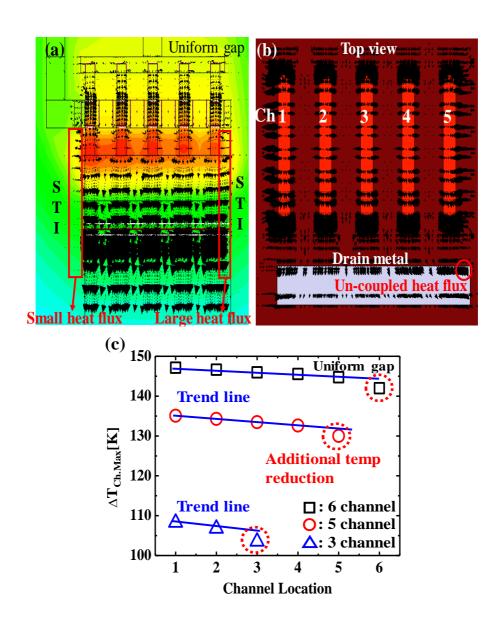

| 5.6. Temperature imbalance of multi-channel VFETs 82                                                                                                                                                                                               |

| 5.7. Mitigation of the channel temperature imbalance 86                                                                                                                                                                                            |

| 5.8. Life time depending on various analysis conditions 88                                                                                                                                                                                         |

| 5.9. Summary 89                                                                                                                                                                                                                                    |

|                                                                                                                                                                                                                                                    |

| Chapter 6                                                                                                                                                                                                                                          |

|                                                                                                                                                                                                                                                    |

| <b>Conclusions</b> 93                                                                                                                                                                                                                              |

| Conclusions 93                                                                                                                                                                                                                                     |

| Appendix A. A Simple and Accurate Modeling Method of                                                                                                                                                                                               |

|                                                                                                                                                                                                                                                    |

| Appendix A. A Simple and Accurate Modeling Method of                                                                                                                                                                                               |

| Appendix A. A Simple and Accurate Modeling Method of Channel Thermal Noise Using BSIM4 Noise Models 95                                                                                                                                             |

| Appendix A. A Simple and Accurate Modeling Method of Channel Thermal Noise Using BSIM4 Noise Models 95  A.1. Introduction 95                                                                                                                       |

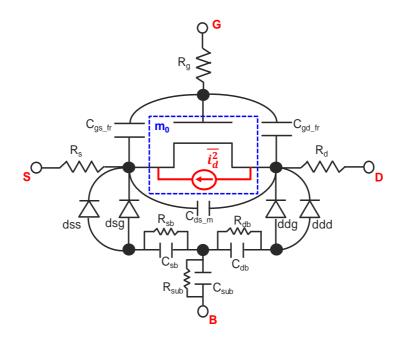

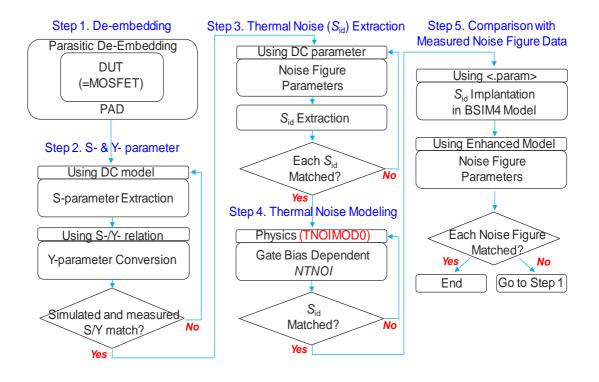

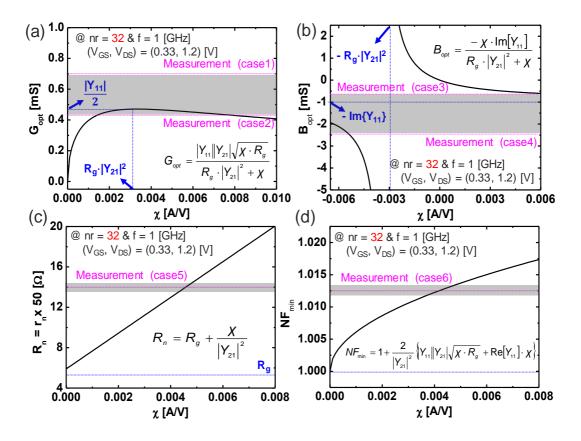

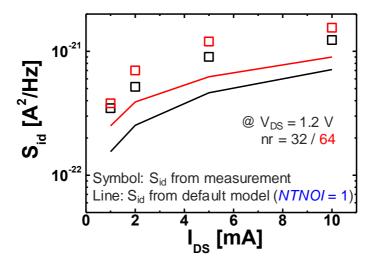

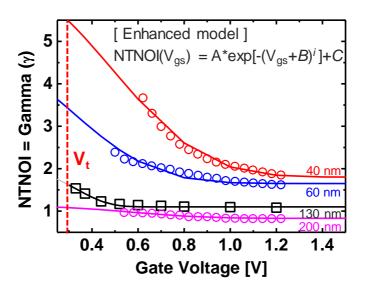

| Appendix A. A Simple and Accurate Modeling Method of Channel Thermal Noise Using BSIM4 Noise Models 95  A.1. Introduction 95  A.2. Overall Schematic of the RF MOSFET Model 97                                                                     |

| Appendix A. A Simple and Accurate Modeling Method of Channel Thermal Noise Using BSIM4 Noise Models                                                                                                                                                |

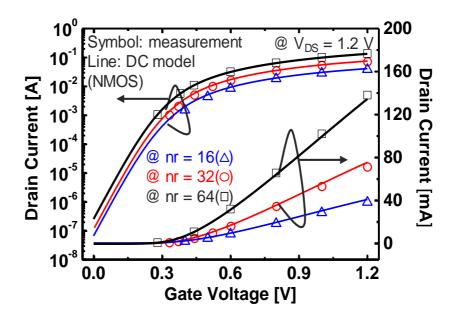

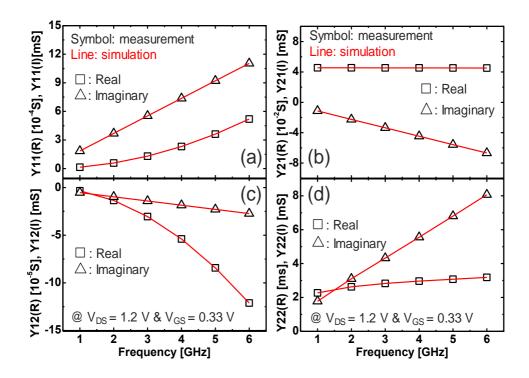

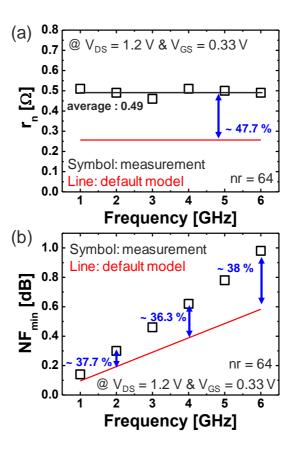

| Appendix A. A Simple and Accurate Modeling Method of Channel Thermal Noise Using BSIM4 Noise Models95  A.1. Introduction95  A.2. Overall Schematic of the RF MOSFET Model97  A.3. Verification of the DC Characteristics of the RF MOSFET  Model98 |

| Appendix A. A Simple and Accurate Modeling Method of Channel Thermal Noise Using BSIM4 Noise Models                                                                                                                                                |

| Appendix A. A Simple and Accurate Modeling Method of Channel Thermal Noise Using BSIM4 Noise Models                                                                                                                                                |

| Appendix A. A Simple and Accurate Modeling Method of Channel Thermal Noise Using BSIM4 Noise Models                                                                                                                                                |

| Abstract in Korean1                                       | 22 |

|-----------------------------------------------------------|----|

| A.10. Conclusion1                                         | 17 |

| A.9. Evaluation the validity of the model for drain bias1 | 15 |

| A.8. Holistic Model (TNOIMOD = 1) 1                       | 14 |

# Chapter 1

## Introduction

## 1.1 Development of semiconductor structure

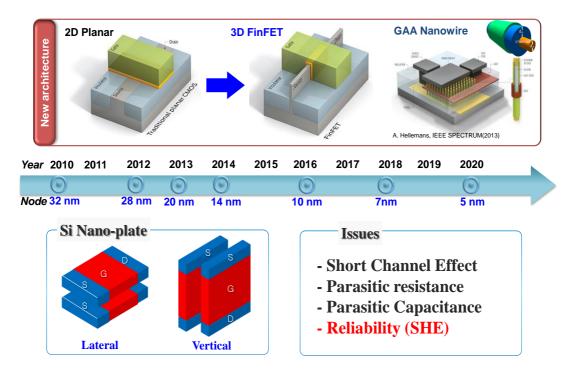

As CMOS technology scales down to a sub-20-nm node, the device experiences severe short-channel effects (SCEs) [1], [2]. To mitigate SCE and have good electrostatic gate control, good subthreshold slope, low-leakage current, and higher transistor density, as shown in Fig. 1.1 device structures have changed from planar structures to multi-gate structures (FinFET). However, as the technology node scaled down from 7 to 5 nm, the FinFET device did not have sufficient electrostatic gate controllability [3]–[5] and thus could not provide further improvement. The gate-all-around (GAA) structure, on the other hand, was a strong candidate for scaling down on sub-5-nm nodes [3]. Furthermore, a nanosheet (NS) structure for better performance has been introduced in [4]. However, even with advanced channel structures of GAA devices, contact gate pitch (CGP) scaling of conventional lateral devices is severely limited by gate length, spacer thickness, and source/drain contact size [5]. Accordingly, vertical nanowire FETs (VFETs) have been proposed to solve the CGP problem and improve scalability. In the conventional device,

the channel is oriented horizontally, while the VFET is oriented vertically. Also, source and drain are at the bottom and top, respectively, with the gate at the center [6]–[9]. Through this vertically oriented structure, the gate length and spacer thickness relaxed CGP and then the SCE can be further mitigated as a result [6]–[9]. VFETs are also more power efficient and have smaller foot prints than lateral field effect transistors of the same node. However, there is no solution for how to induce stress in the channel during VFET fabrication yet and thus cannot increase channel mobility, leading to a lower I<sub>ON</sub> compared to the lateral nanowire FET. Taking this situation into consideration, we have introduced an NS-VFET that makes the width of the channel wide in the nanowire structure to compensate for the weakness of I<sub>ON</sub> of VFETs.

Fig. 1.1. Device structure change according to node and various emerged issues.

## 1.2 Self-Heating Effect issues in Semiconductor devices

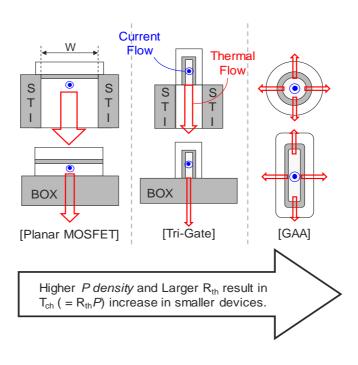

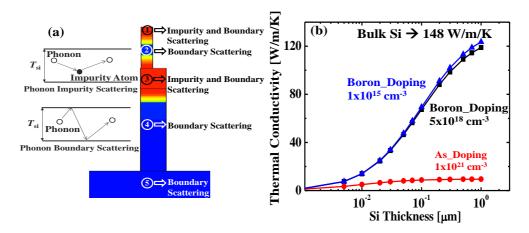

On the other hand, self-heating effect (SHE) is the accumulation of heat in the channel at high-power levels. This is caused by the high current density, material with low thermal conductivity such as SiO2, and a reduced dimension of devices due to downscaling. In the case of Bulk and silicon on insulator (SOI) FinFETs, SiO2 with low thermal conductivity (gate dielectrics; 1.1–1.4 W·m<sup>-1</sup>·K<sup>-1</sup>) surrounds the three sides of the channel [10], [11]. Especially for SOI FinFETs, substrate is also blocked by SiO2 buried oxide (buried oxide (BOX);  $1.4 \cdot m^{-1} \cdot K^{-1}$ ). Therefore, it is impossible to efficiently dissipate heat generated at the channel. In the case of the VFET, the channel is entirely surrounded by SiO2, which makes it difficult to efficiently dissipate the heat generated from the channel. Also, although VFET is not the SOI structure, the drain is located at the bottom as mentioned earlier, and heavily doped drain has low thermal conductivity due to the phonon impurity scattering [12]. For these reasons, the heat dissipation characteristics to the substrate of VFET are also poor. Furthermore, as the device downscaled, the dimensions of the devices (Bulk/SOI FinFET and VFET) became smaller than that of the phonon mean-free-path (100-300 nm). As a result, the thermal conductivity of the Si lattice is influenced by phonon boundary scattering [12], which is lower than that of bulk Si (150  $W \cdot m^{-1} \cdot K^{-1})$  and deteriorates SHE. The lattice temperature (T\_{Lattice}) elevated by SHE further aggravates the vibrations of the lattice, thereby reducing the mobility of the carriers and thus causing performance degradation. In addition, the elevated T<sub>L</sub> further aggravates the hot carrier injection (HCI) and bias temperature instability (BTI), causing problems with reliability [13].

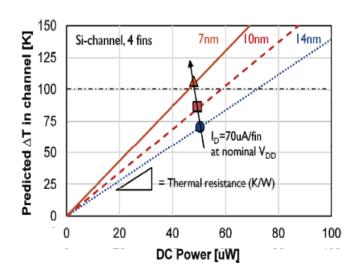

**Fig. 1.2.** (a) Current path and thermal flow according to each structure, (b) Predicted channel temperature rise of Si bulk FinFETs (4 fins) at given drive current. An increase in temperature of about 70℃ is expected for 14nm node and over 100℃ for 7nm node.

## References

- [1] K. J. Kuhn, "CMOS scaling for the 22 nm node and beyond: Device physics and technology," in Proc. Int. Symp. VLSI Technol., Syst. Appl., Apr. 2011, pp. 1–2.

- 2] M. Ieong, B. Doris, J. Kedzierski, K. Rim, and M. Yang, "Silicon device scaling to the sub-10-nm regime," Science, vol. 306, no. 5704, pp. 2057–2060, Dec. 2 004.

- [3] D. Yakimets et al., "Vertical GAAFETs for the ultimate CMOS scaling," IEE E Trans. Electron Devices, vol. 62, no. 5, pp. 1433–1439, May 2015.

- [4] N. Loubet et al., "Stacked nanosheet gate-all-around transistor to enable scaling beyond FinFET," in Proc. Symp. VLSI Technol., Jun. 2017, pp. T230–T231.

- [5] T. H. Bao et al., "Circuit and process co-design with vertical gate-all around nanowire FET technology to extend CMOS scaling for 5 nm and beyond technologies," in Proc. 44th Eur. Solid State Device Res. Conf. (ESSDERC), Sep. 2014, pp. 102–105.

- [6] M. Sharma, S. Maheshwaram, O. Prakash, A. Bulusu, A. K. Saxena, and S. K. Manhas, "Compact model for vertical silicon nanowire based device simulation and circuit design," in Proc. IEEE ISOCC, Nov. 2015, pp. 107–108.

- [7] S. Maheshwaram, S. K. Manhas, G. Kaushal, B. Anand, and N. Singh, "Vertical silicon nanowire gate-all-around field effect transistor based nanoscale CMOS," IEEE Electron Device Lett., vol. 32, no. 8, pp. 1011–1013, Aug. 2011.

- [8] B. Yang, K. D. Buddharaju, S. H. G. Teo, N. Singh, G. Q. Lo, and D. L. K wong, "Vertical silicon-nanowire formation and gate-all-around MOSFET," IEEE El ectron Device Lett., vol. 29, no. 7, pp. 791–794, Jul. 2008.

- [9] A. V-Y. Thean et al., "Vertical device architecture for 5 nm and beyond: Dec vice circuit implications," in Proc. Symp. VLSI Technol. (VLSI Technology), Jun. 2015, pp. T26–T27.

- [10] M. Shrivastava et al., "Physical insight toward heat transport and an improve d electrothermal modeling framework for FinFET architectures," IEEE Trans. Elect ron Devices, vol. 59, no. 5, pp. 1353–1363, May 2012.

- [11] E. Pop and K. E. Goodson, "Thermal phenomena in nanoscale transis tors," in Proc. 9th Intersoc. Conf. Thermal Thermomechan. Phenomena Electron. Syst., Jun. 2004, pp. 1–7. [12] I, Myeong, D. Son, H. Kim, M. Kang, and H. Shin, "Analysis of self-heating effects on vertical FET according to shallow trench isolation," Solid-State Electron., vol. 137, pp. 123–127, Nov. 2017.

- [13] W. Ahn, H. Jiang, S. H. Shin, and M. A. Alam, "A novel syn thesis of Rent's rule and effective-media theory predicts FEOL and BEOL reliability of self-heated ICs," in IEDM Tech. Dig., Dec. 2017, pp. 7.1.1–7.1.4.

# Chapter 2

# Thermal-Aware Shallow Trench Isolation Design Optimization for Minimizing $I_{\text{off}}$ in Various Sub-10-nm 3-D Transistor

## 2.1 Introduction

In this chapter, based on ITRS 2015, Bulk/SOI FinFETs that can be used up to 7-nm node and VFETs that appeared as new candidates in/under 5-nm node are made through Sentaurus, a TCAD simulator. we have studied the method of decreasing the maximum lattice temperature ( $T_{L,max}$ ) through shallow trench isolation (STI) engineering considering  $I_{OFF}$  in each structure and also the improvement of HCI/BTI lifetime based on temperature reduction by STI engineering solution in each structure.

## 2.2 Device Structure and Simulation Conditions

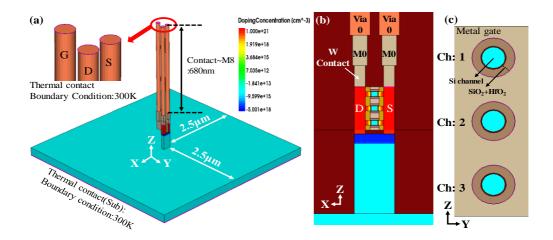

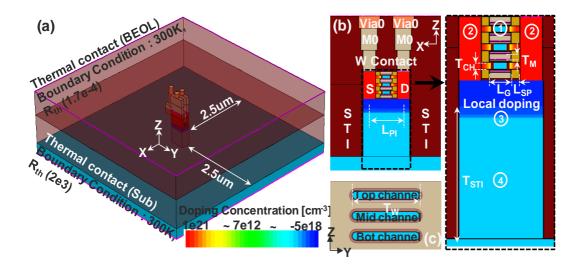

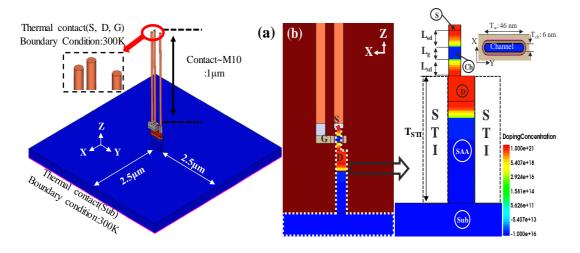

The Bulk/SOI FinFET and VFET structures used in this paper were made using Synopsys Sentaurus [14], a TCAD simulator. Detailed specifications of structures refer to

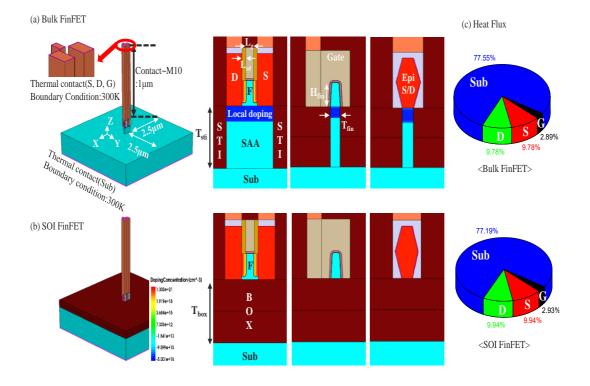

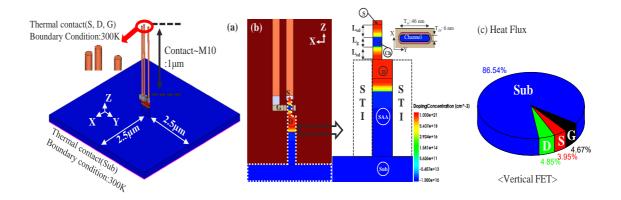

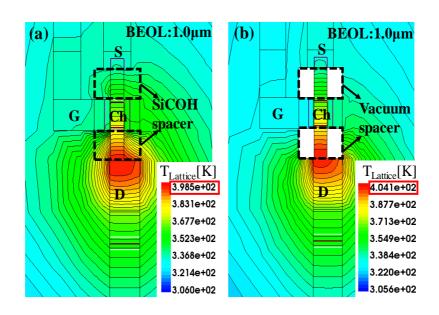

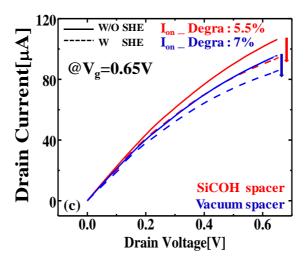

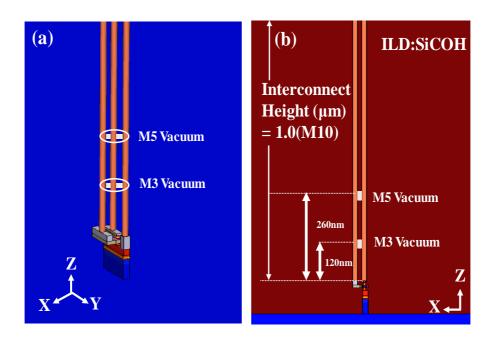

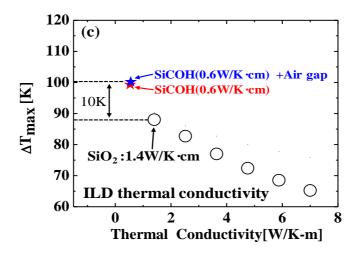

the values of 5-/7-nm node presented in ITRS [15]. Fig. 2.1 shows the entire structure and cross-sectional views of the FinFET. As shown in Fig. 2.1 (a), there is a heavily doped local doping area under source (S)/drain (D) region to improve the I<sub>OFF</sub> characteristic in the bulk FinFET. The shape of S/D bulk is made considering that the growth rate varies depending on the lattice direction when growing epitaxially. Fig. 2.1 (b) shows the structure of the SOI FinFET. SOI FinFET is all the same except that the STI-all-around region of the Bulk FinFET is replaced with an insulator. The following is an introduction to the structure of a VFET. Fig. 2.2 shows the entire structure and cross-sectional views of the VFET. Fig. 2.2 (a) shows the entire structure of a VFET and includes back end of line (BEOL) and large substrate, just like the entire structure of a FinFET. As mentioned in Section introduction, the channel is vertically oriented and the S/D is made up and down the channel. The shape of the S/D is made into a rectangular shape different from that of the FinFET by referring to the papers [6]–[9] dealing with the fabrication of the VFET. In addition, to improve the performance (IoN) of the nanowire channel VFET, a VFET with a sheet-shaped channel can be seen in the cross section. The structure specification such as channel thickness (T<sub>fin</sub>/T<sub>ch</sub>), effective oxide thickness, STI/BOX thickness (Tsti/Tbox), doping concentration, and thermal conductivity of each region is shown in Table 2.1. TCAD tool has a function to tune the thermal conductivity and dielectric constant value of material inside. The thermal conductivity and dielectric constant value are added to the parameter part to account for the difference of the STI material. Values for each substance are obtained through various documents [10]–[12].

**Fig. 2.1** Entire structure and cross sectional views (a)Bulk and (b)SOI FinFETs. In the Bulk FinFETs, there is a heavily doped local doping area in order to improve characteristics of Ioff. Thermal contacts are set on the Source, Drain, Gate, and Substrate, and thermal boundary conditions (temperature: 300K) are set for each contact. In case of Back End of Line (BEOL), it is made up to 1 m (M10 layer height) refer to specification of Table 2.2. (c) For Bulk/SOI FinFET, the heat dissipation from hot spot to thermal contacts is shown by heat flux.

**Fig. 2.2** (a) Entire structure of VFET and (b) cross sectional views of VFET. In the Vertical FETs, the channel is a vertically oriented structure. Thermal contacts, thermal boundary conditions and BEOL specification is set the same as those of the FinFET. (c) For VFET, the heat dissipation from hot spot to thermal contacts is shown by heat flux.

Table 2.1 Thermal and structural specifications.

|                                   | Category                        | F  | inFET              |

|-----------------------------------|---------------------------------|----|--------------------|

|                                   | $V_{DD}(V)$                     |    | 0.7                |

|                                   | EOT (nm)                        |    | 0.7                |

| S                                 | /D Doping (cm <sup>-3</sup> )   | 1  | x 10 <sup>21</sup> |

| Cha                               | nnel Doping (cm <sup>-3</sup> ) | 1  | x 10 <sup>16</sup> |

| L                                 | ocal doping(cm <sup>-3</sup> )  | 5  | x 10 <sup>18</sup> |

|                                   | $T_{fin}/L_g$ (nm)              |    | 7/14               |

|                                   | $H_{fin}/L_{sd}$ (nm)           |    | 40/6               |

|                                   | $T_{sti}/T_{box}(nm)$           |    | 100                |

| Thermal Conductivity[Ref] (W/m/K) |                                 |    |                    |

|                                   | Source/Drain [S, D]             |    | 16                 |

| Fin [F]                           |                                 | 19 |                    |

| Si STI-all-around [SAA]           |                                 | 18 |                    |

| Substrate [Sub]                   |                                 |    | 148                |

|                                    | Category                       | V   | FET       |

|------------------------------------|--------------------------------|-----|-----------|

|                                    | $V_{DD}(V)$                    | (   | ).65      |

|                                    | EOT (nm)                       |     | 0.7       |

| S/I                                | D Doping (cm <sup>-3</sup> )   | 1 x | $10^{21}$ |

| Chan                               | nel Doping (cm <sup>-3</sup> ) | 1 x | $10^{16}$ |

|                                    | T <sub>ch</sub> (nm)           |     | 6         |

|                                    | $W_{fin}$ (nm)                 |     | 46        |

|                                    | $L_{g}$ (nm)                   | 1   | 2.2       |

|                                    | L <sub>sd</sub> (nm)           | 1   | 11.9      |

| Thermal Conductivity [Ref] (W/m/K) |                                |     | Ref]      |

|                                    | Source [S]                     |     | 3.8       |

|                                    | Channel [Ch]                   |     | 8.9       |

| Si                                 | Drain [D]                      |     | 5.6       |

|                                    | STI-all-around [SAA]           |     | 18        |

|                                    | Substrate [Sub]                |     | 148       |

It is underestimated to verify  $T_{Lattice}$  by SHE of single device except BEOL str ucture. The reason for this is that in the case of modern devices, the BEOL form s up to the maximum M10 layer, which not only lengthens the path of heat dissi pation to the BEOL but also the dielectric surrounding the metal line has a low t hermal conductivity. In order to consider contributing the increase of  $T_{Lattice}$  of BE -OL, the BEOL height is briefly calculated by referring to the announcements of companies and several papers [16], [17]. Table 2.2 shows the thickness of Via/Me tal for each layer. It becomes approximately 1  $\mu$ m when it is raised up to M10 1 ayer. This height can also be seen in the entire structures of Fig.2.1 and 2.2.

Table 2.2 BEOL specifications.

| Category                           | Metal<br>Thickness(nm) |

|------------------------------------|------------------------|

| W Contact/M0                       | 27/38                  |

| M1~M3 (1xPitch)<br>V0~V3 (1xPitch) | 20                     |

| M4(1.4xPitch)<br>V4(1.4xPitch)     | 28                     |

| M5(2xPitch)<br>V5(2xPitch)         | 40                     |

| M6(3xPitch)<br>V6(3xPitch)         | 60                     |

| M7~M8(4xPitch)<br>V7~V8(4xPitch)   | 80                     |

| M9~M10(4xPitch)<br>V9~V10(4xPitch) | 80                     |

Several factors have been taken into account for thermal analysis of the device. The thermal contact is set in the area where the heat is dissipated. In [18] and [19] dealing with SHE, source, drain, gate, and substrate are set to thermal contact. In addition, a boundary condition is required when calculating the temperature in the device, and accordingly, we have specified room temperature (300 K) for the thermal contacts. We include equantumPotential and emobility (thinlayer) in the physics to account for the quantum effect. In order to improve the electrical accuracy, the calibration was carried out in the same way as in [23]. Finally, in the case of the hydrodynamic model, the change of device temperature is directly taken into account in the current and can also improve the accuracy of the simulation. For this reason, the hydrodynamic model is used for the overall SHE analysis.

## 2.3 Results and Discussion

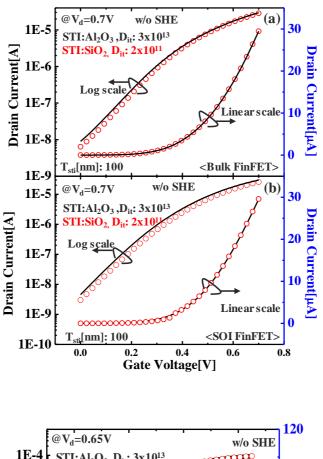

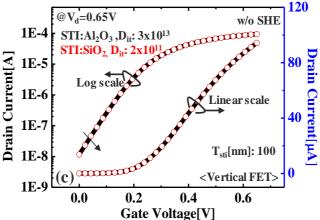

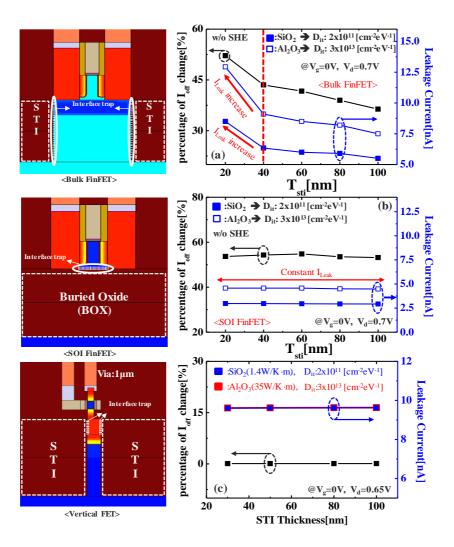

Depending on the material filling the STI, the interface trap density ( $D_{it}$ ) of the Si/oxide interface is different. In the case of STI filled with a commonly used SiO<sub>2</sub>,  $D_{it}$  has a  $2 \times 10^{11}$  [cm<sup>-2</sup> · eV<sup>-1</sup>], whereas in the case of STI filled with Al2O3, Dit increases to  $3 \times 10^{13}$  [cm<sup>-2</sup> · eV<sup>-1</sup>] referring to the paper [20]. Fig. 2.3 shows the  $I_d$ – $V_g$  curves that reflect  $D_{it}$  according to STI materials in sub-10-nm devices. Depending on the material constituting the STI, it can be seen that the off regions are different. There is little difference in the on regions, which can be explained by the fact that the capacitance according to the material in Fig. 2.4 has almost the same. The SHE analysis of this paper proceeded at the current level in Fig. 2.3.

Fig. 2.3 (a) Fig. 3.  $I_d$ - $V_g$  curves according to STI materials (SiO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub>). (a) Bulk FinFET (b) SOI FinFET (c) VFET.

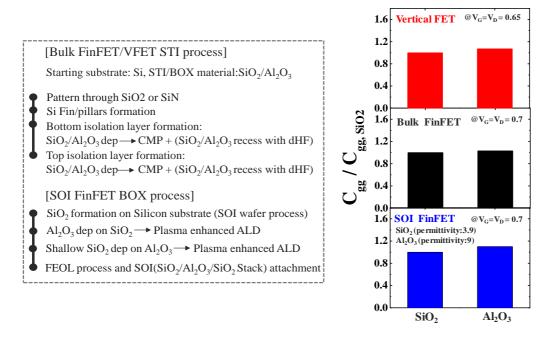

Fig. 2.4 (a) Schematics of the STI process flow in sub -10nm devices and comparison of capacitance according to STI material.

Fig. 2.5 shows a detailed analysis of the OFF current ( $I_{OFF}$ , condition,  $V_g = 0$  V,  $V_d = V_{DD}$ ) characteristics reflecting the difference in  $D_{it}$  according to the STI material. As shown in Fig. 2.5 (a), in the Bulk FinFET, not only  $I_{OFF}$  changes according to the STI thickness but also the STI made of  $Al_2O_3$  having a higher  $D_{it}$  than  $SiO_2$  has a larger  $I_{OFF}$  value. In addition, the  $I_{OFF}$  tends to increase sharply as the thickness of the STI becomes less than 40 nm. As shown in Fig. 2.5 (b), there is no  $I_{OFF}$  tendency depending on the STI thickness because the bottom leakage path is blocked by the BOX and only the  $I_{OFF}$  difference due to  $D_{it}$  changes according to BOX material. As in the case of Bulk FinFET, STI made of  $Al_2O_3$  has a larger  $I_{OFF}$  value. Finally, in the case of VFETs, it can be confirmed that there is no  $I_{OFF}$  tendency depending on the STI material and thickness. As mentioned in [12],

the current direction of the VFET is different from that of the Lateral FET, and therefore, the  $I_{\text{OFF}}$  characteristics are not affected by the STI specification and properties in the VFET.

Fig. 2.5  $I_{off}$  characteristics according to STI specification and properties. (a)Bulk FinFET, (b)SOI FinFET and (c)VFET. The Bulk FinFET is all affected by specification and properties of the STI and the SOI FinFET is only affected by the properties of the STI. VFET is not affected by STI.

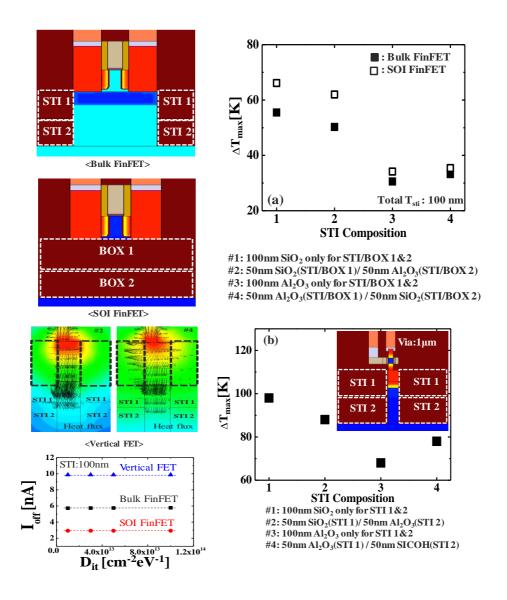

In this section, we analyzed the thermal characteristics according to the difference in thermal conductivity (k) between  $Al_2O_3$  (k: 35 W ·m<sup>-1</sup> · K<sup>-1</sup>) and  $SiO_2$ (k: 1. 4 W· m<sup>-1</sup> · K-1) used in STI, and then analyzed the SHE relaxation in each device through STI composition considering I<sub>OFF</sub>. SiO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub> stack are widely used in the semiconductor industry from the gate-stack of logic device to the oxide-nitride-oxide layer of NAND Flash [24]-[26]. Nevertheless, our group has again analyzed whether the SiO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub> interfacial characteristics (D<sub>ii</sub>: 1e13–1e14 [24]) are causing device performance problems. As shown in the bottom left of Fig. 2.6 (b), there was no performance (I<sub>OFF</sub>) change. Fig. 2.6 also shows the thermal characteristics, which show the max lattice temperature (T<sub>L,max</sub>) according to the STI composition [21]. Bulk/SOI FinFET and VFET both show the same temperature tendency according to the STI composition. In the case of #3, T<sub>L,max</sub> is decreased much compared to #1, because the Al<sub>2</sub>O<sub>3</sub> with high thermal conductivity efficiently dissipates heat to the substrate. In addition, the difference between #2 and #4 is that the material order in the composition is changed. The reason why the T<sub>L,max</sub> of #4 is lower than that of #2 is that the heat flux to the STI region becomes larger as the material having a higher thermal conductivity is located near the hotspot as shown in the top left of Fig. 2.6 (b).

Fig. 2.6  $T_{L,max}$  change according to STI composition. (a) Bulk/SOI FinFET and (b) VFET. As the material with high thermal conductivity properties is located near the hot spot,  $T_{L,max}$  decreases.

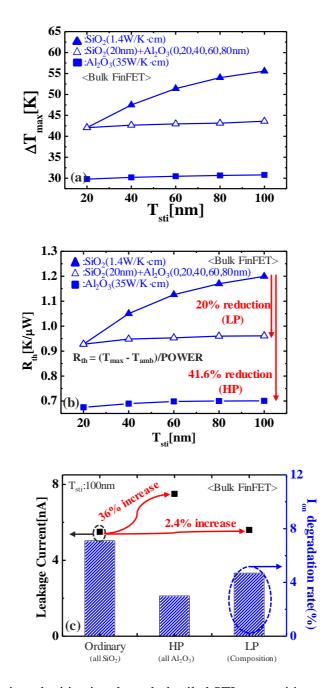

Now, mitigation of SHE through the STI composition considering I<sub>OFF</sub> in each device is discussed. As shown in Fig. 2.7 (a), comparing the T<sub>L,max</sub> for the three cases in a Bulk FinFET. The first is the case where the STI is made only with SiO<sub>2</sub>. The second is the case where the upper part (20 nm) of the STI is made of SiO<sub>2</sub> and the lower part (80 nm) is made of Al<sub>2</sub>O<sub>3</sub> based on the I<sub>OFF</sub> analysis of the Bulk FinFET in the front part. The third case is that the entire STI is made of Al<sub>2</sub>O<sub>3</sub>. When the STI thickness is 100 nm, TL,max is reduced by 13 K in SiO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub> composition compared to using only SiO<sub>2</sub>. When STI is made entirely of Al<sub>2</sub>O<sub>3</sub>, T<sub>L,max</sub> decrease to 25 K. Fig. 2.7 (b) shows that R<sub>th</sub> is reduced by 20% in the case of SiO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub> composition and about 42% in the case of only Al<sub>2</sub>O<sub>3</sub>. Comprehensively, I<sub>OFF</sub> and I<sub>ON</sub> degradation rate according to T<sub>L,max</sub> for SiO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub> composition and only Al<sub>2</sub>O<sub>3</sub> are compared with ordinary case. As can be seen in Fig. 2.7(c), when STI only made of Al<sub>2</sub>O<sub>3</sub> with interfacial properties, I<sub>OFF</sub> is increased by 36%, but the I<sub>ON</sub> degradation rate is reduced from 7.8% to 3% compared to ordinary case. In the case of SiO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub> composition considering I<sub>OFF</sub> characteristic, the I<sub>OFF</sub> is slightly increased to 2.4%, and the  $I_{ON}$  degradation rate is reduced from 7.8% to about 5% compared to ordinary case. Therefore, in the case of a high-performance (HP) device which focuses on the I<sub>ON</sub> characteristics rather than I<sub>OFF</sub>, it is expected that using only Al<sub>2</sub>O<sub>3</sub> will minimize the I<sub>ON</sub> degradation due to the SHE. Next, in the case of a low-power (LP) device in which the I<sub>OFF</sub> characteristics is important, it is expected that the SiO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub> composition can be used to maintain I<sub>OFF</sub> while improving the I<sub>ON</sub> characteristic.

Fig. 2.7 SHE analysis and mitigation through detailed STI composition considering  $I_{\text{off}}$  in Bulk FinFET. (a)  $T_{L,\text{max}}$  change, (b)  $R_{th}$  change and (c)  $I_{\text{on}}$  degradation rate due to  $T_{L,\text{max}}$  change and leakage current ( $I_{\text{off}}$ ) change according to STI composition.

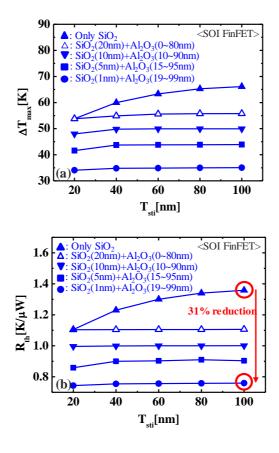

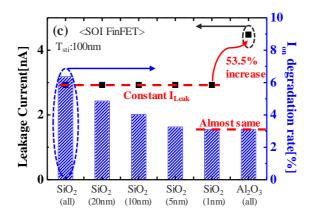

In the case of SOI FinFET,  $I_{OFF}$  changed only by the number of  $D_{it}$  at the BOX/Si interface. Therefore, the analysis is carried out by making the upper part of the BOX with  $SiO_2$  and the lower part with  $Al_2O_3$ . As can be seen in Fig. 2.8 (a), when 1 nm of thin  $SiO_2$  is laid on the interface and the rest (99 nm) is made of  $Al_2O_3$ ,  $T_{L,max}$  is reduced by about 32 K compared to all  $SiO_2$ . Similarly, Fig. 2.8 (b) shows that  $R_{th}$  is reduced by 31%. Fig. 2.8 (c) shows that the BOX made of all  $Al_2O_3$  improves the temperature characteristics and hence the  $I_{ON}$  degradation rate is decreased, but  $I_{OFF}$  is increased by 53.5% compared to all  $SiO_2$ . On the other hand, when the BOX is composed of 1 nm (at interface)  $SiO_2$  and 99 nm (rest)  $Al_2O_3$ ,  $I_{OFF}$  can be kept at almost the same as that of all  $SiO_2$  while keeping  $I_{ON}$  as good as all  $Al_2O_3$ .

Fig. 2.8 SHE analysis and mitigation through detailed STI composition considering  $I_{\rm off}$  in SOI FinFET. (a)  $T_{L,max}$  change, (b)  $R_{th}$  change and (c)  $I_{on}$  degradation rate due to  $T_{L,max}$  change and leakage current ( $I_{\rm off}$ ) change according to STI composition.

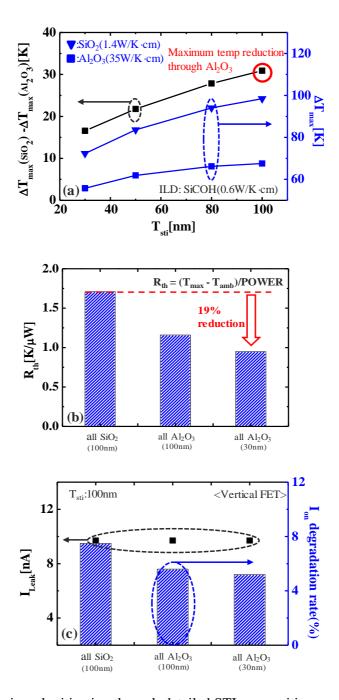

In the case of VFET, there is no  $I_{OFF}$  change depending on the thickness and kind of material of STI due to the nature of the structure. Fig. 2.9(a) shows  $T_{L,max}$  depending on the STI thickness and the material constituting the STI. In VFET, it can be seen that  $T_{L,max}$  is reduced by 30 K compared to all SiO<sub>2</sub> (100 nm) when STI is made with all Al<sub>2</sub>O<sub>3</sub> (100 nm). In addition, since the thickness of STI does not affect  $I_{OFF}$ , if STI is made of Al<sub>2</sub>O<sub>3</sub> with a thickness of 30 nm which can isolate drain region (20 nm) of VFET, it is possible to reduce  $T_{L,max}$  by 42 K compared to all SiO<sub>2</sub>(100 nm). Fig. 2.9(b) shows the change in  $R_{th}$ . When the STI is made of all Al<sub>2</sub>O<sub>3</sub> (30 nm), it can be seen that  $R_{th}$  is reduced up to 19% compared to all SiO<sub>2</sub>(100 nm). As shown in Fig. 2.9(c), there is no change in  $I_{OFF}$  depending on the material and thickness of STI. Therefore, when STI is made of all Al<sub>2</sub>O<sub>3</sub>(30nm), the  $I_{ON}$  degradation rate is changed from 8% to 5%, while  $I_{OFF}$  is kept equal to all SiO<sub>2</sub>(100 nm).

Fig. 2.9 SHE analysis and mitigation through detailed STI composition considering  $I_{\text{off}}$  in VFET. (a)  $T_{L,\text{max}}$  change, (b)  $R_{\text{th}}$  change and (c)  $I_{\text{on}}$  degradation rate due to  $T_{L,\text{max}}$  change and leakage current ( $I_{\text{off}}$ ) change according to STI composition.

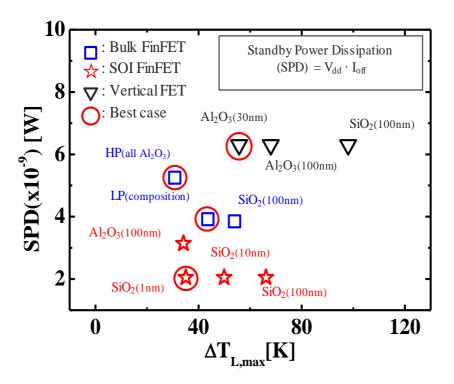

Finally, to organize at a glance, we compiled the best case of Bulk/SOI FinFET and VFET by comparing standby power dissipation (SPD =  $V_{dd} \cdot I_{OFF}$ ) and  $T_{L,max}$  change according to STI composition. As can be seen in Fig. 2.10, in the case of Bulk FinFET, there are two best cases: HP can minimize  $T_{L,max}$  while increasing SPD, and LP can lower  $T_{L,max}$  a little while keeping the SPD almost the same. In the case of SOI FinFET and VFET, all devices have the best case to minimize  $T_{L,max}$  while maintaining the same SPD, respectively

Fig. 2.10 Comparison of standby power dissipation and  $T_{L,max}$  according to STI composition in Bulk/SOI FinFET and VFET.

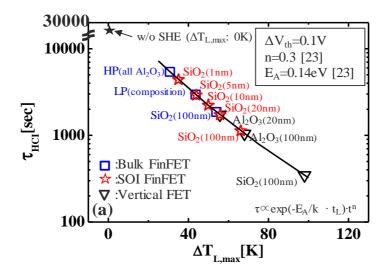

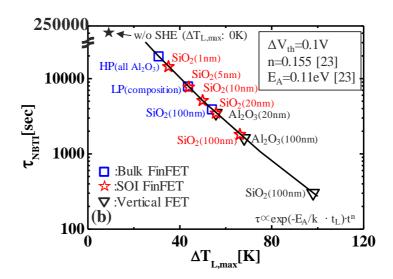

As mentioned in Section 2.3, when optimization of STI composition is performed considering  $I_{OFF}$  in Bulk/SOI FinFET and VFET, respectively,  $T_{L,max}$  decreases compared to ordinary STI (only SiO<sub>2</sub>). Therefore, in this section, we study the change of HCI/BTI lifetime of devices according to  $T_{L,max}$  change. The HCI/BTI lifetime of devices can be predicted through (1) with  $E_a$  and n [22]. Lifetime is defined as the time to reach  $\Delta V_{th} \sim 0.1$  V. We compare three lifetimes:  $\tau_0$ , assuming no temperature rise due to SHE, i.e., T = 300 K;  $\tau_{ordinary}$ , for STI made only of SiO<sub>2</sub>; and  $\tau$ , for STI made with composition in each device

$$\Delta V th \sim exp(-E_A/k \cdot T_{L,max}) \times t^n.$$

(1)

Fig. 2. 11 (a) and (b) shows a comparison of HCI and BTI lifetime according to  $T_{L,max}$  using (1). The black star point represents the HCI/BTI lifetime when  $\Delta T_{L,max}$  is 0 K (i.e., without SHE). In addition, it is also confirmed that the lifetime is improved due to  $\Delta T_{L,max}$  relaxation through STI engineering compared to the case of ordinary STI in Bulk/SOI FinFET and VFET.

Fig. 2. 11. A comparison of (a) HCI, and (b) BTI, lifetime as a function of  $\Delta T_{L,max}$ . The  $T_{L,max}$  is determined by SHE with various STI composition.

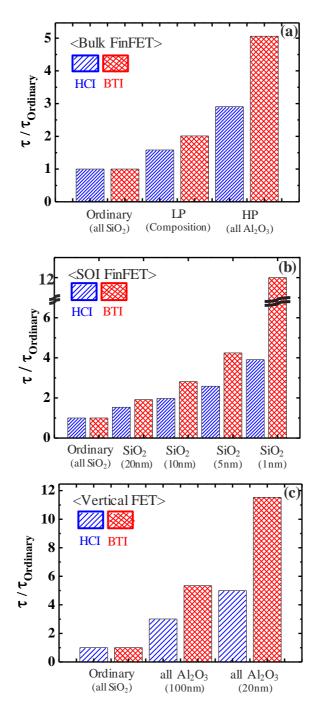

Fig. 2.12 shows the quantitative improvement of the HCI/BTI lifetime when STI engineering is applied compared to ordinary STI in each device. As shown in Fig. 2.12(a), in the case of Bulk FinFET, the HCI lifetime increases up to  $3\times$  and the BTI lifetime increases up to  $5\times$ . As shown in Fig. 2.12(b), when BOX is composed of SiO<sub>2</sub>(1 nm) and Al<sub>2</sub>O<sub>3</sub>(99 nm), the HCI lifetime increases up to  $4\times$  and the BTI lifetime increase up to  $12\times$ . Finally, as shown in Fig. 2.12(c), when the STI is made only with Al<sub>2</sub>O<sub>3</sub>(30 nm), the HCI lifetime increases about  $5\times$  and the BTI lifetime increases about  $11\times$ . For all structures, the HCI/BTI lifetime can be significantly enhanced through STI engineering to improve thermal properties of devices and minimize I<sub>OFF</sub> degradation.

Fig. 2.12 Comparison of life time improvement in STI engineering case compared to Ordinary STI case. (a)Bulk FinFET, (b)SOI FinFET and (c) VFET.

## 2.4 Summary

In this chapter, we have analyzed SHEs in both FinFET (Bulk/SOI) and VFET, which are presented as potential candidates in 7- and 5-nm node, respectively. More specifically, we have studied the lattice temperature relaxation using high thermal conductivity STI materials while considering the I<sub>OFF</sub> characteristic due to the difference in D<sub>it</sub> according to STI materials. In the case of Bulk FinFET, using all Al<sub>2</sub>O<sub>3</sub> compared to using all SiO<sub>2</sub>, reduces I<sub>ON</sub> degradation rate from 7.8% to 3%, while I<sub>OFF</sub> increases by 36%. Therefore, using all Al<sub>2</sub>O<sub>3</sub> for the STI material could be presented as an HP solution for Bulk FinFET. In the case of using SiO<sub>2</sub> for upper 20 nm and Al<sub>2</sub>O<sub>3</sub> for lower 80 nm, I<sub>ON</sub> degradation rate reduces from 7.8% to 5%, while I<sub>OFF</sub> negligibly increases by 2.4%. Therefore, using SiO<sub>2</sub> for upper 20 nm and Al<sub>2</sub>O<sub>3</sub> for lower 80 nm could be presented as LP solution for Bulk FinFET. In the case of SOI FinFET, when using all Al<sub>2</sub>O<sub>3</sub> instead of all SiO<sub>2</sub>, I<sub>ON</sub> degradation rate reduces from 7% to 3% but I<sub>OFF</sub> increases by 53.5%. However, when using our STI design of SiO<sub>2</sub> for upper 1 nm and Al<sub>2</sub>O<sub>3</sub> for lower 99 nm, Ion characteristic is kept similar to that of all Al<sub>2</sub>O<sub>3</sub>, while keeping the same I<sub>OFF</sub> value as that of SiO<sub>2</sub>. Finally, in the case of VFET, our investigation shows that using all 30-nm Al<sub>2</sub>O<sub>3</sub> is optimal solution, compared to using 100 nm all Al<sub>2</sub>O<sub>3</sub> or all SiO<sub>2</sub> for STI composition, because while I<sub>OFF</sub> is independent of STI material and thickness for VFET, I<sub>ON</sub> degradation reduces from 8% to 5% when using 30 nm all Al<sub>2</sub>O<sub>3</sub> compared to others. We also estimated the improvement of HCI/BTI lifetime due to T<sub>L,max</sub> relaxation through STI engineering of each device. Depending on the device, the HCI lifetime can be increased from  $1.5 \times$  to  $5 \times$ , and BTI can be increased from  $2 \times$  to  $12 \times$ .

#### References

- [1] K. J. Kuhn, "CMOS scaling for the 22 nm node and beyond: Device physics and technology," in Proc. Int. Symp. VLSI Technol., Syst. Appl., Apr. 2011, pp. 1–2.

- [2] M. Ieong, B. Doris, J. Kedzierski, K. Rim, and M. Yang, "Silicon device scaling to the sub-10-nm regime," Science, vol. 306, no. 5704, pp. 2057–2060, Dec. 2004.

- [3] D. Yakimets et al., "Vertical GAAFETs for the ultimate CMOS scaling," IEEE Trans. Electron Devices, vol. 62, no. 5, pp. 1433–1439, May 2015.

- [4] N. Loubet et al., "Stacked nanosheet gate-all-around transistor to enable scaling beyond FinFET," in Proc. Symp. VLSI Technol., Jun. 2017, pp. T230–T231.

- [5] T. H. Bao et al., "Circuit and process co-design with vertical gate-all around nanowire FET technology to extend CMOS scaling for 5 nm and beyond technologies," in Proc. 44th Eur. Solid State Device Res. Conf. (ESSDERC), Sep. 2014, pp. 102–105.

- [6] M. Sharma, S. Maheshwaram, O. Prakash, A. Bulusu, A. K. Saxena, and S. K. Manhas, "Compact model for vertical silicon nanowire based device simulation and circuit design," in Proc. IEEE ISOCC, Nov. 2015, pp. 107–108.

- [7] S. Maheshwaram, S. K. Manhas, G. Kaushal, B. Anand, and N. Singh, "Vertical silicon nanowire gate-all-around field effect transistor based nanoscale CMOS," IEEE Electron Device Lett., vol. 32, no. 8, pp. 1011–1013, Aug. 2011.

- [8] B. Yang, K. D. Buddharaju, S. H. G. Teo, N. Singh, G. Q. Lo, and D. L. Kwong, "Vertical silicon-nanowire formation and gate-all-around MOSFET," IEEE Electron Device Lett., vol. 29, no. 7, pp. 791–794, Jul. 2008.

- [9] A. V-Y. Thean et al., "Vertical device architecture for 5 nm and beyond: Decvice

- circuit implications," in Proc. Symp. VLSI Technol. (VLSI Technology), Jun. 2015, pp. T26–T27.

- [10] M. Shrivastava et al., "Physical insight toward heat transport and an improved electrothermal modeling framework for FinFET architectures," IEEE Trans. Electron Devices, vol. 59, no. 5, pp. 1353–1363, May 2012.

- [11] E. Pop and K. E. Goodson, "Thermal phenomena in nanoscale transis tors," in Proc. 9th Intersoc. Conf. Thermal Thermomechan. Phenomena Electron. Syst., Jun. 2004, pp. 1–7.

- [12] I, Myeong, D. Son, H. Kim, M. Kang, and H. Shin, "Analysis of self-heating effects on vertical FET according to shallow trench isolation," Solid-State Electron., vol. 137, pp. 123–127, Nov. 2017.

- [13] W. Ahn, H. Jiang, S. H. Shin, and M. A. Alam, "A novel syn thesis of Rent's rule and effective-media theory predicts FEOL and BEOL reliability of self-heated ICs," in IEDM Tech. Dig., Dec. 2017, pp. 7.1.1–7.1.4.

- [14] Version K-2015.06-SP1. Synopsys Inc., Mountain View, CA, USA; 2017.

- [15] (2015). The International Technology Roadmap for Semiconductors (ITRS).

- [16] K. Fischer et al., "Low-k interconnect stack with multi-layer air gap and tri-metal-insulator-metal capacitors for 14 nm high volume manufacturing," in Proc. IEEE IITC/MAM, May 2015, pp. 5–8.

- [17] C. Auth et al., "A 22 nm high performance and low-power CMOS technology featuring fully-depleted tri-gate transistors, self-aligned contacts and high density MIM capacitors," in Proc. Symp. VLSI Tech nol. (VLSIT), Jun. 2012, pp. 131–132.

- [18] T. Takahashi, T. Matsuki, T. Shinada, Y. Inoue, and K. Uchida, "Comparison of self-heating effect (SHE) in short-channel bulk and ultrathin BOX SOI MOSFETs: Impacts of doped well, ambient temperature, and SOI/BOX thicknesses on SHE," in IEDM Tech. Dig., Dec. 2013, pp. 7.4.1–7.4.4.

- [19] T. Takahashi, S. Oda, and K. Uchida, "Methodology for evaluating operation temperatures of fin-type field-effect transistors connected by interconnect wires," Proc. Jpn. J. Appl. Phys., vol. 52, no. 6R, p. 064203, May 2013.

- [20] J. Benick et al., "Effect of a post-deposition anneal on Al2O3/Si inter face properties," in Proc. 35th IEEE Photovolt. Spec. Conf., Jun. 2010, pp. 891–896.

- [21] S. H. Shin, S.-H. Kim, S. Kim, H. Wu, P. D. Ye, and M. A. Alam, "Substrate and layout engineering to suppress self-heating in floating body transistors," in IEDM Tech. Dig., Dec. 2016, pp. 15.7.1–15.7.4.

- [22] W. Ahn, H. Jiang, S. H. Shin, M. A. Alam, "A novel synthesis of Rent's rule and effective-media theory predicts FEOL and BEOL reliability of self-heated ICs," in IEDM Tech. Dig., Dec. 2016, pp. 7.1.1–7.1.4.

- [23] D. Son, I. Myeong, H. Kim, M. Kang, J. Jeon, and H. Shin, "Analysis of electrothermal characteristics of GAA vertical nanoplate-shaped FETs," IEEE Trans. Electron Devices, vol. 65, no. 7, pp. 3061–3064, Jul. 2018.

- [24] S. Kar, "Selected success stories from twenty years of high-k gate dielectric research," ECS Trans., vol. 75, no. 5, pp. 245–261, Sep. 2016.

- [25] M. Putkonen et al., "Low-temperature atomic layer deposition of SiO2/Al2O3 multilayer structures constructed on self-standing films of cellulose nanofibrils," Philos.

Trans. Roy. Soc. London A, Math. Phys. Sci., vol. 376, no. 2112, p. 20170037, Feb. 2018. [26] P. M. Jordan, D. K. Simon, T. Mikolajick, and I. Dirnstorfer, "Trapped charge densities in Al2O3-based silicon surface passivation layers," J. Appl. Phys., vol. 119, no. 21, p. 215306, May 2016.

# Chapter 3

# Analysis of Self Heating Effect in DC/AC

## Mode in Multi-channel GAA-Field Effect

## **Transistor**

### 3.1 Introduction

Continuous downscaling of semiconductor devices required the contacted gate pitch (CGP) to be reduced as well. This resulted in reducing the gate length. However, when the gate length decreases, it is difficult for transistors to scale down while maintaining the electrostatic characteristics. As a solution to this problem, 3-D devices such as a fin field effect transistors (FETs) or gate-all-around (GAA) nanowire-FETs have been introduced, which improve the controllability of a gate significantly [1]–[3]. By using such multi-gate FETs (MGFETs), downscaling of devices became feasible. However, in MGFETs, especially in nanowire-FETs, a gate dielectric with low thermal conductivity surrounds the channel [4], making it difficult to dissipate heat from the hot spot in the channel. In addition, due to the ultra-scale dimension, thermal conductivity is reduced, and then the

heat transfer efficiency of the nanowire-FET is also decreased [5]. As a result, the ON-current (I<sub>on</sub>) decreases and causes reliability problems due to the increased temperature caused by self-heating effect (SHE). Therefore, thermal issues in nanowire device structures are expected to be continuously addressed in the future. In this chapter, analysis of SHE in a nanowire-FET is conducted in the dc/ac mode.

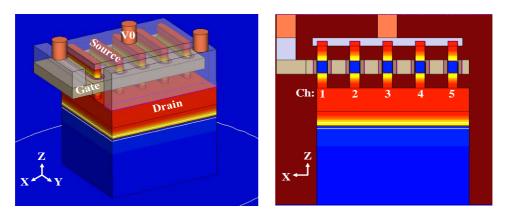

### 3.2 Multi-Channel Nanowire FET and Back End Of line

The multi-channel nanowire-FET structures used in this chapter were simulated using a Synopsys Sentaurus [6], a TCAD simulator. For detailed specifications of structures, refer to the values of the 5-/7-nm node presented in the International Technology Road Map for Semiconductor (ITRS) [7]. Fig. 3.1 shows the entire structures and cross-sectional views of a multi-channel nanowire-FET created by Synopsys simulation tools for the self-heating study. Fig. 3.1(a) shows a 3-D nanowire-FET structure. Fig. 3.1(b) and (c) shows the XZ plane of the 3-D nanowire-FET and the YZ plane of the channel region, respectively. Table 3.1 shows the device specifications with referenced to ITRS 2015. The supply voltage to the device is 0.75 V and the effective oxide thickness (EOT) is 1 nm. The source/drain doping concentration is  $1 \times 10^{21}$  cm<sup>-3</sup>, the channel doping is  $10^{15}$  cm<sup>-3</sup>, and the local doping for reducing the leakage current is  $5 \times 10^{18}$  cm<sup>-3</sup>. The channel thickness ( $T_{ch}$ ) is 6 nm and the STI thickness for isolation is 100 nm. The lengths of the gate ( $L_g$ ) and channel extensions ( $L_{SD}$ ) are 10 and 5 nm, respectively. Fig. 3.1(a) also includes a back end of line (BEOL) metal; the height of the M8 layer is 680 nm and the height is calculated from [18, Table II] based on the short course data on IEDM (2016)

and various articles [10]-[13].

Fig. 3.1 (a) Three-dimensional nanowire FET structure with thermal contact, boundary condition and BEOL. (b) X-Z plane of three-dimensional nanowire FET. (c) Y-Z plane of mulita-channel region.

Table 3.1

Electrical / Thermal specification of Nanowire-FET

| Category                           | NWFET                | Th                           |                 | (II/IIZ) |

|------------------------------------|----------------------|------------------------------|-----------------|----------|

| V <sub>DD</sub> (V)                | 0.75                 | Thermal Conductivity (W/m/K) |                 |          |

| EOT (nm)                           | 1                    |                              | ① Source/Drain  | 7.9      |

| S/D Doping (cm <sup>-3</sup> )     | 1 x 10 <sup>21</sup> |                              |                 |          |

| Channel Doping (cm <sup>-3</sup> ) | 1 x 10 <sup>15</sup> |                              | ② Channel       | 8.9      |

| Local Doping(cm <sup>-3</sup> )    | 5 x 10 <sup>18</sup> |                              | ③Local doping   | 24.6     |

| T <sub>ch</sub> (nm)               | 6                    | Si                           |                 |          |

| T <sub>STI</sub> (nm)              | 100                  |                              | 4STI-all-around | 25       |

| L <sub>g</sub> (nm)                | 10                   |                              |                 |          |

| L <sub>SD</sub> (nm)               | 5                    |                              | ⑤ Substrate     | 148      |

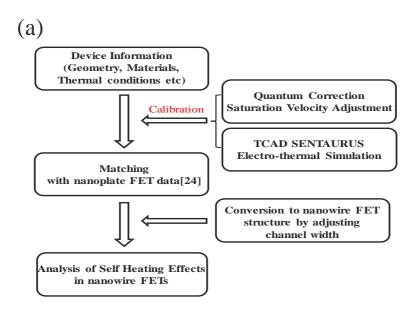

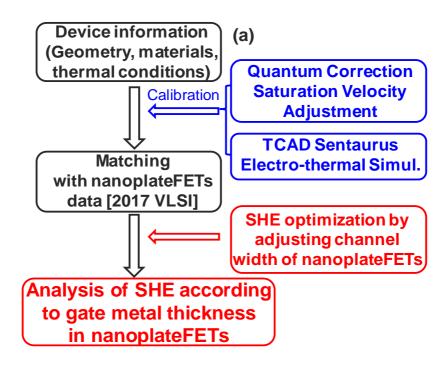

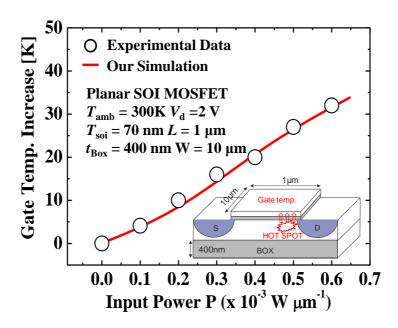

#### 3.3 Work Flow and Calibration Process

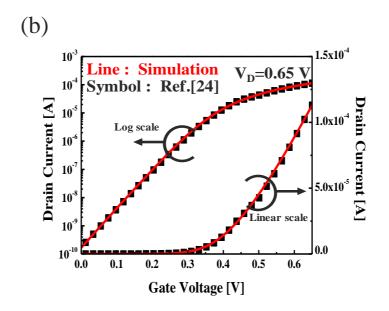

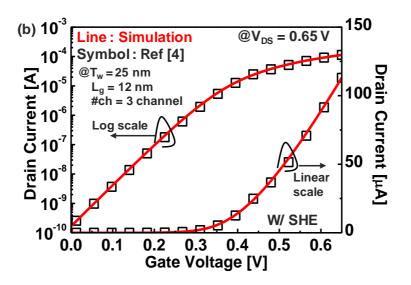

Fig. 3.2(a) shows the total work flow in the study. The calibration of the nanoplate-FET is performed and then the channel width is reduced to convert to the nanowire structure. Finally, SHE analysis is performed on the nanowire-FET. Quantum corrections are conducted for I-V calibration under 3-D TCAD simulation provided by Synopsys [6]. We use the density gradient quantization model (quantumPotential) to consider effect the quantum and use the mobility model (thin layer/phumob/Enormal(lombardi)) to account for Coulomb scattering and interfacial surface calibration roughness scattering for accuracy. First, I-V simulations are performed with the quantum model and the gate work function (WF) and the saturation velocity are carefully adjusted to match the I-V characteristics with the measured data [24]. Second, the thermal conductivity, heat conduction paths, and thermal boundary condition (300 K) to each heat path are considered to reflect the thermal characteristics of the nanoplate-FET. Fig. 3.2(b) shows that our simulation result is well fit with the measured data of the three-channel nanoplate-FETs [24]. The calibrated TCAD models are used to predict the electro-thermal characteristics of the 5-nm node nanowire-FET.

Fig. 3.2 (a) Overall work flow for analysis of SHE in nanowire-FET structures, (b)  $I_D$ - $V_G$  calibration results based on the nanosheet FET structure.

#### 3.4 More Detailed Thermal Simulation of Nanowire-FET

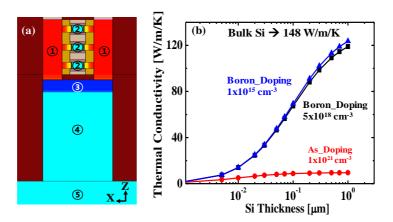

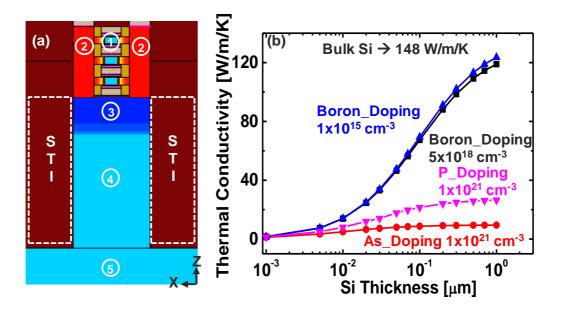

Fig. 3.3(a) shows the device divided into five regions; Fig. 3.3(b) shows the thermal conductivity graph, which is calculated by considering the doping type, doping concentration, and region thickness from the previous articles [8], [14], [15] about modeling the thermal conductivity of silicon by phonon Boltzmann transport equations. Using this graph, we set the thermal conductivity value of the regions. Table 3.1 shows the thermal conductivity of each region. The thermal contact is set in the area where the heat is dissipated. With reference to the articles [9], [16]–[18] dealing with SHE, the source, drain, gate, and substrate are set to thermal contact. In addition, a boundary condition is required when calculating the temperature of the device, and accordingly, we have specified room temperature (300 K) for the thermal contacts. Finally, the thermodynamic model is used for the overall SHE analysis because in the case of thermodynamic model, the change in the device temperature is directly taken into account in the current [17].

Fig. 3.3 (a) The five region for setting of thermal conductivity, (b) Thermal conductivity according to doping type, doping concentration, region thickness.

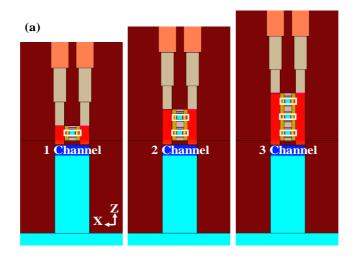

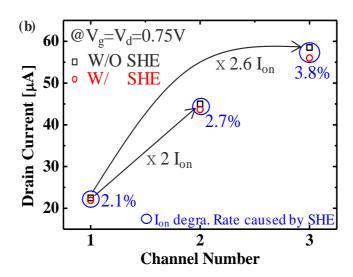

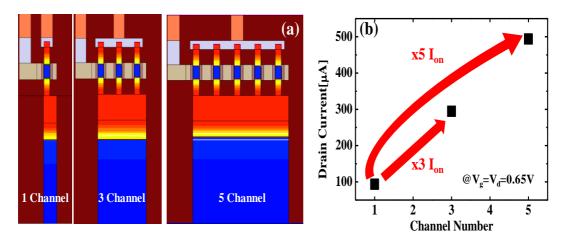

### 3.5 Performance Analysis by Number of Channels

First, we explain why the study is conducted using three-channel nanowire-FETs instead of a single-channel nanowire-FET. Nanowire-FETs with multiple channels (three channels) are very attractive compared to single-channel nanowire-FETs, because they exhibit a better performance [20]. Fig. 3.4(a) shows the structure created by simulation (Synopsys) for single-, two-, and three-channel nanowire-FETs. Fig. 3.4(b) shows a comparison of the Ion and Ion degradation rate for each channel number. As the number of channels increases from one to three, the Ion increases almost three times for the same CGP. The reason why the current does not increase linearly according to the number of channels is because the source and drain sheet resistances increase with the number of channels. Also, as the channel number increases, the Ion degradation rate due to SHE increases. In other words, as the number of channels increases, the degradation due to SHE becomes worse. For this reason, SHE studies are conducted on three-channel nanowire-FETs rather than single-channel nanowire-FETs.

Fig. 3.4 (a) Nanowire-FET structures from one channel to three channels. (b) The comparison of  $I_{on}$  according to channel number.

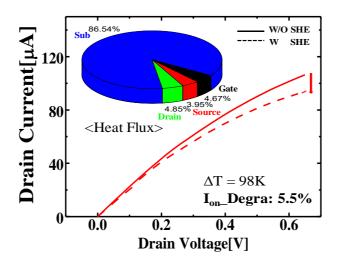

#### 3.6 DC Characteristic of SHE in Three Channel Nanowire-FETs

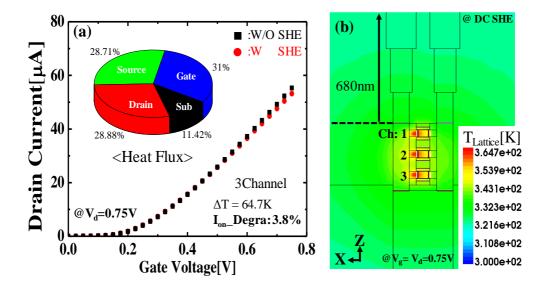

Next, the analysis of dc characteristics of SHE in a three-channel nanowire-FET is conducted. Fig. 3.5(a) shows the  $I_d$  – $V_g$  curve when  $V_d$  is 0.75 V, the  $I_{on}$  degradation rate by SHE, and the percentage of heat flux to the heat paths at  $V_d = V_g = 0.75$  V. The  $I_{on}$  reduces by approximately 3.8% caused by the decrease in electron mobility. Fig. 3.5(b) shows the maximum lattice temperature ( $T_{max}$ ) of the three-channel nanowire-FET with the BEOL (M8 layer height :680 nm).  $\Delta T_{max}$ , which represents the  $T_{max}$  –300 K (the boundary temperature), is approximately 65 K. Fig. 3.5(c) shows the  $\Delta T_{max}$  curve according to the dc power. We can extract the thermal resistance ( $R_{th}$ ) from the slope of the straight line. As shown in Fig. 3.5(c), it can be analyzed that how much the thermal properties of a three-channel nanowire-FET are worse compared to a single-channel nanowire-FET.  $R_{th}$  is 3.34 K/ $\mu$ W for the single- channel and  $R_{th}$  is 4.875 K/ $\mu$ W for three-channels. That is, the thermal characteristics are worsened when a three-channel nanowire-FET is used.

Fig. 3.5 (a)  $I_{d}$ - $V_{g}$  curve with heat flux to heat path and  $I_{on}$  degradation rate by SHE, (b) Thermal distribution and max lattice temperature, (c) Normalized  $R_{th}$  for single-channel and three-channel nanowire-FET.

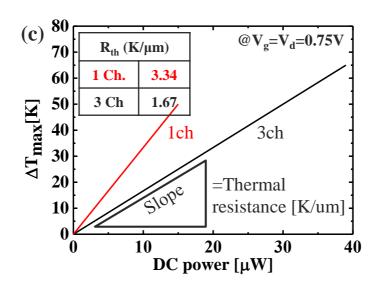

Fig. 3.6 shows the reason why the thermal characteristics of a three-channel nanowire-FET are worse than that of a single channel nanowire-FET a. Fig. 3.6(a) shows the structures when the channel-to-channel distance ( $H_{int}$ ) is 18 nm and  $H_{int}$  is 40 nm, respectively. When  $H_{int}$  is extended to 40 nm,  $T_{max}$  decreases. As shown in Fig. 3.6(b), the effect of  $H_{int}$  variation on the thermal properties of the three-channel nanowire-FET is analyzed through  $R_{th}$ . As the Hint becomes narrower, the heat generated per channel is further coupled with each other, adversely affecting heat dissipation, resulting in an increase of  $R_{th}$ . On the other hand, if  $H_{int}$  is high, the thermal coupling between the heat generated in each channel is weakened, resulting in a decrease in  $R_{th}$ . Therefore, in a three-channel nanowire-FET, the thermal properties are degraded by the large  $I_{on}$  and thermal coupling between channels.

Fig. 3.6 (a) The structures when  $H_{int}$  is 18 nm and 40 nm, (b)  $R_{th}$  when  $H_{int}$  is from 8 nm to 40 nm.

#### 3.7 AC Characteristic of SHE in Three Channel Nanowire-FETs

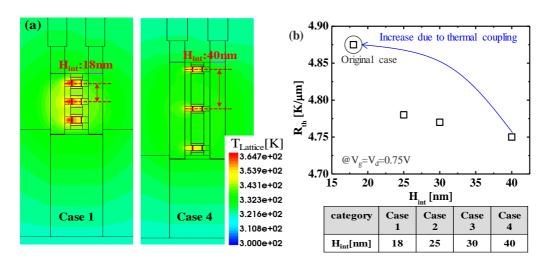

Finally, we analyze the SHE characteristics in the ac mode. Fig. 3.7(a) shows the method of setting the gate voltage to the ac mode. The pulse voltage consists of the rising time (RT), pulse time (PT), and off time (OT). One cycle consists of one PT and OT. The definition of the duty cycle is PT/OT. Fig. 3.7(b) shows the drain voltage. For pulse signals, the drain voltage must be in the dc mode to prevent any overshoot [21]. Therefore, the drain voltage was in the dc mode through ultrashort RT. In the ac mode, we can obtain various frequencies by adjusting the PT and the OT of the gate voltage. Before studying SHE according to the operating frequency, we proceeded to the study of T<sub>Lattice</sub> according to pulse heating time and cooling time. Cooling time is related to heat dissipation capacity (1/R<sub>th</sub>) and thermal capacitance (C<sub>th</sub>). C<sub>th</sub> is proportional to the total heat generated by the device [22].

Fig. 3.7 (a) Gate voltage for AC mode including *RT* (Rising Time), *PT* (Pulse Time) and *OT* (Off Time), (b) DC Drain voltage using ultra-short *RT*.

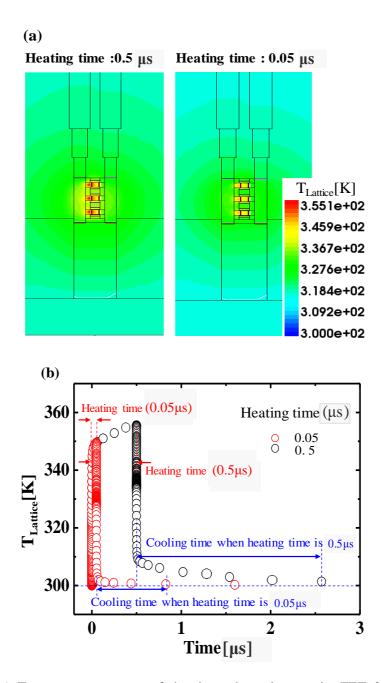

Changing the heating time at the transient input (pulse voltage) makes the difference in total heat in the same device. Fig. 3.8(a) shows the temperature contour of the three-channel nanowire-FET for different heating times. Fig. 3.8(b) shows the difference in  $T_{max}$  according to the heating time and shows each required cooling time accordingly. Here, the heating time is the same as the PT, which means the gate voltage is ON and the cooling time is the time required for  $T_{Lattice}$  to return to 300 K after the gate pulse is off. In conclusion, the longer heating time result in a greater  $T_{max}$  and accordingly, a longer cooling time, as shown in Fig. 3.8(b).

Fig. 3.8 (a) Temperature contour of the three-channel nanowire-FET for different heating times, (b) the transient data of device  $T_{Lattice}$  and cooling time.

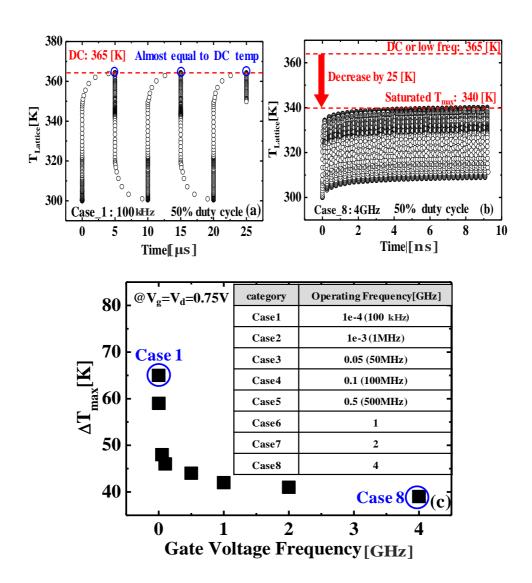

Fig. 3.9 shows the SHE of the device when the gate voltage is set to the ac mode. Fig. 3.9(a) shows the temperature characteristics of the lattice when the gate voltage is 50% duty cycle (that is, PT = OT) and the frequency is 100 kHz (that is, PT and OT are 5 µs each, and RT is set to about 5 ns, which is about 1/1000 times that of PT and OT). At 100 KHz, the temperature rises almost up to 365 K, which is the temperature rise in the dc operation. Fig. 3.9(b) shows the temperature characteristics of the lattice when the operating frequency is 4 GHz (that is, PT and OT are 0.25 ns each and RT is set to  $0.25 \times 10^{-12}$  s) and the duty cycle is set to 50%. At 4 GHz, it is observed that  $T_{max}$  saturates to 340 K, which is 25 K less than the temperature in the dc mode or at a low operating frequency. The reason why T<sub>max</sub> saturates at a low value when the frequency is high can be explained by the heating time and the cooling time illustrated above [Fig. 3.8(b)]. As the frequency increases, the heating time becomes shorter and the temperature rise becomes less. Also, since the cooling time is short, the temperature of the lattice cannot be reduced to 300 K and the residual temperature is generated. For this reason, at high operating frequencies, the temperature characteristic is as shown in Fig. 3.9(b). Fig. 3.9(c) shows the  $\Delta T_{max}$  value according to various frequencies. As the operating frequency rises, it is observed that  $\Delta T_{max}$  decreases and saturates to approximately 40 K. As the device becomes smaller, the operating frequency increases in an inverse proportion to L<sub>g</sub>. When the device operates in the circuit level, it is driven in the ac mode, and the temperature increasing due to SHE is expected to be reduced compared to the dc mode.

Fig. 3.9 (a)  $T_{Lattice}$  at operating frequency of 100KHz, (b)  $T_{Lattice}$  at operating frequency of 4GHz, (c)  $\Delta T_{max}$  according to operating frequency.

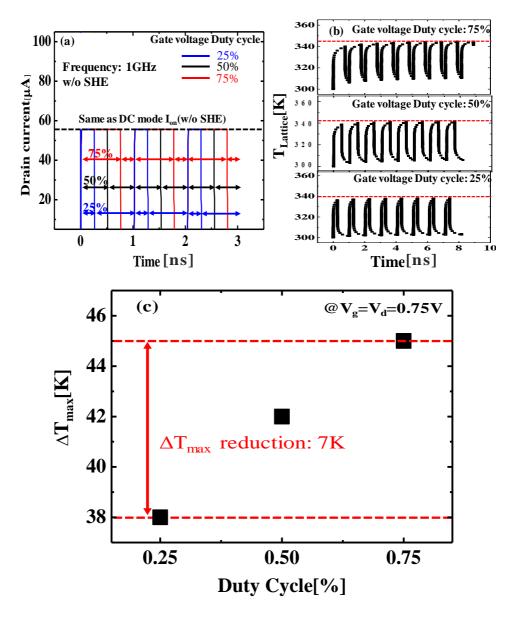

Fig. 3.10(a) shows  $I_{on}$  when the frequency is fixed at 1 GHz and the duty cycle is different. To analyze the effect of only the duty cycle on  $I_{on}$ , the results of Fig. 3.10(a) are carried out with the exception of SHE. It is confirmed that  $I_{on}$  is constant according to the duty cycle and has the same  $I_{on}$  as the dc condition illustrated above [Fig. 3.5(a)]. Fig. 3.10(b) shows  $T_{Lattice}$  according to the duty cycle. When the duty cycle is 50%, it is the same as 1 GHz in Fig. 3.9(c). As shown in Fig. 3.10(b), as the duty cycle increases, the  $T_{Lattice}$  increases. This is because as the duty cycle increases, the heating time increases and the cooling time decreases. Fig. 3.10(c) shows  $\Delta T_{max}$  according to the duty cycle of the gate voltage. Similar to the results of Fig. 3.10(b),  $\Delta T_{max}$  increases as the duty cycle increases. Therefore, if the duty cycle is reduced at the same operating frequency, the  $\Delta T_{max}$  decreases without affecting the  $I_{on}$  characteristics, so the SHE-induced temperature rise will be alleviated if the duty cycle of the gate voltage is reduced. As a result, it is expected that the Ion degradation rate will be reduced and the reliability problem due to heat will be reduced.

Fig. 3.10 (a)  $I_{on}$  comparison according to duty cycle when SHE is not considered, (b) Comparison of  $T_{Lattice}$  according to duty cycle, (c)  $\Delta T_{max}$  Comparison according to Duty Cycle.

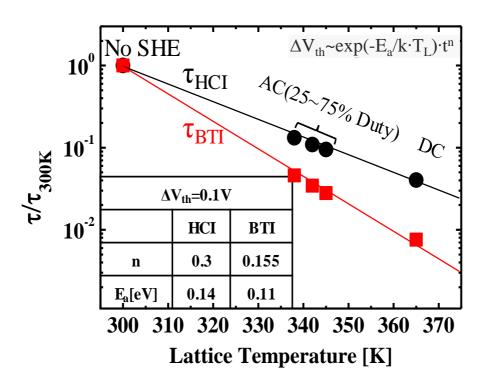

A comparison of the HCI/BTI lifetime is shown in Fig. 3.11, where  $\tau$  is normalized with the HCI/BTI lifetime at 300 K ( $\tau_{300\text{K}}$ ). The E<sub>a</sub> and the *n* of the nanowire-FET were assumed to be the same as [18], [19], and [23]. The  $\tau/\tau_{300\text{K}}$  ratio was significantly changed, from  $1\times10^{-1}$  to  $7\times10^{-3}$ , according to the operation mode and the duty cycle of the ac mode. Therefore, in the ac mode, the SHE can be mitigated, as compared with the dc mode. In the ac mode, the performance can be maintained according to the duty cycle, while HCI and BTI lifetime can be increased up to two times and three times, respectively.

Fig. 3.11 A comparison of HCI (black) and BTI (red) lifetime as a function of  $T_{L,max}$ . The  $T_{L,max}$  is determined by SHE with operation mode and various duty cycle

## 3.8 Summary

In this chapter, we analyzed the SHE of dc and ac for a three-channel nanowire-FET. When using a three-channel nanowire-FET over a single-channel nanowire-FET to increase the performance ( $I_{on}$ ),  $\Delta T_{max}$  in the dc mode increases from 50 to 65 K, resulting in an  $I_{on}$  degradation rate of 3.8%. Also, the  $R_{th}$  increases from 3.34 to 4.875 K/ $\mu$ W compared to the single channel. In the ac mode, when the heating time (PT) becomes longer, the total heat amount increases and the maximum temperature increases. Thus, a longer time is required for cooling to 300 K in the same device. Next, it was confirmed that  $\Delta T_{max}$  decreases as the device operating frequency increases with the duty cycle set to 50% and  $\Delta T_{max}$  saturates to about 40 K at 4 GHz. Finally, when the operating frequency is at 1 GHz, the temperature characteristics are analyzed while changing the duty cycle. As a result,  $\Delta T_{max}$  is reduced when the duty cycle is short. In the ac mode, the performance can be maintained according to the duty cycle, while HCI and BTI lifetime can be increased up to two times and three times, respectively.

#### References

- [1] D. Yakimets et al., "Vertical GAAFETs for the ultimate CMOS scaling," IEEE Trans. Electron Devices, vol. 62, no. 5, pp. 1433–1439, May 2015. doi: 10.1109/TED.2015.2414924.

- [2] C. P. Auth and J. D. Plummer, "Scaling theory for cylindrical, fully depleted, surrounding-gate MOSFET's," IEEE Electron Device Lett., vol. 18, no. 2, pp. 74–76, Feb.

- 1997. doi: 10.1109/55.553049.

- [3] K. H. Yeo et al., "Gate-all-around (GAA) twin silicon nanowire MOSFET (TSNWFET) with 15 nm length gate and 4 nm radius nanowires," in IEDM Tech. Dig., Dec. 2006, pp. 539–542. doi: 10.1109/IEDM.2006.346838.

- [4] M. Shrivastava et al., "Physical insight toward heat transport and an improved electrothermal modeling framework for FinFET architectures," IEEE Trans. Electron Devices, vol. 59, no. 5, pp. 1353–1363, May 2012. doi: 10.1109/TED.2012.2188296.

- [5] E. Pop and K. E. Goodson, "Thermal phenomena in nanoscale transistors," in Proc. 9th Intersoc. Conf. Therm. Thermomechan. Phenomena Electron. Syst., Jun. 2004, pp. 1–7. doi: 10.1109/ITHERM. 2004.1319147.

- [6] Version K-2015.06-SP1. Synopsys Inc., Mountain View, CA, USA, 2017.

- [7] The International Technology Roadmap for Semiconductors (ITRS), 2015.

- [8] E. Pop, S. Sinha, and K. E. Goodson, "Heat generation and transport in nanometer-scale transistors," Proc. IEEE, vol. 94, no. 8, pp. 1587–1601, Aug. 2006. doi: 10.1109/JPROC.2006.879794.

- [9] D. Jang et al., "Self-heating on bulk FinFET from 14 nm down to 7 nm node," in IEDM Tech. Dig., Dec. 2015, pp. 11.6.1–11.6.4. doi: 10.1109/IEDM.2015.7409678.

- [10] C.-H. Jan et al., "A 22 nm SoC platform technology featuring 3-D Tri-gate and high-k/Metal gate, optimized for ultra-low power, high performance and high density SoC applications," in IEDM Tech. Dig., Dec. 2012, pp. 3.1.1–3.1.4. doi: 10.1109/IEDM.2012.6478969.

- [11] D. Ingerly et al., "Low-k interconnect stack with metal-insulator metal capacitors for

- 22 nm high volume manufacturing," in Proc. IEEE Int. Interconnect Technol. Conf., Jun. 2012, pp. 1–3. doi: 10.1109/IITC.2012.6251663.

- [12] K. Fischer et al., "Low-k interconnect stack with multi-layer air gap and tri-metal-insulator-metal capacitors for 14 nm high volume manufacturing," in Proc. IEEE IITC/MAM, May 2015, pp. 5–8. doi: 10.1109/IITC MAM.2015.7325600.

- [13] C. Auth et al., "A 22 nm high performance and low-power CMOS technology featuring fully-depleted tri-gate transistors, self-aligned contacts and high density MIM capacitors," in Proc. Symp. VLSI Technol. (VLSIT), Jun. 2012, pp. 131–132. doi: 10.1109/VLSIT.2012.6242496.

- [14] W. Liu, K. Etessam-Yazdani, R. Hussin, and M. Asheghi, "Modeling and data for thermal conductivity of ultrathin single-crystal SOI layers at high temperature," IEEE Trans. Electron Devices, vol. 53, no. 8, pp. 1868–1876, Aug. 2006. doi: 10.1109/TED.2006.877874.

- [15] M. Asheghi, K. Kurabayashi, R. Kasnavi, and K. E. Goodson, "Thermal conduction in doped single-crystal silicon films," J. Appl. Phys., vol. 91, p. 5079, Jan. 2002. doi: 10.1063/1.1458057.

- [16] T. Takahashi, S. Oda, and K. Uchida, "Methodology for evaluating operation temperatures of fin-type field-effect transistors connected by interconnect wires," Jpn. J. Appl. Phys., vol. 52, no. 6R, May 2013, Art. no. 064203. doi: 10.7567/JJAP.52.064203. [17] I. Myeong, D. Son, H. Kim, M. Kang, J. Jeon, and H. Shin, "Thermal-aware shallow trench isolation design optimization for minimizing Iof f in various sub-10-nm 3-D transistors," IEEE Trans. Electron Devices, vol. 66, no. 1, pp. 647–654, Jan. 2019. doi:

- 10.1109/TED.2018.2882577.

- [18] D. Son, I. Myeong, H. Kim, M. Kang, J. Jeon, and H. Shin, "Analysis of electrothermal characteristics of GAA vertical nanoplate-shaped FETs," IEEE Trans. Electron Devices, vol. 65, no. 7, pp. 3061–3064, Jul. 2018. doi: 10.1109/TED.2018.2832239.

- [19] D. Ryu, I. Myeong, J. Lee, M. Kang, J. Jeon, and H. Shin, "Investigation of gate sidewall spacer optimization from OFF-state leakage current perspective in 3-nm node device," IEEE Trans. Electron Devices, vol. 66, no. 6, pp. 2532–2537, Jun. 2019. doi: 10.1109/TED.2019.2912394.

- [20] H. Zhu, Q. Li, H. Yuan, H. Baumgart, D. E. Loannou, and C. A. Richter, "Self-aligned multi-channel silicon nanowire field-effect transistors," in Proc. Int. Semiconductor Device Research Symp. (ISDRS), Dec. 2012, pp. 1–2. doi: 10.1016/j.sse.2012.05.058.

- [21] N. Beppu, S. Oda, and K. Uchida, "Experimental study of self-heating effect (SHE) in SOI MOSFETs: Accurate understanding of temperatures during AC conductance measurement, proposals of 2  $\omega$  method and modified pulsed IV," in IEDM Tech. Dig., Dec. 2012, pp. 28.2.1–28.2.4. doi: 10.1109/IEDM.2012.6479120.

- [22] J.-Y. Yan et al., "Thermal resistance modeling of back-end interconnect and intrinsic FinFETs, and transient simulation of inverters with capacitive loading effects," in IEDM Tech. Dig., Dec. 2016, pp. 35.6.1–35.6.4. doi: 10.1109/IEDM.2016.7838550.

- [23] W. Ahn, H. Jiang, S. Shin, and M. A. Alam, "A novel synthesis of Rent's rule and effective-media theory predicts FEOL and BEOL reliability of self-heated ICs," in IEDM

Tech. Dig., Dec. 2016, pp. 168–171. doi: 10.1109/IEDM.2016.7838365.

[24] N. Loubet et al., "Stacked nanosheet gate-all-around transistor to enable scaling beyond FinFET," in Proc. Symp. VLSI Technol., Jun. 2017, pp. T230–T231. doi: 10.23919/VLSIT.2017.7998183.

# Chapter 4

**Self-Heating** and **Electrothermal**

Properties of Advanced Sub-5-nm node

# **Nanoplate FET**

#### 4.1 Introduction

Reliability of modern field effect transistors (FET) emerged as one of the most important factors in the semiconductor industry to satisfy the increasing demand of stable computing performance. At the same time, industry continuously targeted to downscale devices by a few nano-meter range to improve integrated circuit performance. Race to downsize transistor introduced new innovative device structures such as Fin-shaped transistor (FinFET) [1-3], nanowire transistor and stacked nanoplate GAA transistor [4]. However, as a result of aggressive downscaling, current FinFET showed high thermal resistance and lattice temperature due to SHE, putting thermal reliability at stake [5,6]. SHE ultimately leads to performance and other reliability issues including, but not limited to, on-current degradation, hot carrier injection (HCI), Bias-temperature instability (BTI) and reduction of device's lifetime [7-9]. Being considered as a successor of FinFET,

GAA nanoplate-FET has growing concerns for self-heating effect as well [10]. Many suggests that especially for nanoplate-FET, SHE could be worse than FinFET due to confined geometry, where gate dielectric with low thermal conductivity fully surrounds the channels [11,12]. In this paper, based on ITRS 2015, nanoplate-FET that appeared as a new candidate in/under 5-nm node [4] is modelled through Sentaurus, a Technology Computer-Aided Design (TCAD) simulator. We have analyzed the temperature characteristics by manipulating several architecture parameters such as number of channels, channel width, and inter-layer metal thickness. And lastly, HCI / BTI lifetime according to maximum lattice temperature (TL,max) fluctuations by varying gate metal thickness is analyzed.

#### 4.2 Device Structure and Simulation Condition

The multi-channel nanoplate-FET structure used in this paper is simulated using a Synopsys Sentaurus [13], a TCAD simulator. Detailed specifications of structure are referred from the values of the 5-nm node in the International Technology Road Map for Semiconductor (ITRS) [14], listed in Table 4.1. Fig. 4.1 shows the entire structures and cross-sectional views of a multi-channel nanoplate-FET for the self-heating study [8-10]. Source (S) and drain (D) structures are modelled as cuboid [4], and the size of S/D bulk is changed according to channel width (T<sub>w</sub>) and metal thickness (T<sub>M</sub>) [21]. S/D is doped with phosphorus (P) as other materials such as arsenic (As) can easily damage the silicon Epi. A metal contact is contacted over the S/D bulk, where S/D bulk is composed of Silicon.

Fig. 4.1 (a) 3-D nanoplate-FET structure with the thermal contact, boundary condition, (b) XZ plane of a 3-D nanoplate-FETs, (c) YZ plane of a multi-channel region.

Table 4.1

Structural / Thermal specification of a nanosheet-FET

| <b>Structural Parameters</b>           | Value<br>(Unit: nm)       | Thermal Conductivity                   | Value<br>(Unit: W/K·m)                    |

|----------------------------------------|---------------------------|----------------------------------------|-------------------------------------------|

| Gate Length (L <sub>G</sub> )          | 12                        | 1 Channel                              | 7.5                                       |

| Spacer Length (L <sub>SP</sub> )       | 5                         | ② Source/Drain (Phosphorus)            | 9.4                                       |

| Gate Pitch (L <sub>PI</sub> )          | 48                        | 3 Local doping                         | 45.4                                      |

| Channel Thickness (T <sub>CH</sub> )   | 5                         | 4 STI-all-around                       | 46                                        |

| STI Thickness (T <sub>STI</sub> )      | 100                       | 5 Substrate (Bulk silicon)             | 148                                       |

| Channel Width (T <sub>W</sub> )        | 25                        | Oxide (SiO <sub>2</sub> )              | 1.4                                       |

| Effective Oxide Thickness (EOT)        | 1                         | Interconnect (Cu / W)                  | 400 / 175                                 |

| Gate metal thickness (T <sub>M</sub> ) | 4.45                      | Metal gate (W)                         | 175                                       |

| Substrate Width                        | 5000                      | <b>Thermal Contact Resistance</b>      | <b>Value</b> (Unit: cm <sup>2</sup> ·K/W) |

| Daning Consentuation                   | Value                     | Si/SiO <sub>2</sub> interface          | $2 \times 10^{-4}$                        |

| <b>Doping Concentration</b>            | (Unit: cm <sup>-3</sup> ) | Back End Of Line (BEOL)                | 1.7×10 <sup>-4</sup>                      |

| Source/Drain Doping                    | $1 \times 10^{21}$        | Thermal Contact Resistance (Sub)       | 2×10 <sup>3</sup>                         |

| Local Doping                           | 5×10 <sup>18</sup>        | Thermal Boundary condition (BEOL, Sub) | 300K                                      |

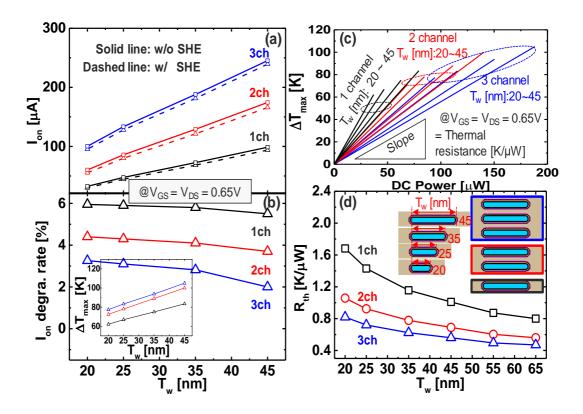

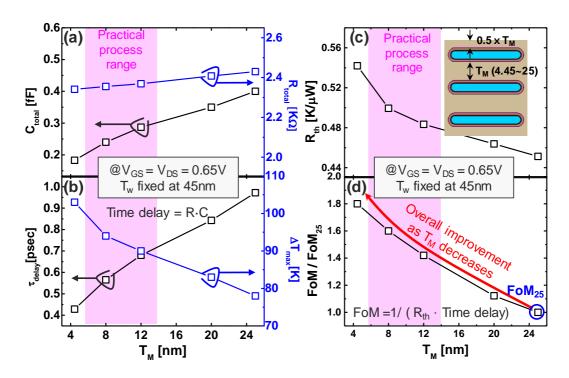

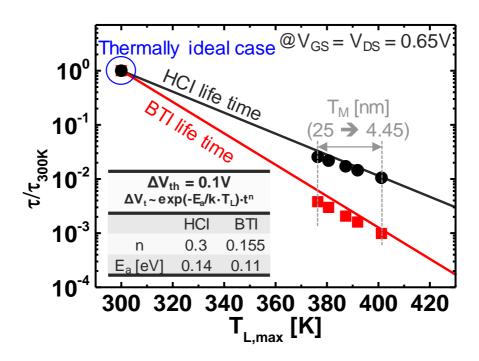

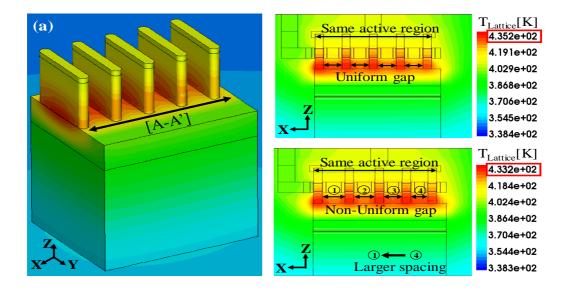

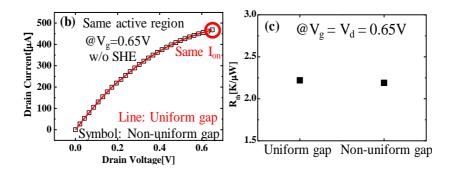

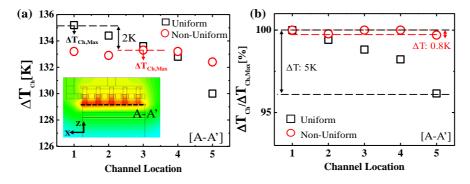

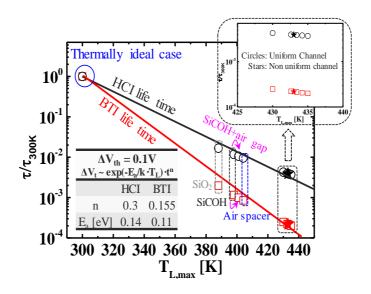

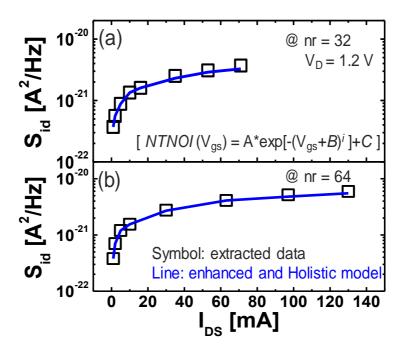

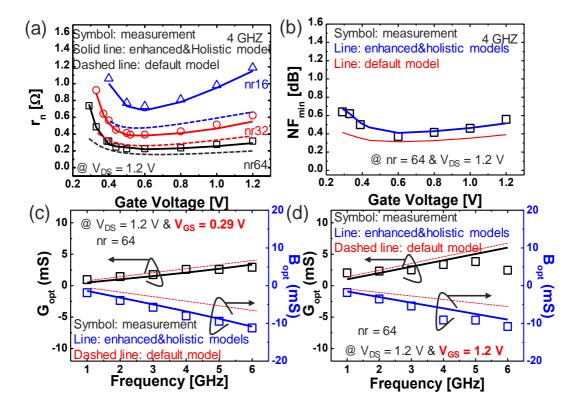

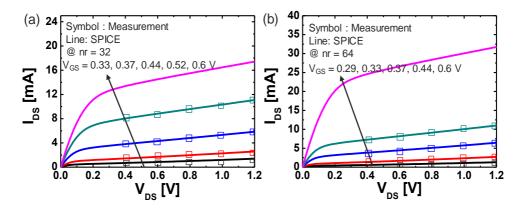

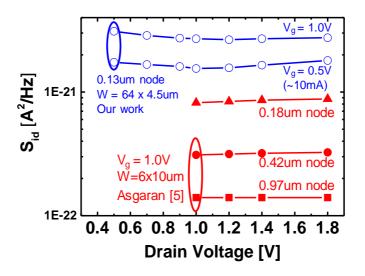

Fig. 4.2 (a) shows the active area divided into five regions. Fig. 4.2 (b) shows calculated thermal conductivity curve based on doped impurity type, doping concentration, and region thickness with reference to the previous research [19] on modelling thermal conductivity of silicon using the Phonon Boltzmann transport equation. We used this curve to determine thermal conductivity of each region in the parameter section.