#### 저작자표시-비영리-변경금지 2.0 대한민국

### 이용자는 아래의 조건을 따르는 경우에 한하여 자유롭게

• 이 저작물을 복제, 배포, 전송, 전시, 공연 및 방송할 수 있습니다.

#### 다음과 같은 조건을 따라야 합니다:

저작자표시. 귀하는 원저작자를 표시하여야 합니다.

비영리. 귀하는 이 저작물을 영리 목적으로 이용할 수 없습니다.

변경금지. 귀하는 이 저작물을 개작, 변형 또는 가공할 수 없습니다.

- 귀하는, 이 저작물의 재이용이나 배포의 경우, 이 저작물에 적용된 이용허락조건 을 명확하게 나타내어야 합니다.

- 저작권자로부터 별도의 허가를 받으면 이러한 조건들은 적용되지 않습니다.

저작권법에 따른 이용자의 권리는 위의 내용에 의하여 영향을 받지 않습니다.

이것은 이용허락규약(Legal Code)을 이해하기 쉽게 요약한 것입니다.

#### Ph.D. DISSERTATION

# Negative Capacitance Field-Effect Transistors with Stacked Nanosheet Structure

적층 나노시트 구조의 음의 정전용량 전계 효과 트랜지스터

BY

SIHYUN KIM

**AUGUST 2022**

DEPARTMENT OF ELECTRICAL AND COMPUTER

ENGINEERING

COLLEGE OF ENGINEERING

SEOUL NATIONAL UNIVERSITY

# Negative Capacitance Field-Effect Transistors with Stacked Nanosheet Structure

적층 나노시트 구조의 음의 정전용량 전계 효과 트랜지스터

지도교수 최 우 영 이 논문을 공학박사 학위논문으로 제출함 2022년 8 월

> 서울대학교 대학원 전기·정보공학부 김 시 현

김시현의 공학박사 학위논문을 인준함 2022년 8월

위원장: 이 수 연 (인)

부위원장: 최 우 영 (인)

위 원: 이종호 (인)

위 원: 권대웅 (인)

위 원: 김상완 (인)

### **Abstract**

The development of integrated circuit (IC) technology has continued to improve speed and capacity through miniaturization of devices. However, power density is increasing rapidly due to the increasing leakage current as miniaturization advances. Although the remarkable advancement of process technology has allowed complementary-metal-oxide-semiconductor (CMOS) technology to consistently overcome its constraints, the physical limitations of the metal-oxide-semiconductor field-effect transistor (MOSFET) are unmanageable. Accordingly, research on logic device is being divided into a CMOS-extension and a beyond-CMOS. CMOSextension focuses on the gate-all-around field-effect transistors (GAAFETs) which is a promising architecture for future CMOS thanks to the excellent electrostatic gate controllability. Particularly, nanosheet (NS) architecture with high current drivability required in ICs, is the most promising. However, NS GAAFET has a trade-off relation between the controllability and the drivability, which requires the necessity of a higher-level effective oxide thickness (EOT) scaling for further scaling of NS GAAFET.

On the other hand, beyond-CMOS mainly focuses on developing devices with novel mechanisms to overcome the MOSFETs' physical limits. Among several

candidates, negative capacitance field-effect transistors (NCFETs) with exceptional

CMOS compatibility and current drivability are highlighted as future logic devices

for low-power, high-performance operation. Although the NCFET utilizing the

negative capacitance (NC) effect of a ferroelectric has been demonstrated

theoretically by the Landau model, it is challenging to be implemented due to the fact

that stabilized NC and sub-thermionic subthreshold swing (SS) are incompatible.

In this dissertation, a GAA NCFET that maintains a stable capacitance boosting

by NC effect and exhibits high performance is demonstrated. A ferroelectric-

antiferroelectric mixed-phase hafnium-zirconium-oxide (HZO) thin film was

introduced, whose effect was confirmed by capacitors and FET experiments.

Furthermore, the mixed-phase HZO was demonstrated on a stacked nanosheet gate-

all-around (stacked NS GAA) structure, the advanced CMOS technology, which

exhibits a superior gate controllability as well as a satisfactory drivability for ICs. The

hysteresis-free stable NC operation with the superior performance was confirmed in

NS GAA NCFET. The improved SS and on-current  $(I_{on})$  compared to MOSFETs

fabricated in the same manner were validated, and its feasibility as a low-power, high-

performance logic device was proven based on a variety of figure of merits.

Keywords: Gate-all-around (GAA), Stacked nanosheet (stacked NS), Negative

ii

capacitance field-effect transistor (NCFET), Ferroelectric, Mixed-phase, Hafniumzirconium-oxide (HZO).

**Student Number**: 2014-21698

### **Contents**

| Abst | ract   |         | ······i                                                                             |

|------|--------|---------|-------------------------------------------------------------------------------------|

| Cont | tents  |         | iv                                                                                  |

| List | of Ta  | able ·· | ······vii                                                                           |

| List | of Fi  | gures · | ·····viii                                                                           |

| Chaj | pter   | 1 I     | ntroduction ····· 1                                                                 |

|      | 1.1    | Power   | and Area Scaling Challenges · · · · · 1                                             |

|      | 1.2    | Nanos   | heet Gate-All-Around FETs····· 5                                                    |

|      |        | 1.2.1   | Gate-All-Around FETs 5                                                              |

|      |        | 1.2.2   | Nanosheet GAAFETs · · · · 6                                                         |

|      | 1.3    | Negati  | ive Capacitance FETs · · · · · 11                                                   |

|      |        | 1.3.1   | Negative Capacitance in Ferroelectric Materials · · · · · · 11                      |

|      |        | 1.3.2   | Negative Capacitance for Steep Switching Devices ······14                           |

|      |        | 1.3.3   | Stable NC vs. Sub-thermionic SS · · · · · · 17                                      |

|      | 1.4    | Scope   | and Organization of Dissertation 21                                                 |

| Chaj | pter 2 |         | acked NS GAA NCFET with Ferroelectric-Antiferroelectric-<br>lixed-Phase HZO······22 |

|     | 2.1  | Mixed   | -Phase HZO for Capacitance Boosting · · · · · 22                        |

|-----|------|---------|-------------------------------------------------------------------------|

|     | 2.2  | NS GA   | AA NCFET using Mixed-Phase HZO25                                        |

| Cha | pter | 3 H     | ZO ALD Stack Optimization ······28                                      |

|     | 3.1  | Metal-  | Ferroelectric-Interlayer-Silicon (MFIS) / MFM Capacitors · · · · · · 29 |

|     |      | 3.1.1   | Fabrication of MFIS Capacitors · · · · · 29                             |

|     |      | 3.1.2   | Electrical Characteristics of MFIS / MFM Capacitors33                   |

|     | 3.2  | SOI Pl  | anar NCFETs ······38                                                    |

|     |      | 3.2.1   | DC Measurements ······38                                                |

|     |      | 3.2.2   | Direct Capacitance Measurements · · · · · 47                            |

|     |      | 3.2.3   | Speed Measurements · · · · · · 49                                       |

| Cha | pter | 4 De    | evice Fabrication of Stacked NS GAA NCFET51                             |

|     | 4.1  | Initial | Process Flow of NS GAA NCFET52                                          |

|     | 4.2  | Proces  | s Issues and Solution56                                                 |

|     |      | 4.2.1   | External Resistance56                                                   |

|     |      | 4.2.2   | TiN Gate Sidewall Spacer ····· 60                                       |

|     |      | 4.2.3   | Unintentionally Etched Sacrificial Layer65                              |

|     |      | 4.2.4   | Discussions ······68                                                    |

|     | 4.3  | Chann   | el Release Process ······69                                             |

|     |      | 4.3.1   | Consideration in Channel Release Process69                              |

|          |            | 4.3.2  | Methods for SiGe Selective Etching · · · · · 72                 |

|----------|------------|--------|-----------------------------------------------------------------|

|          |            | 4.3.3  | SiGe Selective Etching using Carboxylic Acid Solution ·······75 |

|          | 4.4        | Revise | ed Process of NS GAA NCFET ······78                             |

| Cha      | pter       | 5 El   | ectrical Characteristics of Fabricated NS GAA NCFET ······84    |

|          | 5.1        | DC Cł  | naracteristics ······85                                         |

|          |            | 5.1.1  | NS GAA NCFET vs. Planar SOI NCFET ·······85                     |

|          |            | 5.1.2  | Performance Enhancement of NS GAA NCFET 88                      |

|          |            | 5.1.3  | Performance Evaluation · · · · 96                               |

|          | 5.2        | Operat | ting Temperature Properties · · · · · 99                        |

| Cha      | pter       | 6 C    | onclusion 102                                                   |

| Bib      | liogra     | phy …  |                                                                 |

| <b>ラ</b> | . <b>로</b> |        | 115                                                             |

## **List of Table**

| Table | 3.1. Dielectric constants of high-κ films extracted from accumulation                                                                                  |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | capacitances ( $V_G$ =-1.5 V).                                                                                                                         |

| Table | <b>3.2.</b> Physical parameters and process conditions of SOI planar NCFET 3                                                                           |

| Table | 4.1. ISRC ICP metal etcher recipe (existed Al etch and new TiN etch recipe                                                                             |

|       | 6                                                                                                                                                      |

| Table | <b>4.2.</b> Process condition of CDE for SiGe selective etching                                                                                        |

| Table | <b>5.1.</b> $I_{\rm on}$ enhancement [ $(I_{\rm on,NC}$ - $I_{\rm on,Ref}$ )/ $I_{\rm on,Ref}$ ] and $V_{\rm G}$ scalability for the same $I_{\rm on}$ |

|       | including/excluding $R_{\text{External}}$ at $V_{\text{D.Lin}}$ and various $V_{\text{OV}}$ s                                                          |

# **List of Figures**

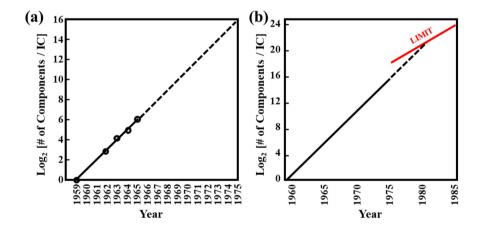

| Figure 1.1. Trend lines of the number of components in integrated circuit introduced                     |

|----------------------------------------------------------------------------------------------------------|

| by Moore: (a) Doubling every year [1] and (b) Doubling interval                                          |

| increased to 2 years [2]                                                                                 |

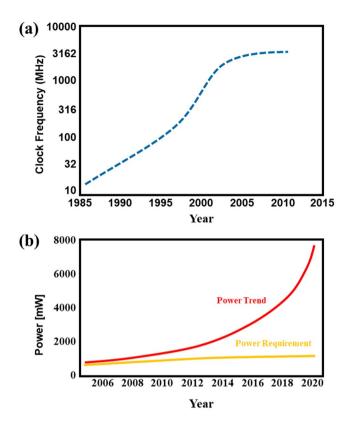

| Figure 1.2. (a) Clock frequency [3] and (b) power dissipation trend [8] of logic device                  |

| 4                                                                                                        |

| <b>Figure 1.3.</b> Development of CMOS device from planar to 3D Fin structure [9] 4                      |

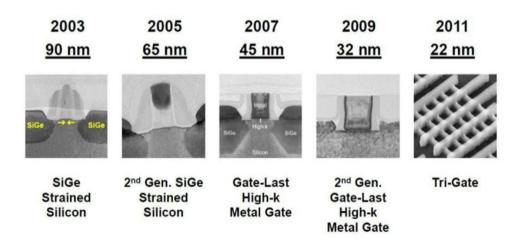

| Figure 1.4. Device architecture roadmap for future logic devices [30]                                    |

| <b>Figure 1.5.</b> (a) Subthreshold swing (SS) / drain-induced-barrier-lowering (DIBL) and               |

| (b) frequency of GAAFETs according to the nanosheet width [29] 6                                         |

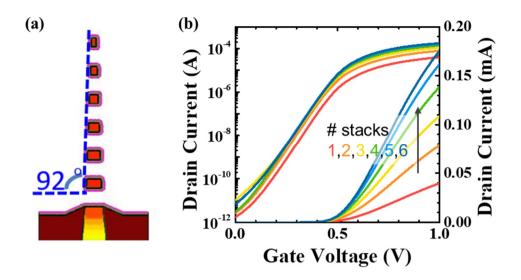

| Figure 1.6. (a) Schematic image of simulated stacked-GAAFET. (b) Simulated                               |

| current characteristics according to the number of stacked channels 9                                    |

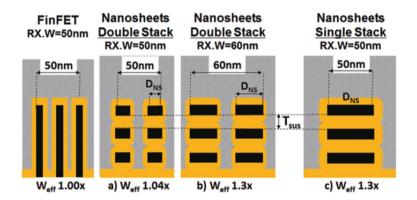

| <b>Figure 1.7.</b> Optimum GAA structure for high current drivability ( $\sim W_{\rm eff}$ ) considering |

| the active width (RX. W) [21]9                                                                           |

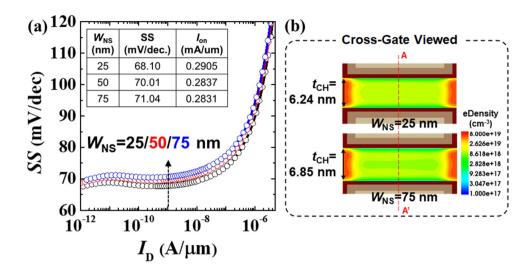

| <b>Figure 1.8.</b> (a) SS- $I_D$ of NS GAAFET with regard to nanosheet width $(W_{NS})$ . (b)            |

| Electron density along the channel of NS GAAFET w/ $W_{NS}$ = 25 and 75                                  |

| nm10                                                                                                     |

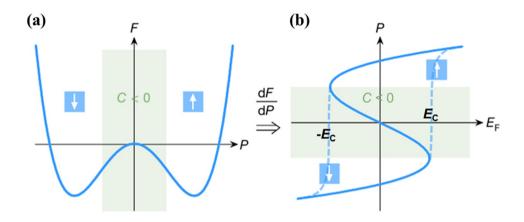

| <b>Figure 1.9.</b> (a) Double-well free-energy landscape and (b) Polarization ( <i>P</i> ) -electric     |

| field (E) relationship of ferroelectric material [40]                                                    |

| Figure 1.10. Non-centrosymmetric intermediate phase (orthorhombic phase) of                              |

| polycrystalline HfO for ferroelectricity [68]                                                            |

| Figure 1.11. (a) Schematic transfer characteristics of MOSFETs with positive /                          |

|---------------------------------------------------------------------------------------------------------|

| negative capacitance. (b) $V_{\rm DD}$ and EOT scaling trend [67]                                       |

| Figure 1.12. (a) Schematic of dielectric (DE)-ferroelectric (FE) series capacitor for                   |

| NC stabilization. (b) Corresponding free-energy landscapes [67] 20                                      |

| Figure 2.1. Free-energy landscape of ferroelectric (FE), antiferroelectric (AFE) and                    |

| FE+AFE mixed phase material [84]24                                                                      |

| <b>Figure 2.2.</b> Polarization-electric field ( <i>P-E</i> ) characteristics of HZO with regard to the |

| Hf / Zr composition [85]                                                                                |

| Figure 2.3. SS-I <sub>on</sub> benchmarks of reported NCFETs [53-65]                                    |

| Figure 2.4. Proposed device: stacked NS GAAFETs with ferroelectric-                                     |

| antiferroelectric mixed-phase HZO for low-power and high-performance                                    |

| logic technology                                                                                        |

| Figure 3.1. (a) Summarized process flow of MFIS capacitors. (b) Schematic image                         |

| of MFIS capacitors fabricated on p- Si. Two types of HZO ALD stacks                                     |

| along with reference pure HfO ALD stack are depicted. (c) TEM / EDS                                     |

| analysis of HZO stack 1                                                                                 |

| Figure 3.2. (a) Capacitance-Voltage (C-V) characteristics of MOS (TiN-HfO-SiO <sub>2</sub> -            |

| p-Si) capacitor with different TiN gate stack (ALD TiN + sputter TiN and                                |

| only sputter TiN). (b) C-V characteristics of MFIS capacitor with and                                   |

| without HPA process                                                                                     |

| Figure 3.3. (a) Gate capacitance characteristics of various MFIS stacks: 1) Pure HfO                    |

| / 2) HZO stack 1 3) HZO stack 2. Capacitance enhancements in HZO                                        |

| stacks are noticeable. (b) Gate leakage currents of three ALD stacks 36                                 |

| Figure 3.4. (a) Displacement current measurement of MFM capacitor (HZO stack1)       |

|--------------------------------------------------------------------------------------|

| for triangular voltage pulse. (b) P-V curve obtained from (c), showing               |

| ferroelectric-antiferroelectric-mixed characteristic                                 |

| Figure 3.5. Schematic image of SOI planar NCFET                                      |

| Figure 3.6. (a) Transfer characteristics of most SOI planar NCFET (b) enlarged graph |

| of (a), showing nearly hysteresis-free feature. (c) Transfer characteristic          |

| of few devices and enlarged graph (inset), showing counter-clockwise                 |

| hysteresis. (d) Free-energy landscape of ferroelectric (FE),                         |

| antiferroelectric (AFE), and mixed phase (FE + AFE) 41                               |

| Figure 3.7. (a) and (b) Transfer characteristics of SOI planar NCFET with HZO        |

| stack1 ( $V_D = 50 \text{ mV}$ and 0.5 V, respectively) compared with reference      |

| pure HfO device. (c) Subthreshold swing (SS)-I <sub>D</sub> curve extracted from (a) |

| and (b)44                                                                            |

| Figure 3.8. (a) Transfer characteristics of NCFET and reference MOSFET with          |

| relatively large channel width ( $W = 10 \mu m$ ). (b) Series resistance of          |

| MOSFET (c) External resistance extraction by $1/V_{\rm OV}$ method                   |

| Figure 3.9. On-current enhancement in SOI planar NCFET compared to the reference     |

| HfO device at linear and saturation $V_D$ conditions                                 |

| Figure 3.10. Output characteristics $(I_D-V_D)$ of SOI planar NCFET compared to pure |

| HfO device                                                                           |

| Figure 3.11. (a) Capacitance-voltage characteristics (y1) directly measured from SOI |

| planar FETs (Pure HfO and HZO stack 1) and the capacitance ratio (y2).               |

| (b) Transfer characteristics of the same device as (a)                               |

| Figure 3.12. (a) Measurement setup for transient $I_D$ - $V_G$ using B1500 WGFMU. (b)                        |

|--------------------------------------------------------------------------------------------------------------|

| $I_{\rm D}$ s of SOI planar NCFET ( $W/L = 50/0.5~\mu m$ ) with $V_{\rm G}$ pulse of $t_{\rm D} + t_{\rm M}$ |

| = 20 ns $\sim$ 100 $\mu$ s. (c) Enlarged $I_D$ - $V_G$ graph                                                 |

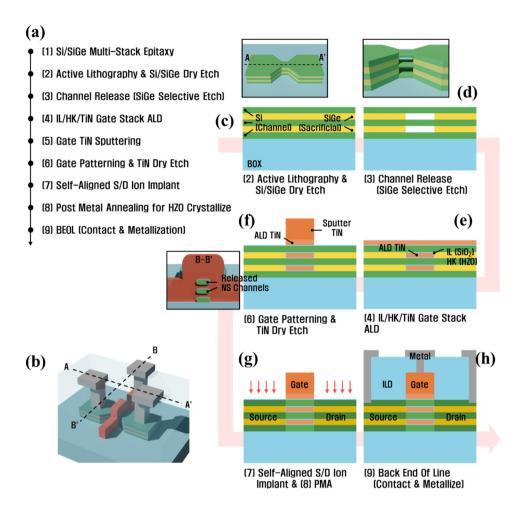

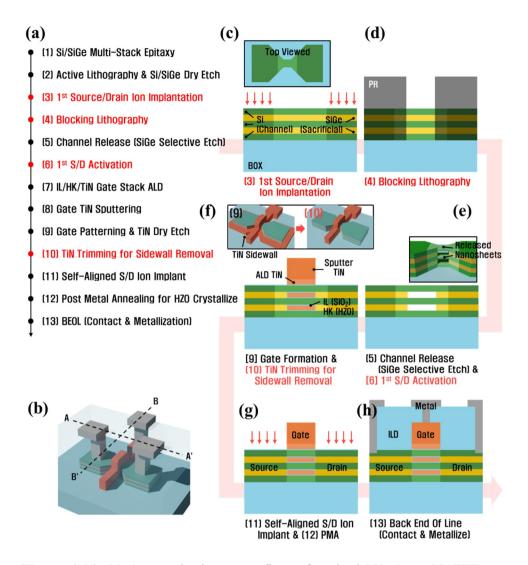

| Figure 4.1. (a) Summarized process flow of initially designed NS GAA NCFET                                   |

| fabrication. (b) 3D schematic image of NS GAA NCFET. (c)-(h) Cross-                                          |

| sectional schematic images of several key fabrication steps 54                                               |

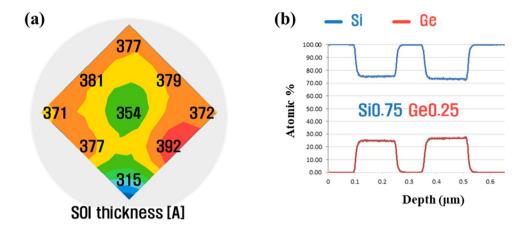

| <b>Figure 4.2.</b> (a) Silicon-on-insulator (SOI) thickness thinned from $1000A$ to $\sim 350A$ .            |

| (b) Atomic percent (Si and Ge) profile of SiGe/Si/SiGe/Si multi-stacked                                      |

| epitaxy test wafer55                                                                                         |

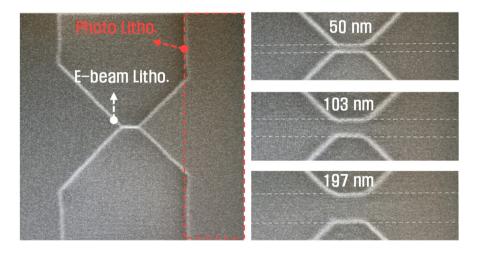

| Figure 4.3. Top-viewed SEM image after active patterning (photo / e-beam                                     |

| lithography and Si/SiGe dry etching). Actives with width of 50 nm, 100                                       |

| nm, 200 nm are clearly defined by e-beam lithography55                                                       |

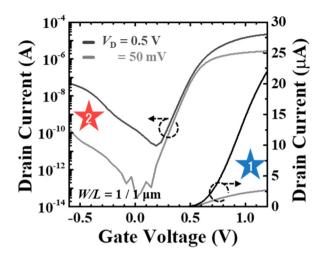

| Figure 4.4. $I_D$ - $V_G$ characteristics of SOI planar FET fabricated with initial process                  |

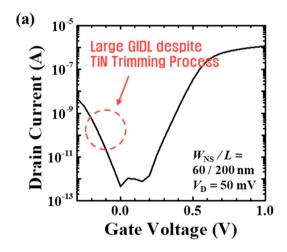

| excluding the channel release process: two major issues are represented.                                     |

| (1) Early current saturation at operation $V_G$ due to large external resistance                             |

| especially remarkable at low $V_{\rm D}$ (50mV). (2) Large GIDL current at                                   |

| negative $V_{\rm G}$ region                                                                                  |

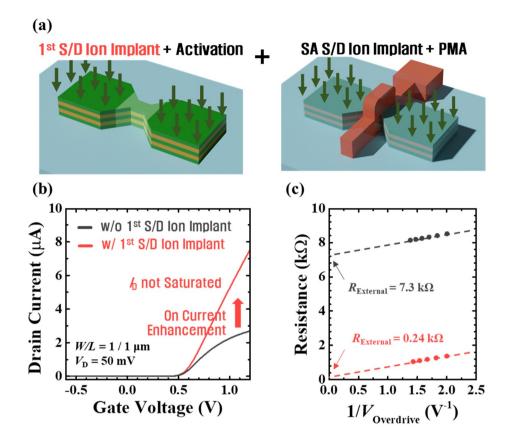

| <b>Figure 4.5.</b> (a) Schematic images of revised process for external resistance reduction:                |

| 1st S/D ion implant and high temperature activation before the gate stack                                    |

| formation. (b) Transfer characteristics of SOI planar FETs with initial /                                    |

| revised process. (c) External resistance of two devices extracted by $1/V_{\rm OV}$                          |

| method                                                                                                       |

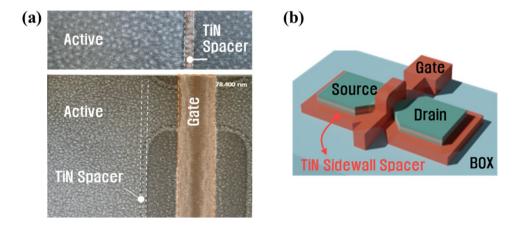

| Figure 4.6. (a) Top-viewed SEM image after gate dry etching, where the TiN spacer                            |

| remained along the active region is remarkable. (b) 3D schematic image                     |

|--------------------------------------------------------------------------------------------|

| after the gate dry etching.                                                                |

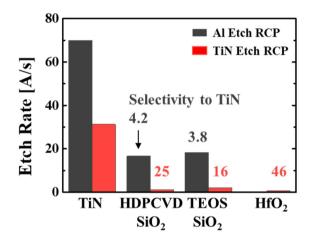

| Figure 4.7. Etch rate of ISRC ICP metal etcher recipes (existed Al etch recipe and         |

| new TiN etch recipe) for TiN and several dielectrics                                       |

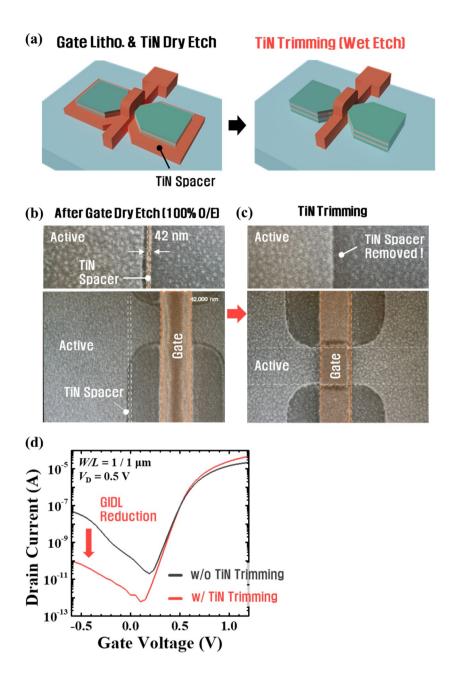

| Figure 4.8. (a) 3D schematic image of TiN wet trimming after gate dry etching. Top         |

| viewed SEM image of SOI planar FET (b) after TiN dry etch (100% over                       |

| etching using new TiN etch recipe) and (c) after TiN trimming (d                           |

| Transfer characteristics of SOI planar FETs with initial / revised process                 |

| 64                                                                                         |

| Figure 4.9. (a) $I_D$ - $V_G$ characteristic of fabricated NS GAA FET with initial channel |

| release process. (b) Tilted-viewed SEM image after channel release                         |

| process and (c) its enlarged image                                                         |

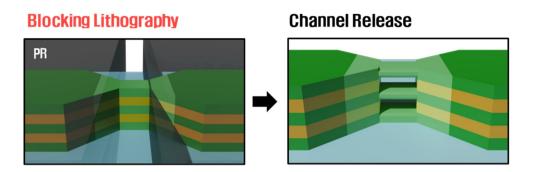

| Figure 4.10. Schematic image of solution for initial channel release process: blocking     |

| lithography for channel release, which hinder the sacrificial layers located               |

| out of the channel region from being unintentionally etched6                               |

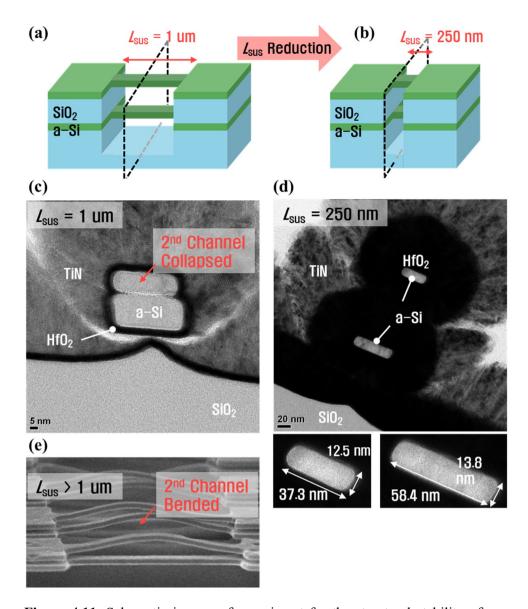

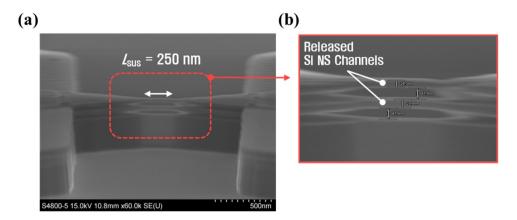

| Figure 4.11. Schematic images of experiment for the structural stability of suspended      |

| channel with (a) long and (b) reduced $L_{\rm SUS}$ (1 $\mu m$ and 250 nm). Cross          |

| sectional TEM images of structure after the channel release process with                   |

| (c) $L_{SUS} = 1 \mu m$ and (d) 250 nm. (e) Tilted-viewed SEM image of released            |

| channel with $L_{SUS} > 1 \mu m$ [90]                                                      |

| Figure 4.12. Cross-sectional SEM images after SiGe selective etching using CDI             |

| with CF <sub>4</sub> flow rate of (a) 80 sccm [99] and (b)/(c) 15 sccm (reduced) 73        |

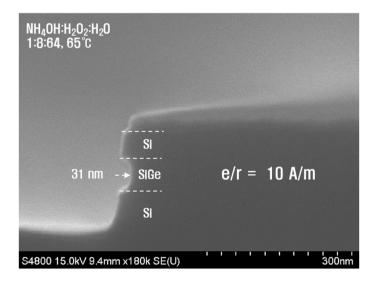

| Figure 4.13 gross sectional SEM image after SiGe selective etching with 1.9.64 SC          |

| 1 solution                                                                                          |

|-----------------------------------------------------------------------------------------------------|

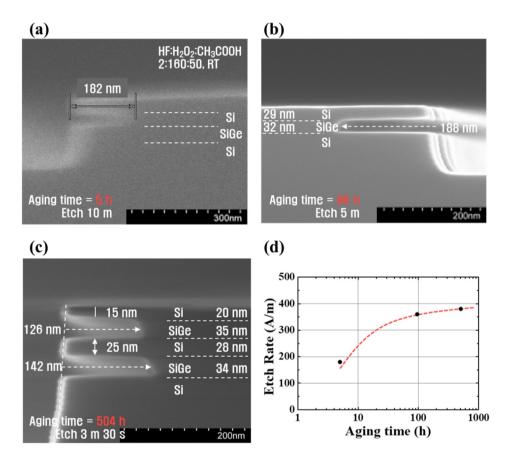

| Figure 4.14. Cross sectional SEM images after SiGe selective etching using                          |

| carboxylic acid solution (HF : $H_2O_2$ : $CH_3COOH = 2$ : 160 : 50 at room                         |

| temperature) of which aging times are (a) 5 hours, (b) 96 hours and (c)                             |

| 504 hours. (d) SiGe etch rate in the solution according to the aging time.                          |

|                                                                                                     |

| Figure 4.15. (a) tilted-viewed SEM image of released NS channels of which $L_{\rm SUS}$ =           |

| 250 nm after the active patterning by photo / e-beam mix-and-match                                  |

| lithography. (b) enlarged image of (a)77                                                            |

| Figure 4.16. (a) Summarized process flow of revised NS GAA NCFET fabrication.                       |

| (b) 3D schematic image of NS GAA NCFET. (c)-(h) Cross-sectional                                     |

| schematic images of several key fabrication steps                                                   |

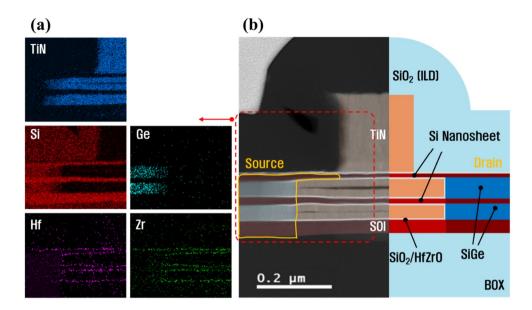

| Figure 4.17. (a) Cross-sectional [B-B' direction of Figure 4.16(b)] TEM image of 2-                 |

| stacked Si NS GAA NCFET. Enlarged TEM image of (b) 2nd (top) Si NS                                  |

| channel and (c) bottom Si (SOI). EDS analysis of 2-stacked Si NS GAA                                |

| NCFET (d) 2D material mapping and (e) line mapping 82                                               |

| Figure 4.18. (a) EDS analysis of 2-stacked Si NS GAA NCFET [red dotted area of                      |

| (b)]. (b) Cross-sectional [A-A' direction of Figure 4.16(b)] TEM image                              |

| of 2-stacked Si NS GAA NCFET83                                                                      |

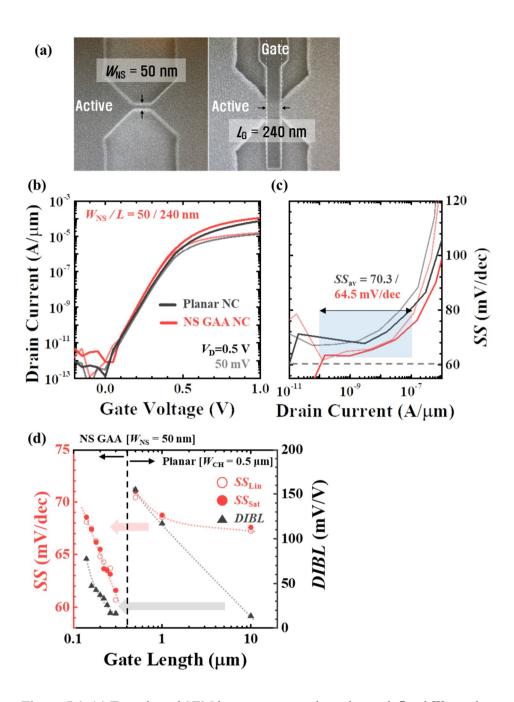

| <b>Figure 5.1.</b> (a) Top-viewed SEM images representing e-beam defined $W_{\rm NS}$ and $L$ . (b) |

| $I_{ m D}$ - $V_{ m G}$ , (c) SS- $I_{ m D}$ and (d) SS / DIBL vs. $L_{ m G}$ plots of NS GAA NCFET |

| compared to the SOI planar NCFET ( $W/L = 0.5 / 0.5 \mu m$ ) 87                                     |

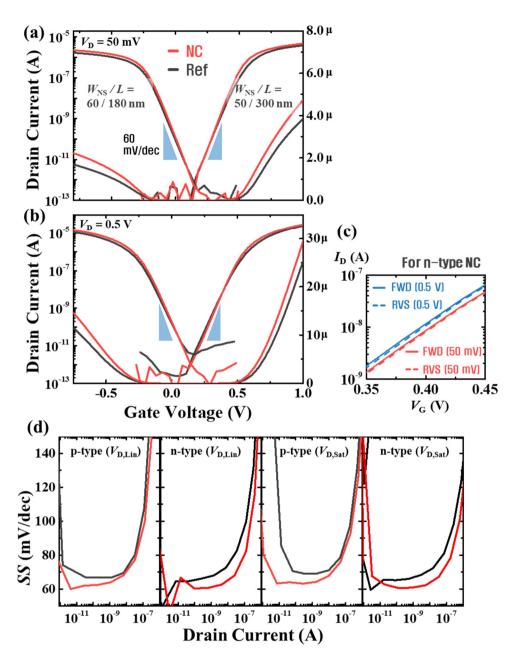

| Figure 5.2 Transfer characteristics of n- and n-type stacked NS GAA NCFFT at (a)                    |

|            | linear ( $V_D = 50 \text{ mV}$ ) and (b) saturation region ( $V_D = 0.5 \text{ V}$ ). (c) Enlarged                                                                        |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|            | forward and reverse swept $I_{\rm D}\text{-}V_{\rm G}$ s of n-type NS GAA NCFET (d) SS- $I_{\rm D}$                                                                       |

|            | plots of n- and p-type devices at different $V_D$ conditions                                                                                                              |

| Figure 5.3 | 3. DIBL of n-type NS GAAFETs (w/ reference HfO and NC HZO)                                                                                                                |

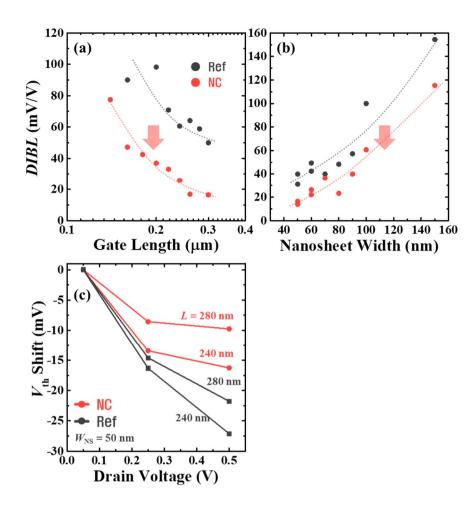

|            | according to (a) the gate length and (b) the nanosheet width. (c) $V_{\rm th}$ shift                                                                                      |

|            | of n-type NS GAFETs (reference and NC) with regard to $V_D$ 93                                                                                                            |

| Figure 5.4 | <b>4.</b> $R_{\text{External}}$ of n-type NS GAAFETs (w/ reference HfO and NC HZO)                                                                                        |

|            | extracted by 1/Vov method                                                                                                                                                 |

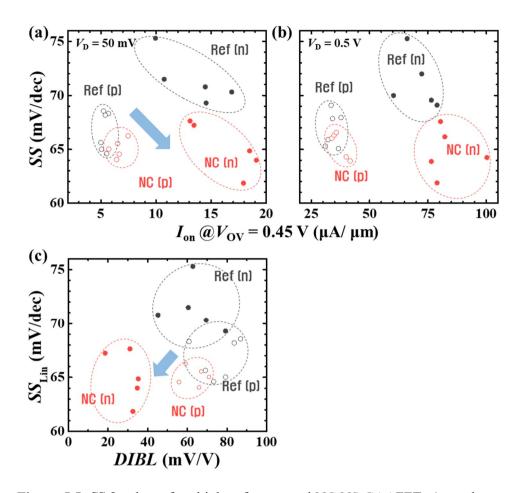

| Figure 5.5 | S. SS-I <sub>on</sub> plots of multiple reference and NC NS GAAFETs (n- and p-type)                                                                                       |

|            | at (a) $V_D = 50 \text{ mV}$ and (b) $V_D = 0.5 \text{ V}$ . (c) $SS_{Lin} - DIBL \text{ plots.}$                                                                         |

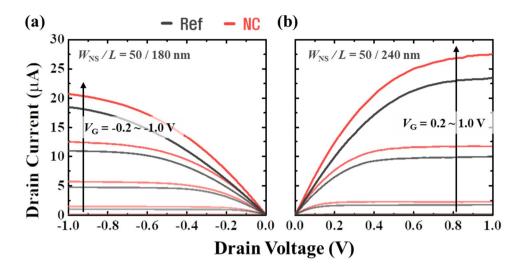

| Figure 5.6 | 6. Output characteristics of (a) p- and (b) n-type NS GAA FETs (reference                                                                                                 |

|            | and NC)96                                                                                                                                                                 |

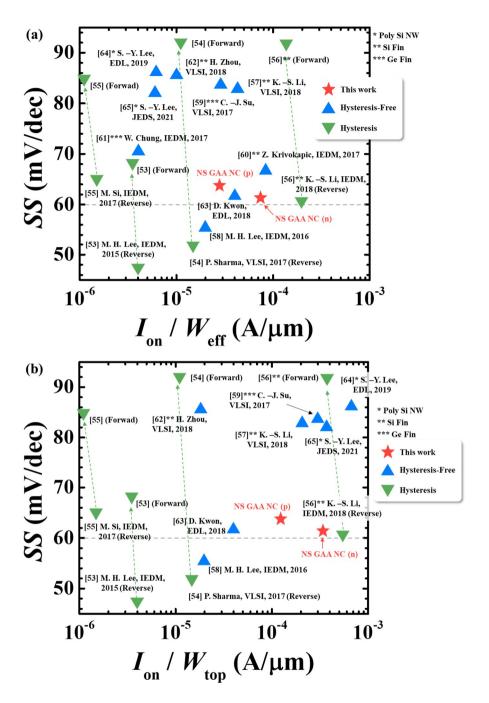

| Figure 5.7 | 7. Average $SS - I_{on}$ [normalized by (a) effective channel width and (b) by                                                                                            |

|            | top channel width] benchmarks of NS GAA NCFET (this work)                                                                                                                 |

|            | compared to other reported NCFETs                                                                                                                                         |

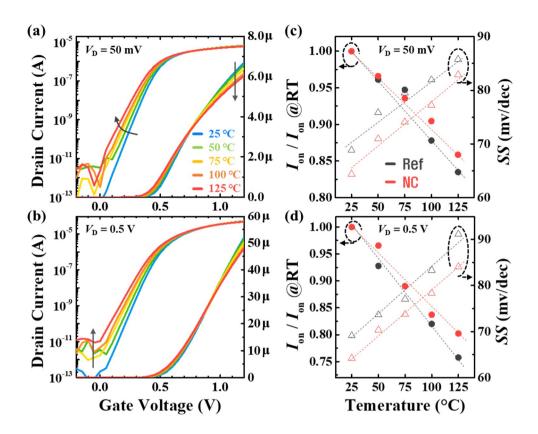

| Figure 5.8 | 3. (a) and (b) Transfer curves (linear and saturation region) of NS GAA                                                                                                   |

|            |                                                                                                                                                                           |

|            | NCFET at various operating temperatures (25°C ~ 125°C). (c) and (d) $I_{on}$                                                                                              |

|            | NCFET at various operating temperatures (25°C $\sim$ 125°C). (c) and (d) $I_{\rm on}$ / $I_{\rm on}$ at room temperature (RT) and SS (linear and saturation region) of NS |

|            |                                                                                                                                                                           |

### Chapter 1

### Introduction

### 1.1 Power and Area Scaling Challenges

In 1965, Gordan Moore reported that the number of transistors in an integrated circuit (IC) chip is doubling every year, as shown in **Figure 1.1**(a) [1]. Although the doubling interval has been extended to 2-years [**Figure 1.1**(b)] [2], the complementary metal oxide semiconductor (CMOS) device has been continuously scaled down, thus increasing the clock speed [3]. In 1974, Robert Dennard proposed a constant field scaling law, and accordingly the design parameters of metal-oxide-semiconductor field-effect transistors (MOSFETs) has been shrunk with the scaling factor [4]. Nonetheless, fundamental physical limits gradually hampered device scaling. As illustrated in **Figure 1.2**(a), the frequency growth trend due to device scaling down

broke down in the middle of the 2000s [3]. Particularly, in the conventional planar MOSFET architecture, the short channel effect (SCE), in which the source/drain junction becomes closer as the gate length increases, hence weakening the channel controllability of the gate, has severely degraded the device properties [5-7]. As depicted in Figure 1.2(b), the power density increased rapidly as the device density of integrated circuit (IC) chips increased rapidly, and further scaling of supply voltage  $(V_{\rm DD})$  became challenging as a result of increasing standby power density caused by SCE [8]. It is required to guarantee a sufficient on/off current ratio within a given  $V_{\rm DD}$ in order to scale down  $V_{\rm DD}$  while increasing performance, which is how CMOS devices have been developed. As indicated in **Figure 1.3** [9], strained silicon (90-nm node) was introduced utilizing SiGe source/drain to enhance the on-current  $(I_{on})$  in planar MOSFETs [10]. The continuous reduction of gate oxide thickness in accordance with Dennard's scaling law has resulted in an increase in gate leakage current, leading to the introduction of a high-κ metal gate (HKMG) in the 45nm node [11]. Due to the low thermal budget of high-k, the advent of HKMG brought a replacement metal gate process at the same time. Despite these attempts, continued gate length scaling required an ever-increasing degree of gate controllability. Eventually, for further length scaling at the 22-nm node, a multi-gate structure, represented by Fin field-effect transistor (FinFET), has been implemented [6, 12-14]. FinFETs, in which a narrow Fin-shaped channel is covered by a gate, can have better

electrostatic controllability, and are currently being applied to mass manufacturing at nodes as small as sub-5nm [15, 16]. However, from the same perspective, rather than a tri-gate structure, a gate-all-around (GAA) structure in which the gate wraps around the channel in all directions can enhance the gate-controllability ultimately, which is being researched extensively as a platform for the sub-3nm node [17-29].

**Figure 1.1.** Trend lines of the number of components in integrated circuit introduced by Moore: (a) Doubling every year [1] and (b) Doubling interval increased to 2 years [2].

**Figure 1.2.** (a) Clock frequency [3] and (b) power dissipation trend [8] of logic device.

Figure 1.3. Development of CMOS device from planar to 3D Fin structure [9].

### 1.2 Nanosheet Gate-All-Around FETs

#### 1.2.1 Gate-All-Around FETs

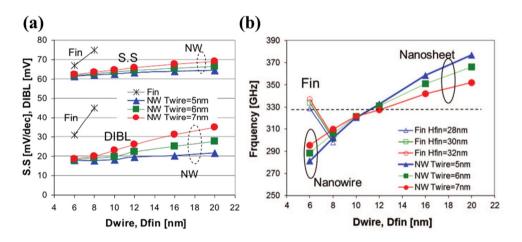

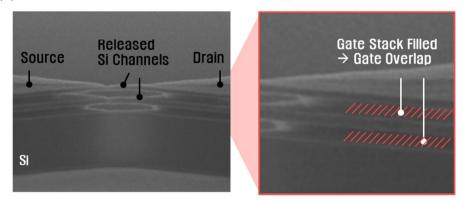

According to international roadmap for devices and systems (IRDS) 2021 (Figure 1.4), the trend of CMOS devices is eventually towards gate-all-around MOSFETs (GAAFET) [30]. As depicted in Figure 1.5(a), a cylindrical nanowire (NW) structure, where the gate electric field is concentrated to the channel, is optimal for achieving the highest electrostatic controllability [29]. Accordingly, numerous research groups have investigated NW GAAFETs [17-20, 26-28]. IRDS 2018 estimated that verticaltype NW GAAFET would be implemented in the 1.5nm node in 2028. [31]. Although the vertical NW GAA structure offers higher area scaling through pillar-structured channel patterning, due to numerous fabrication issues, notably the difficulty of the self-aligning process [27], the prediction of vertical GAA was eliminated in IRDS 2021 [30]. On the other hand, the NW GAA structure of the horizontal type is regarded desirable due to its compatibility with the existed FinFET process with the exception of the channel release process [17-20].

| 2021   | 2022           | 2025    | 2028      | 2031        | 2034        |

|--------|----------------|---------|-----------|-------------|-------------|

| G51M30 | G48M24         | G45M20  | G42M16    | G40M16/T2   | G38M16/T4   |

| "5"    | "3"            | "2.1"   | "1.5"     | "1.0 eq"    | "0.7 eq"    |

| i7-f5  | i5-f3          | i3-f2.1 | i2.1-f1.5 | i1.5e-f1.0e | i1.0e-f0.7e |

| FinFET | finFET<br>LGAA | LGAA    | LGAA      | LGAA-3D     | LGAA-3D     |

| finFET | finFET         | LGAA    | LGAA      | LGAA-3D     | LGAA-3D     |

| Oxide  | Oxde           | Oxde    | Oxde      | Oxide       | Oxide       |

Figure 1.4. Device architecture roadmap for future logic devices [30].

**Figure 1.5.** (a) Subthreshold swing (SS) / drain-induced-barrier-lowering (DIBL) and (b) frequency of GAAFETs according to the nanosheet width [29].

### 1.2.2 Nanosheet GAAFETs

As can be recognized by the development process of FinFETs evolving toward a higher Fin aspect ratio [32-34], current drivability must be adequately guaranteed in

order to improve device performance. For satisfying the current requirements, there has been a demand for vertically-stacking of horizontal NWs; unfortunately, the performance increase as stacking of NW channels is restricted by the increase in parasitic resistance and capacitance. In addition, as shown in **Figure 1.6**(a), as the aspect ratio of the device increases, the channel width between layers varies due to the etch slope; hence, the current does not increase proportionally to the number of stacked channels [**Figure 1.6**(b)]. Eventually, as a future logic device architecture alternative for FinFET, a vertically-stacked nanosheet (NS) was introduced to achieve sufficient current drivability along with greater gate-controllability [21-25, 29]. **Figure 1.7** compares the effective width ( $W_{eff}$ ) of aggressively scaled FinFETs and various types of NS GAAFETs [21], which claims that a single stacked NS structure is considered to obtain the largest current drivability in a limited active width.

In CPU blocks, circuit components with various performances are required, which are co-integrated on one wafer. The requirement is satisfied by the tuning of current drivability, implemented by the number of Fin in FinFET technology. However, the multiple Fin scheme has disadvantages; firstly, it can only achieve discrete current quantity fundamentally, and secondly, the increase of cell area is unavoidable due to the constant Fin pitch. In the case of NS GAAFETs, on the other hand, continuous current drivability can be provided by patterning the NS width as required.

Although there are numerous challenges, such as parasitic resistance and capacitance issues, as well as process difficulties, in terms of electrostatic controllability and current drivability, a vertically-stacked horizontal NS GAAFET is considered to be the most optimal device for the structure of the next-generation CMOS device. However, as illustrated in **Figure 1.8** [also in **Figure 1.5**(a)], the gate controllability is fairly deteriorated as increasing  $W_{NS}$ ; that is, electrostatic controllability and the current drivability is trade-off relation. Therefore, for the nanosheet technology to be applied to the future logic device moving toward further length scaling, a higher-level of EOT engineering is necessary.

**Figure 1.6.** (a) Schematic image of simulated stacked-GAAFET. (b) Simulated current characteristics according to the number of stacked channels.

**Figure 1.7.** Optimum GAA structure for high current drivability ( $\sim W_{\rm eff}$ ) considering the active width (RX.W) [21].

**Figure 1.8.** (a) SS- $I_D$  of NS GAAFET with regard to nanosheet width ( $W_{NS}$ ). (b) Electron density along the channel of NS GAAFET w/  $W_{NS}$  = 25 and 75 nm.

### 1.3 Negative Capacitance FETs

### 1.3.1 Negative Capacitance in Ferroelectric Materials

In 1976, Rolf Landauer reported that the capacitance of ferroelectric materials can be negative [35]. Ferroelectric materials have spontaneous polarization due to their non-centrosymmetric crystal structure, which maintains a permanent dipole even in the absence of an electric field. His theory is based on the thermodynamic Landau model [36-38], where the ferroelectric free-energy (F) is expressed as follows.

$$F/t_r = \alpha P^2 + \beta P^4 + \gamma P^6 - E_r P$$

1.1

where  $t_F$ ,  $E_F$  and P represent thickness, electric field and polarization of ferroelectric material. The relationship between the ferroelectric electric field and polarization can be established In Equation 1.1, by determining the point at which the value of the derivative of F with respect to P becomes zero (stable point).

$$E_{\rm F} = 2\alpha P + 4\beta P^3 + 6\gamma P^5$$

, when  $\frac{\partial F}{\partial P} = 0$  1.2

**Figure 1.9**(a) illustrates the free-energy landscape as a function of polarization for a ferroelectric material according to the Landau model (Equation 1.1) [39]. It has a double well shape, where the two stable energy states mean polarization up and down, respectively. **Figure 1.9**(b) depicts the ferroelectric *P-E* curve (Equation 1.2)

calculated by differentiating the free-energy with respect to polarization, also known as the Landau S-curve [39]. The spontaneous polarization is either positive or negative (or 0) at E = 0 and polarization switching occurs in an electric field above the coercive electric field ( $E_{\rm C}$ ), which indicates that the charge in the energy well surpasses the energy barrier shown in the **Figure 1.9**(a). Remarkably, an unstable region with a negative curvature between the two energy wells exists, which implies negative capacitance (NC) region: the region with a negative slope in the S-curve since the capacitance is proportional to dP/dE [40].

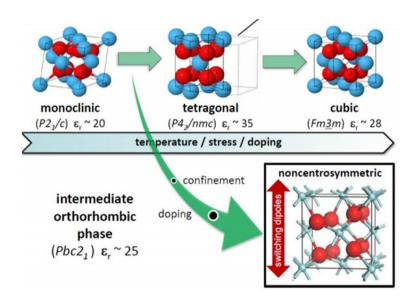

In the past, researches on ferroelectricity in perovskite-structured materials such as BaTiO [41, 42], PZT [43, 44], and polymer-based materials [45, 46] were predominantly reported. Since the discovery of ferroelectricity in CMOS-friendly and thickness-scalable HfO in 2011 [47], a significant amount of research has been undertaken on nonvolatile memory [48-52] and NC transistors [53-65] utilizing HfO-based ferroelectric material. The ferroelectricity of HfO stems from a noncentrosymmetric polycrystal phase [66, 67]. **Figure 1.10** explains the polycrystal phase transition of HfO, exhibiting ferroelectricity in the intermediate orthorhombic phase (o-phase) [68]. The crystal phase transition of HfO is induced by heat and stress and is promoted with the help of dopants such as Si, Al, and Zr. Among the different doped-HfO materials, Zr-doped HfO (HZO) has been attracting attention since its o-phase crystallize temperature is relatively (~500°C) [69] as well as the ferroelectricity

has been reported at an extremely scaled thickness of ~1 nm [70].

**Figure 1.9.** (a) Double-well free-energy landscape and (b) Polarization (P) - electric field (E) relationship of ferroelectric material [40].

**Figure 1.10.** Non-centrosymmetric intermediate phase (orthorhombic phase) of polycrystalline HfO for ferroelectricity [68].

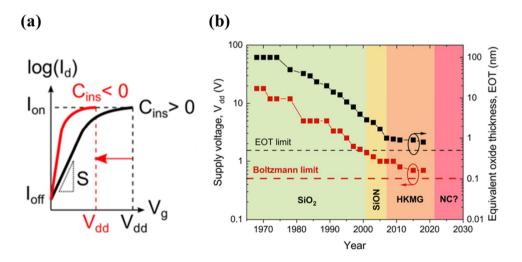

### 1.3.2 Negative Capacitance for Steep Switching Devices

The aforementioned NC effect of ferroelectric materials has the potential to overcome the limits of MOSFETs when used to CMOS technology. The subthreshold swing (SS) of a MOSFET is defined as the amount of gate voltage ( $V_G$ ) required to change the drain current ( $I_D$ ) 10 times in the subthreshold region: the inverse slope of  $\log_{10}I_D$  -  $V_G$  curve in the subthreshold region, reflecting how abruptly on-off switching occurs.

$$SS = \left(\frac{\partial \log_{10} I_{D}}{\partial V_{G}}\right)^{-1} = \frac{\partial V_{G}}{\partial \psi_{s}} \times \frac{\partial \psi_{s}}{\partial \log_{10} I_{D}} = m \times n$$

1.3

where,  $\psi_s$  represents surface potential of silicon.

As seen in Equation 1.3, SS is determined by how much surface potential changes with  $V_G(m)$  and how much drain current varies with surface potential (n). By voltage dividing of oxide capacitance and semiconductor capacitance connected in series, m is represented as  $(1+C_{ox}/C_{dm})$ , which cannot be less than 1 because  $C_{ox}$  has a positive value. In the case of n, since the number of carriers injected from the source to the channel is governed by the Boltzmann statistics, it cannot be reduced below a certain value. By substituting the  $I_D$  of subthreshold region into n, one can obtain n = 2.3 kT/q, which is limited to 60 mV/dec at 300 k, thus the SS of a MOSFET fundamentally cannot be less than 60 mV/dec at room temperature. In order to overcome the Boltzmann constraint (limitation of "n"), numerous devices with a novel transport

mechanism, such as tunnel-FETs utilizing band-to-band tunneling of pin diodes [71], feedback-FETs using positive feedback loops of n-p-n-p diodes [72], and i-MOS utilizing impact ionization of p-i-n diodes [73], have been extensively studied. Although TFET can exhibit superior SS and on/off ratio theoretically, its  $I_{\rm on}$  is several decades below that of MOSFETs, leaving it unsuitable for use as high-performance logic devices. Feedback-FET cannot respond to high-speed operation, while i-MOS requires high  $V_{\rm DD}$  for breakdown, as well as has reliability issues. In addition, above devices are not applicable for highly-scaled CMOS technology due to the difficulty in self-aligned junction formation.

In 2008, Sayeef Salahuddin suggested a FET utilizing the NC effect [74], which contains the concept of enabling m < 1 by employing a NC material in the gate oxide of MOSFET [67]. He demonstrated that the NC effect in the MOSFET causes the amplification of the surface potential by the applied voltage amplification ( $\partial \psi_s / \partial V_G > 1$ ) through the mathematical calculations using the Landau model. As shown in **Figure 1.11**(a), negative capacitance FET (NCFET) enables  $V_{DD}$  scaling with the same performance, since it has steep SS and current drivability similar to that of the existing MOSFET, which is the simplest method for power scaling [67]. Since [74], numerous studies on the understanding of NCFET and demonstration of NCFETs with HfO-based ferroelectric material have been published. [53-65]. NCFET with CMOS compatible HfO-based material can be easily implemented to the existing

logic device structure such as FinFET, featuring high current drivability due to the same carrier injection mechanism as conventional MOSFET; consequently, being regarded as the most promising candidates among other emerging next generation logic devices such as TFET, feedback-FET and i-MOS. NCFET is being evaluated as a solution to extend  $V_{\rm DD}$  and equivalent oxide thickness (EOT) scaling of CMOS devices, which has stalled since the middle of the 2000s due to the Boltzmann limit and increasing gate leakage current [**Figure 1.11**(b)].

**Figure 1.11.** (a) Schematic transfer characteristics of MOSFETs with positive / negative capacitance. (b)  $V_{\rm DD}$  and EOT scaling trend [67].

### 1.3.3 Stable NC vs. Sub-thermionic SS

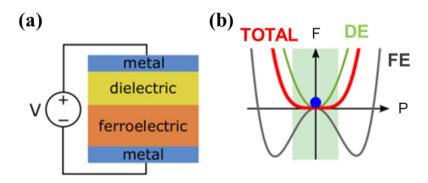

However, the NC region claimed by the simple thermodynamic Landau model is thermodynamically unstable because it exists on the maximum of free-energy as shown in Figure 1.9(a). Charge can exist in two energy minima in a ferroelectric material; hence, only polarization switching is seen above the  $E_C$ , leading to the memory hysteresis of the ferroelectric FET's  $I_D$ . That is, NC cannot be accessed in a stand-alone ferroelectric capacitor. Therefore, it is necessary to answer the questions of whether NC exists and whether it is actually possible to be utilized. Several groups have tried to experimentally observe the NC of ferroelectric materials [39, 75-78]. Michael Hoffmann [39] has calculated a double-well free-energy landscape from the voltage and current measured in the resistor for applied transient voltage pulses using a ferroelectric capacitor including a second dielectric layer and a series-connected resistor. The second dielectric and external resistor used in this experiment delay the charge screening of the electrode for voltage pulses. The phenomenon observed when metal charge screening is slower than polarization switching in fast measurement is referred to as the transient NC effect [39, 67]. However, it is only a transient observation which eventually ends up in positive capacitance with a hysteresis loop due to the instability of the NC region. Since the transient NC involves polarization switching, it generates hysteresis in transfer characteristics [53-56, 79] and requires a great amount of voltage or time; thus, the direct observation of NC using transient NC nature still does not answer whether NC can be applied to logic devices.

On the other side, research has been performed on the thermodynamically stabilization NC [67, 80, 81]. NC stabilization in previous studies means the introduction of a series-connected positive capacitor (dielectric). They argue that the total capacitance of dielectric + ferroelectric can be positive even in the NC region of the ferroelectric as following description. The free-energy ( $F_d$ ) of a dielectric material is a quadratic function of the charge with the coefficient inversely proportional to the capacitance ( $F_d = Q/2C^2$ ). Therefore, the total free-energy ( $F_t$ ) of the system [**Figure 1.12**(a)] in which the ferroelectric material following the landau model (Equation 1.1) and the dielectric are connected can be expressed as follows.

$$F_{t} = F_{f} + F_{d} = \left(\alpha t_{f} + \frac{t_{d}}{2\varepsilon_{o}\varepsilon_{d}}\right)P^{2} + t_{f}\beta P^{4} + t_{f}\gamma P^{6} - VP$$

1.4

, where  $\varepsilon_0$ ,  $\varepsilon_d$  and  $t_d$  represents vacuum permittivity, relative permittivity and thickness of dielectric. The free-energy landscape of total system along with that of ferroelectric and dielectric are illustrated in **Figure 1.12**(b) [67]. Here, the curvature of the total free-energy near P=0 is determined by the second-order coefficient in Equation 1.4: capacitance of the series-connected dielectric ( $t_d$  and  $\varepsilon_d$ ), the landau second-order constants ( $\alpha$ ), and  $t_f$ . The total free-energy can be stabilized near P=0 while the ferroelectric is in NC region only if the second-order coefficient of Equation 1.4 is

positive, which is satisfied when the dielectric capacitance is adequately small. However, in advanced CMOS technologies utilizing high- $\kappa$  dielectric, interfacial layer (IL) SiO<sub>2</sub> is indispensable to reduce interfacial trap density ( $D_{it}$ ) and it must be extremely thin (~several angstrom) for EOT scaling, which is contrary to the requirement of a series-connected dielectric for stable NC [81]. Furthermore, stabilized NC cannot be realized in the real devices due to the screening effect by trapped charges [39].

Meanwhile, the criterion for achieving a stable NC in MOS system with a ferroelectric layer can be expressed in a capacitance form as,

$$|C_{\text{FE}}| < C_{\text{MOS}} = (C_{\text{IL}}^{-1} + C_{\text{Si}}^{-1})^{-1}$$

1.5

where,  $C_{\rm FE}$ ,  $C_{\rm MOS}$ ,  $C_{\rm IL}$  and  $C_{\rm si}$  represents the capacitance of ferroelectric layer, MOS system, IL and Si, respectively. In addition, the capacitance condition for subthermionic SS (< 60 mV/dec) in NCFET can be expressed as,

$$|C_{\text{\tiny FF}}| > |C_{\text{\tiny II}}|$$

from

$$SS = 60 \text{ mV/dec} \times \left(1 + \frac{C_{\text{Si}}}{(C_{\text{IL}}^{-1} + C_{\text{FE}}^{-1})^{-1}}\right)$$

1.7

Here, since the  $C_{Si}$  of Equation 1.5 is negligible in the inversion region, the criterions of Equation 1.5 and Equation 1.6 are incompatible. Although there surely is a window

for satisfying both conditions in the depletion region, where  $C_{\rm Si}$  is quite small, little design space exists for the entire operating voltage including the inversion region. Consequently, the sub-thermionic SS claimed by conventional NCFETs is difficult to be implemented in practically [82]; thus, recent researches on NCFET focuses on the performance enhancement through stable capacitance boosting using the NC effect of ferroelectric material [83]. They aim at employing a high- $\kappa$  with a larger permittivity, hence enhancing SCE immunity through near-60 mV/dec SS and enabling performance boosting by improved  $I_{\rm on}$ .

**Figure 1.12.** (a) Schematic of dielectric (DE)-ferroelectric (FE) series capacitor for NC stabilization. (b) Corresponding free-energy landscapes [67].

#### 1.4 Scope and Organization of Dissertation

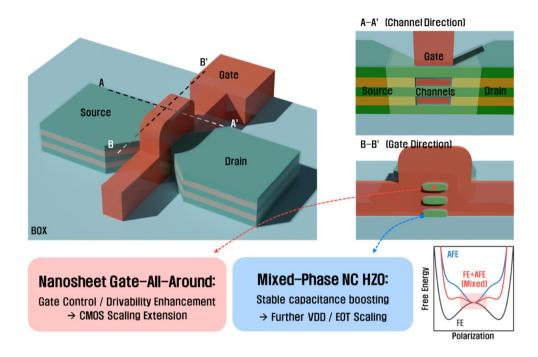

This thesis focuses on the design of NC material for stable capacitance boosting for low-power and high-performance logic device and the fabrication of the stacked NS GAA structure utilizing it. To overcome the constraints of previous research described in Subsection 1.3.3, optimization of a stable NC HZO and application of NC material to the ultimate advanced logic technology, stacked NS GAAFET for the first time.

In Chapter 2, the concept of stable NC material using mixed-phase HZO proposed in this research and the NS GAA NCFET with optimized HZO are described.

Chapter 3 describes the process of optimizing NC materials experimentally using ferroelectric capacitors and silicon-on-insulator (SOI) planar NCFETs.

Chapter 4 describes the fabrication process for NS GAA NCFET, which is the ultimate objective of this study, and provides a solution for issues in gate-first process.

Electrical characteristics of fabricated NS GAA NCFET are estimated in Chapter 5, which includes DC performance enhancements in fabricated NS GAA NC device. The comparison to other reported NCFETs is also presented, which verifies the superiority of demonstrated NS GAA NCFET in terms of hysteresis-free, steep-SS and high current drivability.

## Chapter 2

## Stacked NS GAA NCFET with Ferroelectric-Antiferroelectric-Mixed-Phase HZO

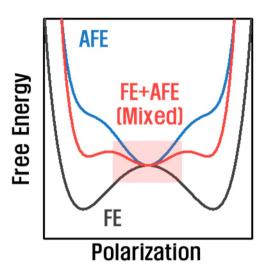

#### 2.1 Mixed-Phase HZO for Capacitance Boosting

As mentioned in Subsection 1.3.3, a focus on stable capacitance boosting, not an achieving sub-60mV/dec SS is essential to utilize the NC effect of ferroelectric materials in logic devices, since the sub-thermionic SS with a thermodynamically stabilized NC is not applicable. This dissertation focuses on an NCFET with a ferroelectric-antiferroelectric-mixed-phase HZO, which utilizes NC effect for capacitance boosting in operating regime, and attempts to experimentally validate its

effect at the FET level.

Figure 2.1 shows the free-energy landscape of ferroelectric, antiferroelectric and ferroelectric-antiferroelectric-mixed-phase materials. Since the NC region located near P = 0 of the ferroelectric material is thermodynamically unstable, it is impossible to statically access it. On the other hand, the curvature of the free-energy landscape of the ferroelectric-antiferroelectric-mixed phase material has a positive value near P = 0 (NC region of ferroelectric) [84]. In other words, free-energy of mixed-phase preserves a thermodynamically stable state in the NC region of ferroelectric, which is similar to the result of NC stabilization by employing a series-connected dielectric explained in Subsection 1.3.3. However, it is significant compared to the capacitance matching method through the interfacial layer (IL) SiO<sub>2</sub> in that it enables the introduction of an EOT-scalable NC material.

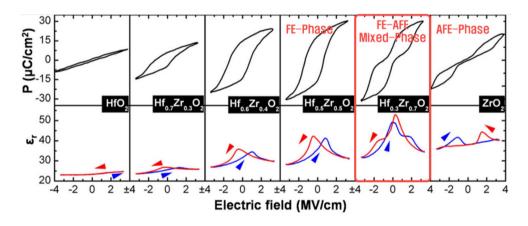

As demonstrated in **Figure 2.2**, the polarization characteristic of HZO varies with the composition rate (*x*) of Zr, where the pure HfO exhibits paraelectric property; HZO with increased *x* displays ferroelectric hysteresis loop; and pure ZrO shows antiferroelectricity [85]. From the **Figure 2.2**, it is expected that the ferroelectricantiferroelectric-mixed-phase material proposed in this research can be obtained in Zr-rich HZO.

**Figure 2.1.** Free-energy landscape of ferroelectric (FE), antiferroelectric (AFE) and FE+AFE mixed phase material [84].

**Figure 2.2.** Polarization-electric field (*P-E*) characteristics of HZO with regard to the Hf / Zr composition [85].

#### 2.2 NS GAA NCFET using Mixed-Phase HZO

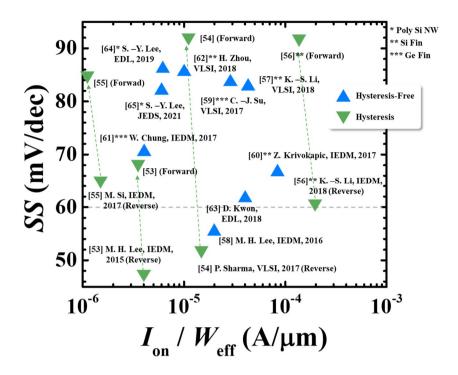

Since the discovery of ferroelectricity in CMOS-compatible doped HfO, extensive researches on HfSiO (HSO) or HZO-based NCFETs of various topologies have been conducted [53-65]. **Figure 2.3** shows the SS and on-current ( $I_{ON}$ ) (at  $V_{DD} = 0.65$  V) benchmarks of reported NCFETs. Multiple reports claim to have demonstrated a SS of sub-60 mV/dec based on minimum point SS [54, 56, 57, 59, 61, 62, 64, 65] or exhibit a steep slope with ferroelectric counter-clockwise hysteresis [53-56], which implies the transient NC through polarization switching as described in Subsection 1.3.3. In addition, numerous studies merely validate the effect of NC HZO on the 2D planar structured transistor [53-55, 58, 63], demonstrating poor current drivability, and do not verify its applicability to the advanced logic structure.

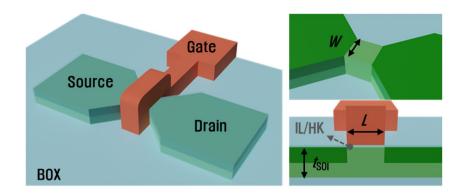

This research proposes and demonstrates a stacked NS GAA NCFET utilizing a ferroelectric-antiferroelectric mixed-phase HZO material as illustrated in **Figure 2.4**. A hysteresis-free stabilized operation and high performance is to be confirmed by applying the mixed-phase HZO to the vertically-stacked nanosheet FET which requires a higher-level of EOT scaling for CMOS extension. Dissertation aims to validate that the capacitance boosting effect of HZO enhances *SS* and *I*<sub>on</sub> compared to the reference high-κ NS GAAFET fabricated in the same manner. For the first time, crystalline Si NS GAA structured NCFET is demonstrated, evaluating the feasibility

Figure 2.3. SS-I<sub>on</sub> benchmarks of reported NCFETs [53-65].

**Figure 2.4.** Proposed device: stacked NS GAAFETs with ferroelectric-antiferroelectric mixed-phase HZO for low-power and high-performance logic technology.

## Chapter 3

## **HZO ALD Stack Optimization**

This chapter describes the optimization process of negative capacitance thin films using ferroelectric-antiferroelectric mixed-phase HZO. In order to evaluate the capacitance boosting effect induced by the NC effect, metal-ferroelectric-interlayer-silicon (MFIS) capacitors are fabricated for multiple HZO stacks and their gate capacitance properties are evaluated.

Prior to employing the HZO thin film optimized through MFIS and metal-ferroelectric-metal (MFM) capacitor experiments to the NS GAA NCFETs, planar NCFETs using silicon-on-insulator (SOI) are fabricated to verify the improvement of current characteristics in MOSFETs. The processes were carried out mainly in the inter-university semiconductor research center (ISRC), Seoul National University, while some parts of fabrication were requested to the other fabs. By validating the

characteristics of SOI Planar NCFETs with floating body structures identical to those of NS GAA structures, it would be possible to predict the characteristics of HZO thin films when applied to actual NS GAA structures, as well as to compare the features with NS GAA NCFETs that will be processed later.

## 3.1 Metal-Ferroelectric-Interlayer-Silicon (MFIS) / MFM Capacitors

#### 3.1.1 Fabrication of MFIS Capacitors

A common approach for validating the ferroelectricity of a ferroelectric thin film is to measure the displacement current for voltage pulses of metal-ferroelectric-metal (MFM) capacitor. However, as stated previously, it is impossible to observe unstable negative capacitance in a single MFM capacitor [39]. In addition, since it is necessary to examine the effect of the ferroelectric layer on the structure of the actual device to be fabricated, a metal-ferroelectric-interlayer-silicon (MFIS) capacitor was fabricated and compared with the existing HfO (high-κ dielectric) MOS.

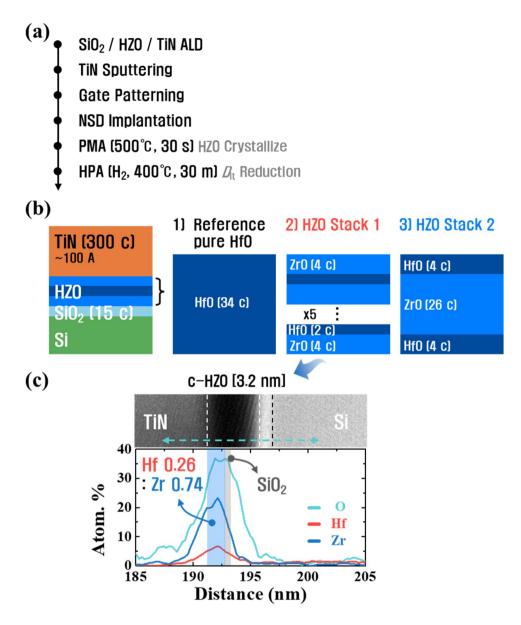

The manufacturing sequence of MFIS capacitor is as follows [**Figure 3.1**(a)]. (1) An interfacial layer (IL)  $SiO_2$  (15 cycles) followed by several Hf(Zr)O stacks were deposited on the  $p^-$  bare wafer through atomic layer deposition (ALD): As a high- $\kappa$  control, 34 cycles of pure HfO were deposited; and two kinds of Zr-rich HZO stacks

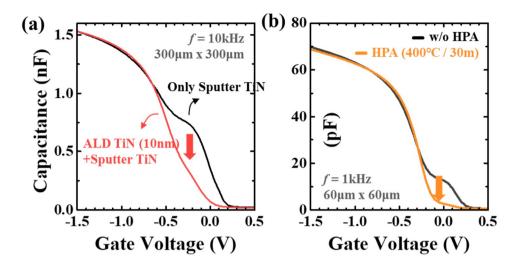

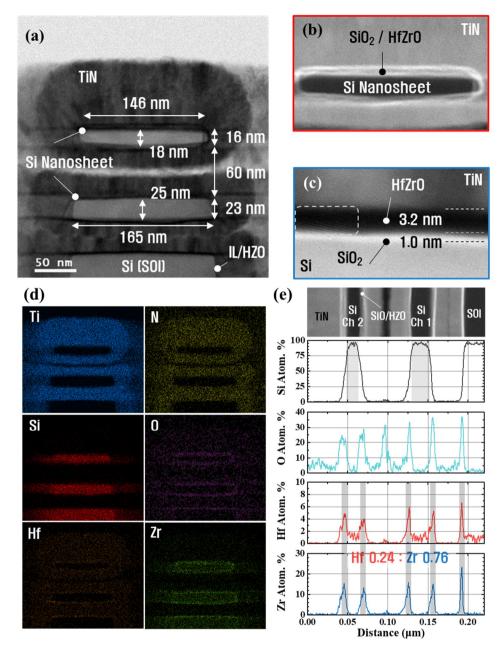

(HZO stack 1, HZO stack 2, totaling 34 cycles) were deposited to adopt a ferroelectric-antiferroelectric mixed-phase, as illustrated in Figure 3.1(b). In the case of HZO stack 1, ZrO and HfO were deposited in a nanolaminate structure that was repeatedly deposited in 4 cycles and 2 cycles, respectively, and in the case of HZO stack 2, it was deposited in a superlattice form in the order of HfO 4 cycle-ZrO 26 cycle-HfO 4 cycle. (2) Subsequently, ALD TiN deposition was carried out for two reasons: i) If TiN is directly deposited on a insulator as a gate material via sputtering, the high-κ layer is damaged resulting in the increase of trap states. Therefore, the ALD TiN 300 cycle (100 A) was deposited preferentially as a sputtering damage barrier. Figure 3.2(a) compares the gate capacitance characteristics of MOS (TiN-HfO-SiO<sub>2</sub>-p<sup>-</sup> Si) capacitors with and without barrier ALD TiN deposition. Since the ISRC TiN sputtering power is quite high (5000 W), the capacitance hump in the depletion region induced by the high-κ thin film's trap is apparently exhibited without the barrier metal. On the other hand, it is confirmed that the hump in the depletion region is significantly alleviated with barrier TiN ALD of 300 cycles (100 A). ii) Since the to-be-fabricated device is a GAA structure with a suspended channel, the gate metal between the vertically stacked channels must be filled using the chemical vapor deposition (CVD), which cannot be fulfilled by physical vapor deposition (PVD). (3) TiN gate electrode material was deposited through sputtering. (4) Patterning was performed through photo lithography and inductively coupled plasma-reactive ion etching (ICP-RIE) dry etching using Cl<sub>2</sub> gas. (5) To assess the inversion region characteristic of the MFIS capacitor, a self-aligned n<sup>+</sup> doping was conducted under the condition of As<sup>+</sup>, 20 keV,  $2 \times 10^{15} \text{ cm}^{-2}$  using a medium current ion implanter. (6) Post metal annealing (PMA) process (500°C, 30 seconds) was performed using rapid thermal annealing (RTA) for HZO crystallization and dopant activation. (7) Lastly, in order to minimize the interfacial trap density  $(D_{ii})$ , high pressure annealing (HPA) was carried out in an H<sub>2</sub> atmosphere (18 Bar, 400°C, 1hour). **Figure 3.2**(b) illustrates the capacitance-voltage (C - V) characteristics of a MOS (TiN-HfO-SiO<sub>2</sub>-p<sup>-</sup> Si) capacitor with and without HPA process. The lowering of the C-V curve's hump in MOS capacitor with HPA confirms that the  $D_{it}$  was greatly reduced due to the elimination of the Si - SiO<sub>2</sub> interfacial dangling bond. Transmission electron microscopy (TEM) image confirms that the stack was deposited with IL (SiO<sub>2</sub>) 1.0 nm / HZO 3.2 nm, while Energy-dispersive X-ray spectroscopy (EDS) analysis verifies the composition ratio (Hf 0.26 : Zr 0.74), which has been designed to produce Zr-rich mixed-phase HZO [Figure 3.1(c)].

**Figure 3.1.** (a) Summarized process flow of MFIS capacitors. (b) Schematic image of MFIS capacitors fabricated on p- Si. Two types of HZO ALD stacks along with reference pure HfO ALD stack are depicted. (c) TEM / EDS analysis of HZO stack 1.

**Figure 3.2.** (a) Capacitance-Voltage (C-V) characteristics of MOS (TiN-HfO-SiO<sub>2</sub>-p<sup>-</sup>Si) capacitor with different TiN gate stack (ALD TiN + sputter TiN and only sputter TiN). (b) C-V characteristics of MFIS capacitor with and without HPA process.

#### 3.1.2 Electrical Characteristics of MFIS / MFM Capacitors

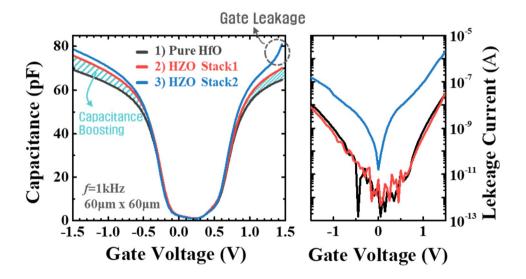

Gate capacitance characteristics of the reference HfO and two types of ferroelectric thin films (HZO stack 1 and HZO stack 2) were electrically measured for validating the capacitance enhancement by NC effect of the fabricated MFIS capacitors. Capacitance measurements were conducted using an Agilent B1500A capacitance

measuring device (CMU). Dimension of capacitor was  $60 \times 60 \mu m^2$  and the capacitance measuring frequency was 1 kHz. Both inversion capacitance and accumulation capacitance can be measured owing to n<sup>+</sup> doping. As can be seen in Figure 3.3(a), accumulation and inversion capacitance enhancements were validated in HZO stack 1 and HZO stack 2 compared to the pure HfO. The capacitive effective oxide thickness (CET) was calculated to be 1.79 nm for pure HfO, 1.64 nm for HZO stack 1 and 1.57 nm for HZO stack 2. Since TEM [Figure 3.1(c)] proved the thickness of IL to be 1.0 nm, the dielectric constant of ALD Hf / HZOs can be calculated. As summarized in Table 3.1, it was determined that the dielectric constant of pure HfO was 14.5, and that of HZO stack 1 / 2 was 20.4 / 22.5, respectively, where the dielectric constant improvement was 40% in HZO stack 1 and 55% in HZO stack 2. Here, note that the accumulation capacitance is not saturated yet at gate voltage  $(V_G)$ = -1.5 V, due to the large area of capacitor; thus, the calculated CET could be underestimated.

However, the leakage current-gate voltage (*I-V*) graph [**Figure 3.3**(b)] reveals that the gate leakage current of HZO stack 2 is quite large. In general, it is known that the poly crystallization temperature of ZrO is slightly lower than that of HfO [86, 87]. Since the same PMA temperature (500°C, 30 seconds) was applied to all three samples in this experiment, it can be concluded that poly-crystallization was greatest in the case of HZO stack 2 deposited in the form of superlattice, leading to the

increase of leakage. Accordingly, the capacitance was distorted in the inversion region, as indicated by the *C-V* characteristic [**Figure 3.3**(a)]. Considering the actual device area and operating voltage, the HZO stack1 with an acceptable leakage level was chosen for the NC thin film.

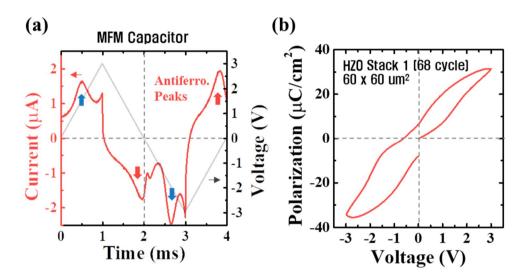

In order to examine the polarization characteristics of the HZO stack, MFM capacitor was fabricated to measure displacement current for triangular voltage pulses. In the case of MFM capacitor, if the thin film is too thin, leakage current becomes too large to distinguish the the displacement current due to polarization. Therefore, HZO stack 1 was deposited twice as thick as the prior MFIS experiment, in 68 cycles with the identical HfO / ZrO composition. For pulse measurement, an Agilent B1500 waveform generator/fast measurement unit (WGFMU) was utilized. In order to validate the polarization characteristic of the ferroelectric film, a triangle-shaped voltage pulse was applied to the top electrode. As depicted in Figure 3.4(a), a triangular  $V_G$  pulse with a rising / falling period of 1 ms was applied, and the resulting current was measured in the bottom electrode to exclude the external parasitic capacitance of pulse generator. The measured current consists of leakage current and displacement current which is separated into a paraelectric capacitive component and a polarization component induced by ferroelectric switching. In ferroelectric materials, current peaks due to polarization switching are observed when the voltage increases at a positive voltage above coercive voltage (polarization up) and when the

voltage decreases at a negative voltage (polarization down), whereas the current peak is not observed in the opposite cases (V decrease in positive and V increase in negative region) as it maintains the polarization state. However, as indicated by the red arrow in the voltage / current - time diagram [Figure 3.4(a)], it can be confirmed that the current peak appears in the case of V decrease in positive and V increase in negative region, indicating the antiferroelectric nature. Calculating the polarization by integrating the current over time results in the graph presented in Figure 3.4(b), which confirms that ferroelectricity and antiferroelectricity coexist in HZO stack 1.

**Figure 3.3.** (a) Gate capacitance characteristics of various MFIS stacks: 1) Pure HfO/2) HZO stack 1 3) HZO stack 2. Capacitance enhancements in HZO stacks are noticeable. (b) Gate leakage currents of three ALD stacks.

**Table 3.1.** Dielectric constants of high- $\kappa$  films extracted from accumulation capacitances ( $V_G$ =-1.5 V).

|               | CET [nm] | t <sub>IL</sub> [nm] | CET <sub>HK</sub> [nm] | Dielectric<br>Constant |

|---------------|----------|----------------------|------------------------|------------------------|

| 1) Pure HfO   | 1.79     |                      | 0.79                   | 14.5                   |

| 2) HZO Stack1 | 1.64     | 1.0                  | 0.64                   | 20.4                   |

| 3) HZO Stack2 | 1.57     |                      | 0.57                   | 22.5                   |

**Figure 3.4.** (a) Displacement current measurement of MFM capacitor (HZO stack1) for triangular voltage pulse. (b) *P-V* curve obtained from (c), showing ferroelectric-antiferroelectric-mixed characteristic.

#### 3.2 SOI Planar NCFETs

#### 3.2.1 DC Measurements

Prior to applying the HZO thin film which was setup through MFIS and MFM capacitor experiments to the NS GAA architecture, a planar NCFET was fabricated using a silicon-on-insulator (SOI) wafer in order to validate the current improvement in the FET. Since the NS GAAFET has a body floating structure, an SOI wafer was employed, and the device dimensions [channel width (W) and gate length (L)] were defined by photolithography for the convenience of the fabrication process. The schematic image and physical parameters of the fabricated device are shown in **Figure 3.5** and **Table 3.1**. As a control for the NCFET with HZO stack 1, a MOSFET with a pure HfO high- $\kappa$  gate dielectric was fabricated in the same manner. The detailed device fabrication method including the source / drain (S/D) 1st doping and self-aligned (S-A) S/D doping shown in **Table 3.1** is similar to the NS GAA NCFET process, which will be covered in Chapter 4.

Figure 3.5. Schematic image of SOI planar NCFET.

Table 3.2. Physical parameters and process conditions of SOI planar NCFET

| Physical Parameters |                    | <b>Process Conditions</b> |                                          |  |  |

|---------------------|--------------------|---------------------------|------------------------------------------|--|--|

| $t_{ m SOI}$        | 100 nm             | НК                        | Pure HfO / HZO stack 1                   |  |  |

| W                   | $0.5\sim 50~\mu m$ | S/D 1st Doping            | $As^{+}/2\times10^{15} cm^{-2}$          |  |  |

| L                   | $0.5\sim 50~\mu m$ | S-A S/D Doping            | $P^+ / 2 \times 10^{15} \text{ cm}^{-2}$ |  |  |

| $t_{ m IL}$         | 1.0 nm             |                           |                                          |  |  |

| $t_{ m HK}$         | 3.2 nm             |                           |                                          |  |  |

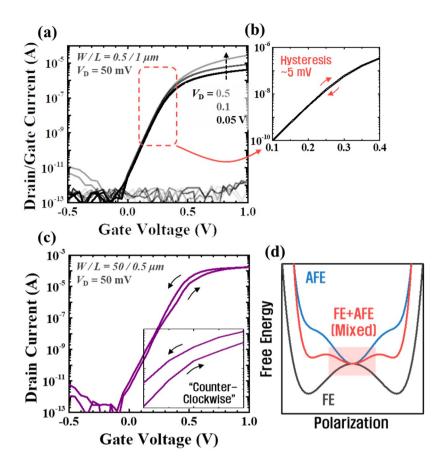

Figure 3.6(a) illustrates the drain current  $(I_D)$  -  $V_G$  characteristics of the SOI planar NCFET under different drain voltages  $(V_D s)$ . The enlarged transfer curve [Figure 3.6 (b)] demonstrates that the majority of HZO devices exhibit stable characteristics with clockwise hysteresis of 5mV or less (nearly hysteresis-free) thanks to the mixed-phase stable NC material. However, as shown in Figure 3.6(c), few devices had an uncommon counterclockwise hysteresis loop, with the steeper subthreshold swing (SS) in the reverse-swept  $I_D$ . The memory effect (counter-

clockwise hysteresis) of ferroelectric (FE) material induced by polarization switching arises above the coercive electric field ( $E_{\rm C}$ ), which requires much higher  $V_{\rm G}$  than the operating VG of a typical logic device [48]. Nonetheless, the counterclockwise hysteresis in the very low gate voltage sweep region of **Figure 3.6**(c) might be attributed to the extremely low energy barrier for polarization switching in the FE+AFE energy landscape [**Figure 3.6**(d)]. The steeper SS in the reverse sweep direction also indicate the effect of polarization switching as described in the Subsection 1.3.3.

**Figure 3.6.** (a) Transfer characteristics of most SOI planar NCFET (b) enlarged graph of (a), showing nearly hysteresis-free feature. (c) Transfer characteristic of few devices and enlarged graph (inset), showing counterclockwise hysteresis. (d) Free-energy landscape of ferroelectric (FE), antiferroelectric (AFE), and mixed phase (FE + AFE).

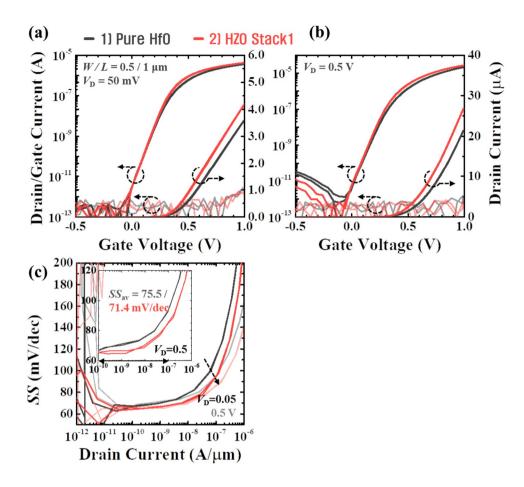

**Figure 3.7**(a) and (b) show the  $I_D / I_G - V_G$  characteristics (at  $V_D = 50$  mV and 0.5 V, respectively) for pure HfO and HZO stack 1 device with W / L =  $0.5 / 1 \mu m$ . It was confirmed that the gate current had a low value of  $10^{12}$  A or less in the  $V_G \sim 1$  V sweep range in both devices. When the  $V_G$  is set to identical off-current ( $I_{off}$ ) in the linear  $V_D$  (50 mV) condition, it can be observed that the current in the HZO stack 1 device is enhanced from near the threshold voltage  $(V_{th})$  compared to the pure HfO device. The gate-induced-drain-leakage (GIDL) current of saturation  $V_D$  (0.5 V) condition is different as can be seen in Figure 3.7(b), which is thought to be due to the misalignment occurred in the non-self-aligned S/D doping (S/D 1st doping). SS –  $I_D$  plot [**Figure 3.7**(c)] confirms the SS enhancement by capacitance boosting of HZO stack 1. A 3-decades average SS ( $W_{\text{eff}}$ -normalized  $I_{\text{D}}$  range from  $10^{-10}$  A/µm, where  $I_{\rm D}$  is sufficiently larger than  $I_{\rm G}$ , to  $10^{-7}$  A/ $\mu$ m) for reference and HZO device was 75.5 mV/dec and 71.4 mV/dec, respectively.

On the other hand, the transfer characteristics of devices with relatively large W ( $W = 10 \mu m$ ) [Figure 3.8(a)] exhibits somewhat extraordinary behavior: the  $I_D$  of HZO device was enhanced from near the  $V_{th}$  as similar to Figure 3.7(a), but  $I_D$  of reference device overtakes that of HZO device as the  $V_G$  increase. The phenomenon can be explained as follows. The on-resistance ( $R_{ON}$ ) component of MOSFET is shown in Figure 3.8(b) and Equation 2.1.

$$R_{\rm ON} = R_{\rm CH} + R_{\rm External} = R_{\rm CH} + (R_{\rm EXT} + R_{\rm SD} + R_{\rm CNT})$$

2.1

, where  $R_{\text{CH}}$  and  $R_{\text{External}}$  refers to the channel and external resistance, respectively, and the  $R_{\text{External}}$  consists of S/D extension resistance ( $R_{\text{EXT}}$ ), doped S/D resistance ( $R_{\text{SD}}$ ) and contact resistance ( $R_{\rm CNT}$ ). The  $R_{\rm CH}$  become comparable to  $R_{\rm External}$  in the high VG region, leading to the increase of  $R_{\text{External}}$ 's dominance. Particularly in the case of a device with a wide W the channel resistance is relatively low (since the size of the pad where the contact is placed is designed to be the same regardless of W), thus the influence of  $R_{\text{External}}$  is more significant. Therefore, the behavior depicted in **Figure 3.8**(a) can be considered because the  $R_{\text{External}}$  of the pure HfO device is less than that of the HZO device. This interpretation is consistent with the explanation of the GIDL difference in Figure 3.7(b). As described in Figure 3.8(c), the total resistance of the FET according to 1/overdrive voltage  $(1/V_{OV})$  was calculated from the  $I_D$ - $V_G$ characteristics of linear  $V_D$ . At the point where  $1/V_{OV} = 0$  ( $V_{OV}$  goes to infinity),  $R_{CH}$ can be ignored; that is, y-intersect of the graph can be approximately regarded as the  $R_{\text{External}}$ . The  $R_{\text{External}}$  of reference pure HfO device (0.11 k $\Omega$ ) was revealed to be significantly lower than that of HZO stack1 device (0.3 k $\Omega$ ). Nevertheless, given that the HZO device's current is larger in the relatively low  $V_{\rm G}$  region, it can be confirmed that the current improvement due to the capacitance boosting of fabricated HZO devices is an intrinsic performance enhancement regardless of the  $R_{\text{External}}$ .

**Figure 3.7.** (a) and (b) Transfer characteristics of SOI planar NCFET with HZO stack1 ( $V_D = 50 \text{ mV}$  and 0.5 V, respectively) compared with reference pure HfO device. (c) Subthreshold swing (SS)- $I_D$  curve extracted from (a) and (b).

**Figure 3.8.** (a) Transfer characteristics of NCFET and reference MOSFET with relatively large channel width ( $W = 10 \mu \text{m}$ ). (b) Series resistance of MOSFET (c) External resistance extraction by  $1/V_{\text{OV}}$  method.

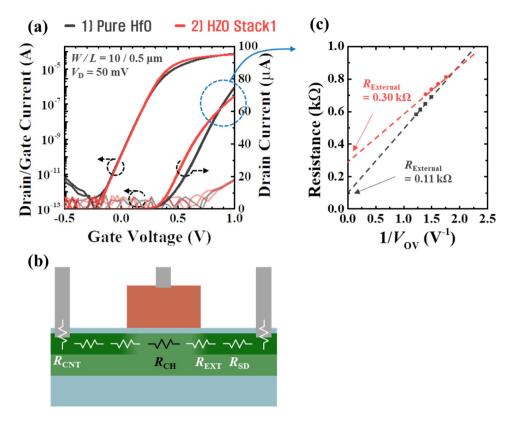

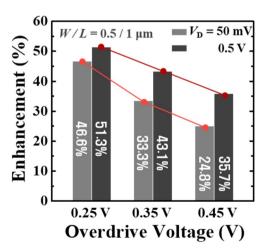

Figure 3.9 demonstrates that the HZO enhances the current by 25 to 50% compared to the reference HfO device in the linear ( $V_D = 50 \text{ mV}$ ) and saturation ( $V_D = 0.5 \text{ V}$ ) regions, and under various overdrive voltage ( $V_{OV}$ ) conditions ranging from 0.25 to 0.45 V. Here,  $V_{OV} = 0.45 \text{ V}$  and  $V_{OV} = 0.35 \text{ V}$  corresponds to the operation  $V_G$  considering the  $V_{th}$  and  $V_{DD}$  of 2.1nm-node and 0.7nm-eq-node high performance (HP)

device presented in IRDS 2021 [30], respectively. It can be noticed that the current improvement is larger as the smaller the  $V_{\rm OV}$ ; this is due to the fact that i) the  $V_{\rm th}$  of the HZO device is slightly smaller, thus difference of  $I_{\rm DS}$  in low  $V_{\rm OV}$  (near the subthreshold region) is amplified, and ii) the impact of  $R_{\rm External}$  increases at the high  $V_{\rm OV}$ . Consequently, it is possible to anticipate ever-improving current characteristics in the on state through the optimized processes including junction control and contact formation. A Schottky barrier NCFET using silicide S/D has been proposed to minimize the  $R_{\rm External}$  in the gate-first process [88]. The output characteristic [**Figure 3.10**] confirms the current gain of HZO device in the entire  $V_{\rm D}$  region compared to the reference pure HfO devce.

**Figure 3.9.** On-current enhancement in SOI planar NCFET compared to the reference HfO device at linear and saturation  $V_D$  conditions.

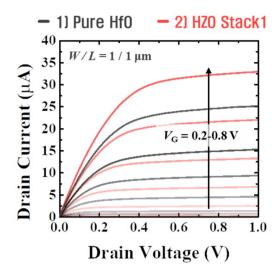

**Figure 3.10.** Output characteristics  $(I_D-V_D)$  of SOI planar NCFET compared to pure HfO device.

#### 3.2.2 Direct Capacitance Measurements

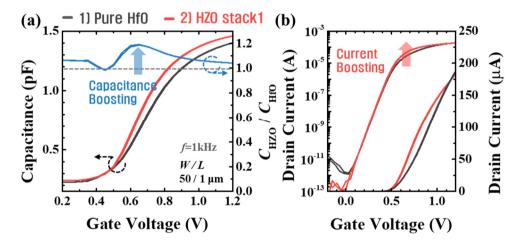

The SS and current enhancement confirmed in the Subsection 3.2.1 result from the capacitance boosting effect of the mixed-phase HZO. In order to verify the capacitance enhancing effect of the mixed-phase HZO at the FET level, direct gate capacitance measurements in the FET were performed. For the sufficient resolution of small-signal capacitance measurement, the planar SOI FETs with relatively large width ( $W = 50 \mu m$ ) were used. As depicted in **Figure 3.11**(a), the gate capacitance of HZO device has been enhanced compared to the pure HfO device. The capacitance enhancement of the HZO device over the HfO device is expressed as ( $C_{\rm HZO}$  /  $C_{\rm HfO}$ ),

where the  $C_{\rm HZO}$  and  $C_{\rm HfO}$  represents the capacitance of HZO device and HfO device, respectively. It should be emphasized that the capacitance boosting at near / above threshold voltage is exhibited. It results from the electric field dependence of permittivity in mixed-phase HZO, as opposed to the dielectric whose permittivity is constant. Figure 3.11(b) exhibits the transfer characteristic of the same devices as Figure 3.11(a), which clearly demonstrates the current boosting at the near / above  $V_{\rm th}$  region.

**Figure 3.11.** (a) Capacitance-voltage characteristics (y1) directly measured from SOI planar FETs (Pure HfO and HZO stack 1) and the capacitance ratio (y2). (b) Transfer characteristics of the same device as (a).

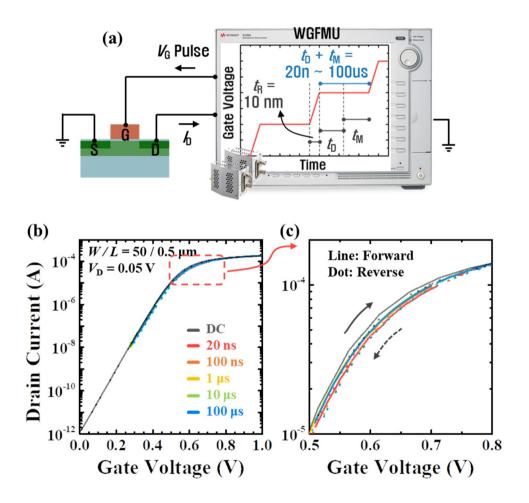

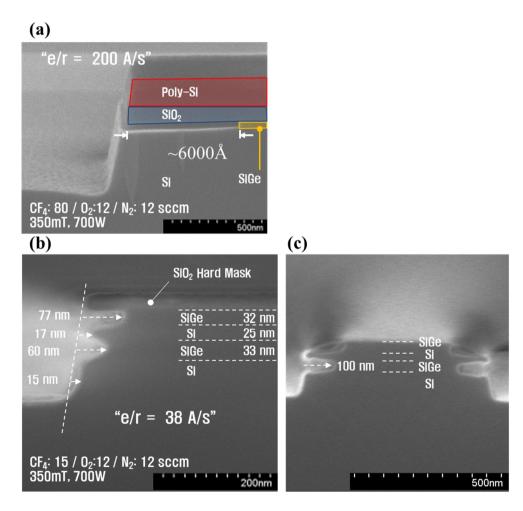

#### 3.2.3 Speed Measurements