#### 저작자표시-비영리-변경금지 2.0 대한민국

#### 이용자는 아래의 조건을 따르는 경우에 한하여 자유롭게

• 이 저작물을 복제, 배포, 전송, 전시, 공연 및 방송할 수 있습니다.

#### 다음과 같은 조건을 따라야 합니다:

저작자표시. 귀하는 원저작자를 표시하여야 합니다.

비영리. 귀하는 이 저작물을 영리 목적으로 이용할 수 없습니다.

변경금지. 귀하는 이 저작물을 개작, 변형 또는 가공할 수 없습니다.

- 귀하는, 이 저작물의 재이용이나 배포의 경우, 이 저작물에 적용된 이용허락조건 을 명확하게 나타내어야 합니다.

- 저작권자로부터 별도의 허가를 받으면 이러한 조건들은 적용되지 않습니다.

저작권법에 따른 이용자의 권리는 위의 내용에 의하여 영향을 받지 않습니다.

이것은 이용허락규약(Legal Code)을 이해하기 쉽게 요약한 것입니다.

Disclaimer 🖃

### 공학박사 학위 논문

# 캐패시터 방전 전류 Map을 이용한 선박용 DC 전력 시스템 보호

Protection of DC Shipboard Power System with Capacitor Discharge Current Map

2022 년 8월

서울대학교 대학원 전기·정보공학부

이승용

# 캐패시터 방전 전류 Map을 이용한 선박용 DC 전력 시스템 보호

지도 교수 설 승기

이 논문을 공학박사 학위논문으로 제출함 2022 년 8 월

서울대학교 대학원 전기·정보 공학부 이 승 용

이승용의 공학박사 학위논문을 인준함 2022 년 8 월

- 위원장 하정익 (인)

- 부위원장 설 승 기 (인)

- 위원 최성휘 (인)

- 위원 정일엽(인)

- 위원 김성민 (인)

# 초 록

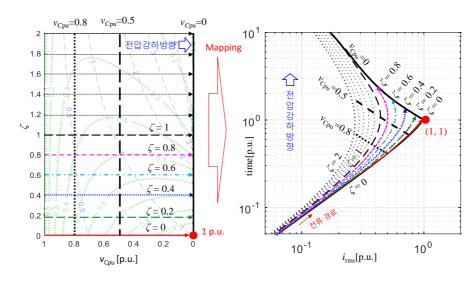

본 논문에서는 선박용 DC 전력시스템 내 단락 고장 발생 시, 캐패시터 방전 전류의 실효 값을 직관적이고 편리하게 참조할 수 있는 정규화된 캐패시터 방전 전류 Map 및 그 이용 방법을 제안한다. 이는 감쇠비(damping ratio)와 정규화된 캐패시터 전압에 따른 캐패시터 방전 I't Map 또는 정규화된 캐패시터 방전 시간-전류 특성(time-current characteristic, TCC) Map의 형태로 미리 계산되어 제공된다. 실제 값을 정규화 하거나 역으로 변환할 때는 R-L-C 등가 회로의 파라미터로 계산한 기준값(base value)을 통해 변환할 수 있다.

최근 선박 분야에서는 연료 효율 향상 및 환경 문제 개선을 위해 VSC(voltage source converter)를 적용한 전기 추진 방식을 다수 도입하고 있으며, 더 높은 효율을 위해 다수 VSC의 DC링크 캐패시터들을 연결한 DC 전력시스템이 등장하고 있다. 그런데 모든 전력시스템은 전기의 안전한 사용을 위해 적절한 보호 방식을 갖추어야 하고, 그 설계를 위해서는 먼저 단락 사고시의 고장전류 특성을 분석해야 한다. DC 전력시스템은 AC 전력시스템과 달리 캐패시터 때문에 고장 전류 계산이 복잡하므로, 분석시 IEC 61660-1 표준과 같은 주요 특징점 참조법 또는 컴퓨터를 이용하 수치해석법을 이용할 수 있다. 그러나 해당 표준에는 보호기기의 동작특성과 직접적인 비교를 할 수 있는 Pt값이나 시간-전류 특성에 대한 참조 데이터는 제시되어 있지 않으며, 수치해석적인 방법은 직관적인 수치를 제공해주지 못해 파라미터 수정시 반복적인 시뮬레이션을 통해 보호 특성을 확인해야 하는 단점이 있다. 따라서 기존 연구에서는 고장 전류 분석 및 보호 방식 설계시 점진적 반복법(iteration method)을 사용하였지만 본 논문에서 제안된 Map을 이용하면 감쇠비 별 캐패시터 전압에 따른 Pt값과 캐패시터 방전 전류의 시간-전류 특성을 직관적으로 파악할 수 있다. 특히 시간-전류 특성 그래프는 과전류 보호설계 시에 보편적으로 사용되는 표현방식으로, 기존 설계자들에게 좀 더 익숙한 접근이 가능할 것으로 기대된다.

본 논문에서는 초기 캐패시터 전압이  $V_0$ 인 단일 R-L-C 회로의 캐패시터 전압, 전류, 시간,  $P_t$ 에 대한 수식을 분석하여 각각을 기준값과 정규화된 항의 곱으로 표현할 수 있음을 보인다. 정규화된  $P_t$ 항은 감쇠비와 위상각의 함수로

나타낼 수 있는데, 활용도를 높이기 위해 위상각 대신 정규화된 캐패시터 전압으로 대체하여 캐패시터 방전 *l*<sup>2</sup>t Map으로 나타낼 수 있다. 추가적으로 r.m.s.(root-mean-square) 계산식의 정의를 이용하면, 캐패시터 방전 *l*<sup>2</sup>t Map과 시간 Map을 시간-전류 평면 상의 캐패시터 방전 시간-전류 특성 Map으로 나타낼 수 있다. 위의 과정을 거쳐 해석적으로 도출된 캐패시터 방전 전류 Map의 정확도를 검증하기 위해 R-L-C 등가 회로에서의 시뮬레이션 및 퓨즈를 포함한 실험을 수행하였으며, 각각의 설계 예시를 제시하였다.

추가적으로 선박에서 적용되고 있는 DC전력시스템의 네트워크 형태에 대해서 분석한다. 버스와 피더의 임피던스 비율에 따라 차단시 선택성이 달라질 수 있음을 보이고, 가장 낮은 공진주파수를 기준으로 다수의 캐패시터와 버스 임피던스를 고장 피더에 대하여 단일 R-L-C 회로로 등가화할 수 있음을 보인다. 이를 선박용 DC전력시스템 축소모델을 기반으로 실험을 통해 검증한다.

**주요어**: 선박용 DC전력시스템, 단락 보호 시스템, 캐패시터 방전, 정규화, Pt Map, 시간-전류 특성 Map, 기준 값, 기준 점, 참조법

학 번 : 2017-38572

# 목 차

| 제 1장 서론                                                   | 1 |

|-----------------------------------------------------------|---|

| 1.1 연구의 배경                                                | 1 |

| 1.2 연구의 목적                                                | 4 |

| 1.3 논문의 구성                                                | 6 |

| 제 2장 선박용 DC 전력시스템의 단락 보호1                                 | 7 |

| 2.1 단일 VSC의 DC 측 단락 사고시 특성1                               | 7 |

| 2.2 DC 보호시스템 설계 시 고려사항 및 상용화 사례                           | 2 |

| 2.2.1 보호시스템의 개요                                           | 2 |

| 2.2.2 DC 보호시스템 설계시 고려 사항                                  | 4 |

| 2.2.3 상용화된 DC 보호시스템 사례                                    | 0 |

| 2.3 다수 캐패시터 및 개별 퓨즈 방식에 대한 기존 연구 4                        | 9 |

| 2.3.1 고속 퓨즈의 구조 및 동작 특성                                   | 9 |

| 2.3.2 다수 캐패시터 및 개별 퓨즈를 이용한 보호 방식5                         | 3 |

| 2.3.3 DC 보호시스템 상세 설계에 대한 기존의 연구5                          | 6 |

| 제 3장 정규화된 캐패시터 방전 <i>I²t</i> Map                          | 1 |

| 3.1 캐패시터 방전 특성식의 정규화                                      | 1 |

| 3.2 캐패시터 방전 <i>l</i> <sup>2</sup> t Map의 작성               | 7 |

| 3.3 I²t Map 기반의 보호 시스템 파라미터 설계                            | 4 |

| 제 4장 캐패시터 방전 시간-전류 특성 Map9                                | 6 |

| 4.1 캐패시터 방전 <i>l</i> <sup>2</sup> t Map의 시간-전류 특성 Map 변환9 | 6 |

| 4.2 시간-전류 특성 Map 기반 보호 시스템 파라미터 설계 1 0                    | 4 |

| 제 5장 선박용 DC 전력시스템 적용 시 고려사항1 1                            | 5 |

| 5.1 보호 시스템의 선택성을 확보하기 위한 설계 항목 1 1                        | 5 |

| 5.1.1 버스 내 VSC의 수 1 1                                     | 6 |

| 5.1.2 버스 임피던스와 피더 임피던스의 비율 및 고장 위치 고려 1 1                 | 9 |

| 5.1.3 피더 간 C-L-C 공진 억제 1 2                                | 2 |

| 5.1.4 퓨즈 용량 균등화 1 2                                       | 3 |

| 5.2 DC 전력시스템의 고장 피더 기준 등가회로화 1 2                          | 5 |

| 제 6장 결론 및 향후연구 | 1 | 3 | 8 |

|----------------|---|---|---|

| 6.1 결론         | 1 | 3 | 8 |

| 6.2 향후 연구      | 1 | 4 | 2 |

| 참고 무허          | 1 | 4 | 4 |

# 표 목차

| 표 2-1. 실제 선박용 DC전력시스템 1개 버스의 등가회로 파라미터 3 1                       |

|------------------------------------------------------------------|

| 표 2-2. 주요 직접 측정 보호 방식의 비교 [67] 3 5                               |

| 표 2-3. 다양한 전류센서의 특성 비교 [85] 3 7                                  |

| 표 2-4. DC전력시스템에 적용 가능한 차단기 비교                                    |

| 표 2-5. 주요 제조사의 위치 별 보호기기 및 방식                                    |

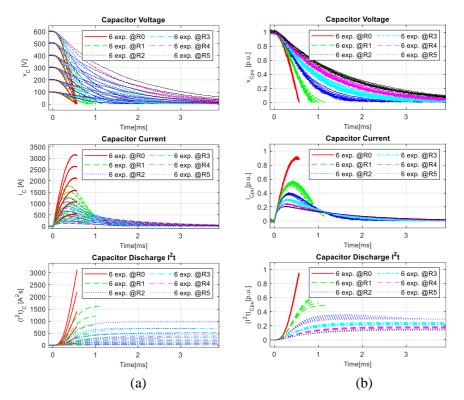

| 표 3-1. 가변저항 위치에 따른 등가 R-L-C 파라미터 및 감쇠비( $C=1~\mathrm{mF}$ ). 7 5 |

| 표 3-2. 초기 전압 변화에 따른 캐패시터 방전 $Pt$ 기준 값 $(C=1 \text{ mF})$ 7 5     |

| 표 3-3. 낮은 초기값을 설정했을 때의 수렴시까지의 반복 설계 프로세스 예시                      |

|                                                                  |

| 표 3-4. 높은 초기값을 설정했을 때의 수렴시까지의 반복 설계 프로세스 예시                      |

|                                                                  |

| 표 4-1. 가변저항 위치에 따른 등가 R-L-C 파라미터 및 감쇠비( $C' = 2 \text{ mF}$ )    |

|                                                                  |

| 표 4-2. 초기 전압 변화에 따른 캐패시터 방전 $Pt$ 기준 값 ( $C'=2$ mF) 1 0 8         |

| 표 5-1.선박용 DC전력시스템 내 선택차단성 확인을 위한 VSC 파라미터 예시                     |

|                                                                  |

| 표 5-2. 축소모델 파라미터 및 단락 위치별 외부 등가 파라미터1 3 2                        |

| 표 5-3. 축소모델 단락 시 최종 등가 파라미터 및 기준 값 계산 1 3 4                      |

# 그림 목차

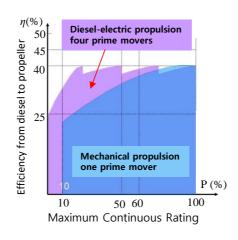

| 그림 1-1. 전기 추진과 기계식 추진의 효율 비교(Fuel to Propeller) [7] 2 |

|-------------------------------------------------------|

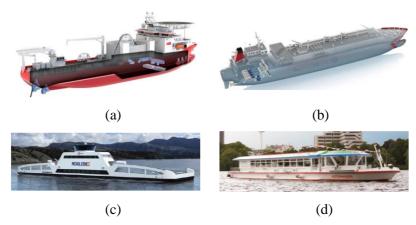

| 그림 1-2. 전기 추진 적용이 유리한 선박 예시 [3], [9], [10], [11] 3    |

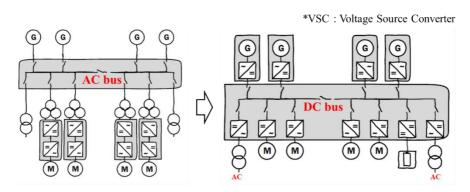

| 그림 1-3. 선박용 전력시스템의 변화(AC to DC)                       |

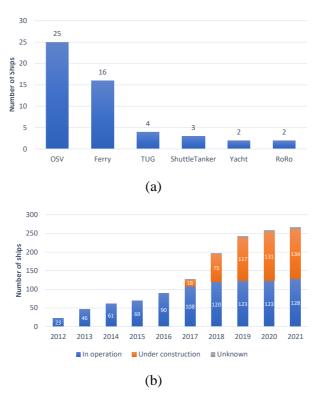

| 그림 1-4. 선박용 DC전력시스템 및 배터리가 적용된 선박 수5                  |

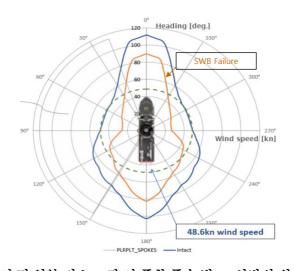

| 그림 1-5. 정상 시 및 일부 버스 고장 시 풍향·풍속 별 DP선박의 위치 제어         |

| 능력[24]6                                               |

| 그림 1-6. 방사형 AC 전력시스템의 보호기기 배치 예[34]9                  |

| 그림 1-7. 상용화된 선박용 DC전력시스템에서 보호기기의 배치1 1                |

| 그림 1-8. 전력변환 시스템에서의 주요 고장 부품 및 주요 스트레스 1 2            |

| 그림 1-9. IGBT의 치명적인 고장의 개요[39] 1 2                     |

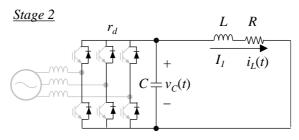

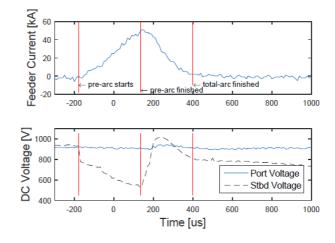

| 그림 2-1. 외부 단락사고시 정상 VSC 관점에서의 등가회로 및 사고 단계 별          |

| 주요 전류 경로1 9                                           |

| 그림 2-2. 외부 단락사고 시 단계 별 캐패시터 전압, 고장 전류, 고장 $I^2t$ 파형   |

| 예시1 9                                                 |

| 그림 2-3. 고장 1 단계 고장 전류 분석을 위한 단일 R-L-C 등가 회로 2 2       |

| 그림 2-4. 감쇠상수, 고유주파수, 감쇠고유주파수 간 관계 2 4                 |

| 그림 2-5. 고장 2단계의 주요 경로 2 7                             |

| 그림 2-6. 고장 3단계에서의 단락 전류 유입경로 2 8                      |

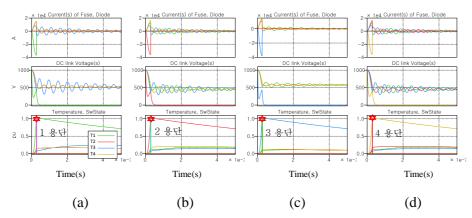

| 그림 2-7. 고장 단계 별 퓨즈 용단 모의 시험결과 2 9                     |

| 그림 2-8. 미 해군 선박의 DC전력시스템 구성도 및 고장지점 [12] 3 0          |

| 그림 2-9. 미 해군 선박 내 인공 단락시 고속 퓨즈 차단 실험결과 [12] 3 0       |

| 그림 2-10. 일반적인 전력시스템 보호 순서 [56] 3 3                    |

| 그림 2-11. 계전기, 차단기, 퓨즈 예시 [58]-[60]                    |

| 그림 2-12. DC 전력시스템에 사용 가능한 주요 차단기 형태 3 8               |

| 그림 2-13. 일반적인 DC 전력시스템 구성 4 0                         |

| 그림 2-14. ABB사의 DC전력시스템 구조[31]                         |

| 그림 2-15. ABB사 DC전력시스템의 방식 변화 [14] 4 4                 |

| 그림 2-16. Siemens 사의 VSC 내부 단락 발생시 단락 사고 보호 시스템[12]    |

| 그림 2-17. Siemens 반도체 차단기(ILC)의 구조 및 실험파형[12] 4 7                          |

|---------------------------------------------------------------------------|

| 그림 2-18. 고속 퓨즈의 내부 엘리먼트 구조                                                |

| 그림 2-19. 퓨즈의 용단 시간-전류 특성(TCC) 곡선 및 구간 별 설명 5 0                            |

| 그림 2-20. EATON사에서 제시한 퓨즈 용단 판별 방법[42] 5 1                                 |

| 그림 2-21. Mersen 사에서 제시한 퓨즈 용단 판별 방법[114] 5 2                              |

| 그림 2-22. 개별 퓨즈를 이용한 AC 역률 보상용 캐패시터 과전류 보호                                 |

| 방식[117] 5 3                                                               |

| 그림 2-23. 단락전류 시뮬레이션 및 퓨즈 용단여부 비교판별[15] 5 5                                |

| 그림 2-24. IEC 61660-1 고장 전류의 표준 근사함수 5 8                                   |

| 그림 2-25. Kim이 제안한 점진적 반복법을 이용한 추가 캐패시턴스 산정                                |

| 방식[46] 5 9                                                                |

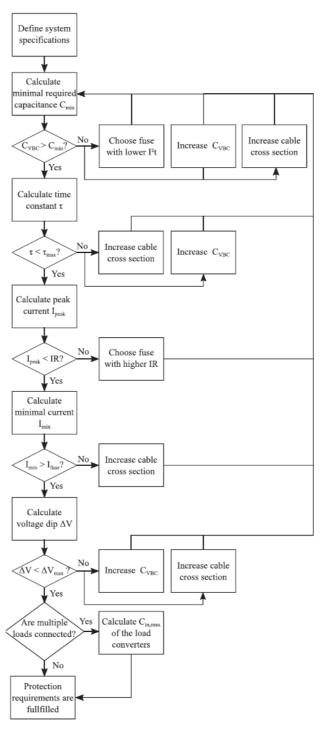

| 그림 2-26. Ravyts가 제안한 종합적인 퓨즈 기반 보호 방식 설계 순서도[47]                          |

|                                                                           |

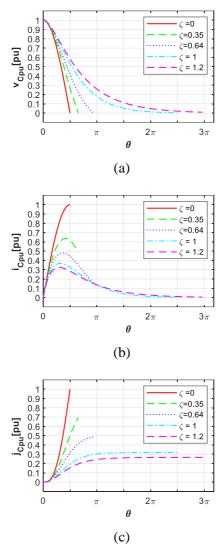

| 그림 3-1. 위상각에 따른 감쇠비 별 정규화된 그래프 7 3                                        |

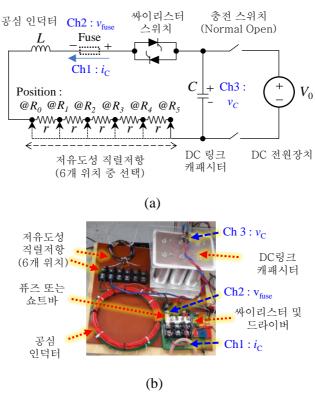

| 그림 3-2. 캐패시터 단락 실험 세트                                                     |

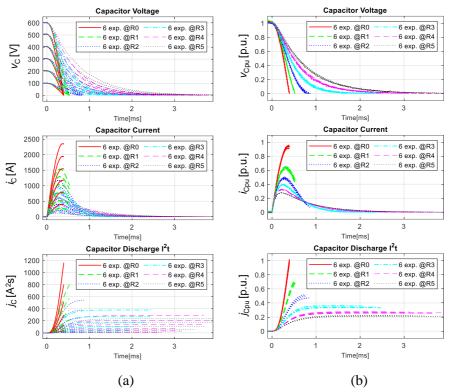

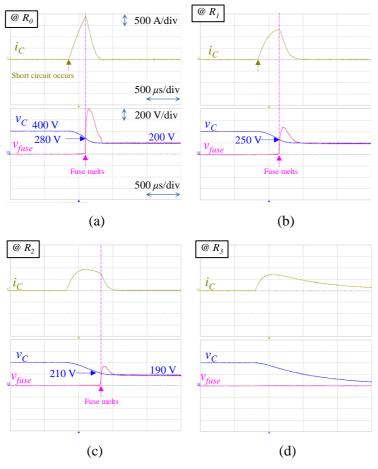

| 그림 3-3. 단일 R-L-C 회로의 단락시 캐패시터 방전 실험 결과( $C=1$ mF). 7 6                    |

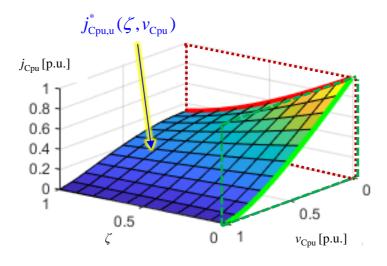

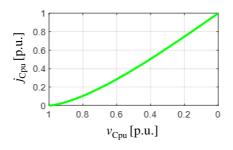

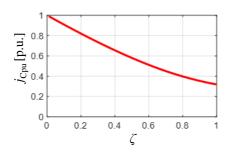

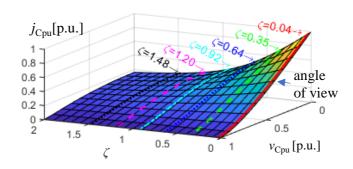

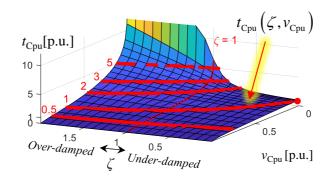

| 그림 3-4. 정규화된 캐패시터 방전 <i>I</i> <sup>2</sup> t Map(저감쇠 영역) 3D 곡면 7 8        |

| 그림 3-5. 비 감쇠인 경우( $\zeta$ =0)의 캐패시터 전압에 따른 $I$ - $t$ 의 크기                 |

| 그림 3-6. 감쇠비 간 삼각함수 관계 8 0                                                 |

| 그림 3-7. 저 감쇠시 1단계 종료시점 (vcpu=0)의 캐패시터 방전 I²t 크기 8 0                       |

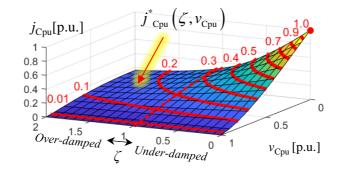

| 그림 3-8. 정규화된 캐패시터 방전 <i>I²t</i> Map(0≤ζ≤2) 3D 곡면 8 0                      |

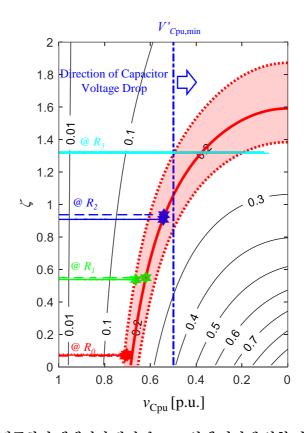

| 그림 3-9. 실험에 사용된 감쇠비 별 예상 $I$ t 의 곡면 상 경로 8 $1$                            |

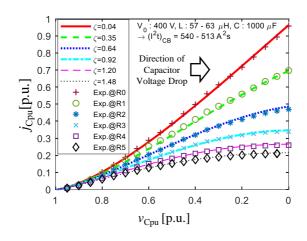

| 그림 3-10. 곡면의 $\zeta$ 축에서 바라본 예상경로와 실험값의 비교 ( $C=1$ mF). 8 1               |

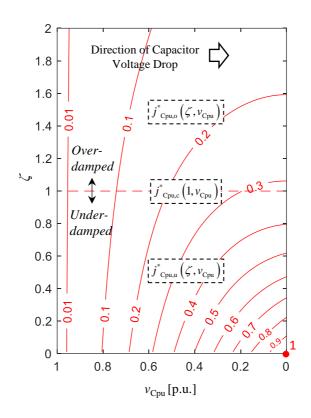

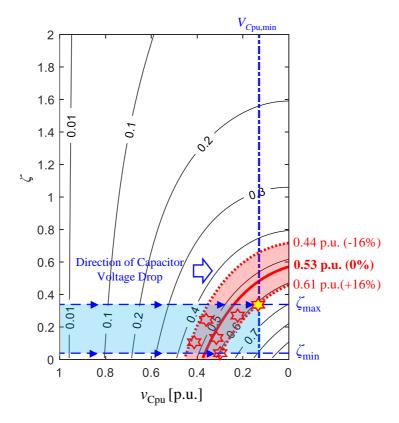

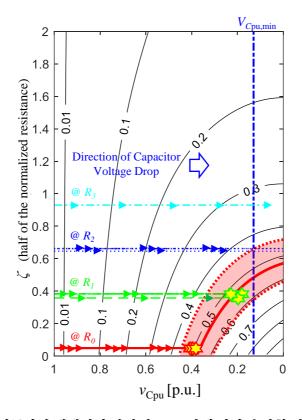

| 그림 3-11. 정규화된 캐패시터 방전 $I^2t$ Map( $0 \le \zeta \le 2$ ) - 2D 평면 등고선도. 8 2 |

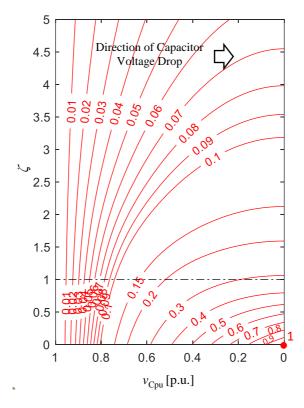

| 그림 3-12. 정규화된 캐패시터 방전 $I^2t$ Map $(0 \le \zeta \le 5)$ - 2D 평면 등고선도. 8 3  |

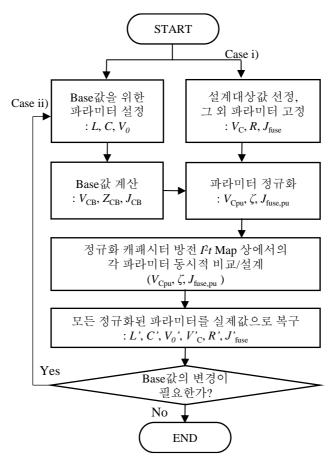

| 그림 3-13. 정규화된 캐패시터 방전 $P_t$ Map을 이용한 퓨즈 보호시스템                             |

| 설계과정 8 4                                                                  |

| 그림 3-14. 감쇠비 범위 및 최소 캐패시터 전압 지정시 퓨즈의 용단 12t 설계                            |

| 그림 3-15. 낮은 초기 캐패시턴스 값을 설정했을 때의 수렴시까지의 반복                    |

|--------------------------------------------------------------|

| 설계 프로세스 예시                                                   |

| 그림 3-16. 높은 캐패시턴스 초기값을 설정했을 때의 수렴시까지의 반복 설계                  |

| 프로세스 예시                                                      |

| 그림 3-17. 단일 R-L-C회로에서 퓨즈 실험(C=1 mF)                          |

| 그림 3-18. 정규화된 캐패시터 방전 $I^2t$ Map 상에 나타낸 실험 결과 ( $C=1$ mF)    |

| 9 4                                                          |

| 그림 3-19. 실험에 사용된 퓨즈 A ~ H                                    |

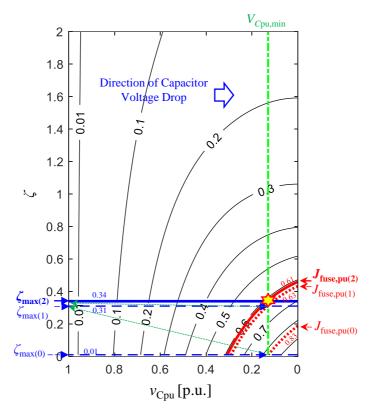

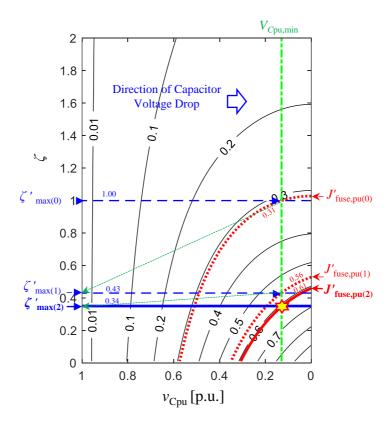

| 그림 4-1. 감쇠비 별 해당 캐패시터 전압에 도달하는 정규화된 시간 Map . 9 7             |

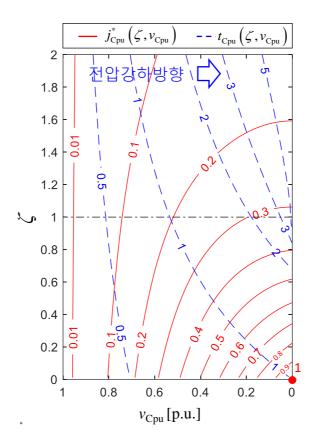

| 그림 4-2. 정규화된 캐패시터 방전 <i>I</i> -t 및 시간 Map - 2D 등고선도 9 8      |

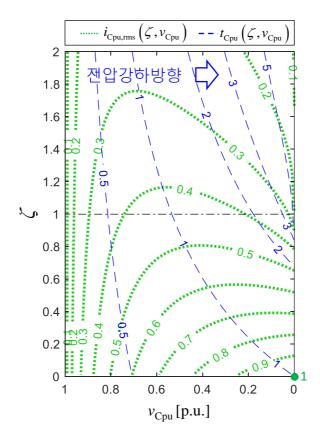

| 그림 4-3. 정규화된 캐패시터 방전 r.m.s. 전류 및 시간 Map – 2D 등고선도 9 9        |

| 그림 4-4. 시간-전류 평면에 사영된 정규화된 캐패시터 방전 전류 1 0 0                  |

| 그림 4-5. 정규화된 캐패시터 방전 시간-전류 특성 Map의 주요 특징 점 1 0 0             |

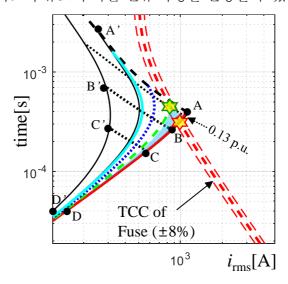

| 그림 4-6. 퓨즈 데이터시트 상에 표시된 실제 스케일 시간-전류 특성 Map의                 |

| 예시                                                           |

| 그림 4-7. 기준값 관련 파라미터 변경에 따른 시간-전류 특성 Map의 평행이동                |

| 예시103                                                        |

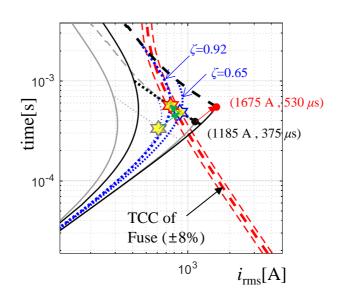

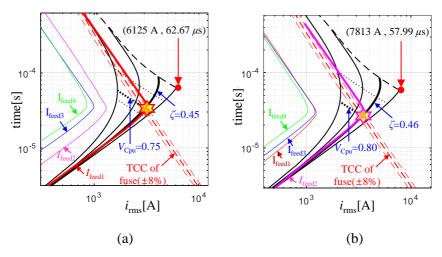

| 그림 4-8. 캐패시터 방전 시간-전류 특성 Map 및 퓨즈 설계 예시 1 0 5                |

| 그림 4-9. 예시 시간-전류 특성 Map의 캐패시턴스 2배 변경시 예상 평행이동                |

| 위치 및 퓨즈 용단 위치1 0 7                                           |

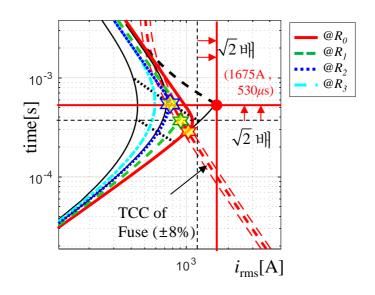

| 그림 4-10. 시간-전류 평면 상 퓨즈 용단 실험 결과( <i>C</i> = 1 mF) 1 0 8      |

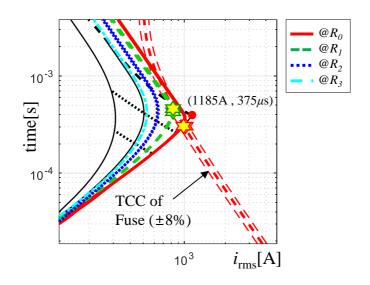

| 그림 4-11. 단일 R-L-C 회로의 단락시 캐패시터 방전 실험 결과(C' = 2 mF)           |

|                                                              |

| 그림 4-12. 단일 R-L-C회로에서 퓨즈 실험(C'=2 mF) 1 1 0                   |

| 그림 4-13. 정규화된 캐패시터 방전 $I^2t$ Map 상에 나타낸 실험 결과 ( $C' = 2$ mF) |

|                                                              |

| 그림 4-14. 시간-전류 평면 상 퓨즈 용단 실험 결과 ( <i>C</i> '=2 mF) 1 1 2     |

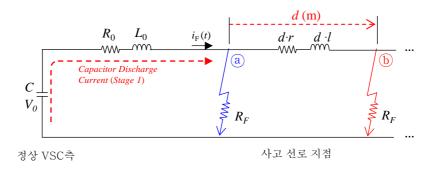

| 그림 4-15. DC 선로의 임의의 지점에서 사고시 등가 모델 1 1 3                     |

| 그림 4-16. 선로 내 고장지점 위치에 따른 고장전류 영역 및 퓨즈 특성 곡선과          |

|--------------------------------------------------------|

| 비교                                                     |

| 그림 5-1. 동일한 파라미터를 가진 N개 피더 중 한 곳(우측)에서 단락사고            |

| 발생시 등가회로1 1 6                                          |

| 그림 5-2. 버스 내 VSC 수에 따른 선택차단 가능범위 및 적용된 캐패시터 $P$        |

| 및 퓨즈 $I^2t$ 의 비율 $(J_{\mathrm{C}}/J_{\mathrm{fuse}})$  |

| 그림 5-3. 선박용 DC전력시스템 Demo룸 [15] 1 1 9                   |

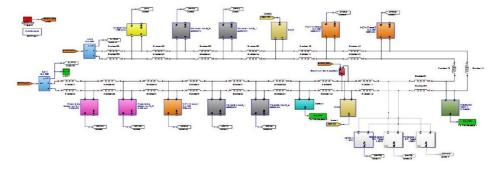

| 그림 5-4. 고장 전류 분석을 위한 시뮬레이션 모델 예시 [15] 1 1 9            |

| 그림 5-5. 버스 임피던스 $(Z_a)$ 와 피더 임피던스 $(Z_b)$ 크기에 따른 형태 차이 |

|                                                        |

| 그림 5-6. Star 형태 버스에서 각 위치 별 단락 시뮬레이션 1 2 1             |

| 그림 5-7. Cascade 형태의 버스에서 각 위치별 단락 시뮬레이션 1 2 2          |

| 그림 5-8. C-L-C 공진회로 1 2 2                               |

| 그림 5-9. Star 형태의 버스에서 작은 용량 퓨즈(3) 포함시 단락 시뮬레이션         |

|                                                        |

| 그림 5-10. Star 형태의 버스에서 동일 용량 퓨즈 포함시 단락 시뮬레이션           |

|                                                        |

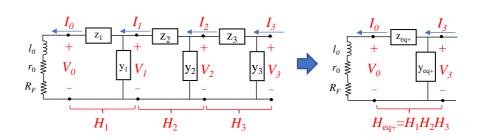

| 그림 5-11. 말단 지점 사고 발생시 Cascade 연결 회로의 등가회로화 1 2 5       |

| 그림 5-12. Cascade 형태의 버스에서 사고 지점 기준의 전달 행렬과 근시          |

| 행렬의 보드 선도 비교                                           |

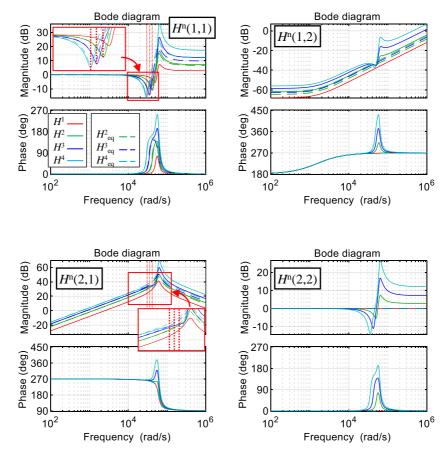

| 그림 5-13. 중간 지점 사고 발생시 등가회로화 1 3 0                      |

| 그림 5-14. 외부 등가 파라미터와 사고 피더의 임피던스를 고려한 최종               |

| 등가회로131                                                |

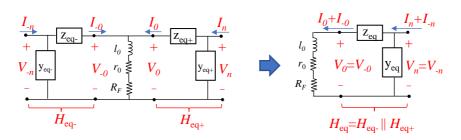

| 그림 5-15. 4개의 피더로 구성된 축소모델의 파라미터 및 단락 실험시 측정            |

| 위치132                                                  |

| 그림 5-16. 축소모델 단락 시 퓨즈 용단 실험 결과 1 3 3                   |

| 그림 5-17. 축소모델 단락 시 다수 피더 시뮬레이션 및 등가 시뮬레이션 결과           |

| 비교                                                     |

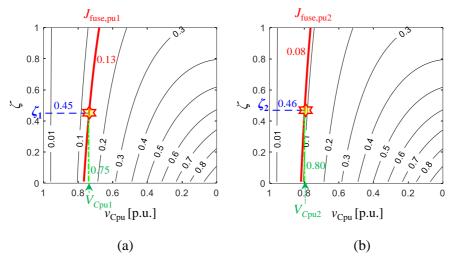

| 그림 5-18. 정규화된 캐패시터 방전 Pt Map 상에 나타낸 축소모델 실험 결과         |

|                                          | 1 | 3 | 6 |

|------------------------------------------|---|---|---|

| 그림 5-19. 계산된 시간-전류 특성 Map과 축소모델 실험 결과 비교 | 1 | 3 | 6 |

# 제 1장 서론

### 1.1 연구의 배경

전력전자의 기술의 발전에 의해 성능과 경제성이 확보된 VSC(voltage source converter)는 에너지 효율 향상과 제어의 편의성 등을 장점으로, 가전 제품을 포함한 산업 전반에서 널리 쓰이고 있다. 예를 들면 가정에서는 컴퓨터, 노트북, 태블릿, 핸드폰, 프린터, TV, 전자레인지, LED조명, 에어컨 등이 있으며, 그 외에도 엘리베이터, 크레인과 같은 권상부하(lift), 산업용 팬, 펌프 및 공조장치와 같은 HVAC(heating, ventilation and air conditioning) 분야에도 가변속제어가 가능한 VSC를 적용하여 에너지 효율을 높이고 있다 [1]-[3].

최근 지구온난화나 대기오염같은 환경적인 문제 때문에, 발전 연료로 석탄 대신 더 오염이 적은 LNG를 사용하거나, 화석연료를 이용한 화력발전소대신 태양광, 수소 연료전지나 배터리를 더 활성화하려는 세계적인 추세가 존재한다. 그런데 태양광이나 리튬전지, 연료전지와 같은 신재생 에너지원은 태생적으로 DC 출력 특성을 가지고 있어 VSC를 사용하여 AC 계통에 전력을 전달하고 있다. 그 외에도 속도가 변하는 풍력발전이나 고속의 마이크로 터빈도 상용 고정 주파수를 가진 AC 계통과 동기화가 어려우므로 DC로의 변환 및 VSC를 통해 AC계통과 연계되고 있다 [4]. 이처럼 DC 발전원과 DC 부하의 연계를 위해 DC를 AC로 변환한 후, 다시 AC를 DC로 변환하는 단계를 거치는 것은 일반적으로 10-25%의 추가 손실을 초래한다 [5].

이와 같이 DC부하와 DC발전원의 수가 많아지면 DC 전력시스템을 사용하여 전력을 전달하는 것이 효율적이지만, 대규모의 AC 전력계통을 모두 DC로 변경하는 것은 지금까지 설치된 AC 전력계통의 규모를 고려했을 때 비현실적이다. 따라서 아직까지 DC 전력시스템은 소규모로 자체적인 전력의 발전, 전송 및 소비가 모두 가능하고, 별도의 주파수로 운용할 수 있는 마이크로 그리드, 자동차, 선박, 비행기 등의 시스템에서 독립적으로 적용하는 추세이다.

선박 관련 환경문제를 살펴보면, 일반적인 대형 선박은 중유(heavy oil)를 사용한 디젤엔진을 많이 사용해왔기 때문에 선박의 수는 차량에 비해 적지만 대기오염배출은 국내 전체 발생량의 6.4%를 차지하는 등 문제가 심각하다 [6]. 이를 해결하기 위하여 국제해사기구(International Maritime Organization, IMO)에서는 해상영역에 따른 질소산화물(NO<sub>x</sub>), 황산화물(SO<sub>x</sub>) 등의 배출량 제한과 신조 선박의 에너지 효율지수(Energy Effeciency Design Index, EEDI), 현존 선박의 에너지 효율지수(Energy Efficiency eXisting ship Index, EEXI), CII(Carbon Intensity Indicator) 등 다수의 규제를 시행하고 있다. 이에 따라 선주 및 조선사에서는 선박이 배출하는 오염물질의 양을 줄이기 위하여 기존 시스템에 스크러버를 장착하여 제거하거나, 오염물질 생성량이 적은 저유황유나 LNG를 사용할 수 있는 엔진을 도입하고 있으며, 암모니아 및 수소와 같은 친환경 연료를 활용한 방식을 적극적으로 연구개발 중에 있다.

또한 최근 경부하 시 에너지 사용 효율 향상을 위하여, 기계식 추진 방식보다 효율적인 전기 추진 방식이 많이 도입되고 있다. 기계식 추진 방식은 내연 기관의 기계적 출력으로 직접 프로펠러를 구동하는 방식이고, 전기 추진 방식은 전기에너지로 전동기 및 프로펠러를 구동하는 방식이다. 전기 추진 방식은 발전원을 다양화하고 운전 중인 발전기의 수를 조절할 수 있기 때문에, 그림 1-1과 같이 기계식 추진 방식보다 경부하 구간에서 효율적이다 [7].

그림 1-1. 전기 추진과 기계식 추진의 효율 비교(Fuel to Propeller) [7]

따라서 경부하 운전이 많은 선박은 전기 추진 방식을 적용하는 것이 유리하다. 해당 선박은 예를 들어 그림 1-2의 (a), (b)와 같이 해상에서 능동 위치 제어 기능 (dynamic positioning, DP)이 필요한 해상지원선(offshore support vessel, OSV)이나 셔틀탱커가 있다. 실제로 해상에서의 능동 위치제어가 필요한 선박은 최대 추력 확보를 위해 대용량 VSC 및 추진전동기를 다수 설치하는데, 실제 운용시에는 대부분 부하율이 높지 않아 경부하 운전 시간이 많다 [8]. 한편, 북유럽을 중심으로 카/여객 페리와 같은 연안선박에는 환경 보호를 위한 무탄소 배출 (zero-emission) 운전에 대한 요구가 높아지고 있다. 이처럼 오염물질을 최소한으로 배출해야 하는 선박은 기계식 추진이나 발전용 디젤엔진을 사용하지 않는 것이 좋다. 이 경우에는 그림 1-2의 (c), (d)와 같이, 배터리나 연료전지를 에너지원으로 한 전기 추진 방식이 적절한 솔루션이 될 수 있다.

그림 1-2. 전기 추진 적용이 유리한 선박 예시 [3], [9], [10], [11]

(a) 해상지원선(OSV) (b) 셔틀탱커 (a) 카/여객 페리(배터리) (d) 여객선(연료전지)

선박에 전기 추진을 적용하기 위해서는 VSC, 추진용 전동기 뿐만 아니라 이들이 사용할 전력을 안정적으로 공급하기 위한 전력시스템도 필수적이다. 기존에는 육상에서와 같이 AC 전력 시스템을 사용하였으나 실제로 전기 추진용 VSC는 DC 전원을 필요로 하기 때문에 VSC 입력 측에 다권선 변압기 및 정류기를 이용하여 DC 전력을 공급하였다. 하지만 최근 전력시스템에서 선박용 VSC가 차지하는 부하 비중이 늘어나면서 그림 1-3의 우측과 같이

VSC의 DC 입력 측을 공통 버스로 연결한 DC 전력시스템이 등장하고 있다. 이는 기존 VSC 입력 측 다권선 변압기 및 정류기 대신, AC 발전기의 출력에 정류기를 직접 연결하거나 배터리 등의 DC 전원을 DC 버스를 통해 부하에 공급한다. 이러한 변화는 선박 추진용 VSC 제품군을 가진 선진 업체들이 이끌고 있으며 VSC로 구성한 선박용 DC 전력시스템을 통해 2010년대 초반부터 선박 시장에 진출하고 있다 [9], [10], [12]-[17].

그림 1-3. 선박용 전력시스템의 변화(AC to DC)

앞에서 언급한 바와 같이, 선박에 DC 전력시스템을 적용하면 AC로의 변환단계를 거치지 않게 되어 효율을 높일 수 있다. 특히 디젤 발전기를 고정속도로 운전할 필요가 없어지기 때문에 부하율에 따라 연료소비율(Specific Fuel Oil Consumption, SFOC)이 낮은 속도로도 운전할 수 있고, 이를 통해경부하에서의 효율 및 연비를 개선할 수 있다 [9], [10]. 위에서 언급한 OSV나셔틀탱커와 같이 경부하 운전이 많은 선박은 발전기 수 조절 뿐만 아니라 DC 전력시스템까지 적용하여 효율을 추가로 개선할 수 있다. 또한 DC 특성을가진 배터리와 연료전지를 에너지원으로 하는 선박도 AC로 변환할 필요 없는 DC 전력시스템을 적용하는 것이 유리하다. 그림 1-4에서는 선종 별 DC 전력시스템이 적용된 선박 수와 배터리가 적용된 선박 수를 나타내었는데, 이중 다수는 경부하 운전이 많은 DP선박이거나, 충전이 가능한 짧은 거리를 오가는 연안 선박임을 알 수 있다. 그리고 DC 전력시스템에서 배터리를 적용하는 사례도 70% 정도로 늘어나고 있다 [18].

그림 1-4. 선박용 DC전력시스템 및 배터리가 적용된 선박 수

(a) 선종 별 DC 전력시스템 적용 선박 수 [14]-[17],

(b) 연도 별 배터리 적용 선박의 수 [18]

이처럼 환경 보호 및 효율 향상을 위해 선박용 DC 전력시스템을 점차적용하는 추세이지만, 운용 중 발생할 수 있는 전기적인 고장(fault)으로부터 인명이나 정상 기기 등에 미치는 악영향을 최소화하는 것 또한 중요하다. 특히 선박은 바다, 강, 호수 등의 물에서 사람 또는 물건을 운반하거나 작업을 수행하는 구조물이므로 공통적으로 부양성, 이동성, 생존성, 안락성, 안전성 등의 특징을 갖추어야 한다 [19]. 특히 안전성은 운항 중 화재, 폭발, 폭풍, 충돌, 좌초 등으로 인한 피해 발생 가능성을 최소화할 수 있어야 하고, 사고들이 발생하더라도 선박이 완전히 손상되지 않도록 대비하는 기능들이 있어야 한다는 것을 의미한다.

만약 해상 플랜트에서 원유를 싣고 운반하는 셔틀 탱커와 같은 선박이 위치 제어능력을 상실할 경우, 해상에서의 충돌사고와 같은 대형 사고로 이어질 수 있기 때문에 위치 제어 중복성(redundancy)을 확보해야 한다. 이를 위하여 일반적으로 다수의 발전원과 분리 가능한 버스로 이루어진 전력시스템을 사용하여 중복성을 확보한다 [20]. 위험하지 않은 평상시에는 버스 타이를 닫은(closed bus-tie) 상태로 최적 효율을 갖는 발전기 대수로 운전을 할 수 있고, DP모드와 같이 중요한 순간에는 버스 타이를 모두 열어(open bus-tie) 분리한 상태에서 운전함으로써, 어느 한 버스에서 고장이 발생하더라도 다른 버스에는 영향이 없도록 한다. 따라서 정상시에는 그림 1-5의 청색 선과 같이 선박의 각 방향에서 불어오는 바람에 대해서 위치제어를 할 수 있고, 1개 버스고장 시에는 남은 전력시스템의 추진 능력을 이용하여 주황색 선과 같은 축소된 위치 제어를 할 수 있다 [24]. ABS나 DNV-GL과 같은 선급에서는 이런 중복성을 갖춘 선박을 평가하여 DP 등급을 부여하는데, 최근에는 친환경고효율 운전이 점차 중요해지고 있어 closed bus 운전을 하더라도 open bus와 유사한 무결성(integrity)과 신뢰성을 증명하는 경우에 별도로 EHS-P, DYNPOS-ER와 같은 진보된 등급을 부여하고 있다 [21]-[23].

그림 1-5. 정상 시 및 일부 버스 고장 시 풍향·풍속 별 DP선박의 위치 제어 능력[24]

DP 선박이 아니더라도 선박용 전력시스템은 선급 승인 및 선주에게 고장 발생시의 충분한 정보를 제공하기 위하여 주요 기기 고장시 단락 전류 계산과 선택 차단 분석(discrimination analysis) 또는 보호 협조 분석(protection coordination analysis) 등의 문서를 제공해야 한다 [22], [25]. 따라서 AC 전력시스템에서 발전기, 버스, 피더, 변압기, 케이블 등에서 고장을 분석한 것과 같이, DC 전력시스템의 주요 기기인 VSC에 고장이 발생했을 때에도 고장시 단락 전류 분석과, 건전한 기기 보호 전략이 필요하다. 그런데 VSC의 DC링크 캐패시터의 외부에서 DC 단락 사고가 발생할 때에는 다음과 같이 AC 전력시스템에서의 고장과 다른 특성을 가지기 때문에 기존과 다른 보호 전략이 필요하다.

첫째, DC 전력시스템은 주기적인 영전류/영전압 구간이 없어 전류의 영점교차구간(zero-crossing)을 활용하는 기존의 AC 차단기를 적용할 수 없다.

둘째, DC 버스에 연결되어 있는 다수 대용량 VSC의 DC링크 캐패시터 및 짧은 선로 길이 때문에 사고 전류의 상승 기울기가 매우 크다. 일반적으로 대형 선박의 길이는 최대 수 백 m인데, 만약 배전반 내에서만 DC 선로가 존재하는 경우에는 수 m에 불과하므로 인덕턴스는 수 μH에 불과하다. 이 경우, 직류단 캐패시터 방전 전류는 최대 수 백 kA/ms의 상승 기울기를 가진다 [26]. 하지만 이를 고속으로 차단할 수 있는 기기는 매우 적다.

셋째, DC 전력시스템을 구성하고 있는 VSC의 전력 반도체 과전류 내량은 AC 기기들에 비하여 현저히 낮다. 변압기, 전동기, 발전기 등은 정격 전류의 1.2배에는 수 분 동안 견딜 수 있고, 수 배에 달하는 고장 전류는 수 백 ms 이상을 견디는 것이 일반적이지만, VSC에 사용되는 전력용 반도체는 120%의 과전류에 대해서 최대 5 초, 200%의 과전류는 최대 10 ms 가량 정도 밖에 버티지 못한다.

이러한 특징들 때문에 DC 전력시스템을 위한 보호시스템은 AC의 경우보다 훨씬 빠른 속도로(수 십  $\mu$ s ~ 수 ms 이내) 고장 지점을 차단시켜야하는 과제를 안고 있다. 그런데 AC 전력시스템에서 주로 사용되는 기계식 차단기는 차단 동작 명령이 내려진 시점으로부터 회로가 분리될 때까지 보통수 십 ms가 소요되기 때문에 이를 이용하여 DC 사고에 대응하기는 어렵다. 다시 말하면, DC 전력시스템을 보호하기 위해서는 AC와 근본적으로 다른 접근이 필요하며, 기본적으로 다음과 같은 전략을 생각할 수 있다.

첫 번째로는 피보호기기의 내량을 상향하여 캐패시터 방전 및 환류 시간 동안 소손이 일어나지 않게 하는 방법을 생각할 수 있다. 이러한 접근 방법은 빠른 보호 동작을 필요로 하지 않지만 캐패시터의 에너지가 모두 소모될 때까지 전력반도체들이 이를 견뎌야 하므로 상당한 양을 병렬로 추가설치해야 하고, 따라서 과다한 비용이 발생할 것으로 추정된다.

두 번째는 캐패시터를 포함하지 않거나 DC 측 전류 제어가 가능한 토폴로지를 이용하여 DC 전력시스템을 구성하는 방안이다. 발전단에는 캐패시터가 없는 다이오드 또는 싸이리스터 정류기를 사용하고, 부하 측에는 직류 모터 또는 전류형 컨버터를 사용할 수 있다 [27], [28]. MVDC(medium voltage DC)나 HVDC(high voltage DC) 분야에서는 full-bridge 타입의 MMC(modular multilevel converter)를 이용하면 DC 측 고장 전류를 제어할 수 있다 [29]. 하지만 이들 방식은 경제적인 상용 2레벨 VSC를 사용할 수 없기 때문에 경제성이 낮을 것으로 예상된다.

세 번째는 상용 2레벨 VSC를 사용하되 캐패시터 방전을 억제하는 장치를 추가로 설치하는 것이다. 만약 버스에서 부하측으로 전력이 단방향으로만 흐른다면 입력단 다이오드를 직렬로 설치하여 캐패시터의 방전을 원천적으로 차단할 수 있고 [30], 양방향으로 흐를 수 있는 경우에는 IGBT와 같은 능동 스위치 소자를 포함한 고속 차단 회로를 구성할 수도 있다 [31]. 또는 반도체 스위치를 내부 DC 링크 캐패시터와 직렬로 연결하는 방식으로 순간적인 차단을 할 수도 있다 [32], [33]. 하지만 이 경우에는 VSC의 외부로 유의미한 고장전류가 발생하지 않기 때문에 고장 위치 판별을 위한 별도의 장치, 통신, 보호기기가 필요하므로 시스템이 복잡해지게 된다.

네 번째는 고장 전류가 시스템 상에서 흐르는 것을 허용하고, 이를 고속으로 판별, 차단 및 분리하는 방법이 있다. 이상적으로는 반도체 차단기(solid-state circuit breaker)를 각 회로의 분기점 마다 설치하면 모든 고장 전류를 고속으로 차단하는 것이 가능하다. 하지만 반도체 차단기는 기계식 차단기에 비해 도통 손실이 크고 규격 및 표준이 아직 확립 되지 않아 아직 가격이 높다는 문제점을 가지고 있다. 한편, 전력 반도체 보호용으로 사용되는 고속 퓨즈는 고속 차단이 가능하면서 구성이 간단하고, 표준 및 규격이 확립되어 있어 비용도 저렴하다. 하지만 한 번 용단되면 수동으로 교체 및 복구를 해야한다는 단점이 있다.

앞에서 소개한 전략 외에도 보다 효과적이고 경제적인 보호방식을 찾기 위한 연구가 다수 진행되어 왔다. 그 중 실제로 상용화된 DC전력시스템에는 모든 곳에 반도체 차단기를 사용하지 않고, 보호영역에 따라 각기 다른 3단계의 보호방식을 상용선박에 적용하고 있다 [12]. 만약 버스의 어느 한지점에서 고장이 발생하면, 1 단계로 버스타이(bus-tie)에 위치한 반도체차단기를 이용하여 고속으로 고장 버스를 분리한다. 그 후, 2 단계로 고장피더가 포함된 고장 버스 내에서 다수 피더에서 공급되는 전류를 이용하여해당 피더의 고속 퓨즈를 용단한다. 이를 위해 각 피더의 입력단에는 고속퓨즈가 적용이 되어 있다. 그런데 만약 퓨즈가 용단되지 않거나, 피더가 아닌버스바의 단락 사고인 경우에는 발전기로부터 고장전류 공급이 지속되는데,이 경우에는 3 단계로 발전기 여자 전류 제거를 통해서 기전력을 소거하거나[12], 퓨즈나 기계식 차단기를 통해서 발전단과 버스를 분리하여 고장 전류를 차단할 수 있다 [31].

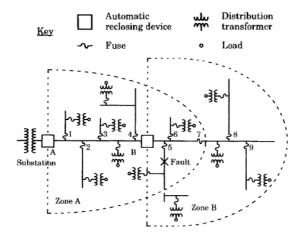

주목할 것은, 퓨즈가 일회성 동작, 수동 복구가 필요한 단점을 가지고 있음에도 불구하고 다수의 제조사에서 공통적으로 고속 퓨즈를 이용한 보호 방식을 적용하고 있다는 점이다. 이는 해당 위치에서 반도체 차단기 보다 경제성을 가지기 때문에 적용된 것으로 해석할 수 있다. 경제성을 고려하여 위치에 따라 보호기기를 다르게 조합하여 사용하는 예는 그림 1-6과 같이 기존 방사형(radial) AC 전력시스템에서도 찾아볼 수 있다 [34].

그림 1-6. 방사형 AC 전력시스템의 보호기기 배치 예[34]

대부분의 상용 전력시스템은 경제적인 부분을 고려하여 그림 1-6과 같이 주 전력선을 중심으로 방사형으로 구성되어 있다. 육상용 전력시스템에서 고장은 낙뢰, 나무와의 접촉, 교통사고로 인한 단락 등 대부분 일시적이고 과도적인 특성을 가지고 있다. 따라서 모든 지점에 일정 시간 뒤 복구를 시도하는 자동 recloser를 설치하는 것이 이상적이지만, 주 전력선이 아닌분기 또는 말단 위치는 주 전력선보다 즉각적인 복구의 필요성이 낮고, 영구적인 고장인 경우에는 현장에서 작업자에 의한 확인 및 조치가 이루어져야 하기 때문에 고 비용의 recloser보다는 저렴한 퓨즈를 사용하는 것이 충분히 합리적이다.

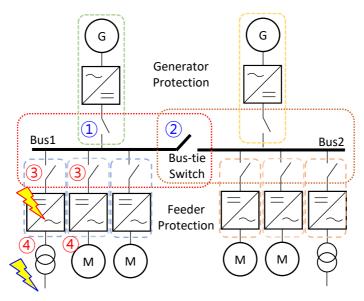

위와 같은 보호기기 배치 전략을 그림 1-7과 같은 DC 전력시스템의 경우에 대입해보면, 주 전력선에 해당하는 발전단 ①과 버스타이 ②의 위치에는 재투입이 가능한 반도체 차단기나 기계식 차단기를 적용하고 있으며, 버스에서 분기되거나 직접 부하를 구동하는 말단의 피더 위치인 VSC의 입력측 ③에는 저렴한 퓨즈를 사용하고 있어 유사한 전략으로 해석할 수 있다. 한편, VSC의 출력 측 ④에서도 고장이 발생할 수 있는데, 이는 VSC 자체의 고장검지 기능을 활용하여 하위의 전력공급을 차단할 수 있다. 일시적인 경우에는 재기동을 시도할 수 있고, 수 차례 시도에도 지속적으로 고장이 발생한다면 현장에서 확인이 이루어질 때까지 VSC를 정지시켜 둘 수 있다. 따라서 피더에 위치한 퓨즈가 작동하는 경우는 VSC 내부 고장으로 인해 영구적인 단락이 발생한 경우로 한정되기 때문에 해당 위치에 퓨즈를 적용하는 것은 충분히 합리적이라고 할 수 있다.

그림 1-7. 상용화된 선박용 DC전력시스템에서 보호기기의 배치

위에서 언급한 합리성을 뒷받침하기 위해서는 DC 전력시스템의 고장이주로 발생하는 부품과 확률에 대한 정보가 필요하다. 하지만 선박용 DC 전력시스템은 아직 통계적으로 분석할만큼 충분한 데이터가 공개되지 않아 VSC를 다수 사용하는 시스템인 태양광과 풍력에서의 고장 빈도, VSC가단락회로로 고장을 일으킬 수 있는 가능성을 대신 살펴보고자 한다.

15년 간 1500개의 풍력발전기를 운영해 본 경험 자료에 의하면, 터빈, 기어박스, 발전기, 전기기기, 제어기 등 다수의 전기-기계 부품들로 이루어진 풍력발전시스템에서, 전기계에서 발생한 연간 고장 빈도는 1/2이 넘는다 [35]. 또한 5년 간의 대형 태양광 발전시스템 운영 경험에 의하면, 태양광 인버터의 수리 발생 비율은 전체의 37% 로 나타났다 [36]. 제조사의 기술력이나 운전환경 등 다양한 원인이 있을 수 있지만, 일단 VSC의 고장 빈도는 상당히 높은 것을 알 수 있다.

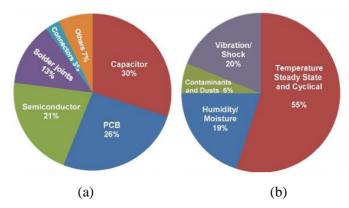

VSC는 핵심인 전력반도체와 이것을 제어하는 제어보드 PCB(printed circuit board) 및 DC링크 캐패시터 등으로 이루어져 있는데, 그림 1-8의 통계자료에 따르면 전력변환장치 고장의 근본원인이 되는 부품은 캐패시터가 30%, PCB는 26%, 전력반도체는 21%에 해당하는 것으로 조사되었다 [37]. 또한 고장을 발생시키는 주요 스트레스 요인에는 온도가 55%, 습도는 19%, 진동

및 충격은 20% 를 차지하는 것으로 각각 조사되었다 [38].

그림 1-8. 전력변환 시스템에서의 주요 고장 부품 및 주요 스트레스

(a) 전력변환 시스템 고장의 근본 원인 분포 [37], (b) 주요 스트레스 요인 [38]

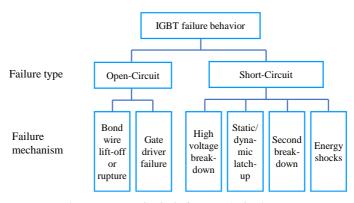

현재 주력으로 사용되는 전력반도체 중 하나인 IGBT(insulated gate bipolar transistor)는 고장 시 주로 개방 또는 단락회로로 나타나는데, 고장을 일으키는 메커니즘은 다양하게 있을 수 있으나, 다수가 단락으로 이어지는 것으로 나타났다 [39], [40]. 또한 DC링크 캐패시터도 충전/방전 싸이클에 따라 전해질 용액의 증발이 일어나 단락이 발생할 가능성이 있다 [41].

그림 1-9. IGBT의 치명적인 고장의 개요[39]

위에서 살펴본 바와 같이 VSC 내부의 전력반도체나 캐패시터에 단락이 발생할 메커니즘과 확률은 분명히 존재하고, 이는 영구적인 고장에 해당된다. 기술의 발달에 따라 고장이 발생할 확률은 점차 낮아지겠지만 선박의 안전한

운항을 위해서는 위와 같은 VSC의 영구적인 고장에 대비하여 사전에 충분한 보호 전략을 세워야 한다.

### 1.2 연구의 목적

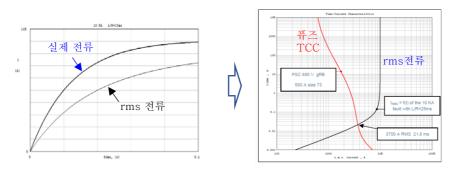

퓨즈와 같은 과전류 보호시스템을 설계하기 위해서는 우선 DC 전력시스템의 회로 파라미터를 분석하여 예상 고장전류를 계산해야 한다. 그후에 퓨즈를 그 지점에 위치시켰을 때, 예상 고장 전류와 퓨즈의 동작 특성을 비교하여 퓨즈의 용단 여부를 판단할 수 있다. 퓨즈는 데이터시트 상에서용단 Pt 값 또는 용단 시간-전류 특성 그래프로 제시되므로, 고장 전류는 최종적으로 Pt 값 또는 시간-전류 특성으로의 계산이 필요하다.

기존의 AC 전력시스템에서는 전압의 변동이 없는 이상적인 전원으로부터 고장전류가 공급된다고 해석하기 때문에 등가 회로 및 계산이 비교적 단순하며, 이를 바탕으로 고장 전류를 분석하고 적정 퓨즈를 선정하는 방식 또한 퓨즈 제조사 가이드에 잘 제시되어 있다 [42]-[44]. 하지만 DC 전력시스템에서의 고장 전류 공급원인 캐패시터는 방전이 일어날 때 전압이 감소하기 때문에 복잡한 계산이 필요하며, 다수의 캐패시터에서 고장전류가 공급되기 때문에 더욱 복잡한 다변수 방정식을 계산해야 한다. 따라서 컴퓨터를 통해 수치해석적(numerical method)으로 시뮬레이션 결과를 구하거나, 근사적으로는 IEC 61660-1과 같이 미리 계산된 참조 데이터를 기반으로 표준근사함수의 주요 특징점을 구하는 참조법(reference method)을 이용하여 구할 수도 있다 [45]. 하지만 해당 표준에는 캐패시터 방전 전류의 사와 실효값인 r.m.s.(root-mean-square) 전류 값에 대한 참조데이터는 제시되어 있지 않다.

그런데 퓨즈는 정격 전류와 용단 특성이 고정되어 있어 용단 특성을 더민감하게 하려면 정격 전류가 부족해지는 등 설계 자유도가 많지 않다. 따라서 DC 전력시스템의 파라미터가 고정된 상태에서 적합한 퓨즈를 선정할수도 있지만, 반대로 퓨즈의 정격 전류와 용단특성에 충분한 고장전류를 발생시키는 방식으로 보호시스템을 설계할 수도 있다. 이를 위해서는 DC 전력시스템의 파라미터를 수정해야 하는데, 필요한 설계 값은 캐패시터 방전특성식의 음함수(implicit function) 특성 때문에 해석적으로 구할 수 없는 경우가 대부분이다.

일부 연구에서는 적절한 파라미터를 선정하기 위해 컴퓨터 시뮬레이션을

반복적으로 수행하여 용단 조건에 부합할 때까지 파라미터를 수정하는 점진적 반복 설계법(iterative method)이 제안되었다 [46], [47]. 하지만 이와 같이 컴퓨터를 이용한 방식은 설계자에게 파라미터 변경 시의 영향에 대한 직관을 가져다 주지 못하는 단점이 있다.

본 논문에서는 복잡한 수식을 정규화하여 참조 데이터로 제공함으로써 사양에 맞는 적절한 파라미터를 바로 선택할 수 있도록 하였으며, 음함수 특성 때문에 해석적으로 구할 수 없는 경우에도 역함수에 해당하는 값을 참조하여 필요한 값을 구할 수 있다. 본 논문에서는 초기 캐패시터 전압이 Vo인 단일 R-L-C 회로의 캐패시터 전압, 전류, 시간, I't에 대한 수식을 분석하여 각각을 기준값(base value) 과 정규화된 항의 곱으로 표현할 수 있음을 보인다. 정규화된 I't 항은 감쇠비와 위상각 또는 감쇠비와 캐패시터 전압의 함수로 나타낼 수 있고, 이를 본 논문에서 제안하는 캐패시터 방전 I't Map으로 나타낼 수 있다. 추가로, 정규화된 시간 정보와 실효 값(r.m.s.) 계산식의 정의를 이용하여 시간-전류 평면으로 사영(projection)하면 캐패시터 방전 시간-전류 특성 Map을 구할 수 있다. 위의 과정을 거쳐 해석적으로 도출된 각 정규화 데이터의 정확도를 검증하기 위해, 단일 R-L-C 회로에서의 시뮬레이션 및 퓨즈를 포함한 실험을 수행하였으며, 또한 설계 예시를 제시하였다.

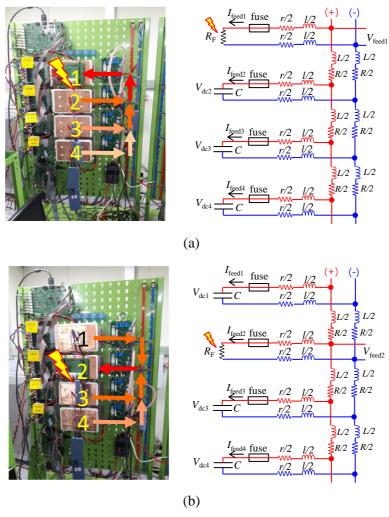

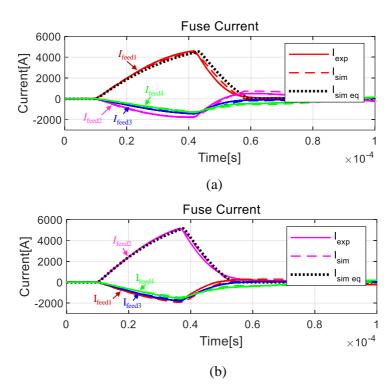

추가적으로 선박에서 적용되고 있는 DC 전력시스템의 네트워크 형태에 대해서 분석한다. 버스와 피더의 임피던스 비율에 따라 차단시 선택성이 달라질 수 있음을 보이고, 가장 낮은 공진주파수를 기준으로 다수의 캐패시터와 버스 임피던스를 고장 피더에 대하여 단일 R-L-C 회로로 등가화할 수 있음을 보인다. 이러한 등가화 방법의 유효성을 선박용 DC 전력시스템 축소모델을 기반으로 실험을 통해 검증한다.

## 1.3 논문의 구성

본 논문은 다음과 같은 구성으로 되어 있다.

1 장은 서론으로서, 연구의 배경, 연구의 목적, 논문의 구성에 대해서설명하였다.

2 장에서는 선박용 DC 전력시스템에서의 단락 사고 특징 및 관련 수식을 정리하고, 선박용 보호 시스템이 갖추어야 할 특성에 대해서 고찰해본다. 상용화된 선박용 DC 전력시스템에서 3단계 보호 방식이 주로 채택된 이유에 대해서 분석해보고, 그 중 고속 퓨즈 기반 보호 시스템과 그 설계를 위한 기존 연구에 대해서 소개한다.

3 장에서는 DC 전력시스템 사고 순간의 등가 인덕턴스, 캐패시턴스, 초기 전압을 상수로 가정하여 캐패시터 전압, 1단계 진행시간, 캐패시터 전류, Pt 식에 대하여 기준 값(base value)을 설정하고 각각 감쇠비와 위상각의 함수로 정규화할 수 있음을 보인다. 정규화된 함수는 다시 감쇠비와 전압강하에 따라 발생하는 Pt를 직관적으로 파악할 수 있도록 정규화된 캐패시터 방전 Pt Map 형태의 참조 데이터로 제시하고 그를 이용한 설계 방법을 제안한다.

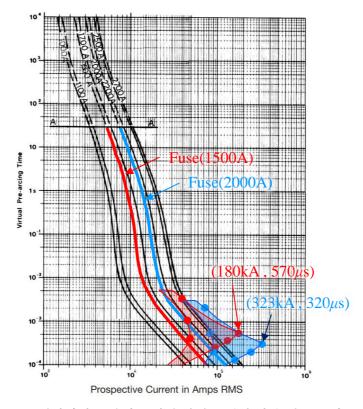

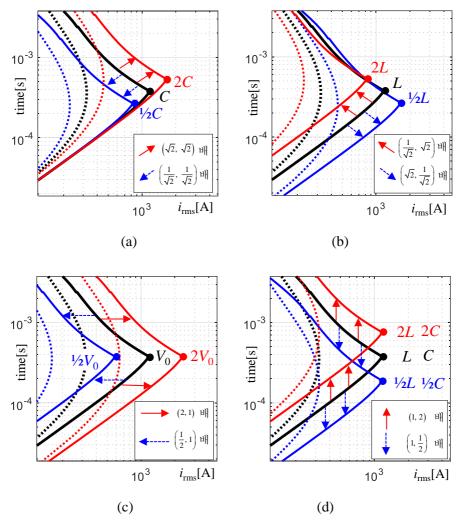

4 장에서는 3 장에서 도출한 정규화된 캐패시터 방전 *Pt* Map을 기반으로 만들어진 정규화된 캐패시터 방전 시간-전류 특성 Map과 이를 이용한 시스템 파라미터 설계 방법을 제안한다. 본 곡선은 보호 협조 설계시 많이 이용되는 시간-전류 특성 곡선 형태로 제공되며 파라미터 변경에 따른 평행이동 특성으로 참조 편의성이 증대된다.

5 장에서는 다수 건전 피더의 캐패시터 방전 전류를 이용하여 고장 피더를 선택 차단(discrimination)할 때 필요한 고려 사항에 대해서 분석한다. 그리고 본 논문에서 제안한 캐패시터 방전 전류 Map을 다수의 VSC로 이루어진 DC 전력시스템에 적용할 수 있도록 등가회로를 구성하는 방법을 제안하고, 축소모델 실험을 통해 그 유의성을 검증한다.

마지막 6 장에서는 본 논문의 결론과 향후 과제에 대하여 기술한다.

# 제 2장 선박용 DC 전력시스템의 단락 보호

본 장에서는 선박용 DC 전력시스템에서의 단락 사고 특징 및 관련 수식을 정리하고, 선박용 보호 계전 시스템이 갖추어야 할 특성에 대해서 고찰해본다. 상용화된 선박용 DC 전력시스템에서 3단계 보호 방식이 주로 채택된 이유에 대해서 분석해보고, 그 중 고속 퓨즈 기반 보호 시스템과 그 설계를 위한 기존 연구에 대해서 소개한다.

### 2.1 단일 VSC의 DC 측 단락 사고시 특성

단락(short-circuit)은 두 개 이상의 전도성 부분 사이의 우발적이거나 의도적인 전도성 경로로 두 부분의 전위차가 0과 같거나 0에 가까워지는 경우를 말한다 [IEV(International Electrotechnical Vocabulary) 151-12-04]. 전압원 기반의 전력시스템에서는 전력을 사용하는 부하로 하여금 적정한 범위 내의 전압을 공급하기 위해 발전원 및 부하가 병렬로 연결되어 있는데, 만약 내부에서 과부하, 단락 등으로 인한 낮은 임피던스가 갑자기 발생하면 전압원으로부터 막대한 전류가 흐를 수 있다. 예를 들어 작업자 실수로 극성을 잘못 조립하거나, 전위차가 존재하는 양 극에 전도성의 물체가 닿은 경우나, 또는 VSC 내의 전력반도체나 캐패시터 등에 이상이 발생하여 내부 회로에 단락이 발생하는 것을 전력시스템에서의 고장이라고 부른다. 그리고 이 고장으로 인해 네트워크의 특정 지점에 흐르는 전류를 고장 전류(fault current)라고 한다[IEV 603-02-25].

위와 같이 잘못된 연결이나 절연의 결함에 의하여 좁은 영역의 도체에서 막대한 고장 전류가 흐르게 되면 주로 저항성분에 의한 줄(Joule)열이 발생하여 도체의 온도가 급격히 상승하게 된다. 이로 인하여 도체가 용융, 기체-이온화하면서 아크(arc)까지 발생하게 되면 공기의 급격한 팽창 및 폭발이 일어나게 되고, 기기에 손상을 가져오거나 인명 안전에 위협이 될 수 있다. 특히 DC 아크가 발생하는 경우에는 전압-전류의 자연적인 극성 교차가일어나지 않아 플라즈마 상태가 지속되기 쉽고 아크 소호에 더욱 어려움을

겪는다. 또한 발생한 고장으로 인하여 정상적인 부하들도 정전상황에 처하게 된다면 선박 계통 전체가 동작 불능 상태에 빠지게 된다. 따라서 이를 막기 위하여 전력시스템은 단락 사고에 대하여 적절한 보호시스템을 갖추어야 하며, 사고의 특성에 따라 필요한 보호시스템의 성능도 달라져야 한다.

본 절에서는 DC 전력시스템에 필요한 보호시스템의 특성을 도출하기 위하여, 우선 하나의 VSC 외부에서 단락 사고가 발생했을 때의 사고 전류의 특성에 대해서 설명한다. 기존의 캐패시터가 없는 다이오드 정류기나 싸이리스터 정류기 기반의 단락사고는 무한 버스전원, 필터, 선로 임피던스, 고장저항로 이루어진 직렬 회로로 해석될 수 있다. 퓨즈 제조사의 많은 DC 보호에 대한 상용 가이드들은 이러한 모델을 기반으로 퓨즈 설계 방법을 제시하고 있다 [42]-[44]. 하지만 VSC는 순간적인 전류를 공급하는 특성이좋고 방전에 따라 전압이 감소하는 DC링크 캐패시터를 포함하고 있는데, 바로 이 캐패시터 때문에 DC 전력시스템에서는 단락사고의 특성이 달라지고, 해석하기 어렵게 된다.

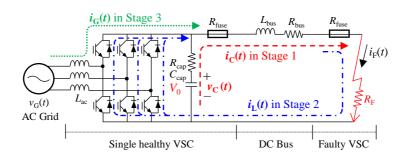

그림 2-1 (a)는 고장 VSC(faulty VSC)의 내부에 단락사고가 발생했을 때 DC 버스를 통하여 연결되어 있는 건전 VSC(healthy VSC) 관점에서의 회로를 임의의 예시로 나타낸 것이다. 여기서,  $V_0 = 400$  V,  $C_{\rm cap} = 10$  mF,  $v_{\rm G}(t) = 220$   $\sin(2\pi\cdot60\ t)$ ,  $L_{\rm ac} = 400\ \mu$ H,  $L_{\rm bus} = 10\ \mu$ H,  $R_{\rm bus} = 10$  m $\Omega$ ,  $R_{\rm F} = 0\ \Omega$  로 시뮬레이션을 수행하였다. 건전 VSC는  $R_{\rm fuse}$ 의 내부저항을 가진 퓨즈, DC링크 캐패시터, 전력반도체, 계통연계용 AC리액터( $L_{\rm ac}$ )로 구성되어 있고 AC 계통의 전압은  $v_{\rm G}(t)$ 의 함수로 운용이 되고 있다고 하였다. 여기서 DC링크 캐패시터는  $C_{\rm cap}$ 의 캐패시턴스와, 내부등가 직렬저항(Equivalent Series Resistance, ESR)  $R_{\rm cap}$ 으로 구성되어 있고 초기 전압은  $V_0$ 이다. DC 버스는 등가 인덕턴스  $L_{\rm bus}$ , 등가 저항  $R_{\rm bus}$ 의 임피던스를 가지고 있고, 고장 VSC는 사고시의 등가 고장 저항  $R_{\rm F}$ 로 모델링할 수 있으며  $R_{\rm fuse}$ 의 내부저항을 갖는 DC측 퓨즈를 통해 DC 버스와 연결되어 있다.

고장 부위의 회로는 단순히 저항  $R_F$ 로 둘 수 있는데, 이는 고장 VSC 내부에 캐패시터에 전압이 충전되어 있거나 연결된 역기전력 등이 있더라도 고장 전류의 에너지를 단락사고 부위 내부에서만 대부분 열로써 소모하므로 외부에서 바라보았을 때는 이를 등가적인 고장 저항 성분으로 볼 수 있기 때문이다. 일반적인 전력시스템에서의 단락은 아크 발생 고장이 80%이상이며, 아크 회로 모델은 주로 저항성분으로 등가 모델링한다 [48]. 만약 전력반도체 내에서 아크가 형성된다면 Gap이 작기 때문에 고장 저항도 수  $m\Omega$  정도로 작을 것으로 추정된다 [49].

그림 2-1. 외부 단락사고시 정상 VSC 관점에서의 등가회로 및 사고 단계 별 주요 전류 경로

그림 2-2. 외부 단락사고 시 단계 별 캐패시터 전압, 고장 전류, 고장 I't 파형 예시

단락 사고가 발생하게 되면 정상 VSC의 캐패시터와 AC계통 전압으로부터 고장 VSC로 고장 전류  $i_F(t)$ 가 흐르게 된다. 이 고장 전류는 흐르는 경로에 따라 일반적으로 3개의 진행단계로 이루어지며 기존 연구들에서도 각 단계에 대한 기본적인 분석을 한 사례를 찾을 수 있다 [50]-[52].

고장 1 단계(stage 1)는 캐패시터 방전 단계이다. 사고 직전 정상 VSC의 DC링크 캐패시터는  $V_0$ 로 충전되어 있으며, AC계통보다 고장 지점에 가까이 연결되어 있다. 외부 사고시 이 캐패시터는 고장 저항과 캐패시터 외부의 선로 임피던스를 통하여 캐패시터 방전 전류 ic(t)를 공급하게 된다. 본논문에서 다루고 있는 선박용 DC버스는 길이가 짧기 때문에 선로임피던스가 작아서 그림 2-2에서와 같이 캐패시터 전압 vc(t)는 빠르게하강하고, 캐패시터 방전 전류 ic(t)는 매우 빠르게 상승하여 높은 전류를발생시킨다. 다른 고장 전류 공급원인 AC 계통이 사고 1단계에서 미치는영향은 미미한데, 이는 상대적으로 큰 임피던스를 갖고 있는 계통연계리액터를 통하여 연결되어 있고, 캐패시터의 전압이 AC계통을 정류한전압보다 작아지는 시점부터 전류를 공급하기 때문이다. 따라서 고장 1단계에서 고장 전류 ic(t)의 대부분은 캐패시터 방전 전류 ic(t)로 이루어져있음을 알수 있다.

고장 1 단계의 종료시점은 캐패시터 전압이 0이 되거나 AC계통으로부터의 고장 전류가 캐패시터 고장 전류 보다 우월(dominant)해질 때로 정할 수 있다. 캐패시터 방전 회로는 L-C 공진회로도 해석할 수 있는데, 만약 등가 저항 성분이 낮아서 비 감쇠 또는 저감쇠 회로가 되면 캐패시터 전압은 0까지 도달하게 되어 1 단계가 종료된다. 하지만 임계감쇠나 과감쇠의 경우에는 캐패시터 전압이 0에 도달하지 않으며 따라서 2단계의 다이오드를 통한 환류도 일어나지 않는다. 이런 경우에는 AC 계통으로부터 유입되는 전류가 우월해지는 시점이 될 때 1단계가 종료되고 3단계가 시작된다고 볼 수 있다.

고장 2 단계(stage 2)는 다이오드 환류(diode-freewheel) 단계이다. 1 단계의 캐패시터 방전으로 전압이 0에 도달하고 난 뒤 선로의 인덕턴스에 흐르고 있던 전류  $i_L(t)$ 가 캐패시터 전압을 음의 방향으로 충전시키고, 캐패시터 전압이 다이오드의 문턱 전압(threshold voltage)과 같아지는 순간부터

다이오드를 통해 환류 전류가 흐른다. 만약 감쇠비(damping ratio)가 0에 가까운 경우에는 1 단계 종료시점의 전류가 2 단계의 초기 전류값이 되기 때문에 열적 내량이 낮은 다이오드는 이 시점의 막대한 전류에 의해 소손될 우려가 있다. 그림 2-2의 고장 전류 그래프를 보면  $T_{\rm c}$  시점 직후에 약 9 kA에 해당하는 전류가 다이오드로 흐르기 시작함을 알 수 있다. 환류가 진행됨에 따라 다이오드에 미치는 영향을 판단하기 위해서는 해당 전력반도체의 데이터시트에 주어진  $P_{\rm t}$ 값을 참조하면 되는데, 그림 2-2 하단의 그래프와 같이 고장 전류를 제곱하여 누적 적분한 고장  $P_{\rm t}$ 를 계산할 수 있으면, 이 값을 반도체의 열적 내량  $P_{\rm t}$ 값과 비교하여 소손이 일어나는지 판단할 수 있다. 만약 사고시 일어날 수 있는 최소 등가 저항값을 적용했을 때 소손이 일어날 것으로 예상된다면 가능한 1 단계에서 보호동작을 완료하여 환류가 일어나지 않도록 하는 것이 바람직하다.

고장 3 단계(stage 3)는 계통 유입(grid-feed) 단계이다. 이 단계는 앞서 말한 바와 같이 2 단계의 환류 전류가 0에 가까이 수렴하거나, AC 계통으로부터 유입되는 전류  $i_G(t)$ 가 지속적으로 증가하여 1 단계 또는 2 단계의 사고 전류보다 우월해지는 시점부터 시작된다고 볼 수 있다. 전류  $i_G(t)$ 는 DC링크 캐패시터 전압이 계통 정류 전압보다 낮아질 때부터 증가하기 시작하는데, 1 단계와 2 단계에도 해당 전류가 존재할 수 있지만 계통연계 리액터  $L_{ac}$ 의 임피던스 때문에 전류 증가율이 제한되어 캐패시터 방전과 환류로 인한 전류보다는 비교적 작게 존재한다. 그렇지만 무한 모선인 AC 계통으로부터 사고전류는 이후 지속적으로 유입되므로 보호회로가 동작하거나 회로의 손상이 발생할 때까지 3 단계 고장 전류는 지속될 수 있다.

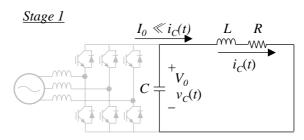

위에서 설명한 바를 단계별 등가회로를 통해 수식적 분석을 할 수 있다. 그림 2-3은 등가 파라미터로 표현된 단일 R-L-C 회로에서  $V_0$ 의 전압으로 충전되어 있던 등가 캐패시터 C가 외부의 단락사고로 인해 방전되는 고장 1 단계를 나타낸 것이다. 이 때 단락 고장 전류  $i_F$ 는 캐패시터 방전 전류  $i_C$ 가 주성분이고 단락 사고시 초기 전압  $V_0$ 는 사고 직전의 정상 동작 전압, 즉 DC 전력시스템의 정격전압이다. 등가 인덕턴스 L은 주로 케이블이나 전력버스의 길이에 의한 인덕턴스이며 사고 직전에는 부하전류  $I_0$ 가 흐르고

있었다고 가정한다. 마지막으로 등가 저항 R은 고장 저항  $R_F$ , 정상 VSC와 고장 사이의 케이블 저항, 캐패시터의 내부저항(ESR) 등의 합으로 볼 수 있다.

그림 2-3. 고장 1 단계 고장 전류 분석을 위한 단일 R-L-C 등가 회로

앞에서 언급하였듯, 초기 조건은 단락 사고가 발생하기 직전에 정상 VSC의 캐패시터는 정격 전압  $V_0$ 로 충전된 상태이고, 피더로 부하 전류  $I_0$ 가 흐르는 상태이다. 시간 당 전압 변화량과 전류 변화량도 고려하여 초기 조건을 식으로 나타내면 다음과 같다.

$$V_0 = L \frac{dI_0}{dt} + RI_0. (2.1)$$

$$C\frac{dV_0}{dt} = -I_0. (2.2)$$

키르히호프의 전압법칙에 따라 외부에서 사고 저항  $R_{\rm F}$ 가 발생했을 때의 캐패시터 전류의 미분 방정식과 캐패시터 전압과 전류의 관계를 나타내면 다음과 같다.

$$L\frac{di_C(t)}{dt} + R \cdot i_C(t) + \frac{1}{C} \int i_C(t) dt = 0.$$

(2.3)

$$C\frac{dv_C}{dt} = -i_C(t). (2.4)$$

식 (2.4)를 (2.3)에 대입하면 식 (2.5)와 같이 캐패시터 전압  $v_c$ 에 대한 미분 방정식으로 나타낼 수 있다.

$$\frac{d^2v_C(t)}{dt^2} + \frac{R}{L}\frac{dv_C(t)}{dt} + \frac{1}{LC}v_C(t) = 0.$$

(2.5)

캐패시터 전압의 함수  $v_{\rm C}(t)$ 는 연속이므로 초기값을 고려하여 라플라스 변환을 하면 식 (2.6)과 같고  $V_{\rm C}(s)$ 의 해는 식 (2.7)과 같다. 여기에서 -a와 -b는 특성 방정식의 근이고  $\alpha$ 는 감쇠계수(damping coefficient),  $\omega_0$ 는 고유 주파수 (natural frequency),  $\omega_d$ 는 감쇠고유주파수 (damped natural frequency)를 나타낸다.

$$\left(s^{2} \cdot V_{C}(s) - s \cdot V_{0} - \frac{dV_{0}}{dt}\right) + \frac{R}{L}\left(s \cdot V_{C}(s) - V_{0}\right) + \frac{1}{LC}V_{C}(s) = 0.$$

(2.6)

$$V_{C}(s) = \frac{V_{0}\left(s + \frac{R}{L}\right) + \frac{dV_{0}}{dt}}{s^{2} + \frac{R}{L}s + \frac{1}{LC}} = \frac{V_{0}\left(s + \frac{R}{L}\right) + \frac{dV_{0}}{dt}}{(s+a)(s+b)}.$$

(2.7)

달,

$$a = \alpha + \sqrt{\alpha^2 - \omega_0^2}$$

,  $b = \alpha - \sqrt{\alpha^2 - \omega_0^2}$ ,  $\alpha = \frac{R}{2L}$ ,  $\omega_0 = \frac{1}{\sqrt{LC}}$ ,  $\omega_d = \sqrt{\omega_0^2 - \alpha^2}$

단락사고 1 단계는 캐패시터 전압이 0이 되는 순간까지만 정의되기 때문에이 때의 전압 함수와 전류의 함수는 주기적인(periodic) 함수가 아니라서주파수 도메인에서 해석할 수 없고, 최종적으로 모든 함수는 라플라스역변환을 통해 시간 t의 함수로 구해야 한다. 기존 연구에서저감쇠(underdamping)인 경우와 과감쇠(overdamping)인 경우의 함수를간략히 제시하였으나 그 과정은 대부분 생략되어 있다 [50], [51]. 본 절에서는 저감쇠인 경우와 과감쇠인 경우의 시간 영역에서의 전압, 전류식과 l²t의 식이도출되는 과정을 설명한다.

Case i) 저감쇠(underdamping)인 경우  $(v_{C,u}(t), \alpha^2 < \omega_0^2)$

저감쇠인 경우는 실제 발생하는 고장 저항을 포함한 등가 저항값이 충분히

작은 경우이다. 계산 편의를 위해 주파수 도메인의 캐패시터 전압식 (2.7)을 두 부분으로 나누고 식 (2.2)를 대입하면 식 (2.8)과 같은 해를 구할 수 있다.

$$v_{C,u}(s) = \frac{V_0(s+\alpha) + V_0\alpha + \frac{dV_0}{dt}}{\left(s+\alpha\right)^2 + \left(\sqrt{\omega_0^2 - \alpha^2}\right)^2} = \frac{V_0(s+\alpha)}{\left(s+\alpha\right)^2 + \omega_d^2} + \frac{V_0\alpha - \frac{I_0}{C}}{\left(s+\alpha\right)^2 + \omega_d^2}.$$

(2.8)

식 (2.8)을 라플라스 역변환하면 식 (2.9)와 같이 정리할 수 있다.

$$v_{C,u}(t) = V_0 e^{-\alpha t} \cos(\omega_d t) + \left(\frac{V_0 \alpha}{\omega_d} - \frac{I_0}{C\omega_d}\right) e^{-\alpha t} \sin(\omega_d t)$$

$$= V_0 e^{-\alpha t} \left(\cos(\omega_d t) + \frac{\alpha}{\omega_d} \sin(\omega_d t)\right) - \frac{I_0}{C\omega_d} e^{-\alpha t} \sin(\omega_d t)$$

(2.9)

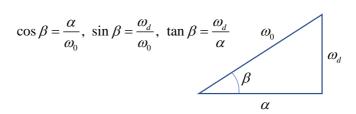

여기에서 그림 2-4와 같은 삼각함수의 관계를 이용하면 식 (2.9)는 식(2.10) 과 같이 정리할 수 있다. 또한 사고 전 초기 전류  $I_0$ 가 단락전류에 비해 그 크기가 매우 작은 경우에는 식 (2.10)은 식 (2.11)과 같이 근사화 될 수 있다.

그림 2-4. 감쇠상수, 고유주파수, 감쇠고유주파수 간 관계

$$\begin{split} v_{C.u}(t) &= V_0 e^{-\alpha t} \frac{\omega_0}{\omega_d} \left( \frac{\omega_d}{\omega_0} \cos\left(\omega_d t\right) + \frac{\alpha}{\omega_0} \sin\left(\omega_d t\right) \right) - \frac{I_0}{C\omega_d} e^{-\alpha t} \sin\left(\omega_d t\right) \\ &= \frac{V_0 \omega_0}{\omega_d} e^{-\alpha t} \sin\left(\omega_d t + \beta\right) - \frac{I_0}{C\omega_d} e^{-\alpha t} \sin\left(\omega_d t\right) \\ &\rightleftharpoons, \cos\beta = \frac{\alpha}{\omega_0}, \sin\beta = \frac{\omega_d}{\omega_0}, \tan\beta = \frac{\omega_d}{\alpha} \,. \end{split}$$

(2.10)

$$v_{C.u}(t) \approx \frac{V_0 \omega_0}{\omega_d} e^{-\alpha t} \sin(\omega_d t + \beta).$$

(2.11)

위에서 구한 식 (2.11)을 식 (2.4)에 대입하면 식 (2.12)와 같은 전류방정식을 도출할 수 있다. 이는 기존 연구 [50]의 식과도 같다. 여기에서도 사고 전 초기 전류  $I_0$ 가 단락전류에 비해 그 크기가 매우 작은 경우에는 초기 전류에 관한 항을 생략할 수 있다.

$$i_{C,u}(t) = -C \frac{dv_{C,u}(t)}{dt}$$

$$= \frac{V_0}{\omega_d L} e^{-\alpha t} \sin(\omega_d t) - \frac{I_0 \omega_0}{\omega_d} e^{-\alpha t} \sin(\omega_d t - \beta).$$

$$\approx \frac{V_0}{\omega_d L} e^{-\alpha t} \sin(\omega_d t)$$

(2.12)

Case ii) 과감쇠(Overdamping)인 경우  $(v_{C,o}(t), \alpha^2 > \omega_0^2)$

기존 연구에서도 과감쇠인 경우에 대한 수식을 분석한 바가 있으나, 역시 상세한 식은 주어져 있지 않다 [51]. 식 (2.7)을 라플라스 역변환 하기 위해서 식 (2.13)과 같이 분자에 s를 포함한 부분과 상수인 부분으로 나누어 정리할 수 있다.

$$v_{C,o}(s) = \frac{sV_0 + 2\alpha V_0 + \frac{dV_0}{dt}}{\left(s + \alpha - \sqrt{\alpha^2 - \omega_0^2}\right)\left(s + \alpha + \sqrt{\alpha^2 - \omega_0^2}\right)}$$

$$= \frac{sV_0 + \frac{R}{L}V_0 - \frac{I_0}{C}}{\left(s + a\right)(s + b)} = \frac{sV_0}{\left(s + a\right)(s + b)} + \frac{\frac{R}{L}V_0 - \frac{I_0}{C}}{\left(s + a\right)(s + b)}$$

(2.13)

이 좌항과 우항을 라플라스 역변환하면 식 (2.14)와 같이 정리할 수 있는데, 초기 전류  $I_0$ 가 충분히 작은 경우  $I_o$ 가 포함된 항을 생략할 수 있다. 여기에서는 a > b > 0이므로  $a \cdot e^{-bt}$  항이 가장 지배적 (dominant)임을 알 수 있다. 또한 수식에서 확인할 수 있듯이, 과감쇠인 경우에는 캐패시터 전압이 0으로 떨어지지 않아 2 단계가 생략된다.

$$v_{C,o}(t) = \frac{V_0}{a - b} \left( ae^{-at} - be^{-bt} \right) + \frac{\frac{R}{L}V_0 - \frac{I_0}{C}}{a - b} \left( e^{-bt} - e^{-at} \right)$$

$$\approx \frac{-bV_0 + 2\alpha V_0}{a - b} e^{-bt} + \frac{aV_0 - 2\alpha V_0}{a - b} e^{-at}$$

$$= V_0 \frac{\left( a \cdot e^{-bt} - b \cdot e^{-at} \right)}{a - b}$$

(2.14)

당,

$$\alpha = \frac{R}{2L} = \frac{a+b}{2}$$

,  $a = \alpha + \sqrt{\alpha^2 - \omega_0^2}$ ,  $b = \alpha - \sqrt{\alpha^2 - \omega_0^2}$ .

위의 과감쇠 시 캐패시터의 전압방정식을 식 (2.4)의 관계를 이용하여 캐패시터 전류에 대한 해를 구하면 식 (2.15)과 같이 나타낼 수 있다.

$$i_{C,o}(t) = -C \frac{dv_{C,o}(t)}{dt} = -C \cdot \left( \frac{a \cdot bV_0}{a - b} e^{-at} - \frac{a \cdot bV_0}{a - b} e^{-bt} \right)$$

$$= \frac{V_0}{L(a - b)} \left( e^{-at} - e^{-bt} \right)$$

(2.15)

당,

$$\omega_0 = \frac{1}{\sqrt{LC}} = \sqrt{a \cdot b}$$

,  $a = \alpha + \sqrt{\alpha^2 - \omega_0^2}$ ,  $b = \alpha - \sqrt{\alpha^2 - \omega_0^2}$ .

다이오드 환류가 발생하는 사고 2 단계는 그림 2-5와 같이 1 단계의회로에서 다이오드를 통한 경로가 추가되는데, 다이오드의 등가회로모델링에 따라 수식의 복잡도가 달라진다. 즉, 다이오드를 이상적이거나 문턱전압만 존재하거나, 순방향 다이오드 저항( $r_d$ )이 1 단계의 등가저항 R에 비해무시할 수 있을 정도로 작으면 등가회로의 방정식도 식 (2.16)과 같이간단하게 해석할 수 있다.

그림 2-5. 고장 2단계의 주요 경로

$$i_L(t) = I_1 \cdot e^{-\frac{R}{L}t} \tag{2.16}$$

하지만 순방향 다이오드 저항을 무시할 수 없다면 큰 전류로 인한다이오드에서 큰 전압 강하가 발생하고, 병렬로 연결된 캐패시터를역방향으로 다시 충전하게 되면서 식 (2.17)과 같이 복잡한 수식으로나타나게 된다 [51]. 여기에서 R, L은 다이오드를 제외한 등가 저항과 등가인덕턴스, C는 DC 링크 캐패시턴스, I1은 1단계 종료시 인덕턴스에 흐르던 2단계 초기 전류, ra는 직병렬로 연결된 다수의 다이오드를 등가적으로 계산한순방향 다이오드 저항값이고 다이오드 턴온 전압 va는 기여하는 바가 작아생략하여 표현하였다. 간단한 경우나 복잡한 경우 모두 2단계 초기 전류 I1상수값이 필요하므로 1단계 종료시에 흐르던 전류에 대한 계산을 완료하는것이 중요하다.

$$\begin{split} i_L^{\ \prime}(t) &= I_1 \left\{ \! \left( b^\prime + \frac{R}{L} \right) \! e^{a^\prime t} + \! \left( 1 \! - \! b^\prime - \! \frac{R}{L} \right) \! e^{b^\prime t} \right\}. \end{split} \tag{2.17}$$

$$\ \ \ \Box, \ \alpha^\prime = \frac{R}{2L} + \frac{1}{2r_aC}, \omega_0^\prime = \frac{1}{\sqrt{LC}} + \frac{R}{\sqrt{r_aLC}}, a^\prime = -\alpha^\prime + \sqrt{\alpha^{\prime 2} - \omega_0^{\prime 2}}, b^\prime = -\alpha^\prime - \sqrt{\alpha^{\prime 2} - \omega_0^{\prime 2}} \end{split}$$

계통 유입단계인 고장 3 단계의 고장 전류는 주로 계통연계 리액터 L과 다이오드를 통하여 흐르게 된다. 3 상 계통 전압과 연계하고 있는 컨버터 입장에서는 최대 선간 전압이 고장 전압원이 되며, 각 상의 위상에 따라 고장 전압원이 되는 상의 조합도 지속적으로 바뀌게 된다. 예를 들어 u상 상단과 w상 하단의 다이오드를 통한 일 순간의 도통상태는 아래 그림 2-6과 같다.

그림 2-6. 고장 3단계에서의 단락 전류 유입경로

J.Yang은 3상 계통에 대한 고장 전류 분석을 수행하기 위하여 우선 하나의 상(one-phase)에 대한 분석을 수행한 후 이를 합산하였다 [50]. 먼저, 고장 3 단계에서의 u상 계통 전압은 다음 식(2.18) 과 같이 표현될 수 있다.

$$v_{Gu}(t) = V_G \sin(\omega_s t + \delta). \tag{2.18}$$

단,  $V_{G}$ 는 계통 전압 크기,  $\omega_{s}$ 는 동기 각 주파수,  $\delta$ 는 3단계 시작 시의 A상 전압각이다. u상 전류는 다음과 같이 표현된다고 알려져 있다 [50].

I<sub>60</sub>와 φ<sub>0</sub>는 초기 계통 전류 크기와 전류각이며 L<sub>7</sub>은 계통연계 리액터의 상인덕턴스이다. ν상과 ν상은 각각 ν상으로부터 120도, 240도 위상 차가존재하고, 각각 전류가 양의 방향으로 흐를 때에 다이오드에 순방향으로 전류가 흐를 수 있다는 점을 고려하여 3개 상의 전류를 식 (2.20)과 같이합산할 수 있다. 최종적으로 계산되는 전류 수식은 참조 문헌 [50]에 제시되어있으나 지나치게 복잡하여 본 논문에서는 생략한다.

$$i_G(t) = i_{Gu,(>0)} + i_{Gv,(>0)} + i_{Gw,(>0)}$$

(2.20)

지금까지 살펴본 바와 같이 고장 1 단계에서는 전력반도체가 단락전류의 회로에 포함되지 않았지만 2 단계와 3 단계에서는 고장 전류가 역방향다이오드를 통하게 된다. 통상적으로 최소저항값을 1 mΩ으로 가정하면 저감쇠 상태로 전력반도체로 환류하는 2 단계까지 진행될 확률이 높으므로 1 단계에서 선택 차단을 완료하는 것이 적절하다 [52], [53].

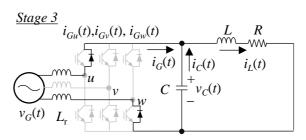

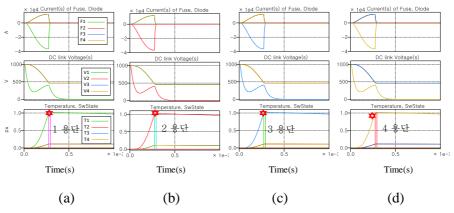

하지만 만약 1 단계에서 차단을 완료하지 못하여 2 단계 또는 3 단계까지 진행되더라도, 퓨즈는 별도의 후비보호 없이 차단이 가능하다. 예를 들어그림 2-7 (a)는 그림 2-1의 회로에서 1 단계 내에서 용단되도록 퓨즈의 용단 It를 6.2 A²s로 설정했을 때의 모의실험 결과이며, 그림 2-7 (b)는 62 A²s로 크게 설정하였을 때의 결과이다. 퓨즈는 내부 도체에서 발생하는 열에 의해용단되는 원리를 가지고 있는데, 캐패시터 방전 전류 외에 발전원으로부터고장 전류가 지속적으로 공급되기 때문에 후비 보호를 적용한 것과 같은최종적인 용단이 가능하다. 다만 2 단계에서 건전한 전력반도체에 막대한 환류전류가 흐르므로 소손이 발생할 우려가 있다.

그림 2-7. 고장 단계 별 퓨즈 용단 모의 시험결과

(a) 퓨즈의 용단 *l²t가* 6.2 A²s인 경우, (b) 용단 *l²t가* 62 A²s인 경우

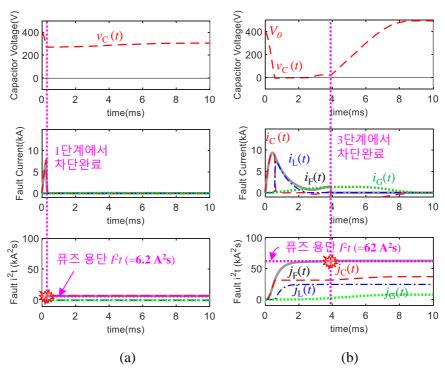

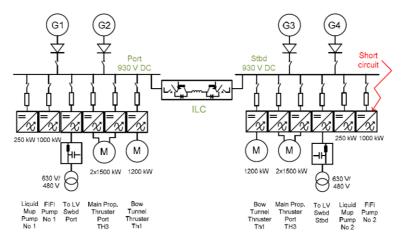

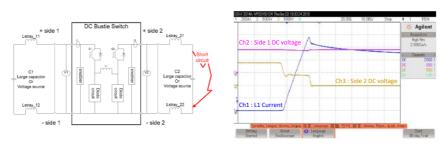

그림 2-8은 미 해군 선박에 적용된 DC 전력시스템의 간략화된 구성도이다 [12]. 우현(Stbd 또는 Starboard)과 좌현(Port) 측 2 개 버스로 구성되어 있으며, 그 사이에는 유사시 수 십  $\mu$ s 내 고속 차단이 가능한 반도체 차단기의 역할을 하는 ILC(Intelligent Load Controller)로 연결되어 있다. 각각의 버스 내부에는 다이오드 정류기로 연결된 발전기, 수 MW의 전동기 및 드라이브용 VSC, 정전압-정주파수 AC 전원을 공급하기 위한 다수의 MW급 VSC들로 이루어져 있음을 볼 수 있다. 해당 연구에서는 FiFi Pump No. 2의 위치에서 VSC 대신 인공적인 단락을 발생시켰는데, 해당 퓨즈 실험 파형은 그림 2-9와 같다. 해당 논문에는 자세한 파라미터가 주어져 있지 않지만, 320  $\mu$ s 동안 전류가 50 kA 상승하였으므로 평균 상승률이 156 kA/ms에 달하는 것을 확인할 수 있다.

그림 2-8. 미 해군 선박의 DC전력시스템 구성도 및 고장지점 [12]

그림 2-9. 미 해군 선박 내 인공 단락시 고속 퓨즈 차단 실험결과 [12]

유사한 구성을 가진 다른 실제 선박들의 버스 파라미터를 R-L-C 등가회로로 재구성하고, 만약 버스 내의 한 지점에서 등가 저항이 0인 단락사고가 발생했다고 가정했을 때 식 (2.12)를 참조하여 초기 고장전류 기울기, 피크 전류 크기, 1 단계 종료시점을 계산하면 표 2-1과 같이 나타낼 수 있다.

표 2-1. 실제 선박용 DC전력시스템 1개 버스의 등가회로 파라미터

| 항목                       | 버스 A  | 버스 B  | 버스 C  | 버스 D  |

|--------------------------|-------|-------|-------|-------|

| 버스 내 총 VSC용량(kW)         | 11000 | 9700  | 5020  | 4200  |

| 버스 내 VSC 수               | 9     | 7     | 5     | 3     |

| 버스 정격전압 <i>V₀</i> (V)    | 930   | 930   | 1100  | 1100  |

| VSC 평균정격전류 <i>I₀</i> (A) | 1308  | 1490  | 913   | 1273  |

| 배전반 버스 길이(m)             | 8.6   | 9.8   | 8     | 6     |

| 등가인덕턴스 L(μH)             | 11.6  | 11.1  | 8.6   | 5.9   |

| 등가캐패시턴스 C(mF)            | 170.7 | 132.1 | 120   | 80    |

| 초기고장전류기울기(kA/ms)         | 80.1  | 83.9  | 128.2 | 185.2 |

| 미차단시 피크전류크기(kA)          | 112.7 | 101.5 | 130.1 | 127.7 |

| 예상 1단계종료시점(ms)           | 2.2   | 1.9   | 1.6   | 1.1   |

위의 경우를 살펴보면 미 해군 선박의 경우와 유사하게 수 백 kA/ms에 달하는 기울기로 상승하며, 1 단계에서 미차단시 다이오드로 흐를 수 있는 피크 전류의 크기가 100 kA 정도에 이를 수 있음을 확인할 수 있다. 만약 1 단계가 종료되는 수 ms내에 사고 피더가 차단되지 않으면, 정격이 1-2 kA밖에 되지 않는 나머지 VSC의 다이오드를 통해 100 kA에 달하는 전류가 환류되어 소손을 발생시킬 수 있다. 이처럼 실제 파라미터를 기반으로 분석해보아도, 다이오드 측으로 고장 전류가 흐르지 않는 1 단계 구간 내에서 사고 전류를 차단하는 것이 바람직하다.

## 2.2 DC 보호시스템 설계 시 고려사항 및 상용화 사례

### 2.2.1 보호시스템의 개요

전력시스템의 보호계전(protective relaying)은 시스템의 비정상적인 동작으로 인한 감전이나, 화재로 인한 인명과 재산상의 상해를 최소화하고, 전력 공급 연속성의 최대화를 위하여 제어되는 전력 시스템 내의 보호기기들의 동작을 의미한다. 다시 말하면, 이 전략은 고장 기기를 보호하는 것이 아니라 고장 기기의 영향으로부터 정상적인 시스템과 주변환경을 보호하기 위한 것이다 [34]. 보호시스템(protection system)은 보호원리에 기초하여 지정된 보호기능을 달성하기 위한 보호장비(protection equipments) 및 기타 장치들의 완성된 배치를 의미한다 [54].

보호시스템은 일반적으로 다음의 보호 원리로 구성된다 [34], [55].

- 선택성(selectivity) : 최소한의 전력 공급 중단이 발생하도록 고장난 부위만을 격리하는 것. 사고에 가장 가까이 있는 보호기기들이 사고기기를 제거하기 위해 동작하는 보호전략의 전체적인 설계

- 민감도(sensitivity) : 시스템의 비정상적인 상태를 식별하는 능력

- 신뢰성(reliability): 보호시스템이 조치를 취해야 할 때 올바르게 작동할 확률. 보호 구역 내 고장에 대해서는 동작, 보호 구역 밖의 고장이나 고장이 없는 경우에 불필요하게 작동해서는 안된다.

- 신속성(speed) : 기기의 손상을 줄이고 시스템의 불안정성을 피하기 위한 빠른 동작

- 단순성(simplicity) : 보호기기와 관련된 부품 수의 최소화

- 경제적효율성(economical efficiency) : 최소 비용으로 높은 기능성

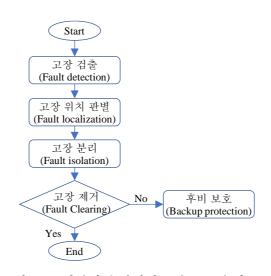

위의 보호원리를 고려하여 보호기능을 달성하기 위한 일반적인 보호 시스템의 동작 순서를 구성하면 그림 2-10과 같다 [56]. 첫 번째로, 단락 사고 등 비정상적인 현상이 일어났을 때, 민감하게 고장을 검출(fault detection) 해야한다. 두 번째로는 고장 기기를 선택적으로 분리시키기 위해 그 고장 위치를 정확하게 판별(fault localization)하는 것이 필요하다. 세 번째는 경제적인 방식으로 신속하고 확실하게 고장을 분리(fault isolation)하여 다른 건전 기기들이 입을 수 있는 피해를 최소화하는 것이 중요하다. 마지막으로 위의 주 보호 과정을 통해 고장이 신뢰성있게 제거되지 못했을 때, 고장확산을 막기 위해 같은 지점 또는 더 큰 범위에서의 후비 보호(Backup Protection)가 필요하다.

그림 2-10. 일반적인 전력시스템 보호 순서 [56]

보호 동작의 구현을 위해서, 먼저 고장 감지 및 위치 파악을 위한 장치가 필요하다. 계전기(relay)는 전력시스템에 단락이나 지락사고가 발생할 경우 또는 절연파괴의 원인이나 계통의 나머지 부분에 악영향을 주는 이상 상태가 생겼을 때, 이를 검출하여 차단기를 동작시켜서 사고 부분을 신속히 계통에서 분리시키도록 지령을 내보내는 장치이다 [57]. 그 중 과전류 계전기(overcurrent relay)는 계전기에 흐르는 전류가 설정 값 이상일 때 작동하는 계기로, 전기설비를 과전류로부터 보호하며, 전기회로에서 단락사고를 막는데 널리 이용된다. 보호협조 (protection co-ordination)는 복수 개의 계전기상호 간에서 시간에 따라 또는 사고 전류 크기에 따라 서로 구분하면서보호를 행하는 것이다.

차단기(circuit breaker)는 비자동적 수단에 의하여 회로를 개폐하며, 미리

정해진 전류의 과부하를 이용해 자동적으로 회로를 개방하는 장치이다. 또한 정격 범위 내에서 바르게 쓰이는 경우 아무 손상도 생기지 않도록 설계되어야 한다 [57]. 퓨즈(fuse)는 과전류 보호장치의 하나로 단락전류 및 과부하전류를 자동적으로 차단하는 가용체이다 [57].

그림 2-11. 계전기, 차단기, 퓨즈 예시 [58]-[60]

### 2.2.2 DC 보호시스템 설계시 고려 사항

2.1.절에서 살펴본 DC 전력시스템 내 단락사고의 전류 상승 속도를 고려했을 때, 기존의 AC 전력시스템보다 상당히 빠른 시간안에 보호 동작이 이루어져야 함을 알 수 있다. 이러한 특징을 가진 DC 전력시스템의 보호와 관련한 많은 연구가 진행되어 왔으며, 주요 기술 현황은 다음과 같다.

#### 1) 고장 검출 및 위치 판별

이 기능은 앞에서 언급한 계전기에 해당하는 부분으로 크게 직접적인(direct)방법과 신호처리 (signal processing)에 기반하는 방법이 있다 [61]-[66]. 일부 방식은 고장 검출과 동시에 위치까지 판별하게 되므로 여기서는 통합하여 설명한다.

직접 측정 방식은 전압과 전류를 직접 측정하여 빠르게 고장을 판별할 수 있지만 노이즈에 민감할 수 있다. 대표적인 5가지 방식은 아래 설명 및 표 2-2와 같다.

표 2-2. 주요 직접 측정 보호 방식의 비교 [67]

| 보호 방식        | 과전류                            | 전류변화율                          | 임피던스 추정                                    | 방향성                             | 차동                |

|--------------|--------------------------------|--------------------------------|--------------------------------------------|---------------------------------|-------------------|

| 검출 조건        | 문턱값 이상의<br>전류 발생 시             | 문턱값 이상의<br>전류변화율<br>발생 시       | 선로 인덕턴스가<br>작게 추정될 시                       | 고장 전/후의<br>전류방향변화               | 전류 합이 0이<br>아닐 때  |

| 측정위치,        | 지역측정,                          | 지역측정,                          | 지역측정,                                      | 전역측정,                           | 전역측정,             |

| 필요해상도        | 중/고 해상도                        | 중/고 해상도                        | 중/고 해상도                                    | 고 해상도                           | 저 해상도             |

| 통신           | 불필요                            | 불필요                            | 불필요                                        | 필요                              | 필요                |

| 민감도 및<br>신뢰성 | 왜곡된 고장<br>전류에 민감               | 왜곡된 고장<br>전류에 민감               | 이웃 보호영역의<br>고장과 고장<br>임피던스에 민감             | 과도상태의<br>동적작용에 민감,<br>통신에 매우 의존 | 통신에 매우 의존         |

| 실제 적용시<br>이슈 | 문턱값 선정,<br>전류제한방식과<br>동시사용 어려움 | 문턱값 선정,<br>전류제한방식과<br>동시사용 어려움 | 고속/정확한<br>인덕턴스 계산,<br>전류제한방식과<br>동시사용 어려움. | 통신 능력에 따라<br>제한발생               | 통신 능력에 따라<br>제한발생 |

과전류 보호 방식(overcurrent protection) 은 AC 전력시스템에서도 많이 사용하는 방식인데, 도통 전류가 과전류 레벨을 넘는 경우 고장으로 인식하는 방법이다. 상위 장치에서 다수의 하위 장치로 전력을 공급할 때, 두 기기 간보호협조를 위해서는 두 레벨이 충분한 여유를 두고 설계되어야 하며, 그렇지 않으면 선택성이 줄어들 수 있다. 또한 높은 고장 임피던스에 대해서는 고장 전류가 크지 않기 때문에 낮은 민감도를 보이는 특징이 있다 [68].

전류 변화율 보호 방식(current-derivative protection)은 전류의 미분값을 측정 및 계산하는 것으로, 매우 짧은 시간에 고장을 감지할 수 있다. 하지만 시스템을 구성하는 다수 파라미터의 영향으로 감지 레벨을 정하기가 어렵고, 높은 대역폭의 센서가 필요하며 노이즈에 약하다는 것이 단점이다 [69].

방향성 과전류 보호 방식(directional overcurrent protection)은 다수 계전기간의 통신을 통해 여러 곳의 전압과 전류를 감시하고 있다가 일부 전압과전류 방향이 비 정상적으로 갑자기 달라지는 경우 고장 위치를 판별해낼 수있는 방법이다 [70], [71]. 하지만 이를 구현하기 위해서는 또한 각각 높은 대역폭의 센서와 통신이 필요하다.

임피던스 추정 보호 방식(distance protection)은 측정지점에서부터 사고 지점까지 임피던스를 반복적으로 예측함으로써 고장을 감지하는 방식이다. 하지만 연산에 적어도 10-20 ms가 소요되고 짧은 케이블 구간이나 높은 고장 저항 발생시에는 낮은 성능을 보인다 [72], [73].

차동 보호 방식(differential protection)은 입력과 출력의 전류를 측정하여 차이가 발생한 경우에 고장으로 간주한다. 하지만 센서 오류에 취약하고, 다수 측정과 엄격한 통신시스템이 필요하여 높은 비용이 든다 [74]-[76].

그 외 최근 연구되고 있는 신호처리 보호방식으로는 진행파 기반 방식, Wavelet 변환 및 인공신경망 방식 또는 신호 주입 방식 등이 있다. 진행파 기반 방식(travelling wave based)은 HVDC 등에서 고장 시 입사파와 반사파의 시간 차를 측정하여 고장 위치를 추정하는 방식이다. 하지만 이는 고성능의 데이터 수집 장치가 필요하고, 선박과 같은 컴팩트한 시스템에는 적합하지 않다 [77]-[79].

Wavelet 변환 및 인공신경망 방식은 Wavelet 파형을 통한 고장 감지와 고장 구분을 할 수 있지만 큰 메모리와 많은 연산 시간이 필요하다 [80], [81].

신호 주입방식은 프로브 유닛으로 전력시스템에 신호를 주입하여 임피던스를 예측하는 방식이다. 통신은 필요하지 않지만 부가적인 장비가 필요하기 때문에 비용이 상승한다 [82], [83].

위의 방식들을 구현하기 위한 실질적으로 계전기의 측정부분에 해당하는 전류센서의 선정이 중요하다. 전류 센서는 사고 감지 알고리즘에 필요한 정보를 신속하고 정확하게 제공해야 하는데, DC 전력시스템은 DC 전류를 기본적으로 측정해야 하고, 높은 고장 전류도 측정해야 한다. AC 전력시스템에서 사용된 변류기(current transformer)는 DC 성분 측정이 안되고, 감지 대역폭이 수 kHz에 불과하고 높은 전류에 대해서는 비선형적이며 포화되는 특성을 가지고 있다 [84]. 따라서 전류 센서의 값 포화 및 선형성, 전류 측정폭, 손실, 가격적인 측면까지 고려하여 표 2-3과 같은 다양한 방식이 DC 전력시스템의 보호를 위해 검토되고 있다 [85].

표 2-3. 다양한 전류센서의 특성 비교 [85]

| 전류 측정 기술       | Low Resistance | Current     | Hall Effect | Rogowski  |

|----------------|----------------|-------------|-------------|-----------|

|                | Current Shunt  | Transformer | Sensor      | Coil      |

| 비용             | Very Low       | Medium      | High        | Low       |

| 선형성            | Very Good      | Fair        | Poor        | Very Good |

| 고전류 측정         | Very Poor      | Good        | Good        | Very Good |

| 전력소비           | High           | Low         | Medium      | Low       |

| 전류포화문제         | No             | Yes         | Yes         | No        |

| 온도영향           | Medium         | Low         | High        | Very Low  |

| DC오프셋문제        | Yes            | No          | Yes         | No        |

| 포화 및 히스테리시스 문제 | No             | Yes         | Yes         | No        |

#### 2) 고장 분리(fault isolation)

위의 차단기의 기능에 해당하는 것으로, 크게 고장 전류에 대해서 차단기로만 대응하는 차단기 기반 방식(breaker based)과, 고장 전류 제한이 가능한 토폴로지로 전류를 제어하고 전기적으로 분리한 후 시스템을 다시 복구하는 Breaker-less 방식이 있다 [86], [87].

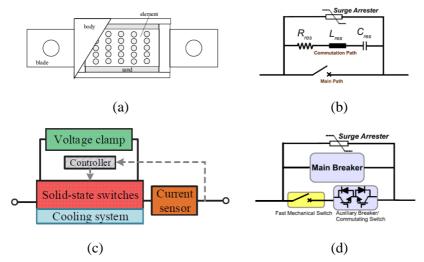

차단기 기반 방식은 크게, 관련 표준이 존재하고 제조사가 풍부한 기계식 차단기와 퓨즈가 있으며, 표준은 아직 없지만 상용화가 이루어지고 있는 반도체 차단기, 아직 연구 단계인 하이브리드 차단기가 있다 [12], [88]-[90]. 각 차단기의 주요 회로를 나타내면 그림 2-12과 같다.

퓨즈는 내부에 과전류시 용단되는 엘리먼트(element)와 아크 흡수체만 존재하므로 구조가 간단하고 부피가 작고 저렴하다는 장점이 있다. 또한 국제 표준 시험 방법에 의해 데이터시트의 특성이 도출되므로 평가 기준이 일정하고 제조사가 많다. 최근에 사용되고 있는 반도체 보호용 고속 퓨즈는 100 μs까지 시간-전류 특성이 표시 되지만 더 짧은 시간에서도 동작이 가능하기 때문에 선박과 같이 낮은 인덕턴스를 가진 DC전력시스템에서 사용이 가능하다 [91]. 하지만 공급되는 줄 열(Joule heat)로 엘리먼트가 녹을 때까지 기다려야 하므로 시간 응답성이 낮고, 과도 상태와 영구적인 고장을 구분하기가 어려우며, 한 번 사용 후에는 수동으로 교체해야하는 단점이 있다.

그림 2-12. DC 전력시스템에 사용 가능한 주요 차단기 형태

(a) 고속 퓨즈[44], (b) 기계식 차단기[85],

(c) 반도체 차단기[68], (d) 하이브리드 차단기[85]

기계식 차단기(mechanical circuit breaker)는 AC 전력시스템에서 많이 사용하는 기기로, 평소에는 두 도체가 붙어 있어 손실이 매우 낮고 가격도 저렴한 편이다. 하지만 차단 명령시에는 스프링, 전자석 등의 기계적 구동방식을 사용하여 도체 접점을 개방하는데, 이에 보통 수 십 ms가소요된다. 하지만 최근 연구에 의하면 톰슨 코일 사용 시에는 동작시간을 1-3 ms까지 줄일 수 있다 [92], [93]. 또한 고장 전류를 차단하기 위해 스위치접점을 개방할 때, 두 도체 사이에 전기 아크가 발생하게 되는데 AC와 달리영전류가 없어 아크 소호가 어려운 특징이 있다. 따라서 인위적인 영 전류구간을 만들기 위해 그림 2-12(b)와 같이 공진 회로를 이용하는 방식도 제안되었다 [94].

반도체 차단기(solid-state circuit breaker)는 전력반도체를 사용하여 고장 전류를 수 십 μs 이내로 고속 차단하는 것이 가능하지만, 평소에는 전력반도체를 통한 비교적 큰 도통 손실이 발생하여 냉각 시스템이 필요하고 방열판 부피가 커지는 단점이 있다. 따라서 반도체 차단기에 적합한 전력반도체를 찾는 연구가 다수 이루어지고 있다 [95]-[98].

하이브리드 차단기는 기계식 차단기의 낮은 손실과, 반도체 차단기의 빠른

차단 속도의 장점을 결합한 것이다. 최근 대부분의 연구 주제는 그림 2-12(d)의 Main Breaker 부분에 맞춰져 있다 [99].

표 2-4에서는 위에서 설명한 여러가지 차단기 방식의 장단점을 비교하고, 각각에 대한 표준과 제품의 성숙도를 표시하였다. 표준 및 제품의 성숙도는 기술적으로는 가격이 안정화되었으며, 현재 DC전력시스템에 상용화 적용이가능함을 나타낸다. 향후에는 하이브리드 및 반도체 차단기가 DC 전력시스템에서 필수적인 부분이 될 것으로 예상되지만, 현재의 고속 퓨즈는 과도기적인 단계에서 기존 AC 전력시스템과 DC 전력시스템의 비용적격차를 해소하고 보호와 차단에 도움을 줄 수 있는 실행 가능한 옵션으로 판단된다 [47].

표 2-4. DC전력시스템에 적용 가능한 차단기 비교

| 보호기기              | 장점                                    | 단점                                     | 표준, 제품 |

|-------------------|---------------------------------------|----------------------------------------|--------|

| 포호기기              | ~ ~ ~ ~ ~ ~ ~ ~ ~ ~ ~ ~ ~ ~ ~ ~ ~ ~ ~ | ###################################### | 성숙도    |

|                   | - 간단한 구조, 낮은 가격                       | - 과도상태와 영구고장 구분 불가                     |        |

| 고속 퓨즈             | - 작은 부피, 낮은 손실                        | - 1회 사용 후 교체 필요                        | 0      |

| [47], [68], [100] | - 높은 차단 능력                            | - 온도, 피로 등 환경 영향이 큼                    | О      |

|                   | - 빠른 동작 가능(< 수 ms)                    | - 동작을 위해 실제 전류 인가 필요                   |        |

| 기계식 차단기           | - 상대적으로 낮은 가격                         | - 긴 동작시간(30-100 ms)                    | 0      |

| [68], [94]        | - 매우 낮은 손실                            | - 제한된 차단 능력                            | U      |

| 반도체 차단기           | - 빠른 동작속도(<100 μs)                    | - 높은 가격, 높은 손실                         | Δ      |

| [101], [102]      | - 차단 횟수 무제한                           | - 큰 부피(히트싱크)                           |        |

| 하이브리드             | - 낮은 손실                               | - 매우 높은 가격                             | X      |

| 차단기[99]           | - 빠른 동작속도(수 ms)                       |                                        | Λ      |

Breaker-less 방식은 DC측 전류 제어가 가능한 컨버터로 고장 전류를 완화하여 정격 이하 또는 무부하 상태에서 개폐기를 개방하여 고장 지점을 분리하는 방식이며, 이 방식은 차단기의 필요성을 크게 낮출 수 있다 [104]-[106]. 하지만 흔히 이용되는 2레벨 컨버터는 DC측 전류 제어가 불가능하므로 싸이리스터 정류기 또는 전류형 컨버터, Full-bridge 기반 MMC (modular multilevel converter) 등의 토폴로지가 적용가능하다. 하지만 고장 감지, 위치 파악에 관련한 복잡도와 다수의 컨버터와 컨택터 간 보호 협조의

필요성이 증가된다. 이런 방식은 중앙집중화된 통신에 크게 의존하므로 통신이 불능화되었을 때 보호 성능이 떨어진다. 그리고 차단기 방식에 비해서는 일반적으로 차단 시간이 오래 걸린다는 단점이 있다.

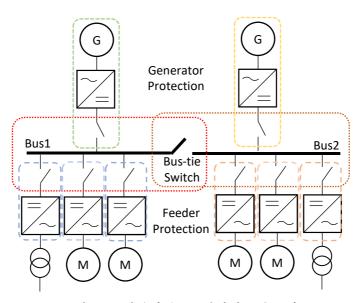

#### 2.2.3 상용화된 DC 보호시스템 사례

위의 실질적인 문제를 상용화된 보호시스템에서는 어떤 방식으로 접근했는지 조사해볼 필요가 있다. 아래 그림 2-13은 일반적인 선박용 DC전력시스템 구성을 발전단, 배전단, 부하단의 보호영역(protection zone)으로 구분하고 보호기기는 일반적인 스위치 형태로 표시해놓은 것이다. 그리고 표 2-5는 각 위치 별 보호기기를 적용한 방식을 제조사 별로 나타낸 것이다. 조사 결과, Bus-tie 에 사용되는 스위치는 대부분 전자식(반도체차단기)을 채택하고 있고, 피더 보호에는 대부분 퓨즈를 적용하고 있음을 알수 있다. 발전단 보호 방식은 제조사마다 차이가 있고, ABB와 Siemens는 관련자료의 설명으로 확인할 수 있으나 다른 곳은 기호 외의 설명이 부족하여 괄호로 표시하였다.

그림 2-13. 일반적인 DC 전력시스템 구성

표 2-5. 주요 제조사의 위치 별 보호기기 및 방식

| 제조사                     | ABB<br>[31] 외                  | Siemens<br>[12] | Ingeteam<br>[107] | Danfoss<br>[108] | Yaskawa<br>[13] 외 |

|-------------------------|--------------------------------|-----------------|-------------------|------------------|-------------------|

| Bus-tie<br>Switch       | 기계식차단기<br>+전자식<br>→전자식         | 전자식             | 전자식 또는<br>퓨즈      | 전자식              | 전자식               |

| Feeder<br>Protection    | 퓨즈                             | 퓨즈              | 퓨즈                | 퓨즈               | 전자식 또는<br>(퓨즈)    |

| Generator<br>Protection | 싸이리스터<br>전류제한 <b>→</b><br>(퓨즈) | 동기발전기<br>여자전류제거 | (퓨즈)              | (퓨즈)             | (전자식) 또는<br>(퓨즈)  |

먼저 발전부를 싸이리스터 기반의 토폴로지로 구성했을 때 보호시스템의 구성을 살펴보면 다음과 같다.

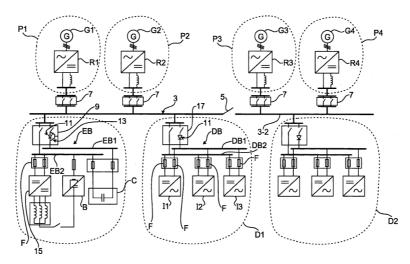

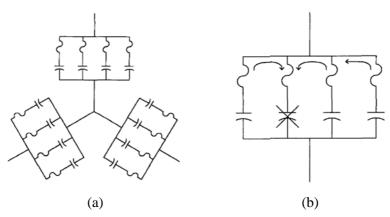

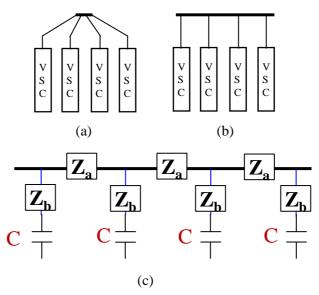

그림 2-14는 ABB사 DC전력시스템에 대한 특허 [31]의 대표도면으로, 상부의 발전단 P1, P2, P3, P4는 동기발전기(G1, G2, G3, G4) 및 싸이리스터 (Thyristor, R1, R2, R3, R4)로 구성되어 있으며 단로기(Isolator, 7번)를 통해 DC Grid zone (3번, 3-2번)과 각각 연결되어 있다. 2 개의 DC Grid zone은 버스타이 차단기(5번)를 통해서 연결되어 있으며, DC Grid Zone과 DC Link Zone (EB, DB 등)은 전류 방향에 따라 순방향 다이오드 혹은 순방향 다이오드 및 역방향 IGBT로 된 입력유닛(Input Unit, 11번)로 연결되어 있다. DC Link Zone에서 각각의 퓨즈(F)를 통하여 개별 VSC (15번, I1, I2, I3 등)가 연결되어 있으며, 퓨즈의 용단을 보조하기 위한 캐패시터 뱅크(C) 도 함께 연결되어 있는 것을 볼 수 있다. 가장 큰 특징은 캐패시턴스 존재 유무에 따라 DC Grid Zone과 DC Link Zone 으로 구분하여 보호시스템을 구성하고 있다는 점이다.

그림 2-14. ABB사의 DC전력시스템 구조[31]

문헌의 설명을 바탕으로 고장 위치 별로 전력시스템의 보호동작을 재구성하여 설명하면 아래와 같다.

## 1) 외부 버스의 DC Grid Zone이나 DC Link Zone에서 단락이 발생한 경우

건전한 DC Grid Zone에는 캐패시턴스가 존재하지 않고 동기발전기 및 싸이리스터용 DC 평활 리액터의 큰 인덕턴스로 인하여 고장 전류가 느리게 증가한다. 그리고 건전 DC Link Zone은 캐패시터 방전이 일어나지만 입력 유닛의 다이오드에 역방향 전압이 인가 되거나, 과전류를 검지하여 입력 유닛의 스위치를 고속으로 차단하여 고장지점으로의 급속한 캐패시터 방전 전류의 공급을 막을 수 있다. 따라서 버스타이(Bus-tie)에는 수 십 ms의 비교적 느린 기계식 차단기 사고보호 적용이 가능하다.

# 2) 자기 버스의 발전단 내부에서 단락이 발생한 경우

싸이리스터 내부의 퓨즈가 용단되거나, AC측 차단기에 의하여 사고 전류가 차단된다. 해당 퓨즈나 차단기는 충분히 큰 용량으로 설계되어 외부의 사고에 대해서는 차단되지 않도록 설계된다.

# 3) 자기 버스의 DC Grid Zone에서 단락이 발생한 경우

입력 유닛(11번)의 동작으로 다른 DC Link Zone으로부터의 캐패시터 방전은 막을 수 있지만 발전원으로부터의 고장 전류가 순방향 다이오드로 지속되기 때문에 발전원을 차단해야 한다. 이 경우 싸이리스터 정류기의 위상각(firing angle) 제어를 통해 고장전류를 정격전류 이내로 제한할 수 있으며 최종적으로 정격 전류 정도의 차단용량을 가진 발전단 측 단로기(Isolator) 로써 최종적으로 계통에서 분리할 수 있다.

## 4) 자기 버스의 DC Link Zone 버스바 단락이 발생한 경우

해당 DC Link Zone 내에 있는 건전 VSC들로부터 캐패시터 방전에 의한 고장전류가 빠르게 공급되며, 이후 발전원으로부터의 사고전류가 입력 유닛을 통하여 느리게 공급된다. 이 경우에는 마찬가지로 싸이리스터 정류기의 위상각 제어를 통해 사고 전류를 제한한 후, 입력 유닛과 직렬로 연결된 단로기를 개방함으로써 고장난 DC Link Zone을 분리할 수 있다.

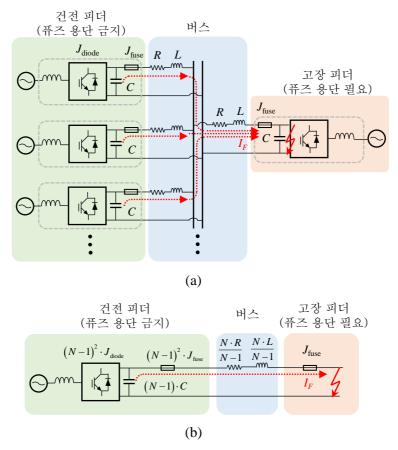

#### 5) 자기 버스의 VSC 내부에서 단락이 발생한 경우

이웃의 건전한 VSC들로부터 캐패시터 방전에 의한 고장전류가 빠르게 집중 공급되어 고장 VSC의 퓨즈가 용단된다. 적절히 설계된 경우에는 고장 VSC의 퓨즈만 용단되고 건전 VSC의 퓨즈는 용단되지 않기 때문에 일시적인 DC link 전압 강하 이후 전원 복구가 가능하다. 위와 같이 고속 차단이 완료된다면 발전원으로부터의 고장 전류는 비교적 상당히 느리게 공급되기 때문에 무시 가능하다. 하지만 만약 퓨즈가 용단되지 않고 캐패시터 전압이 0까지 떨어진 경우에는 건전 VSC에 환류전류가 발생하여 VSC의 다이오드 소손이 될 가능성이 있으며, 이후의 발전원으로부터의 지속적인 고장 전류에 대해서도 후비 보호 대책을 갖추어야 한다.

## 6) 자기 버스의 VSC 출력 외부에 단락이 발생한 경우

VSC의 출력 과전류 감지를 통해 전력반도체의 스위칭을 정지하면 쉽게 고장전류를 차단할 수 있다.

위 방식의 장점은 DC Grid Zone에서는 기존의 기계식 차단기나 단로기를 적용할 수 있다는 점이다. 이는 발전단에는 싸이리스터 정류기를 사용하여 고장 전류를 제한하고, 하위로부터는 다이오드가 포함된 입력유닛을 적용하여 캐패시터 방전과 같은 고속의 전류가 발생하지 않기 때문이다. 다만 정상 운전시 모든 부하 전류가 다이오드를 통하기 때문에 부하에 비례하는 손실이 있고, 기계식 차단기나 단로기가 고장 버스를 완전히 분리할 때까지는 정전이 발생할 수 있다. 그리고 2개 이상의 DC Grid Zone으로 구성된 경우에는 운전 중인 발전단을 모두 포함하여 다양한 시나리오에 대해서 고장 전류 해석을 해야 하기 때문에 보호협조 설정이 복잡해지는 단점이 있다. 또한 고장 위치 파악을 위해서 각 버스를 구성하는 다수 계전기 간 고속으로 통신을 하거나, 직접 여러 피더의 전류를 측정하여 종합적으로 판단할 수 있는 전력제어 시스템(Power Management System, PMS)이 필요하다.

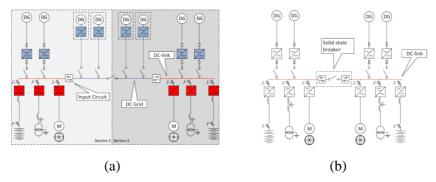

다만 위 특허는 2013년에 출원된 것이고, 2018년에 발표된 그림 2-15의자료[14]에서는 구성의 일부 변경이 있었다. 발전단이 DC Grid Zone 뿐만아니라 DC Link Zone에도 연결되면서 퓨즈가 추가되었으며, Input Circuit이연결되면서 자연스럽게 Bus-tie위치와 동일해졌다. 그림 2-15 (b)는 Siemens사의 구성과 큰 차이가 없는 구성임을 알 수 있다. 변경의 가장 큰원인은 DC링크 캐패시터를 가지고 있는 AFE(Active Front End) 방식의발전단은 캐패시턴스가 없어야 하는 DC Grid Zone에는 연결하기 어렵고, 또DC Grid에서의 고장 해석을 간소화하기 위한 것으로 추정된다.

그림 2-15. ABB사 DC전력시스템의 방식 변화 [14] (a) 2013년도 특허 방식, (b) 이후 변경된 방식

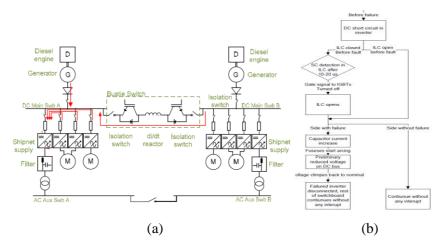

다음은 발전단을 다이오드로 구성했을 때의 보호시스템의 사례이다. 그림 2-16은 Siemens 사에서 발표한 논문[12]의 그림으로, 발전단이 다이오드 정류기로 구성되어 있고, DC Grid Zone에 해당하는 부분이 존재하지 않아 발전단의 출력이 바로 VSC가 연결되어 있는 버스에 연결된다. 그림은 맨 좌측에 있는 VSC 내부에서 단락이 발생했을 때 주요 전류의 흐름과 보호협조가 이루어지는 과정을 설명한 것이다.

그림 2-16. Siemens 사의 VSC 내부 단락 발생시 단락 사고 보호 시스템[12]

(a) VSC 고장 발생시 고장 전류의 흐름, (b) 차단분리 시퀀스

문헌에서의 설명을 바탕으로 고장 위치 별로 전력시스템의 보호동작을 재구성하면 아래와 같다.

# 1) 다른 버스의 메인버스(Main Bus)나 VSC에서 단락이 발생한 경우

버스 타이에 위치한 반도체 차단기인 ILC(Intelligent Load Controller)를 이용하여 수 십 μs 내에 차단할 수 있다. 하지만 반도체 차단기는 매우 짧은 시간 내에 전류를 차단하기 때문에 상세한 사고 위치를 판별할 수 없고, 건전한 자기 버스를 보호하는 데만 사용된다.

## 2) 자기 버스의 발전단 내부에서 단락이 발생한 경우

다이오드 정류기 내부의 퓨즈 용단이나 발전기의 여자 전류를 줄인후 단로기를 개방하여 고장전류를 차단할 수 있다. 발전단이 분리된이후에는 Bus-tie를 통해서 전원을 일부 복구할 수 있다.

#### 3) 자기 버스의 메인버스에서 단락이 발생한 경우

해당 버스 내에 있는 VSC들로부터 캐패시터 방전에 의한 고장 전류가 빠르게 먼저 공급되며, 이후 발전단의 다이오드 정류기로부터의 고장 전류는 느리게 공급된다. 다이오드 정류기는 싸이리스터 정류기와는 달리 능동적인 제어가 되지 않기 때문에, 대신 권선형 동기발전기의 여자전류를 가능한 빠른 속도로 줄여서 역기전력을 감소시켜 고장 전류를 제거할 수 있다. 다이오드 정류기 내부의 퓨즈는 메인 버스 단락에는 용단되지 않도록 설계된다.

#### 4) 자기 버스의 VSC 내부에서 단락이 발생한 경우

이웃의 건전한 VSC들로부터 캐패시터 방전에 의한 고장전류가 빠르게 집중 공급되어 고장 VSC의 퓨즈가 용단된다. 적절히 설계된 경우에는 고장 VSC만 제거되고 건전 VSC의 퓨즈는 용단되지 않기 때문에 일시적인 bus 전압 강하 이후 전원 복구가 가능하다. 만약 퓨즈가 용단되지 않고 캐패시터 전압이 0까지 떨어진 경우에는 건전 VSC에 환류 전류가 발생하여 건전 VSC까지 소손이 될 가능성이 있다. 이 경우에도 발전원에서의 고장전류는 비교적 느리게 공급되므로 고려하지 않거나 후비 보호 대책만 수립하면 된다.

## 5) VSC 출력 외부에 고장이 발생한 경우

VSC의 출력 과전류 감지를 통해 전력반도체의 스위칭을 정지하면 쉽게 고장전류를 차단할 수 있다.

위 경우는 캐패시터가 존재하는 양 단 버스 간 버스 타이에 그림 2-17과 같은 고속의 반도체 차단기를 적용하였기 때문에 건전 버스에는 정전이 거의 발생하지 않는다. ABB사가 적용한 입력 유닛(Input Unit)과 다른 점은 두 개의 IGBT를 사용하여 양방향으로 전류를 제한할 수 있고, 급격한 전류 상승을 막는 인덕터가 포함되어 있다는 점이다. 수 십~수 백  $\mu$ s 이내에 고장 버스를 분리할 수 있으므로, 능동 위치 제어(Dynamic Positioning) 중에도 Closed bus 운전이 가능하여 연료 절감이 가능하다. 또한 빠른 차단으로 이웃 버스를 고려하여 단락전류 계산을 할 필요가 없기 때문에 버스의 수가 증가하여도

독립적으로 단위 버스를 설계할 수 있다. 이웃한 버스와의 전력 차이만큼만 SSCB에 전류가 흐르기 때문에 SSCB의 도통 손실 측면에서도 유리하다.

그림 2-17. Siemens 반도체 차단기(ILC)의 구조 및 실험파형[12]

피더 보호 (feeder protection)에는 ABB, Siemens 뿐만 아니라 다수의 제조사도 반도체용 고속 퓨즈를 적용하고 있는 것을 볼 수 있는데, 이처럼 고속 퓨즈가 상용화된 주요 원인은 경제성을 꼽을 수 있다. 반도체 차단기는 고속의 전류를 센싱할 수 있는 측정부와, 판단부, 차단부를 구성하기 위해 고가의 부품들로 이루어진다. 1000 A급 반도체 차단기의 경우 약 3000 Euro 정도로 퓨즈보다 약 10배 정도 비싼 것으로 알려져 있다 [109]. 그리고 고속 퓨즈는 선박용 DC전력시스템과 같이 컴팩트한 시스템에 적용을 한정하면 다음과 같은 추가적인 경제성을 얻을 수 있다.

첫 번째, 제품에 포함되어 있는 퓨즈를 전력시스템을 위한 보호시스템으로 재해석할 수 있다면, 추가 비용이 적거나 없을 수 있다. 아무리 일회성에 확률이 낮은 고장이라고 하더라도 선박의 운항을 위해서는 고장이 일어날 경우에 보호시스템이 구비되어 있는지를 선급으로부터 확인 받아야 한다 [22], [25]. 대부분의 VSC는 내부 단락시 자체적인 보호 또는 화재를 방지하기 위해 DC측에도 퓨즈를 설치하는데, 이 VSC를 DC 전력시스템으로 구성했을 때 VSC용 퓨즈를 보호시스템의 일부로 해석할 수 있다. 그리고 설계 후 사양변경이 필요한 경우에만 다른 사양의 퓨즈를 교체 설치하면 되기 때문에 초기비용을 최소화 할 수 있다.

두 번째로는 선박용 DC전력시스템에서는 육상 마이크로그리드에 비해 교체 작업비용도 비교적 낮을 것으로 예상된다. 육상의 가공전선은 그 길이와

주변 물체의 접촉에 따라 지락 또는 단락 확률이 적지 않은데, 선박의경우에는 배전반이 집중되어 있어 전력 계통의 길이가 짧고 배전반의외함으로 보호되어 있어 실제로 버스에서 단락 사고가 일어날 확률은 낮다. 또한 VSC 자체의 보호기능이나 성능도 많이 안정화되어 VSC 내부 사고확률도 많이 낮아지고 있으므로 퓨즈의 동작 확률도 낮아지고 있다. 즉, 퓨즈가 용단되어 교체가 필요한 경우는 VSC를 교체해야 하는 경우와 거의동일하므로 퓨즈만 별도로 작업할 필요가 없으며, 작업할 확률도 점차낮아지고 있어 퓨즈 교체 작업 비용이 실제로는 높지 않을 것으로 예상된다.

# 2.3 다수 캐패시터 및 개별 퓨즈 방식에 대한 기존 연구

## 2.3.1 고속 퓨즈의 구조 및 동작 특성

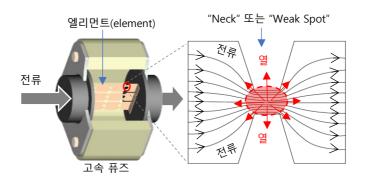

퓨즈는 정상시에는 정격 전류까지 흘릴 수 있고, 설계된 정격 전류를 크게 초과하는 전류가 흐를 때는 용단되도록 설계된 엘리먼트(element)를 내부에 가지고 있다. 이 부분이 녹아 끊어지기 시작하면서 아크가 발생하고 엘리먼트가 증발하여 주변의 석영 모래(quartz sand) 등에 흡수되면 더 이상 전류를 흘릴 수 있는 도체 부분이 존재하지 않아 고장 전류가 최종 차단된다 [42]-[44]. 특히 고속 퓨즈의 엘리먼트는 반도체 소자를 보호하기 위해 온도가 빠르게 상승할 수 있는 weak spot 구조를 가지고 있다. 만약 퓨즈의 용량이 충분하지 않으면, 일시적 과전류에 의해서도 용단될 수 있기 때문에 주의깊게 퓨즈를 선정해야 한다. 또한 온도와 과부하 사용 패턴 등 외부 환경에 의한 영향을 많이 받기 때문에 데이터시트에서 지정된 동작조건과 다를 때는 관계되는 보정계수를 적용하여 최종 정격 전류를 선정해야 한다. 외부의 신호에 의해서 임의로 퓨즈를 용단시키는 연구 [110] 및 제품 [111]이 있지만 대부분의 퓨즈는 고장 전류를 퓨즈에 직접 인가해주어야 동작한다.

그림 2-18. 고속 퓨즈의 내부 엘리먼트 구조

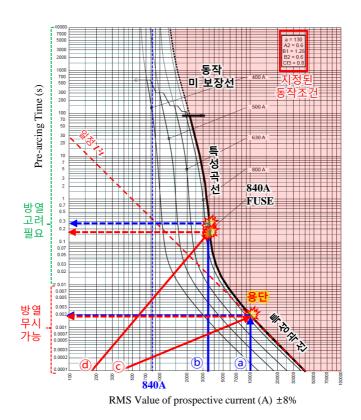

퓨즈의 데이터 시트 등에서 제시되는 시간-전류 특성(time-current characteristic, TCC)은 지정된 동작 조건에서의 용단시간이나 동작시간 등을 예상 전류의 함수로 나타낸 곡선이다. 통상적으로 시간-전류 평면의 가로축은 예상 전류(prospective current)의 r.m.s. 실효값을 로그 스케일로, 세로축은 시간을 로그 스케일로 나타낸다. 그림 2-19에서는 퓨즈 데이터

시트의 예 [60]을 바탕으로 설명을 추가하였다.

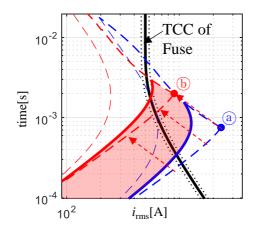

그림 2-19. 퓨즈의 용단 시간-전류 특성(TCC) 곡선 및 구간 별 설명

저전압 퓨즈 표준인 IEC 60269-1에 의하면, AC용 퓨즈는 대칭 전류의실효값을 기준으로 10 사이클 이상 흘렸을 때 용단되어 아크가 발생하는 시간, DC인 경우에는 시정수가 10에서 15 ms 인 파형에 대해서 15 시정수 이상흘렀을 때의 시간을 표준화된 실험을 통하여 산출한다 [112]. 따라서 해당전류는 거의 정상상태의 전류이며, 그림 2-19의 ⓐ, ⑤와 같은 수직선으로나타난다. 용단 시간-전류 특성(TCC) 곡선은 해당 전류에서 용단되는 시간의점을 모아서 나타낸 곡선이다. 따라서 해당 곡선은 실험적으로 약 0.1초이상의 시간에 대해서 유효하고, 그 보다 용단 시간이 짧은 경우에 제조사는참조할 수 있는 Pt 특성을 제시하도록 되어 있다.

2012년 개정된 IEC 60269-4 에서는 사고시 캐패시터 방전을 고려한 전압원 인버터 퓨즈 링크(VSI fuse-link)를 정의하고 1에서 3 ms의 낮은 시정수를 가지는 DC 전류 기준을 추가하였다 [113]. 따라서 반도체 보호용 고속 퓨즈 데이터 시트에서 10 ms 이상의 구간은 실제 실험의 결과로 TCC 곡선이 주어지며, 그보다 낮은 시간은 마찬가지로 Pt 특성값이 제시된다. 일부 제조사에서는 2 가지 정보를 통합하여 나타내기 위해 10 ms 보다 작은 구간은 Pt계산식을 이용하여 가상시간(virtural time)이라는 개념으로 TCC 곡선에함께 표시 및 제공하고 있다 [43].

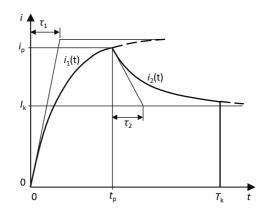

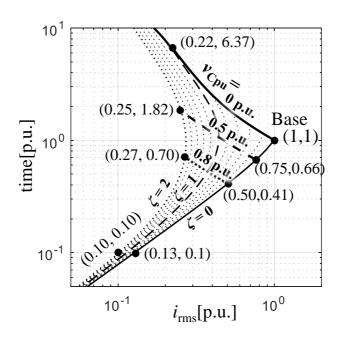

퓨즈 사용자 입장에서 정리하면, 실제로 퓨즈가 용단되는 조건은 10 ms 시간 이내에서는 제조사에서 제시한 pre-arcing Pt(또는 melting Pt) 값에 도달하거나, 고장 전류의 정상상태에서 데이터시트에 주어진 시간-전류특성(TCC) 곡선 이상으로 시간이 경과하게 되면 내부 도체가 용단되는 것으로 판단할 수 있다. EATON 사, LittelFuse 사, Mersen 사 등 다수 퓨즈 제조사들은 사용자를 위해 퓨즈 선택 가이드를 발행하고 있는데, 공통적으로 제시한 용단 유무 판별 방법은 다음 순서와 그림 2-20 및 그림 2-21과 같다 [42], [114].

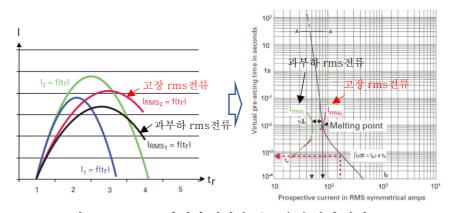

- (1) 실제 전류는 알려져 있어야 한다.( $I_1$  및  $I_2$ )

- (2) 시간에 대해 실효값(r.m.s.)을 계산한다. (I<sub>RMS1</sub>, I<sub>RMS2</sub>)

- (3) 해당 정보를 시간 전류 평면 상에 도시한다.(I<sub>rms1</sub>, t<sub>r</sub>), (I<sub>rms2</sub>, t<sub>r</sub>)

- (4) 만약 도시된 커브가 퓨즈의 시간-특성 곡선과 교차한다면, 퓨즈는 실제시간(t<sub>r</sub>)에서 용단된다.

그림 2-20. EATON사에서 제시한 퓨즈 용단 판별 방법[42]

그림 2-21. Mersen 사에서 제시한 퓨즈 용단 판별 방법[114]

이와 같이 다수 제조사에서는 고장 전류를 실효값으로 계산하고, 이것을 퓨즈의 TCC 곡선과 함께 나타냈을 때 두 곡선이 만나는 점에서 용단이 이루어진다고 설명하고 있다. 이는 퓨즈의 용단 시간-전류 특성에서 Pt가 일정한 구간에서는 성립하지만 그 보다 긴 시간에서는 엘리먼트의 방열(heat dissipation) 효과를 고려하여야 한다 [115]. 즉, 10 ms 혹은 1 ms이하의 시간대에서는 그림 2-19의 전류 ⓒ와 같이 정상상태의 전류가 아니더라도 동일한 시간에서 용단된다고 할 수 있다. 하지만 방열 효과를 고려해야 하는 10 ms 이상의 구간에서는, 그림 2-19의 전류 ⓓ가 가해질 때, 방열 시간이 충분치 않고 TCC 곡선에 비해 약간 더 빨리 용단된다고 할 수 있다.

그런데 기울기가 큰 전류의 경우에는 표피효과(skin-effect) 등의 다른 효과에 의해서 도체의 주변부부터 용단되어 좀 더 빠르게 용단될 수도 있다 [116]. 퓨즈의 정확한 동작 정보를 제공하기 위해서, 각 퓨즈 제조사는 이러한 전류의 특성을 고려하여 퓨즈의 용단 특성 데이터를 재조정하는 과정도 필요할 것으로 생각된다.

#### 2.3.2 다수 캐패시터 및 개별 퓨즈를 이용한 보호 방식

다수 캐패시터 및 개별 퓨즈를 이용한 보호 방식은 기존의 AC 변전소에서 역률 보상용으로 사용되는 커패시터 뱅크에서도 사용되고 있는 방식이다 [117]. 캐패시터 뱅크를 이루는 개별 캐패시터들은 고장 확률은 낮지만 초기투입시나 원격 스위칭 서지(surge), 뇌유도 서지 등의 과전압에 의해서 고장이 발생할 수 있다. 하지만 동시에 여러 캐패시터가 고장날 확률은 낮기 때문에 하나의 고장 캐패시터를 분리하기 위해서 아래와 같은 회로를 구성할 수 있다. 그림 2-22(a)와 같이, 먼저 캐패시터와 퓨즈를 직렬로 구성하고 이를 상 별로 다수 병렬 회로로 구성한다. 이 회로에서 단락발생시에는 그림 2-22(b)와 같이 해당 캐패시터로 다른 캐패시터의 방전 전류가 병렬로 집중되는 현상을 이용하여 고장 캐패시터를 회로에서 분리할 수 있다.

그림 2-22. 개별 퓨즈를 이용한 AC 역률 보상용 캐패시터 과전류 보호 방식[117]

(a) 상 당 4개의 캐패시터 및 개별 퓨즈가 달린 역률 보상용 캐패시터 뱅크,

(b) 한 상에서 한 커패시터 고장시 다른 캐패시터로부터의 병렬 방전

위 방식이 올바르게 동작하도록 설계하려면 다음을 고려해야 한다 [117].

- (1) 캐패시터의 정격 전류를 고려하여 정격 전류 135% 이상의 전류 정격을 가지는 퓨즈가 선정되어야 한다.

- (2) 퓨즈는 정상적이고 일시적인 과도 전류 상태를 견딜 수 있어야 한다.

- (3) 고장 시, 회로에서 퓨즈를 용단시키기 위해 필요한 전류가 발생될 수 있는지 고려해야 한다.

- (4) 전원 역할을 하는 건전 캐패시터와 퓨즈는 고장 제거시까지 전류를

견딜 수 있어야 한다.

- (5) 고장 발생시 및 고장 제거 후 다른 상의 캐패시터에 또 다른 과전압이 발생할 수 있는 지 검토해야 한다.

- (6) 다른 보호협조 방식과 충돌이 있는지 검토하여야 한다.

비슷한 관점으로, 선박용 DC전력시스템은 다수 VSC의 퓨즈를 포함한 DC링크 캐패시터가 서로 병렬로 연결되어 있는 구조를 가지고 있다. 그리고 각각의 VSC는 일반적으로 그 순간 정전 시에도 운전이 가능하도록 큰 DC링크 캐패시턴스를 가지고 있다. 그림 2-22의 사례와 유사하게 만약 DC 전력시스템의 한 지점에서 단락 사고가 발생하면, 주변의 건전한 DC링크 캐패시터로부터 사고 지점으로 큰 단락사고 전류가 급격하게 흐르게 된다. 하지만 AC 전력시스템에서의 사례와 다른 점은 극성이 바뀌지 않고 비교적 일정한 전압이 유지된다는 점이고, 만약 제 때에 고장이 제거되지 못하면 열적 내량이 낮은 전력반도체가 소손될 수도 있다는 점이다.

따라서 VSC 기반 DC전력시스템의 단락보호시스템은 캐패시터 전압이 0이 되기 전에 고장 지점을 선택적으로 차단(discrimination)하여 정상 동작중인 전력반도체를 보호하는 것이 중요하다. 가능하다면 영전압까지 떨어지도록 기다릴 것이 아니라 정상 VSC의 안정적인 동작이 가능한 전압강하 범위 내에서 사고 부위를 차단하고 시스템 전압을 회복하는 것이 DC전력시스템의 좀 더 안정적인 보호 방법이라고 할 수 있다. 따라서 사고시 캐패시터의 전압과 단락사고 전류를 사전에 분석하여 단락보호시스템의 동작이 원하는 조건 하에서 원활히 일어날 수 있도록 해야 한다.

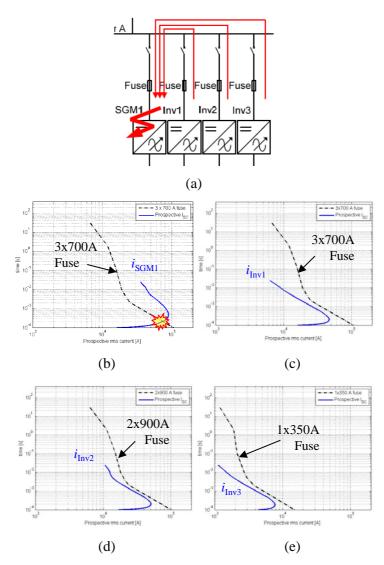

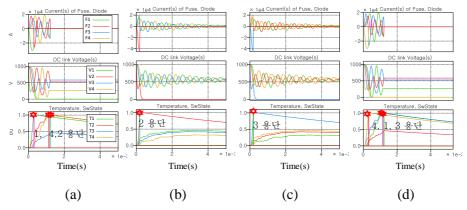

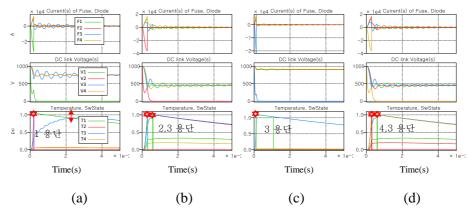

그림 2-23(a)는 4개의 VSC로 이루어진 DC전력시스템에서 좌측 SGM 내에서 단락이 발생했을 때 주위의 Inv1, Inv2, Inv3의 캐패시터에서 방전되는 전류가 SGM1측 퓨즈에 집중되는 현상을 이용해 해당 퓨즈만을 용단시키는 방식을 보여주는 예시이다 [15]. 그리고 그림 2-23의 (b), (c), (d), (e)는 각각 SGM1, Inv1, Inv2, Inv3의 퓨즈에 흐르는 전류를 시뮬레이션을 통하여 구한 후이를 퓨즈의 용단 곡선과 그래프 상에서 비교한 것이다. 사고 지점 SGM1의 퓨즈에는 용단 곡선과 만나는 전류가 발생하여 용단이 이루어지고, 정상

VSC인 Inv1, Inv2, Inv3의 퓨즈는 용단 곡선과 전류 곡선의 교점이 없으므로 용단이 되지 않음을 알 수 있다. 이러한 방식으로 퓨즈 보호시스템의 선택성을 증명할 수는 있지만 해당 문헌에서는 퓨즈 용단 후 남은 캐패시터 전압에 대한 고려는 하고 있지 않고, 또한 사고 저항을 경험적 최소값으로만 가정한 최종 시뮬레이션 결과만 보여주고 있는 것이 한계점이다.

그림 2-23. 단락전류 시뮬레이션 및 퓨즈 용단여부 비교판별[15]

(a) DC전력시스템 내 SGM1의 단락사고시 사고전류의 흐름,

(b) SGM1측 사고전류 및 퓨즈곡선, (c) Inv1측 방전전류 및 퓨즈곡선,

(d) Inv2측 방전전류 및 퓨즈곡선, (e) Inv3측 방전전류 및 퓨즈곡선

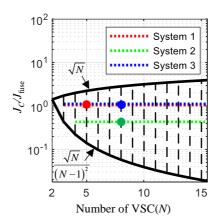

만약 위와 같은 시뮬레이션 분석을 수행하여도 만약 선택 차단이 되지 않는다면 해당 보호시스템의 수정 설계가 필요하다. 이를 위해 용단 Pt가 낮은 퓨즈를 선정하거나 더 많은 고장 전류를 발생시키도록 캐패시턴스나인덕턴스, 저항성분 등과 같은 DC 전력시스템 내 파라미터를 수정하는방법이 있을 수 있다. 하지만 시스템 정격 전압 V6의 변경은 어렵고, 선로인덕턴스 L을 줄이기 위해 기기 간 거리를 줄이는 것도 물리적인 한계가 있다. 또한 등가 저항 R을 줄이기 위해 케이블의 단면적을 증가시키면 설치 비용이크게 상승하기 때문에 결국 캐패시턴스 C를 증가시키는 것이 가장 현실적인방법이다. 이와 유사하게, 상용화된 보호시스템이나 관련 문헌에서도보호시스템의 동작을 위해 캐패시턴스가 부족한 경우 별도의 캐패시턴 뱅크를 추가하고 있다 [12], [31], [46]. 이와 같이 비용을 고려하여 적정 크기의 캐패시턴스를 확보해야 하기 때문에 최소 캐패시턴스 계산이 필요하고, 이를통해 DC 전력시스템의 경제성과 안정성을 모두 확보하는 것이 중요하다.

## 2.3.3 DC 보호시스템 상세 설계에 대한 기존의 연구

단일 R-L-C 회로에서 저항 성분이 0인 경우에는, 식 (2.21)과 같이  $J_{fuse}$ 의 용단 Pt를 가진 퓨즈를 용단시키는데 필요한 최소 캐패시턴스를 비교적용이하게 구할 수 있다 [118].

$$C > \left\{ \left( \frac{4 \cdot J_{fuse}}{\pi \cdot V_0^2} \right)^2 \cdot L \right\}^{\frac{1}{3}}$$

(2.21)

하지만 VSC 기반 DC전력시스템은 내부의 다수 캐패시터와 이들 사이의 임피던스를 포함한 복잡한 회로이기 때문에 사고 회로의 수학적 모델링은 다차원의 미분 방정식 또는 다 변수의 상태공간(multi-variable state-space) 표현식으로 나타낼 수 있다 [119]. 따라서 해석적으로 적절한 캐패시턴스 값을 구하고자 하여도, 다수의 VSC로 이루어진 DC전력시스템 다변수 특성 및 음함수(implicit function) 특성 때문에 전류 및 Pt에 대한 역함수(inverse function)를 구하기는 매우 어렵다.

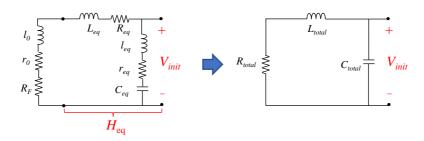

하지만 만약 복잡한 네트워크의 다변수 시스템을 단락사고 지점을 기준으로 한 등가 회로로 나타낼 수 있다면,  $R_{eq}$ ,  $L_{eq}$ ,  $C_{eq}$ 와 같은 등가 파라미터를 사용하여 단락사고 지점의 퓨즈 용단 유무를 손쉽게 판단할 수 있다. 저감쇠인 경우의 전류식 (2.12)를 바탕으로 임의의 시간 t에서의 줄적분(Joule-integral)인  $I^2t$ 를 구하면, 식 (2.22)와 같은 복잡한 식으로 나타나게 된다 [46].

과감쇠인 경우에는, 전류 식 (2.15)를 이용하여 임의의 시간 t에서의  $I^2t$  함수  $j_{Co}(t)$ 를 구할 수 있고, 식 (2.23)과 같이 나타나게 된다.

$$\begin{split} j_{C,o}(t) &= \int_0^t i_{C,o}^2(\tau) \, d\tau = \left(\frac{V_0}{L(a-b)}\right)^2 \int_0^t \left(e^{-2a\tau} + e^{-2b\tau} - 2e^{-(a+b)\tau}\right) d\tau \\ &= \left(\frac{V_0}{L(a-b)}\right)^2 \left[-\frac{1}{2a}e^{-2a\tau} - \frac{1}{2b}e^{-2b\tau} + \frac{2}{a+b}e^{-(a+b)\tau}\right]_0^t \end{split} \tag{2.23}$$

$$\vdots, \quad a &= \alpha + \sqrt{\alpha^2 - \omega_0^2}, \quad b &= \alpha - \sqrt{\alpha^2 - \omega_0^2} \end{split}$$

이와 같이 시간 t일 때의 캐패시터에서 방전되는 등가 It를 해석적으로 구할 수는 있지만, 지수함수와 삼각함수로 이루어져 있어 계산 자체가 어려운 경우가 많고, 역함수를 통해 식을 만족하는 파라미터나 시간의 해석적인 해를 구하기는 매우 어렵다. 대안적인 방법으로는 먼저, 파라미터의 다양한 조합에 대하여 미리 계산된 참조데이터를 이용하는 방식을 생각할 수 있다.

IEC 61660-1 표준에서는 배터리, 캐패시터, 정류기 등 직류 배전 설비에

흐를 수 있는 고장 전류를 그림 2-24의 표준 근사함수 기반으로 각 특성량을 용이하게 참조할 수 있는 방법(reference method)을 제시하였다. 예를 들어 캐패시터 단락전류 특성량을 계산하기 위해서는 먼저 등가회로의 R, L, C를 이용하여  $\alpha$ 와  $\omega$ 0를 계산한 후,  $\alpha$ 와  $\omega$ 0의 함수로 이루어진 첨두단락전류( $i_p$ ), 첨두도달시간( $i_p$ ), 상승시정수( $i_p$ 1) 및 감쇠시정수( $i_p$ 2)의 참조곡선을 이용하여 각각의 값을 도출해낼 수 있다. 하지만 이 표준에는  $i_p$ 2를 참조할 수 있는데이터가 제시되어 있지 않아 퓨즈 보호시스템 설계시에 활용하기가 어렵다.

그림 2-24. IEC 61660-1 고장 전류의 표준 근사함수

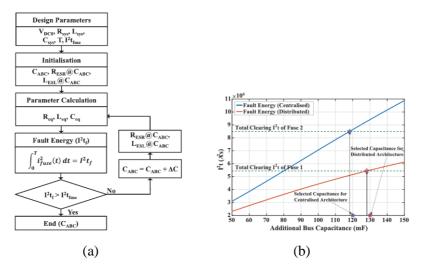

따라서 기존 연구에서는 참조법을 사용하거나 수학적으로 정확한 해를 구하기 보다는 그림 2-25(a) 및 그림 2-26과 같이 캐패시턴스 또는 다른 파라미터를 함께 점진적으로 변경하면서 고장 I't를 계산하고 퓨즈의 용단 I't와 비교하여 퓨즈 용단조건이 만족될 때까지 반복하는 방식을 제안하였다 [46], [47]. 이 같은 방식은 일반적이고 다양한 경우에 대해서 적용할 수 있지만 파라미터의 변경에 따라 어느 정도의 고장 I't 양이 변경되는지 직관적이지 않고 시뮬레이션을 포함한 계산량이 많아 일일이 컴퓨터를 이용해야 하는 단점이 있다. 또한 적절한 설계값이 나올 때까지는 컴퓨터 시뮬레이션 결과를 매 번 보고 다시 어느 정도의 스텝으로 변경할지를 판단해야 하기 때문에 전체 설계 시간이 늘어날 수도 있다.

그림 2-25. Kim이 제안한 점진적 반복법을 이용한 추가 캐패시턴스 산정 방식[46]

(a) 추가 캐패시턴스를 정하기 위한 점진적 반복 플로우 차트,

(b) 집중된 형태와 분산된 형태의 전력시스템에서 캐패시턴스 계산 결과

그림 2-26. Ravyts가 제안한 종합적인 퓨즈 기반 보호 방식 설계 순서도[47]

6 0

# 제 3장 정규화된 캐패시터 방전 I²t Map

본 장에서는 캐패시터 전압, 고장 1 단계 진행시간, 캐패시터 전류를 비 감쇠 회로의 기준 값(base value)으로 각각 정규화할 수 있음을 보인다. 이는 R-L-C 등가회로의 L, C,  $V_0$  성분이 대개 변하지 않기 때문에 상수로 취급할 수 있다는 가정에 근거하고 있다. 이를 통해, 정규화된 항을 감쇠비와 위상각에 대하여 표현한 정규화된 캐패시터 방전  $I^2t$  Map을 제시할 수 있다.

# 3.1 캐패시터 방전 특성식의 정규화

VSC기반의 DC전력시스템에서 퓨즈 보호시스템 설계를 용이하게 하기 위해서는 단락사고시 회로 파라미터(R, L, C, V<sub>0</sub>)에 따라 발생하는 I<sup>2</sup>t와 남은 캐패시터 전압 vc를 직관적으로 파악할 수 있는 방법이 필요하다. 이를 위해서는 가정을 통해 상수로 취급 가능한 파라미터로 변수의 수를 최대한 줄이고, 수식이 복잡한 부분은 정규화된 데이터를 참조표로 제공하여 기준값(Base value)만 산출하면, 정규화 및 역정규화를 통해 실제 값과 정규화된 값을 상호 변환할 수 있다.

우선 캐패시터로부터 단락전류가 공급되는 과정에서 예측이 가능하며 상수로 취급 가능한 파라미터가 있는지 살펴본다. 캐패시터 초기 전압 V6는 단락사고 직전의 전력시스템 전압이므로 기존 설계값으로 예측 및 상수로 취급이 가능하다. 등가 인덕턴스 L 또한 기기의 물리적인 크기와 정상 컨버터에서 사고지점까지의 거리가 고정되어 있으므로 예측 및 상수로 취급이 가능하다. 등가 캐패시턴스 C는 정상 컨버터에 이미 설치되어 있는 DC 링크 캐패시턴스를 의미하기 때문에 사고 중에는 변하지 않으므로 역시 예측 및 상수 취급이 가능하다. 등가 저항 R은 전력 케이블, 버스바, 캐패시터 내부 저항(ESR) 및 사고저항 R<sub>F</sub> 등으로 이루어지는데, 사고저항 R<sub>F</sub>는 기존 연구에서는 경험적인 최소 사고 저항값을 사용하였지만 사실 사고가 발생하기 전까지는 알 수 없는 값이다. 다른 저항값들은 설계된 상수 값으로 예측이 가능하지만 사고저항은 고정되지 않아 최종 등가 저항 R은 변수로 남겨두어야 한다.

위에서 살펴본 바와 같이 단일 등가 R-L-C회로에서 *L, C*와 *V*<sub>6</sub>의 값은 상수라고 둘 수 있고, 이를 근거로 퓨즈 보호시스템의 설계 대상 파라미터를 정할 수 있다. 첫 번째로 퓨즈를 용단시키기에 충분한 *Pt를* 발생시킬 수 있는 등가 저항 *R*의 범위를 파악할 수 있어야 한다. 기존 연구는 대부분 최소 저항값 또는 몇 가지 사고 저항에 대하여 시뮬레이션을 수행함으로써 보호 동작을 보여주었지만, 반대로 퓨즈 보호시스템의 동작을 보증하는 사고 저항의 범위를 제시할 수 있는 것이 보호 시스템 설계에 바람직하다. 두 번째로는 퓨즈가 용단될 때의 남은 캐패시터 전압 *vc*도 일정 이상 확보해야한다. 이는 선택 차단이 되었을 때 DC전력시스템의 전압 또는 정상 *VSC* 들의 캐패시터 전압이 일정 이상 남아있어야 순간적인 정전없이 계속 운전할 가능성이 높기 때문이다.

2.1절과 2.3절에서는 모든 파라미터에 대한 수식을 보여주었으나 위의 상수화 가정을 통해 수식을 간단히 표현할 수 있다면, 퓨즈 보호시스템 설계시 컴퓨터 시뮬레이션에 덜 의존적인 방법으로 직관적인 값을 도출하는데 도움이 될 것이다. 본 절에서는 위에서 고려한 세 가지 변수, 즉 등가 저항 R, 캐패시터 전압 νc, 캐패시터 Pt인 jc를 각각의 기준 값을 통하여 구한 정규화(per-unit화)한 변수 ζ, νcpu, jcpu로 변경하고, 수식 또한 이를 기준으로 새롭게 정리한다. 그리고 수식적으로 복잡한 부분은 정규화된 등가 저항 절반 값 ζ 과 정규화된 캐패시터 전압 νcpu에 대하여 정규화된 캐패시터 방전 Pt Map (nomalized capacitor-discharge Pt Map)을 통해 나타낼 수 있음을 보인다. 본 방식을 사용하면 서로 다른 파라미터를 가진 DC 전력시스템의 경우에도 정규화 Map을 이용하여 적절한 퓨즈 보호 시스템을 설계할 수 있다는 장점이 있다.

수식을 분석하기에 앞서, 수식을 단순화할 수 있는 대상은 정격 전압이 비교적 높고, 캐패시턴스는 크며, 선로의 길이는 짧아 단락 사고시의 캐패시터 방전 전류가 정격 전류보다 훨씬 큰 VSC 기반의 DC 전력시스템을 대상으로 한다. 가선이 수 km에 걸쳐 설치되어 있는 육지 마이크로그리드는 비교적 적합하지 않으며, 좁은 면적에 큰 VSC가 다수 설치된 선박의 경우가이에 해당한다. 해당 시스템의 등가회로에서 초기 전류  $I_0$ 는 캐패시터 방전

전류의 피크값에 비해 충분히 작아 무시할 수 있으며, 시작 시점부터 종료시까지 R, L, C 의 파라미터는 변하지 않는다고 가정한다. 그리고 단락사고 1 단계의 종료시점은 캐패시터 전압이 0에 도달하거나 지수적으로 매우 가까워질 때로 한다.

#### 1) 기준 값(Base value)의 선정

본 절에서는 저항값은 고정이지만 미지의 변수로 가정하였으므로 다양한 결과 값이 존재할 수 있다. 저항 성분의 영향을 배제하기 위해서는 저항성분이 없는 L-C 공진회로에서의 캐패시터 전압, 전류, 시간, *Pt*의 특징적인 값들을 기준 값으로 각각 선정하는 것이 필요하다.

단락사고 1 단계 내에서 캐패시터 전압은 사고 시부터 지속적으로 0까지 감소하므로 기준 값은 초기 캐패시터 값  $V_0$ 로 정할 수 있다.

$$V_{\rm CB} = V_0 \cos(0) = V_0. \tag{3.1}$$

단락사고 발생시부터 1 단계 종료시까지의 시간은 파라미터와 감쇠비에 따라 모두 달라지기 때문에 시간도 정규화하여 표현할 필요가 있다. 시간의 기준 값은 L-C 공진회로에서 캐패시터 전압이  $V_0$ 에서 0 이 될 때까지 걸리는 시간으로 정할 수 있고, 이는 공진주기( $2\pi$ )의 사 분의 일과 같다.

$$T_{\rm CB} = \frac{\pi}{2} \frac{1}{\omega_0} = \frac{\pi}{2} \sqrt{LC} \ . \tag{3.2}$$

캐패시터 전류는 1 단계 내에서 지속적으로 상승하여 1 단계 종료시에 최대값에 도달하므로 기준 값은 1단계 종료시의 최대 피크값으로 정할 수 있다.

$$I_{\rm CB} = \frac{V_0}{\omega_0 L} \sin\left(\frac{\pi}{2}\right) = V_0 \sqrt{\frac{C}{L}} . \tag{3.3}$$

캐패시터 방전 Pt의 기준 값은 위에서 정한 전류와 시간의 기준 값을 고려하여 1 단계 종료시까지 발생하는 Pt 값으로 정할 수 있다.

$$J_{\rm CB} = \int_0^{T_{\rm CB}} \left( \frac{V_0}{\omega_0 L} \sin(\omega_0 t) \right)^2 dt = \frac{\pi}{4} V_0^2 \sqrt{\frac{C^3}{L}}$$

(3.4)

## 2) 등가저항 R과 시간 t의 정규화 : 감쇠비 $\zeta$ 와 위상각 $\theta$

앞의 2.1절과 2.3절에서 소개한 캐패시터 전압, 전류, Pt 식을 위에서 소개한 기준 값을 이용하여 정규화하기 위해서는 식의 다른 항에 사용된 변수들도 정규화할 필요가 있다. 감쇠비(damping ratio) ζ는 저항성분이 포함된 공진 특성의 방정식에서 정의되고 그 값의 크기에 따라 L-C 공진회로의 전압-전류 감쇠특성을 결정하게 되는데, 그 값이 0일 때는 비 감쇠(Undamping), 0 보다 크고 1 미만일 때는 저감쇠(Underdamping), 1일 때는 임계감쇠(Criticaldamping), 1 보다 클 때는 과감쇠(Overdamping)의 특성을 가진다.

다른 관점에서 바라보면, 감쇠비는 일종의 정규화된 저항 값이라고 할 수 있다. 임피던스 기준 값  $Z_{CB}$ 는 전압의 기준 값  $V_{CB}$ 와 전류의 기준 값  $I_{CB}$ 를 이용하여 식 (3.5)와 같이 표현할 수 있는데, 감쇠비는 식 (3.6)과 같이 등가저항 R을  $Z_0$ 로 정규화한 저항의 절반값임을 알 수 있다. 그리고 참고로  $Z_{CB}$ 는 LC공진회로의 특성 임피던스(Characteristic Impedance)  $Z_0$ 의 정의와 같음을 알 수 있다.

$$Z_{\rm CB} = \frac{V_{\rm CB}}{I_{\rm CB}} = Z_0 = \sqrt{\frac{L}{C}}$$

(3.5)

$$\zeta = \frac{R}{2} \sqrt{\frac{C}{L}} = \frac{1}{2} \cdot \frac{R}{Z_{CP}}.$$

(3.6)

감쇠비  $\zeta$ 를 이용하면, 기존의 감쇠 상수  $\alpha$ 와, 감쇠 고유주파수  $\omega$ <sup> $\alpha$ </sup> 및  $\beta$ 를 식 (3.7)과 같이  $\zeta$ 와  $\omega$ <sup> $\alpha$ </sup>의 변수로 나타낼 수 있다.

$$\alpha = \frac{R}{2L} = \zeta \omega_0$$

$$\omega_d = \sqrt{\omega_0^2 - \alpha^2} = \sqrt{1 - \zeta^2} \omega_0 \qquad (3.7)$$

$$\beta = \arctan\left(\frac{\omega_d}{\alpha}\right) = \arctan\left(\frac{\sqrt{1-\zeta^2}}{\zeta}\right)$$

한편, 단락사고 후 진행시간 t는 L-C 공진회로의 공진주기로 나누어 정규화를 할 수 있으며, 이렇게 정규화된 시간 t는 식 (3.8)과 같이 위상각  $\theta$ 의 정의와 같음을 알 수 있다.

$$\theta = \omega_0 t = \frac{t}{\sqrt{LC}} \,. \tag{3.8}$$

## 3) 전 감쇠비 영역에서의 전압, 시간, 전류, Pt의 정규화

앞에서 살펴보았지만 캐패시터의 전압, 1단계 종료시간, 캐패시터의 전류 및 Pt 수식은 감쇠비에 따라 모두 다른 수식으로 표현된다. 그러나 위에서 살펴본 기준 항은 모든 감쇠비에 대하여 일반적으로 적용할 수 있으므로, 기존에 R과 t의 함수로 나타났던 항들은 정규화된 변수인  $\zeta$  및  $\theta$ 로 통일하여 표현할 수 있다. 여기서는 감쇠비의 범위에 따라 비 감쇠(n), 부족감쇠(u), 임계감쇠(c)와 과감쇠(o)인 경우에 대하여 수식을 정리한다.

#### (i) 비 감쇠인 경우 ( $\zeta = 0$ )

비 감쇠인 경우의 특징적인 값은 기준 값을 선정할 때 활용하였으나, 시간 t에 대한 캐패시터 전압, 전류, Pt의 식을  $\zeta$  및  $\theta$ 에 대해서 정리할 수 있다. 우선, 주파수 영역에서의 캐패시터 전압 방정식은 식 (3.9)와 같다. 아래 첨자 n은 비 감쇠인 경우를 뜻한다.

$$v_{\rm C,n}(s) = V_0 \frac{s}{s^2 + \omega_0^2}.$$

(3.9)

식 (3.9)를 라플라스 역변환하면 식 (3.10)과 같고 기준 값인  $V_{CB}$ 와 그 외

정규화된 항의 곱으로 나타낼 수 있다. 아래 첨자는, 정규화는 물리적인 단위를 per-unit화 한다는 뜻에서 pu를 사용하였다.

$$v_{C,n}(t) = V_0 \cdot \cos(\omega_0 t) = \{V_0\} \cdot \{\cos(\theta)\}$$

$$= V_{CB} \cdot \{\cos(\theta)\} = V_{CB} \cdot v_{Cpu,n}(0,\theta)$$

(3.10)

식 (3.10)은 주기 함수의 형태를 가지고 있으나, 1 단계 내의 시간 및 위상각범위 내에서만 정의되고 뒤에서 구할 전류식과 Pt식 또한 같은 정의역을 가진다. 정의역의 최대값인 비 감쇠시 1 단계 종료시간  $T_{\rm Cn}$ 은 식 (3.10)의 캐패시터 전압이 0이 되는 시간이므로 식 (3.11)과 같이 구할 수 있고, 이 역시 기준값과 정규화된 항의 곱 형태로 나타낼 수 있다. 종료 시각은 t 자체의범위를 나타내기 때문에 다른 정규화 함수와 달리  $\zeta$ 에 대한 일변수 함수이다.

$$T_{C,n} = \frac{\pi}{2} \frac{1}{\omega_0} = \left\{ \frac{\pi}{2} \sqrt{LC} \right\} \cdot \{1\}$$

$$= T_{CB} \cdot \{1\} = T_{CB} \cdot T_{Cpu,n} (0)$$

(3.11)

한편 캐패시터 방전 전류는 캐패시터 전압의 미분과 같으므로 식 (3.12)와 같이 구할 수 있고, 위 전류식을 이용하여 단락사고 이후부터 시간 t동안의 캐패시터 방전에 의한 Pt를 구하면 다음 식 (3.13)과 같이 나타낼 수 있다. 두 경우 또한 기준 값과 정규화된 항의 곱으로 나타낼 수 있다.

$$i_{C,n}(t) = -C \frac{dv_{C,n}(t)}{dt} = \frac{V_0}{L\omega_0} \sin(\omega_0 t) = \left\{ \frac{V_0}{L\omega_0} \right\} \cdot \left\{ \sin(\theta) \right\}$$

$$= I_{CB} \cdot \left\{ \sin(\theta) \right\} = I_{CB} \cdot i_{Cpu,n}(0,\theta)$$

(3.12)

$$j_{C,n}(t) = \int_0^t i_{C,n}^2(\tau) d\tau = \left\{ \frac{\pi}{4} V_0^2 \sqrt{\frac{C^3}{L}} \right\} \cdot \left\{ \frac{1}{\pi} \left( 2\theta - \sin(2\theta) \right) \right\}$$

$$= J_{CB} \cdot \left\{ \frac{1}{\pi} \left( 2\theta - \sin(2\theta) \right) \right\} = J_{CB} \cdot j_{Cpu,n}(0,\theta)$$

(3.13)

# (ii) 부족 감쇠인 경우(0 < ζ < 1)

앞의 2.1절에서 이미 부족감쇠인 경우에 대한 수식이 소개되어 있지만 여기에서는 추가로 ζ및 θ에 대해서 표현하면 아래와 같다. 초기 전류에 해당되는 성분을 무시한 주파수 영역에서의 캐패시터 전압 식은 아래 식(3.14)와 같다. 아래 첨자는 부족감쇠의 의미로 u를 사용한다.

$$v_{\text{C,u}}(s) = \frac{V_0(s+2\alpha)}{(s+\alpha)^2 + \omega_d^2}$$

(3.14)

라플라스 역변환을 통하여 식 (3.14)는 식 (3.15)와 같이 시간 t에 대한 식으로 나타낼 수 있으며, 추가로  $\zeta$  및  $\theta$ 에 대해서도 나타낼 수 있다.

$$v_{C,u}(t) = V_0 \cdot \frac{\omega_0}{\omega_d} \cdot e^{-\alpha t} \sin\left(\omega_d t + \beta\right)$$

$$= \{V_0\} \cdot \left\{ \frac{e^{-\zeta \theta}}{\sqrt{1-\zeta^2}} \sin\left(\sqrt{1-\zeta^2}\theta + \arctan\left(\frac{\sqrt{1-\zeta^2}}{\zeta}\right)\right) \right\}. \tag{3.15}$$

$$= V_{CB} \cdot v_{Cpu,u}(\zeta, \theta)$$

감쇠비가  $\zeta$ 일 때 캐패시터 전압이 0이 되는 시간  $T_{C,u}$ 는 식 (3.15)를 이용하여 식 (3.16)과 같이  $\zeta$ 의 함수로 나타낼 수 있다. 여기에서도 마찬가지로  $0 \le t \le T_{C,u}(\zeta)$  시간 범위 내에서 전압, 전류,  $I^2t$ 의 함수 및 역함수가 존재한다.

$$T_{\text{C,u}}(\zeta) = \left\{ \frac{\pi}{2} \sqrt{LC} \right\} \cdot \left\{ \frac{2}{\pi} \frac{1}{\sqrt{1-\zeta^2}} \left( \pi - \arctan\left(\frac{\sqrt{1-\zeta^2}}{\zeta}\right) \right) \right\}.$$