#### 저작자표시-비영리-변경금지 2.0 대한민국

#### 이용자는 아래의 조건을 따르는 경우에 한하여 자유롭게

• 이 저작물을 복제, 배포, 전송, 전시, 공연 및 방송할 수 있습니다.

#### 다음과 같은 조건을 따라야 합니다:

저작자표시. 귀하는 원저작자를 표시하여야 합니다.

비영리. 귀하는 이 저작물을 영리 목적으로 이용할 수 없습니다.

변경금지. 귀하는 이 저작물을 개작, 변형 또는 가공할 수 없습니다.

- 귀하는, 이 저작물의 재이용이나 배포의 경우, 이 저작물에 적용된 이용허락조건 을 명확하게 나타내어야 합니다.

- 저작권자로부터 별도의 허가를 받으면 이러한 조건들은 적용되지 않습니다.

저작권법에 따른 이용자의 권리는 위의 내용에 의하여 영향을 받지 않습니다.

이것은 이용허락규약(Legal Code)을 이해하기 쉽게 요약한 것입니다.

Disclaimer 🖃

### 공학석사 학위논문

# Effects of capacitance on electroforming-free HfO<sub>2</sub> RRAM based one-selector-one-resistor (1S1R) device

2023년 2월

서울대학교 대학원 재료공학부 재료공학전공 이 선 우

# Effects of capacitance on electroforming-free HfO<sub>2</sub> RRAM based one-selector-one-resistor (1S1R) device

지도 교수 황철성

이 논문을 공학석사 학위논문으로 제출함 2023년 1월

> 서울대학교 대학원 재료공학부 재료공학전공 이 선 우

이선우의 공학석사 학위논문을 인준함 2023년 1월

| 위  | 원 장 | 장 혜 진 | <u>(인)</u>     |

|----|-----|-------|----------------|

|    |     |       | ( . <b>3</b> ) |

| 무위 | 원장  | 황 철 성 | (인)            |

| 위  | 원   | 박 민 혁 | (인)            |

저항변화메모리(RRAM, Resistive Random Access Memory)는 공정 미세화(scaling) 한계에 도달할 것으로 예상되는 기존 메모리를 대체할 차세대 메모리로 주목받고 있다. 특히 RRAM이 아날로그 시냅스로서 크로스바 어레이(CBA, crossbar array) 구조에 쓰일 경우, 병목현상이 없고 적은 전력으로 더 많은 데이터를 처리하는 뉴로모픽 컴퓨팅 등에 응용할 수 있다. 그러나 RRAM의 상용화에는 포밍(electroforming) 과정으로 인한 산포 및 소자 항복 문제. CBA에서의 누설 전류(sneak current) 문제와 같은 제약이 있다. 이에 본 연구에서는 electroforming-free RRAM과 선택소자 운용을 통해 이러한 한계점을 보완하고자 하였다. HfO2 기반 forming-free RRAM과 TiO<sub>2</sub> 기반 비선형 선택소자(nonlinear selector)를 제작 및 통합하였으며 전기적 거동을 관찰하였다.

한편 뉴로모픽 컴퓨팅에 응용하기 위해서는 RRAM이 이상적인 아날로그 스위칭 거동을 보이는 것이 바람직하지만, 외부 전선으로 연결한 one-selector-one-resistor(1S1R) 소자는 아날로그 거동에서 윈도우 감소(dynamic range degradation)가 두드러지는 현상이 나타났다. 본 연구에서는 이러한 현상의 주된 원인이 증가한 기생용량(parasitic capacitance)이라고 보고, 적층한 1S1R의 병렬커패시턴스를 조절하여 이것이 소자의 아날로그 특성에 미치는 영향을실험적으로 증명하였으며 회로 모델을 통해 그 원인에 대해 고찰하였다.이를 통해 1S1R 제작 시 외부 케이블 연결이 아닌 통합된 형태로 적층공정하여 parasitic capacitance를 줄이는 것이 필수적임을 시사하였다.

주요어: 저항변화메모리 (Resistive Switching Memory), 포밍프리 (Electroforming-free), 선택소자 (Nonlinear Selector), 커패시턴스 (Capacitance), 아날로그 스위칭 (Analog Switching), 비이상성 (Nonideal Effects)

학 번:2021-27239

# 목차

|     | 록                             |       |

|-----|-------------------------------|-------|

| 목기  | ₹}                            | · iii |

| 丑   | 목차                            | · iv  |

| ユ゙゙ | 림 목차                          | · iv  |

| 1.  | 서론                            | 1     |

| 2.  | 문헌 연구                         | 6     |

|     | 2.1. Electroforming-free RRAM | 6     |

|     | 2.2. 선택소자(Nonlinear Selector) | 10    |

|     | 2.3. RRAM의 아날로그 스위칭           | 14    |

| 3.  | 포밍 프리 RRAM 제작 및 선택소자와의 통합     | . 17  |

|     | 3.1. 실험 목적 및 설계               | 17    |

|     | 3.2. 실험 결과 및 고찰               |       |

| 4.  | 커패시턴스가 아날로그 소자에 미치는 영향        | . 28  |

|     | 4.1. 실험 목적 및 설계               | 28    |

|     | 4.2. 실험 결과 및 고찰               |       |

| 5.  | 결론                            | 45    |

| 참.  | 고문헌                           | 47    |

| At  | ostract                       | 51    |

# 표 목차

| Table 2.2.1 선택소자 종류별 장단점                | 13 |

|-----------------------------------------|----|

| Table 3.1.1 PEALD 공정 조건 및 시퀀스           | 20 |

| Table 3.1.2 Reactive sputter 공정 조건      | 20 |

| Table 3.1.3 Thermal ALD 공정 조건 및 시퀀스     | 21 |

| Table 3.1.4 PR, PEB, Maskless dose 조건에  | 따른 |

| liftoff 결과                              | 22 |

| Table 3.2.1 샘플별 XRF 결과와 계산된 oxide의      | 두꺼 |

|                                         | 26 |

| Table 4.2.1 Exponential fitting에서의 파라미터 | 42 |

# 그림 목차

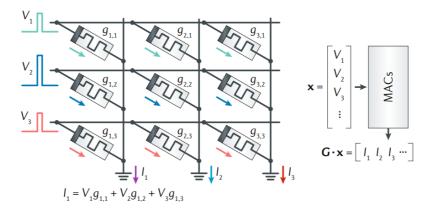

| Figure 1.1 CBA에서 물리적으로 벡터-행렬            | 곱을   |

|-----------------------------------------|------|

| 연산하는 방법[12]                             | 4    |

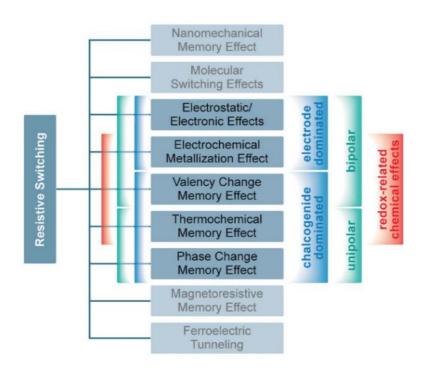

| Figure 1.2 비휘발성 메모리로 응용 가능한 저항          | 변화   |

| 효과의 분류[3]                               | 4    |

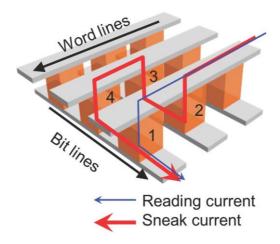

| Figure 1.3 CBA 구조에서 나타나는 sneak cur      | rent |

| 문제[13]                                  | 5    |

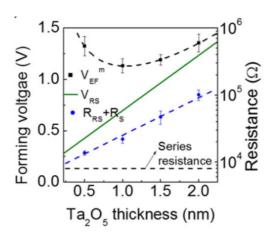

| Figure 2.1.1 Oxide 두께에 따른 forming 전압[4] | 8    |

| Figure 2.1.2 Oxide 두께에 따라 SET, RESET 거  | 동이   |

| 다른 원리 모식도[14]                           | 8    |

| Figure 2.1.3 하부 전극에 따른 산소 공공의           | 분포   |

| 그림[5]9                                        |

|-----------------------------------------------|

| Figure 2.2.1 2D CBA에서 sneak path의 저항 구하는      |

| 과정[13]12                                      |

| Figure 2.2.2 Reading scheme에 따른 sneak path    |

| 문제[13]12                                      |

| Figure 2.3.1 RRAM의 아날로그 특성에서의 신뢰성             |

| 지표[26]16                                      |

| Figure 2.3.2 Pulse 조건 최적화의 중요성[31] 16         |

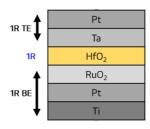

| Figure 3.1.1 Electroforming-free RRAM 소자의     |

| 모식도20                                         |

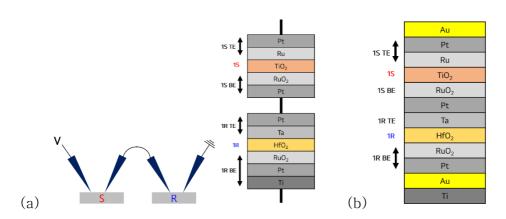

| Figure 3.1.2 1S1R 소자의 모식도21                   |

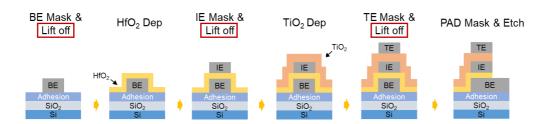

| Figure 3.1.3 1S1R 적층 소자 공정 단계21               |

| Figure 3.1.4 조건에 따른 liftoff 결과 예시22           |

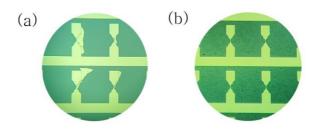

| Figure 3.2.1 제작한 소자의 top view 사진25            |

| Figure 3.2.2 Oxide 두께별 RRAM의 I-V curve 25     |

| Figure 3.2.3 제작한 RRAM 소자의 온도별 retention       |

| 결과26                                          |

| Figure 3.2.4 제작한 selector 소자의 I-V curve 27    |

| Figure 3.2.5 제작한 1S1R 소자의 I-V curve 27        |

| Figure 4.1.1 소자의 아날로그 특성 측정 회로도 30            |

| Figure 4.1.2 Pulse 조건 최적화 과정 순서도 30           |

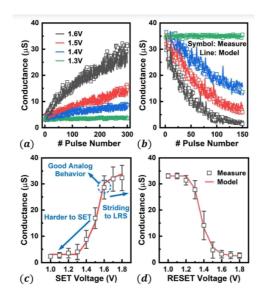

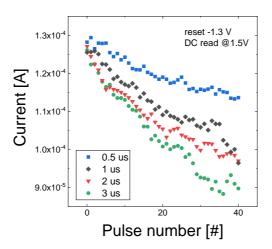

| Figure 4.2.1 Pulse width에 따른 depression 거동 변화 |

|                                               |

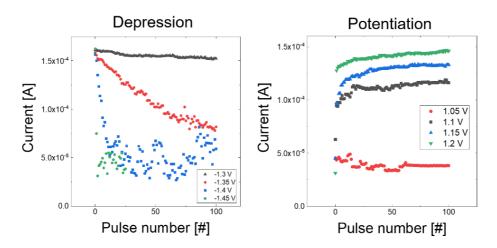

| Figure 4.2.2 Pulse height에 따른 depression,     |

| potentiation 거동 변화 38                         |

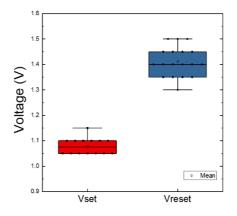

| Figure 4.2.3 최적의 SET, RESET pulse height 분포            |

|--------------------------------------------------------|

|                                                        |

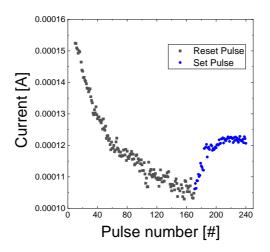

| Figure 4.2.4 외부 케이블로 연결한 1S1R 소자의                      |

| 아날로그 스위칭 특성39                                          |

| Figure 4.2.5 Interfacial layer 생성이 RRAM의               |

| 스위칭을 방해하는 원리 모식도40                                     |

| Figure 4.2.6 추가 capacitance에 따른 아날로그 스위칭               |

| 변화(한 개 샘플)40                                           |

| Figure 4.2.7 추가 capacitance에 따른 아날로그 특성                |

| 지표 변화(측정 샘플들 평균)41                                     |

| Figure 4.2.8 추가 capacitance별 아날로그 스위칭                  |

| 그래프의 exponential fitting41                             |

| Figure 4.2.9 Ch1, Ch2, DUT에 걸리는 시간에 따른                 |

| 전압42                                                   |

| Figure 4.2.10 간소화된 등가 회로 모델(고정된 DUT                    |

| 저항)43                                                  |

| Figure 4.2.11 모델에서 계산된 capacitance에 따른                 |

| DUT 전압(V <sub>1</sub> ), Ch2 전압(V <sub>2</sub> )의 개형43 |

| Figure 4.2.12 모델에서 계산된 DUT 저항에 따른 DUT                  |

| 전압(V <sub>1</sub> )                                    |

## 1. 서론

저항변화메모리(RRAM, Resistive Random Access Memory)는 빠른 동작 속도, 저전압 구동 등의 장점을 가지며 scaling 한계에도달할 것으로 예상되는 기존 메모리를 대체할 차세대 메모리로주목받고 있다.[1] 특히 RRAM은 아날로그 시냅스로서 crossbar array(CBA) 구조에 쓰일 경우, 전력 소모가 심한 vector—matrix multiplication을 Figure 1.1와 같이 물리적으로 계산함으로써 효율적인연산을 가능케 하는 뉴로모픽 컴퓨팅에 응용할 수 있다. 그러나 reliability 문제, 셀 간 혹은 사이클 간 variation 문제, 불안정한 multi—bit 동작과 같이 개선해야 할 부분들이 많다.

RRAM은 절연체의 상태를 변화시켜 높은 저항 상태(HRS, High Resistance State) 혹은 낮은 저항 상태(LRS, Low Resistance State)를 가지게 함으로써 정보 저장이 가능하다. Figure 1.2와 같이다양한 메커니즘을 통해 저항 변화가 가능한데, 그 중에서 산화환원반응 관련 RRAM의 경우 스위칭 메커니즘은 전류가 통하는 길인 conduction filament의 성장과 끊어짐으로 설명할 수 있다.[2,3] Oxygen vacancy의 이동을 이용하는 경우, SET 과정에서는 전압을인가했을 때 oxide 내부에서 oxygen vacancy가 증가하면 transition metal cation의 valence state를 바꾸어 LRS가 되고, RESET과정에서는 반대 방향의 전압 인가 시 filament가 끊어짐으로써 HRS가된다.

RRAM의 pristine 상태에서 conducting filament를 처음으로 생성하기 위해 electroforming 과정을 필요로 한다. 그러나 electroforming 과정은 여러가지 문제점을 유발한다. 우선 이 과정이 atomic scale로 일어나기 때문에 cell마다 conduction path의 모양, 위치 등이 차이가 날 수 있고 cycle to cycle, device to device uniformity를 저하시킨다. 또한 electroforming의 순간에 overshooting 및 oscillation 현상이 발생하거나 over-forming이 일어나기도 하는데, 이는 device failure로 이어질 수 있다. 또한 보통 첫 forming시에 일반적인 set voltage보다 큰 voltage가 필요한데, 이 또한 함께 적층한 선택소자의 breakdown 등의 device failure로 이어질 수 있다. 이를 극복하기 위해 electroforming 과정이 필요 없는 electroforming-free RRAM에 대한 연구가 진행되어 왔다.[4-7]

한편 RRAM CBA의 상용화를 방해하는 몇 가지 요인들이 있는데, 그 중 sneak current는 Figure 1.3에서처럼 unselected cell들로 원치 않는 전류가 흘러 read, write operation을 방해하는 것을 말한다. 따라서 고집적 cell array를 위해서는 sneak current를 줄이는 것이 필요한데, 많은 연구자들이 트랜지스터, 다이오드, nonlinear selector와 같은 다양한 selection device를 제안하였다.[8] 그 중 nonlinear selector을 사용한 1S1R(one-selector-one-resistor) 구조는 cell size, 공정 온도, bipolar 동작 가능 등의 장점이 있어 bipolar RRAM을 응용하기에 적절하다.[9] 한편 RRAM과 selector을 함께 사용하면 electroforming 시 cell 간 산포가 커지거나 소자의 breakdown이 일어날 위험이 있는데, forming-free RRAM을 운용하면 보완이 가능할 것이다.

또한 실제 CBA에서 parasitic element는 무시할 수 없는 요소이다. Parasitic capacitance나 저항 같은 경우는 cable, probe, 전극, 커넥터, PCB 기판 등 다양한 곳에서 유발된다.[10] Parasitic capacitance는

forming 시 conduction filament의 stochasticity를 증가시키기도 하고, 스위칭 시의 current overshoot, RC delay로 인한 동작 방해 등을 유발한다고 알려져 있다. Parasitic resistance는 IR drop을 일으켜 cell에 원하는 수준의 전압을 가하기 위해 더 큰 전압 인가를 필요로하게 하는 등 문제를 일으킨다.[11] 뉴럴 네트워크 등에 응용하기위해서는 RRAM이 이상적인 아날로그 거동을 보이는 것이 바람직하며, 이는 linearity, symmetry, dynamic range degradation 등의 지표로나타낼 수 있다. 따라서 이러한 parasitic element가 실제에서 소자의아날로그 특성이나 회로에 어떤 다양한 영향을 미치는지, 어떤 식으로 제어해야 할지 아는 것이 중요하다.

본 연구에서는 HfO<sub>2</sub> 기반 electroforming-free RRAM과 TiO<sub>2</sub> 기반 선택소자 운용을 통해 RRAM의 한계점을 보완하고 CBA로의 응용가능성을 높이고자 하였다. 한편 1S1R 소자의 아날로그 거동에서 dynamic range degradation이 두드러지는 주된 원인이 parasitic capacitance라고 보고, 적층한 1S1R의 병렬 커패시턴스를 조절하여 커패시턴스가 1S1R 소자의 아날로그 특성에 미치는 영향을 알아보았다. 또한 회로 모델을 통해 이를 설명할 수 있는 논리적인 방법을 제안하고자 하였다.

Figure 1.1. CBA에서 물리적으로 벡터-행렬 곱을 연산하는 방법.[12]

Figure 1.2. 비휘발성 메모리로 응용 가능한 저항 변화 효과의 분류.[3]

Figure 1.3. CBA 구조에서 나타나는 sneak current 문제.[13]

### 2. 문헌 연구

#### 2.1. Electroforming—free RRAM

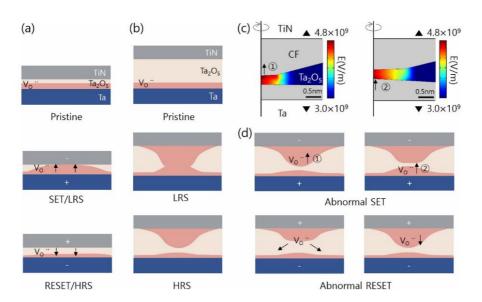

RRAM 소자가 electroforming-free 거동을 가지기 위해서는 oxide를 critical thickness 이하로 만드는 것이 중요하다.[5] 큰 forming voltage로 인해 과도한 forming 거동이 나타날 경우 좋지 않은 특성으로 이어지는데, Figure 2.1.1와 같이 forming voltage는 film 두께에 비례하므로, 두께를 줄임으로써 forming voltage를 낮추어 더욱 uniform한 특성을 기대할 수 있다. 이와 더불어, oxide film이 두꺼우면 hour-glass 모양 conducting filament가 형성될 수 있다. 선행연구에 따르면 oxide 내부에서 conducting filament의 상부, 하부가 자라는 속도에 따라 SET, RESET이 결정되는데, Figure 2.1.2에서와 같이 보다 뾰족한 부분에 전계가 집중됨에 따라 원하는 거동과 반대로 자라면 'inversion(= negative SET)'이 발생한다. 이 결과 endurance가 급감하고 HRS 저항의 variation이 커지는 문제가 발생하며 결국에 SET stuck 되었다.[14]

따라서 더 나은 property를 위해서는 두께를 낮춰 forming voltage를 낮추고 hour-glass 모양을 피하는 것이 좋을 것으로 보인다. 그러나 하부전극을 RuO2가 아닌 TiN을 쓸 경우, oxide film이 얇더라도 switch cycle을 반복하면서 상부에 oxygen vacancy 농도가 높아질 가능성이 계속 존재할뿐더러 critical thickness에 도달하기 전에 전류가 새서 switching 자체가 일어나지 못하는 문제가 발생한다는 연구가

#### 존재한다(Figure 2.1.3).[5]

따라서 전극의 특성 또한 forming-free 거동 여부에 중요하다. 동일 연구에 따르면 Ta/HfO<sub>2</sub>/TiN RRAM cell은 switch cycle이 반복될수록 oxygen vacancy가 쌓여서 failure가 발생했는데, 전극물질인 TiN과 Ta 모두 HfO<sub>2</sub>에서 산소를 빼앗는 역할을 하여 누설전류가 높고, switching cycle이 반복될수록 oxygen vacancy가 계면에 축적되고 hour-glass 모양의 filament가 형성되었기 때문이다. 반면 TiN 대신 RuO<sub>2</sub> 전극을 이용하면 oxygen vacancy를 빼앗는 효과 덕분에 switching을 반복해도 계면에 oxygen vacancy가 쌓이지 않음이 관찰되었다. 따라서 conical한 filament 모양을 가질 수 있었고, 이에 endurance가 크게 증가하였으며 retention 특성도 좋아졌다. 그러나 앞서 언급했듯 RuO<sub>2</sub>를 사용하더라도 oxide의 두께가 두꺼우면 electroforming 과정 자체가 residual filament를 남겨서 switching nonuniformity가 발생되므로, 두께 감소를 통한 electroforming-free 거동이 필요하다.

Figure 2.1.1. Oxide 두께에 따른 forming 전압.[4]

Figure 2.1.2. Oxide 두께에 따라 SET, RESET 거동이 다른 원리모식도. (a) 얇은 oxide, (b) 두꺼운 oxide에서의 Pristine, LRS, HRS. (c) COMSOL로 계산된 전기장 분포. (d) 두꺼운 oxide에서 abnormal SET, RESET의 원리.[14]

Figure 2.1.3. 하부 전극에 따른 산소 공공의 분포 그림. 하부 전극으로 (a) TiN을 사용한 경우 (oxide 4.5 nm), (b), (c) RuO2를 사용한 경우 (oxide 각각 4.5, 3.0 nm).[5]

#### 2.2. 선택소자(Nonlinear Selector)

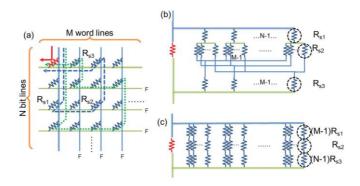

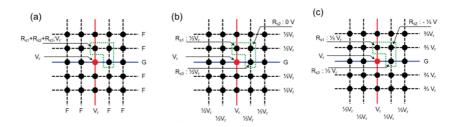

CBA가 커질수록 sneak current의 영향이 증가하는데, 가령 'off-state'에 있는 selected cell을 읽는 동작이나 쓰기 동작에서의 원치 않는 방해 및 전력 손실을 유발한다. Figure 2.2.1에 나타난 것과 같이 sneak path의 저항을 따라 전류 누설이 발생하며, 실제 회로에서는 선저항으로 인해 문제가 더욱 심각해진다. 한편 Figure 2.2.2와 같이데이터를 읽기 위해 다양한 voltage scheme에 가능한데, selected cell에 원하는 전압(V<sub>r</sub>)이 인가될 때 unselected cell들에 인가되는 전압에 따라 분류할 수 있다. Figure 2.2.2.(a)의 V<sub>r</sub> scheme에서는 selected cell에 인접한, 초록색 박스로 표시된 경로에 그대로 V<sub>r</sub>이 걸리며, Figure 2.2.2.(c)의 1/3V<sub>r</sub> scheme과 같이 unselected node에 걸리는 최대 전압이 1/3V<sub>r</sub>이 되도록 만들 수도 있다. Voltage scheme에 따라서 selected cell 전압과 sneak path의 전압의 polarity 관계가다르고, 사용해야 하는 선택소자의 종류도 달라진다.[13]

그동안 선택소자로 트랜지스터(1T1R 구조)나 다이오드(1D1R 구조)가 많이 사용되었다. 그러나 트랜지스터는 3-terminal 소자로서 cell size를 줄이는 데 한계가 있으며, 공정 온도가 높다는 단점이 있다. 일방향 다이오드의 경우 unipolar RRAM에만 사용 가능한데, 보통 bipolar RRAM이 안정적인 거동을 보인다고 알려져 있기 때문에 적합하지 않다. 이에 본 연구에서는 각 crosspoint에 RRAM 부분과 직렬로 integration 되어 있는 nonlinear selector을 사용하였다. 각 구조의 장단점을 Table 2.2.1에 나타내었다.[9]

Nonlinear selector에 요구되는 특성들이 있다. 동작이 가능하도록 충분한 on-current가 흘러야 하고, unselected cell에서의 전류는 막아야 하므로 off-current는 작을수록 좋다. 즉, 이것의 비인 선택소자의 nonlinearity가 충분히 커야 한다. 또한 양방향 동작이 가능해야 하고 동작 전압이 RRAM 소자와 잘 맞아야 한다. Scalability, switching speed, endurance, manufacturability 등의 항목은 RRAM의 특성을 최대한 방해하지 않아야 한다. 최대한 이 조건들을 유념하여 선택소자를 설계해야 한다.[8]

한편 유전물질에서 conduction mechanism은 크게 둘로 나뉘는데, 우선 'electrode-limited' 메커니즘은 전극과 유전물질의 컨택의특성에 좌우되며 barrier height와 interface가 중요한 요소이다. 'Bulk-limited' 메커니즘의 경우 유전 물질 자체의 특성에 좌우되고 trap energy level이 중요하다.[15] 연구된 nonlinear selector 중에서 bulk-limited conduction mechanism을 보인 선택소자에는 Pt/TiO<sub>2</sub>(8 nm)/TiN[16], Ta<sub>2</sub>O<sub>5</sub>/TaO<sub>x</sub>/TiO<sub>2</sub> multilayer tunnel barrier[17] 등이 있으며, electrode-limited conduction을 주로 보인 선택소자로는 Pt/TiO<sub>2</sub>(4 nm)/TiN[18], Ni/TiO<sub>2</sub>/Ni[9] 등이 연구된 바 있다. Pd/TaO<sub>x</sub>/Ta/Pd[19], Ru/TaO<sub>x</sub>/W[20] 선택소자에서는 Schottky emission과 tunneling이 모두 나타났으며, TaN<sub>1+x</sub>/Ta<sub>2</sub>O<sub>5</sub>/TaN<sub>1+x</sub> trilayer tunnel barrier[21], TiN/Ta<sub>2</sub>O<sub>5</sub>/TiN[22], Pt/TaO<sub>x</sub>/TiO<sub>2</sub>/TaO<sub>x</sub>/Pt[23] 선택소자들은 tunneling conduction mechanism만 보였다.

Figure 2.2.1. 2D CBA에서 sneak path의 저항 구하는 과정. (a) 2D CBA에서의 회로도; 읽기 전류(빨간색), 가능한 sneak path(파란색), 불가능한 sneak path(초록색). (b) 중간 단계의 회로도 변형. (c) 최종 회로도 변형(sneak path 저항 표시).[13]

Figure 2.2.2. Reading scheme에 따른 sneak path 문제. (a) Floating scheme ( $V_r$  scheme). (b)  $1/2V_r$  scheme. (c)  $1/3V_r$  scheme.[13]

| Cell<br>Structure | Cell Size         | Selection<br>Device | Process<br>Temp. | Bipolar R |

|-------------------|-------------------|---------------------|------------------|-----------|

| 1R                | $4F^2$            | No                  | Low              | Yes       |

| 1T1R              | > 6F <sup>2</sup> | Yes                 | High             | Yes       |

| 1D1R              | $4F^2$            | Yes                 | Low              | No        |

| 1S1R              | $4\mathrm{F}^2$   | Yes                 | Low              | Yes       |

Table 2.2.1. 선택소자 종류별 장단점.

#### 2.3. RRAM의 아날로그 스위칭

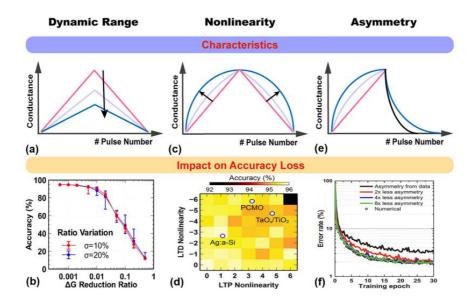

뉴로모픽 컴퓨팅에서 정보 저장과 인풋 시그널 처리를 위해 RRAM의 conductance가 synaptic weight를 잘 모사해야 한다. 또한 얼굴 인식, 강화학습 같은 많은 task들이 아날로그 특성을 가진 RRAM array로 수행된 바 있다.[24,25] 하지만 array의 크기를 키우고 현실적으로 사용하는 것은 어려운데, 그 이유는 소자의 아날로그 특성이 보이는 nonlinearity, asymmetry, dynamic range degradation, variation 등의 문제가 학습 과정 및 이후 추론 과정에서 accuracy degradation을 일으키기 때문이다.[26] 이는 Figure 2.3.1에 잘 나타나 있다. 우선 dynamic range 문제(Figure 2.3.1.(a))는 소자의 원래 LRS. HRS window를 제대로 사용할 수 없는 것이고, nonlinearity 문제(Figure 2.3.1.(c))는 같은 pulse를 가하였을 때 conductance 변화율이 달라지는 것이며, asymmetry 문제(Figure 2.3.1.(e))는 potentiation과 depression에서 pulse number에 따른 아날로그 특성 개형이 다른 것을 말한다. 이러한 문제들을 개선하기 위해 electrothermal modulation layer(ETML)을 삽입하거나[27], defect engineering을 시도하거나[28,29], programming scheme을 조정하는 방식[30]들이 연구되었다.

한편 pulse width, pulse height와 같은 펄스 조건 또한 이러한 지표들에 중요한 영향을 미칠 수 있다. Figure 2.3.2에서와 같이, 가령 programming 전압이 너무 낮으면 state가 변화하기 어렵고, asymmetric하고 작은 dynamic range를 유발하게 된다. 반대로 programming 전압이 너무 높으면 저항 state가 pulse 한 번으로 지나치게 튀어 버려 심한 nonlinearity가 발생할 수 있기에, 적절한

조건을 찾는 것이 중요하다.

Figure 2.3.1. RRAM의 아날로그 특성에서의 신뢰성 지표. (a) Dynamic range, (c) nonlinearity, (e) asymmetry. (b), (d), (f)는 각각 (a), (c), (e)로 인한 accuracy loss.[26]

Figure 2.3.2. Pulse 조건 최적화의 중요성. (a), (c) SET pulse, (b), (d) RESET pulse 전압 크기에 따른 아날로그 스위칭 변화.[31]

## 3. 포밍 프리 RRAM 제작 및 선택소자와의 통합

#### 3.1. 실험 목적 및 설계

Electroforming-free RRAM을 제작하기 위해 선행 연구[5]에 기반하여 Figure 3.1.1에 나타낸 구조와 같이 HfO2를 resistive switching 물질로 사용하였고 Ta를 상부전극(TE)으로, RuO2를 하부전극(BE)으로 이용하였다. 소자 제작 공정은 선행 연구와 같은 방식을 따랐다. P형 실리콘 기판 위에 열 산화 공정으로 약 100 nm의 SiO<sub>2</sub> 층을 생성하고, SSO3A9 감광제(PR, photoresist) 도포 후 서울대학교 반도체공동연구소(ISRC)의 maskless photolithography 장비 (NanoSystem Solutions, Inc, DL-1000 HP)를 이용하여 패턴을 형성하고 하부 전극을 증착한 후 아세톤 및 ST-2000으로 liftoff하였다. 그 후 PEALD (CN1, Atomic Premium plus 200) 장비를 이용하여 Hf[N(CH<sub>3</sub>)(C<sub>2</sub>H<sub>5</sub>)]<sub>4</sub> (TEMAHf)를 전구체로 Table 3.1.1의 시퀀스를 따라 HfO2 layer을 증착하였고, 다시 maskless 장비로 패터닝하고 상부 전극을 증착한 후 liftoff 하였다. 하부 전극 증착 전 Ti는 adhesion laver로. Pt는 선저항을 낮추기 위해 사용했다. 금속들은 모두 reactive sputter (SNTEK, CDS 5000)로 증착하였으며 3 inch 지름의 금속 타겟이 사용되었고, 조건은 Table 3.1.2와 같다. Ta, RuO2 전극은 타겟 두께가 약 20 nm이었다. 선행 연구에 따르면, 이러한 구조의 RRAM은 resistive switching layer의 두께를 낮추고 전극 물질로 RuO2을 사용했기 때문에 forming-free 거동 및 더 나은 특성을 보일 수

있었다.

한편 여러 종류의 선택소자 중 선행연구[32]에 따라 용이한 설계성을 가진 TiO2 nonlinear selector를 선택하였으며 같은 방식으로 소자를 제작하였다. TiO2 layer은 타겟 두께가 7 nm이었고 Ti(OC3H7)4 (TTIP)를 전구체로, O3 농도를 250 g·m<sup>-3</sup>으로 하여 Table 3.1.3의 조건을 따라 thermal ALD (Evertek, Plus-100)로 증착하였다. 선택소자의 경우 RRAM의 특성이 나타나지 않아야 하기 때문에 역시 전극이 산소를 빼앗지 않는 것이 중요하여 마찬가지로 약 20 nm의 RuO2 전극이 사용되었다. 추후 array operation을 염두에 두어추가적으로 선저항을 낮추기 위해 Au가 e-beam evaporator (Sorona, SRN200)로 증착되었다. 선택소자 제작 시의 Ti adhesion layer 또한 e-beam evaporator로 증착되었다.

선택소자를 RRAM 위에 적층하기 위한 공정 조건이 확정되지 않았을 때, 우선 Figure 3.1.2.(a)와 같이 RRAM과 선택소자를 따로 제작하여 probe 네 개를 이용하고 외부 케이블을 통해 연결하여 전기적 특성을 관찰했다. 그러나 외부 케이블 연결 소자는 아날로그 특성 제어가 어려우며, 집적을 위해서는 적층이 필수적이다. 1S1R 적층 공정에서의 대표적인 어려움은 Figure 3.1.3와 같은 많은 공정 단계와 etch를 하지 않을 시 총 세 번의 liftoff 과정이 필요한 점에서 기인한다. 중착되는 전국이 보다 두껍고 하부 layer과의 adhesion도 달라졌기 때문에 1S1R 소자를 제작할 시 Figure 3.1.4.(a)의 예시와 같이 liftoff가 잘 이루어지지 않는 문제가 있었다. 따라서 각 전국별로 다양한 PR 및 dose 조건으로 maskless 패터닝을 하여 liftoff 완성도를 실험하였고 그 결과를 Table 3.1.4에 나타내었다. 우선 감광막 형성 과정 중 PEB(Post Exposure Bake)는 PR 표면을 평탄화하고, 노광 시

standing wave에 의해 생긴 무늬를 줄이기 위해 반드시 필요했다. 한편 SS03A9와 같은 positive PR를 쓸 경우 dose를 늘리면 dose를 적게 했을 때보다 liftoff가 잘 되었는데, PR 측면 profile이 원래의 일반적인 사다리꼴에서 보다 가파르게 형성되어 남는 것으로 추정되었다. 또한 모든 sputtered metal 전극에서 AZ5214와 같은 negative PR을 사용한 경우 PR이 역사다리꼴로 남아 현상액 침투가 용이하기 때문에 liftoff가 잘 되었다(Figure 3.1.4.(b)). 그러나 negative PR은 swelling 현상이 일어나 2  $\mu$ m 이하 선폭을 제대로 구현하지 못하는 단점이 있었다. 현소자 스택의 RRAM 부분은 작은 선폭에서 oxygen vacancy 거동의 variation이 적고 forming—free 특성이 잘 나타나므로, 하부전극은 positive PR을, 중간전극과 상부전극은 negative PR을 이용하여 Figure 3.1.2.(b)와 같이 통합 적충된 1S1R 소자를 제작했다. 다만 선행연구[5]에서는  $4\mu$ m x  $4\mu$ m 선폭에서 좋은 특성의 RRAM을 얻었지만, 실제 제작 결과 8  $\mu$ m x  $8\mu$ m에서까지 forming—free 거동이 잘나타났다.

소자들의 전기적 특성은 probe station (MSTech)에서 semiconductor parameter analyzer (SPA; Hewlett Packard, 4145B)의 I-V sweep mode로 측정하였으며, RRAM의 retention은 0.2 V에서 LRS, HRS 각각에 대하여 온도별로 측정하였다.

Figure 3.1.1. Electroforming-free RRAM 소자의 모식도.

|       | Stage<br>Temp. | TEMAHF  | Ar      | $O_2$   | O <sub>2</sub> (Plasma) | Ar      | Plasma<br>power |

|-------|----------------|---------|---------|---------|-------------------------|---------|-----------------|

| PEALD | (℃)            | Inj.(s) | Pur.(s) | Inj.(s) | Inj.(s)                 | Pur.(s) | (W)             |

|       | 200            | 1.5     | 20      | 1       | 7                       | 20      | 100             |

Table 3.1.1. PEALD 공정 조건 및 시퀀스.

|                     |          | Metal            | Power | Ar flow<br>rate | O <sub>2</sub> flow<br>rate | $P_{working}$          |

|---------------------|----------|------------------|-------|-----------------|-----------------------------|------------------------|

|                     |          | 1,10041          | (W)   | (sccm)          | (sccm)                      | (Torr)                 |

|                     | RRAM     | Та               | 100   | 30              |                             | $1.5 \times 10^{-2}$   |

|                     |          | RuO <sub>2</sub> | 60    | 30              | 3.5                         | 1.5 x 10 <sup>-2</sup> |

| Reactive<br>Sputter |          | Pt               |       | 30              |                             | $1.6 \times 10^{-2}$   |

|                     |          | Ti               |       | 20              |                             | $4.0 \times 10^{-3}$   |

|                     | Selector | Ru               | 60    | 30              |                             | $1.5 \times 10^{-2}$   |

|                     |          | RuO <sub>2</sub> | 60    | 30              | 3.5                         | 1.5 x 10 <sup>-2</sup> |

|                     |          | Pt               |       | 30              |                             | $1.6 \times 10^{-2}$   |

Table 3.1.2. Reactive sputter 공정 조건.

| Thermal<br>ALD | Stage<br>Temp.  | TTIP    | Ar      | O <sub>3</sub> | Ar      |

|----------------|-----------------|---------|---------|----------------|---------|

|                | $(\mathcal{L})$ | Inj.(s) | Pur.(s) | Inj.(s)        | Pur.(s) |

|                | 250             | 3       | 5       | 3              | 5       |

Table 3.1.3. Thermal ALD 공정 조건 및 시퀀스.

Figure 3.1.2. 1S1R 소자의 모식도. (a) 1R과 1S를 외부 전선으로 연결하여 측정하는 모습 및 스택. (b) 1R과 1S를 적층.

Figure 3.1.3. 1S1R 적층 소자 공정 단계.

|                               | BE                     | IE                     | TE                   |

|-------------------------------|------------------------|------------------------|----------------------|

|                               | Ti/Pt/RuO <sub>2</sub> | Ta/Pt/RuO <sub>2</sub> | RuO <sub>2</sub> /Pt |

| SS03A9<br>PEB X<br>Dose 100mJ | X                      | X                      | X                    |

| SS03A9<br>PEB O<br>Dose 100mJ | Bad                    | Worst                  | Worst                |

| SS03A9<br>PEB O<br>Dose 150mJ | Good                   | Bad                    | Good                 |

| AZ5214<br>Dose 30mJ           | Best                   | Best                   | Best                 |

Table 3.1.4. PR, PEB, Maskless dose 조건에 따른 liftoff 결과.

Figure 3.1.4. 조건에 따른 liftoff 결과 예시. (a) BE Bad, (b) BE Best 경우의 광학현미경 사진.

#### 3.2. 실험 결과 및 고찰

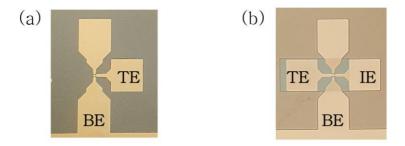

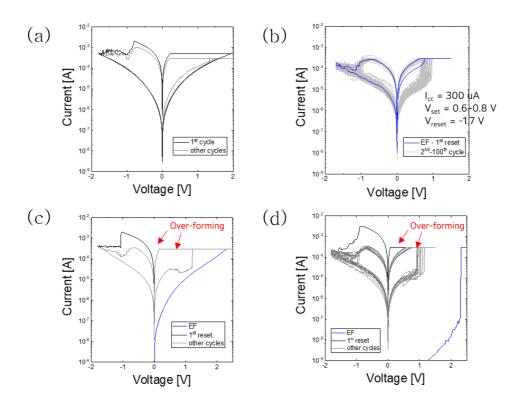

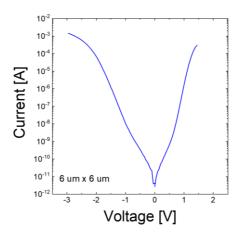

제작한  $HfO_2$  RRAM의 top view 사진을 Figure 3.2.1.(a)에, oxide 두께에 따른 I-V 그래프를 Figure 3.2.2에 나타냈다. SET, RESET 전압은 각각  $0.6 \sim 0.8$  V, -1.8 V이었으며, SET compliance current는  $300~\mu A$ 로 걸어주었다.

HfO<sub>2</sub> forming-free 소자를 제작하기 위해서 oxide 두께를 적절히 맞추고 Ta. RuO2와 같이 oxide 내부의 oxygen vacancy source 및 sink 역할을 잘 수행하는 전극을 이용하였다. 그러나 PEALD 장비의 경우 growth per cycle(GPC)이 달랐기 때문에, 적절한 두께를 맞추기 위해 PEALD 시퀀스 cycle을 조금씩 달리하며 oxide를 증착하였다. 그 결과를 Table 3.2.1에 나타내었으며, 샘플별 총 cycle 수는 GPC가 서로 다른 이상 중요하지 않으므로 표기하지 않았다. 샘플들의 사이클별 XRF 두께는 샘플과 같이 넣은 SiO<sub>2</sub> 기판 위의 HfO<sub>2</sub> 두께를 잰 것인데, HfO2는 SiO2보다 RuO2 위에서 초반에 growth per cycle이 약 3배 크다는 선행연구[5]를 토대로 RuO<sub>2</sub> 위 HfO<sub>2</sub> 두께를 계산하였다. HfO<sub>2</sub> 두께가 약 2 nm 이하(Figure 3.2.2(a))인 샘플에서는 oxide 층이 너무 얇은 관계로 leakage current가 높고 SET이 되려면 compliance current를 올려야 했다. 또한 두께를 지나치게 줄이면 selecting device와 current level이 맞지 않고, window가 작아질 가능성을 확인하였다. 한편 HfO2 약 4 nm 이상(Figure 3.2.2.(c, d)) 샘플에서는 oxide film이 두꺼워 forming-free 특성이 나타나지 못하고, overforming이 일어나서 array로 사용하기 어려움을 확인할 수 있었다. 한편 Figure 3.2.2.(b)와 같이 HfO2의 두께가 3.3 nm 정도로 증착된 경우 실제로 forming-free 특성을 보임을 확인했다. 다만 제작한 샘플에서 모든 cell이 forming-free 특성을 잘 보이지 않았기 때문에, array operation을 위해서는 cell간 variation을 줄일 필요가 있다.

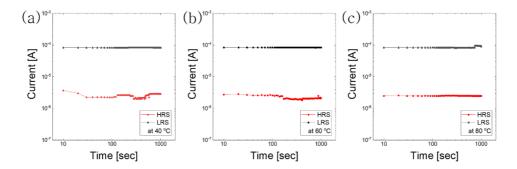

Figure 3.2.3는 forming-free RRAM 소자의 온도별 retention 테스트 결과이다. 온도를 적절히 올릴 경우 80 ℃에서도 10<sup>3</sup> sec까지 state가 잘 유지되었다. 이에 이 소자를 이용하여 선택소자와의 적층을 시도하고 아날로그 테스트를 수행하였다.

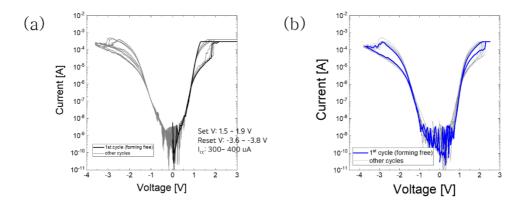

Figure 3.2.4는 1R과 따로 제작한 선택소자의 I-V 그래프이다. 양방향 동작이 가능했으며, 선택소자의 nonlinearity를 (1.5 V에서의 전류 값)/(0.75 V에서의 전류 값)이라 정의하면 10<sup>4</sup> 이상으로 누설 전류를 효과적으로 차단할 수 있으리라 기대하였다. 이어 RRAM과 선택소자를 통합한 1S1R 소자의 top view 사진을 Figure 3.2.1.(b)에, DC I-V sweep 결과를 Figure 3.2.5에 나타내었다. RRAM과 선택소자를 external 케이블로 연결한 경우(Figure 3.2.5.(a))와 공정을 통해 적층한 경우(Figure 3.2.5.(b))에서 유사한 거동을 얻을 수 있었다. 선택소자 덕분에 낮은 전압 영역에서는 효과적으로 leakage current가 차단되었고, 동작 영역에서 RRAM의 forming-free 특성도 같이나타났다. 그러나 작은 window와 cell간 variation 문제는 개선이 더필요한 것으로 보인다.

Figure 3.2.1. 제작한 소자의 top view 사진. (a) RRAM, (b) 1S1R.

Figure 3.2.2. Oxide 두께별 RRAM의 I-V curve. (a) 2nm 이하, (b) 3.3nm, (c) 4.4nm, (d) 5nm.

| Sample                                    | (a)   | (b)                            | (c)   | (d)   |

|-------------------------------------------|-------|--------------------------------|-------|-------|

| XRF (µg/cm <sup>2</sup> )                 | 0.52  | 0.9                            | 1.2   | 1.4   |

| XRF thickness (Å)                         | 6.42  | 11.11                          | 14.81 | 17.28 |

| Estimated RuO <sub>2</sub> thickness (nm) | < 2nm | 3.3nm (forming- free behavior) | 4.4nm | 5nm   |

Table 3.2.1. 샘플별 XRF 결과와 계산된 oxide의 두께.

Figure 3.2.3. 제작한 RRAM 소자의 온도별 retention 결과. (a) 40 ℃, (b) 60 ℃, (c) 80 ℃에서의 retention.

Figure 3.2.4. 제작한 selector 소자의 I-V curve.

Figure 3.2.5. 제작한 1S1R 소자의 I-V curve. (a) 외부 전선으로 연결한 경우, (b) 적층한 경우.

### 4. 커패시턴스가 아날로그 특성에 미치는 영향

#### 4.1. 실험 목적 및 설계

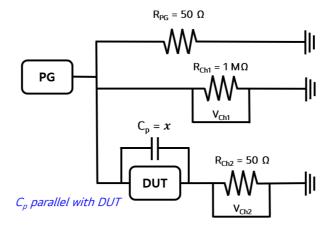

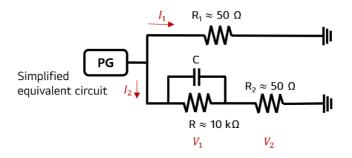

외부 케이블로 1S와 1R을 연결하면 집적 문제뿐 아니라 parasitic element의 증가로 아날로그 특성이 변화되는 것을 관찰하였고, 특히 소자와 병렬 연결 관계의 parasitic capacitance가 증가된 것으로 생각하였다. 따라서 DUT(Device Under Test)에 병렬로 연결된 커패시턴스가 증가할 때 실제로 소자의 아날로그 특성이 어떠한 영향을 받는지 확인하기 위하여 T자형 커넥터 두 개를 이용, 소자에 직접 커패시터를 병렬 연결하여 측정을 시도하였다. 회로도는 Figure 4.1.1과 같다. Pulse generator (PG; Agilent, 81110A)로 펄스를 가하고 oscilloscope (OSC; Tektronix, TDS 684C)로 펄스 모니터링을 하였으며(Vch1, Vch2), SPA로 DC read를 하였다. PG는 voltage—programmed current source로, 입력한 전압을 k라 하면  $I_{total} = \frac{k}{25}$ 의 전류를 흘린다. Figure 4.1.1의 회로에서  $R_{DUT} \approx 10 \ k\Omega$  라 가정하면 총 저항은  $R_{total} \approx 50 \ \Omega$  정도이고,  $V = R_{total} \times I_{total} \approx 2k$  정도가 PG와 나머지 요소들 사이의 노드에 걸리게 된다.

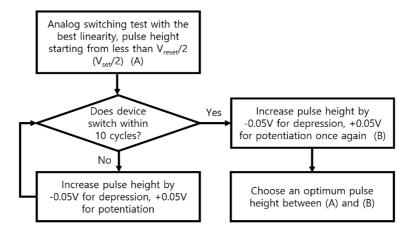

한편 필스 조건은 RRAM의 아날로그 거동의 지표들(dynamic range, nonlinearity, asymmetry 등)에 중요한 영향을 미치기 때문에, 커패시턴스의 영향을 확인하기에 앞서 Figure 4.1.2와 같이 체계적으로 가장 큰 변인인 pulse width와 height를 조절하여 최적화를 시도하였다. 최적 필스 조건은 커패시터를 따로 달지 않은 소자 기준으로 구하였다.

우선 pulse width에 따른 변화를 확인한 후 width를  $1~\mu s$ 로 고정하고 pulse height 조건을 탐색하였다. 절댓값이 작은 전압부터 시작해서, 10회 안에 device의 스위칭이 잘 되지 않을 경우 0.05~V씩 절댓값을 증가시키는 방향으로 최적의 pulse height를 찾아내었다.

Figure 4.1.1. 소자의 아날로그 특성 측정 회로도.

Figure 4.1.2. Pulse 조건 최적화 과정 순서도.

#### 4.2. 실험 결과 및 고찰

Figure 4.2.1에서와 같이, 우선 pulse width를 변화시키며 실험해본 결과 pulse width가 증가할수록 적은 pulse number로 큰 conductance 변화를 일으킴을 확인하였다. 이후 pulse width를 고정하고 height를 조절하며 실험하였고, Figure 4.2.2에 예시를 나타내었다. 이 샘플에서 depression 시에는 -1.3 V 보다 작은 전압에서는 conductance 변화가 미미했고, -1.4 V 보다 큰 전압에서는 지나치게 변화하여 아날로그소자로 응용하기 힘들다. Potentiation 시에는 1.05 V 이하에서는 스위칭이 일어나지 않았으며, 1.1 V 이상에서 depression에서보다급격한 스위칭이 일어남을 알 수 있다. 이 샘플의 경우 최적 RESET pulse를 -1.35 V, 최적 SET pulse를 1.1 V로 설정하였다. 소자별로 최적 조건이 달랐지만, Figure 4.2.3와 같이 일정 범위 내에 최적 pulse height가 존재하였다. 평균은 SET pulse의 경우 1.08 V, RESET pulse의 경우 -1.41 V였다.

Figure 4.2.4는 이렇게 구한 최적 펄스 조건으로 external cable로 연결한 1S1R 소자의 아날로그 특성을 측정한 결과 예시이다. 이 샘플의 최적 펄스 조건은 SET 1.15 V, RESET -1.45 V이었고 1.6 V에서 DC read를 하였다. 아날로그 특성 커브에서 nonlinearity와 asymmetry도 나타나지만, dynamic range degradation과 특히 potentiation에서 이전의 LRS 상태까지 제대로 회복하지 못하는 현상이 두드러졌다. 이러한 비이상적인 아날로그 스위칭 거동의 원인들은 다음과 같다. 첫 번째로, RRAM 자체의 원인이 존재한다. RRAM의 아날로그 스위칭은 두단계로 이루어진다. SET이 일어나는 과정에서 초반에는 filament와 전극 간 gap에 높은 전기장이 걸려 이온 drift가 쉽기에 conductance

변화가 크지만, 점차 lateral growth를 할 때에는 이미 저항이 낮아진 상태이고 전계 집중이 줄어들며 filament 주변으로 모일 oxygen vacancy가 점차 고갈되어 확장되려는 구동력이 약해질 것이다.[27.33] RESET에서도 마찬가지로, filament를 끊는 것보다 gap을 늘리는 것이 더 어려워 conductance 변화율이 작아진다 할 수 있다. 또한 전극과 oxide의 계면에 생성되는 metal oxide interfacial layer의 영향도 고려해야 한다.[34] Figure 4.2.5와 같이 TaO<sub>x</sub> interfacial layer가 생기는 것이 Ta와 oxygen ion의 만남을 방해하고, 가해 준 전압이 switching layer에 온전히 걸리는 것을 막는다. 두 번째로, 이러한 RRAM에 1S 소자가 추가됨으로써 발생하는 효과를 생각해 볼 수 있다. 선행연구에 따르면, 선택소자의 nonlinearity 정도가 1S와 1R의 전압 분배에 영향을 미치기 때문에 아날로그 특성 커브의 linearity에도 영향을 줄 있다.[35] 선택소자가 가파르게 'on' 이 된다면 RRAM 쪽에 급격히 더 많은 전압이 걸리는데, 인가 전압이 RRAM 단독으로 있을 때보다 더 크므로 conductance가 더욱 급격히 변할 여지가 있는 것이다. 그러나 본 연구에서 사용한 선택소자의 기울기와 유사한 nonlinear selector의 경우 RRAM에 걸리는 전압이 거의 일정하도록 조절해주기도 한다. 따라서 현 1S1R 소자의 아날로그 특성을 변화시킨 가장 큰 요인은 parasitic capacitance인 것으로 예상되었다. 즉, 케이블과 커넥터로 인한 parasitic capacitance 증가가 아날로그 스위칭에 악영향을 미쳤다.

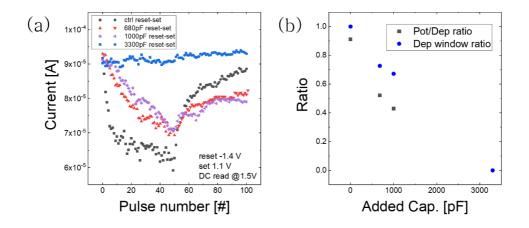

이를 검증하기 위해 DUT에 평행하게 커패시터를 연결하여 parasitic capacitance를 조절하고 그 영향을 알아보았다. 이때는 적층한 1S1R 소자를 이용하였는데, 케이블 연결 소자의 경우 이미 아날로그특성이 좋지 않았기 때문이다. DUT와 회로의 기본 커패시턴스를 RC

delay로 구하였을 때 약 500 pF로 측정되었다( $C = \frac{\tau}{p}$ ,  $\tau = \text{time}$ constant). 추가하는 커패시턴스 값을 x라 하고 x = 680, 1000, 3300 pF로 하였을 때 Figure 4.2.6.(a)와 같은 아날로그 커브 결과를 얻었다. Figure 4.2.6.(b)의 'Pot/Dep ratio'는 Figure 4.2.6.(a)에서 |Potentiation 과정에서의 총 전류 변화량|(= Potentiation window)을 |Depression 과정에서의 총 전류 변화량|(= Depression window)으로 나눈 값을 계산한 것이고, 'Dep window ratio' 는 커패시터를 추가하지 않은 대조군 대비 depression window가 얼마나 감소했는지 그 비율을 계산한 것이다. Figure 4.2.6에서 가장 두드러지는 것은 예상했던 바와 같이 window 및 Pot/Dep 비의 감소였다. 커패시터를 추가하지 않았을 때에는 초반에 급격히 state가 변하긴 하지만 거의 처음 저항 상태까지 잘 회복되었다. 그러나 추가 커패시터 값이 증가할수록 window가 작아지고 dynamic range degradation이 심해졌으며, 커패시터 값이 아주 커질 경우 아예 transition이 일어나지 않았다. 전체 측정 중 80 %가량(32회 중 25.5회)에서 추가 커패시턴스가 증가할수록 이러한 경향성을 보였다.

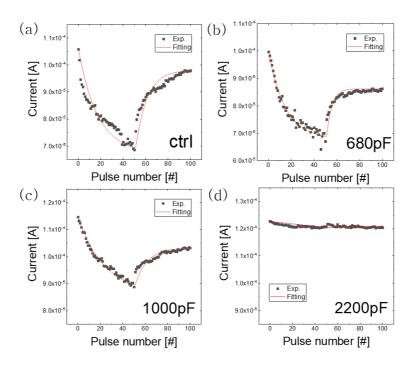

아날로그 conductance가 초반에 급격히 증가하다 saturation되는 과정으로 이루어져 있기 때문에, 각 그룹별로 그래프의 평균을 얻은 후 mean squared error가 최소가 되도록 eq.(1)의 식으로 exponential fitting을 시도하였다(Figure 4.2.8, Table 4.2.1). Linearity factor은 eq.(2)와 같이 피팅 그래프의 기울기 최솟값을 기울기 최댓값으로 나눈 수치로 설정하였다.

$$I = Ae^{B \cdot n} + C \tag{1}$$

(I: current, n: number of pulses)

$$Linearity\ factor = \frac{\min(dI_{reset\ or\ set}/d\ n)}{\max(dI_{reset\ or\ set}/d\ n)} = \frac{\min dG_{reset\ or\ set}}{\max dG_{reset\ or\ set}} \tag{2}$$

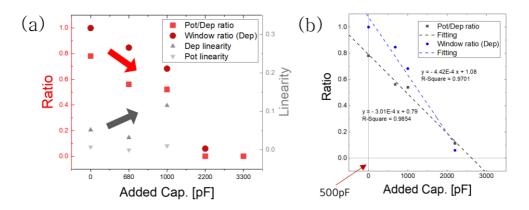

그 결과는 Figure 4.2.7.(a)와 같다. Figure 4.2.6의 예시와 마찬가지로, 커패시턴스가 증가할수록 Pot/Dep ratio와 window가 확연히 감소하였다. 일반적으로 window와 trade-off 관계에 있는 linearity는 커지는 경향성을 보였으나, window의 degradation이 극심하다면 뉴럴 네트워크에 활용할 수 없을 것이므로 ratio의 감소가 더욱 큰 문제라고 설정하였다. 한편 Figure 4.2.7.(b)에 나타낸 것과 같이, Pot/Dep ratio와 Dep window는 추가한 커패시터 값과 선형적 관계가 있었다. 커패시터를 달지 않았을 때 기본적으로 존재하던 커패시턴스가 500 pF였기 때문에, 이를 줄이면 Pot/Dep ratio 및 depression window가 보다 커질 수 있음을 예상해볼 수 있다. 두 linear fitting의 x 절편은 약 2500 pF로, 이 정도의 커패시터를 추가하면 스위칭이 전혀 일어나지 않을 것이라 예측 가능하다.

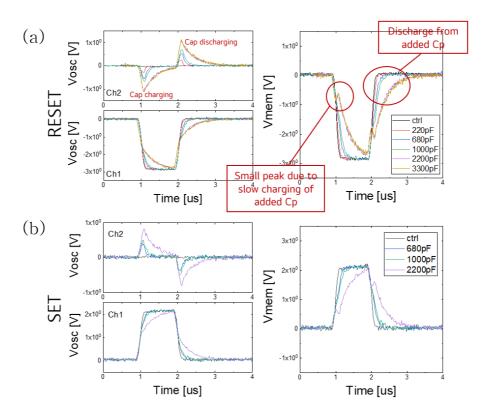

Figure 4.2.9에는 OSC의 Ch1과 Ch2의 시간에 따른 전압 그래프를 나타내었다. RESET peak 전압으로는 -1.45 V, SET peak 전압으로는 1.05 V를 입력하였다. Ch1 전압에서 Ch2 전압을 빼면 DUT에 걸리는 전압을 구할 수 있는데, 커패시턴스가 커질수록 charging 및 discharging의 영향이 크기 때문에 DUT의 전압 및 전류가 서서히 증가한다. Pulse width가 제한되어 있기 때문에, 불충분한 DUT 전류와 전압의 증가가 DUT의 conductance 변화를 둔화시킨다고 해석할 수 있다.

앞선 결과는 equivalent circuit model을 풀어 설명할 수 있었다. 풀이를 위해 Figure 4.2.10과 같이 회로를 간소화하고, 펄스 한 번을 가할 때 DUT의 저항 값인 R이 거의 변하지 않는다 가정하면, 우선 current source인 PG가 생성하는 총 전류는 eq.(3)와 같이 나타낼 수 있다.

$$I_{total} = I_1 + I_2 = \frac{k}{25} \tag{3}$$

(k: input peak voltage value)

또한  $V_1$ 과  $V_2$ 의 합은 eq.(4)와 같이  $R_1$ 에 걸리는 전압과 같다.

$$V_1 + V_2 = 50I_1 \tag{4}$$

마지막으로 C와 R에 흐르는 전류의 합은  $R_2$ 에 흐르는 전류와 같기 때문에 eq.(5)과 같은 식이 성립한다.

$$I_2 = \frac{V_2}{50} = C \frac{\partial V_1}{\partial t} + \frac{V_1}{R} \tag{5}$$

$Eq.(3)\sim(5)$ 를 풀면 eq.(6), (7)과 같이  $V_1$ 과  $V_2$ 에 대한 식을 얻을 수 있다.

$$V_1 = \frac{2Rx}{R+100} \left( 1 - e^{-\frac{R+100}{100RC}t} \right) \tag{6}$$

$$V_2 = \frac{100x}{R+100} + \frac{Rx}{R+100} e^{-\frac{R+100}{100RC}t}$$

(7)

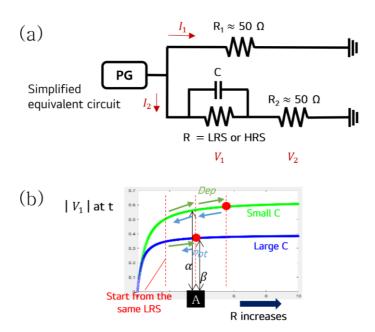

$V_1$ 과  $V_2$ 의 커패시턴스 변화에 따른 대략적인 개형은 Figure 4.2.11와 같다. 초기의 어떤 시간 t에서, R과 평행 관계인 C의 값이 증가할수록  $V_1$ 는 작아지고  $V_2$ 는 커진다. 즉, 커패시터가 병렬로 달린 저항 쪽의 전압이 천천히 증가하는 것이다. 그 이유는 다음과 같다. 전압이나 전류가 가해지기 전 전하가 채워져 있지 않은 커패시터에는  $V=\frac{Q}{c}$ 의 식에 의해 전압이 걸려 있지 않다. 따라서 R에도 전압이 걸리지 않는다. 그러다 커패시터에 전하가 채워질수록  $V_1$ 이 증가하고 저항에도 전류가 흐르게 된다. 그런데 커패시턴스가 클 경우 time constant가 크기 때문에  $V_1$ 이 더 천천히 증가한다. 만약 pulse width가 아주 길다면  $V_1$ 에 걸리는 최대 전압은 R에만 의존하므로 결국 C 값에 관계없이 최대 전압에 도달할 수 있겠지만, 본 실험의 pulse width에서는 커패시턴스를 크게 증가시키면 DUT에 전압이 충분히 잘

걸리지 못하게 되었다.

이어서 같은 circuit model에서 DUT의 conductance state, 즉 R이 DUT에 가해지는 전압에 어떠한 영향을 달라지면 미치는지 알아보았다(Figure 4.2.12.(a)). Eq.(6). (7)은 SET 과정과 RESET 모두에 적용되므로 각각의  $V_1$  값은 다르겠지만 과정 Figure 4.2.12.(b)와 같은 개형을 공유한다. 이러한 R에 따른 V<sub>1</sub>의 개형을 살펴보면, 고정된 초기의 t에서 DUT의 저항이 낮을수록, 즉 LRS 상태가 되어 갈수록 V1이 더 작으며, 시간이 더 흘렀을 때 도달할 수 있는 최대 전압 값 또한 더 작았다. 사실 이처럼 기본적으로 parasitic capacitance가 크든 작든, SET 과정은 진행되면 될수록 DUT에 걸리는 전압이 작아지고, 심지어 nonlinearity가 큰 셀렉터가 연결되었다면 1R에 걸리는 전압도 더 작아져서 스위칭이 어렵게 되며 이것이 SET 과정 시 아날로그 거동이 saturation되는 원인 중 하나로 작용한다. 그러나 그 와중에도 커패시턴스가 작을 때 Pot/Dep ratio가 거의 1에 가까운 경우가 존재한다. 그 경우를 Figure 4.2.12.(b)에서 small C라고 나타내었고, 커패시터를 추가한 경우를 large C라 하였으며 depression. potentiation 과정에서의 V<sub>1</sub> 변화를 화살표로 표시하였다. Small C 경우의 pot-dep 궤적에 나타난 V1값이 각 저항 state에서 SET 혹은 RESET transition에 필요한 '적절한' DUT 전압 값일 것이다. 그런데 이 경우보다 parasitic capacitance가 크다면, 어떠한 저항 state에서도 Pot/Dep ratio를 '적절히' 하기 위한 전압 값에 도달하지 못한다. 그래서 처음에 같은 LRS에서 시작하더라도, 작은 parasitic capacitance에서의 depression window에 비해서, 큰 parasitic capacitance에서는 그보다 작은 정도로 저항이 변한다. 그리고 다시 potentiation을 할 때, 원래 Figure 4.2.12.(b)의 A state에서 처음 상태로 가기 위한  $V_1$ 값은  $\alpha$  만큼이었는데, large C의 경우 늘 그 전압보다 작은 전압( $\beta$ )이 DUT에 걸린다. 이것이 parasitic capacitance가 증가할수록 dynamic range degradation이 심각해지는 이유이다.

본 연구에서는 pulse 측정을 depression-potentiation 순으로 했는데, 그 이유는 소자의 variation으로 인해 HRS를 동일한 level로 맞추는 것이 어려웠기 때문이다. Variation 문제가 극복된다면 HRS에서부터 시작하는 potentiation-depression 순으로 측정해도 동일한 결과가 나오는지 확인이 필요하다.

이처럼 병렬 커패시턴스의 증가는 아날로그 특성 중 특히 dynamic range degradation를 심화시킨다. 수행 과제 및 소자에 따라 차이가 있겠지만, 소자의 conductance window가 10 % 정도만 감소해도 뉴럴 네트워크 분류 정확도가 50 %가량이나 저하되었다는 선행 연구도 존재한다.[36] 따라서 1S1R 소자 제작 시 parasitic capacitance를 줄이기 위해 선택소자를 적충하는 공정이 필수적이고, 소자 전극 크기를 불필요하게 키우지 말아야 한다. 한편 소자 자체의 커패시턴스는 8 μm x 8 μm 선폭의 3nm HfO<sub>2</sub> RRAM의 경우 약 4.7 pF로 계산되어, 회로 전체의 커패시턴스에 비해 작은 값을 가진다. 선택소자를 고려하더라도 직렬 관계인 1R, 1S 각각의 저항에 커패시턴스가 병렬 연결된 형태를 띠어, 회로 전체 커패시턴스에 비하면 무시 가능하다. 따라서 소자를 측정할 때에는 커넥터를 최소화하고 probe needle이나 케이블 등을 최대한 짧게 장비를 세팅하여 회로에서 기인하는 parasitic capacitance를 줄이려는 노력이 필요하다.

Figure 4.2.1. Pulse width에 따른 depression 거동 변화.

Figure 4.2.2. Pulse height에 따른 depression, potentiation 거동 변화.

# Optimum $V_{\text{set}}$ , $V_{\text{reset}}$ Distribution

Figure 4.2.3. 최적의 SET, RESET pulse height 분포.

Figure 4.2.4. 외부 케이블로 연결한 1S1R 소자의 아날로그 스위칭특성.

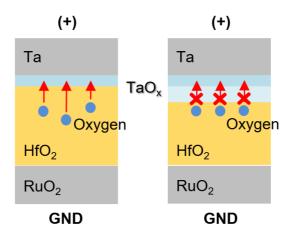

**Figure 4.2.5.** Interfacial layer 생성이 RRAM의 스위칭을 방해하는 원리 모식도.

Figure 4.2.6. 추가 capacitance에 따른 아날로그 스위칭 변화(한 개샘플). (a) 펄스 횟수에 따른 전류(전도도) 변화. (b) Pot/Dep window 비율과 상대적인 depression window 변화.

Figure 4.2.7. 추가 capacitance에 따른 아날로그 특성 지표 변화(측정 샘플들 평균). (a) Window ratio, linearity 변화. (b) Pot/Dep ratio, Dep window ratio와 추가 capacitance의 선형 관계.

Figure 4.2.8. 추가 capacitance별 아날로그 스위칭 그래프의 exponential fitting. (a) 추가 capacitor을 달지 않은 경우, (b) 680 pF, (c) 1000 pF, (d) 2200 pF를 단 경우.

|        | A        |           | В         |           | С        |          |

|--------|----------|-----------|-----------|-----------|----------|----------|

|        | Dep      | Pot       | Dep       | Pot       | Dep      | Pot      |

| Ctrl   | 3.8.E-05 | -4.3.E-03 | -5.9.E-02 | -9.8.E-02 | 6.8.E-05 | 9.8.E-05 |

| 680pF  | 3.2.E-05 | -1.1.E+00 | -6.9.E-02 | -2.2.E-01 | 6.8.E-05 | 8.6.E-05 |

| 1000pF | 2.8.E-05 | -1.4.E-03 | -4.3.E-02 | -9.2.E-02 | 8.7.E-05 | 1.0.E-04 |

| 2200pF | 1.2.E-04 | -4.0.E-05 | -3.6.E-04 | -1.3.E-04 | 1.0.E-06 | 1.6.E-04 |

Table 4.2.1. Exponential fitting에서의 파라미터.

Figure 4.2.9. Ch1, Ch2, DUT에 걸리는 시간에 따른 전압. (a) RESET pulse (-1.45 V), (b) SET pulse (1.05 V)를 가했을 때.

Figure 4.2.10. 간소화된 등가 회로 모델(고정된 DUT 저항).

Figure 4.2.11. 모델에서 계산된 capacitance에 따른 DUT 전압 $(V_1)$ , Ch2 전압 $(V_2)$ 의 개형.

Figure 4.2.12. 모델에서 계산된 DUT 저항에 따른 DUT 전압 $(V_1)$ . (a) 간소화된 등가 회로 모델(변하는 DUT 저항). (b) DUT 저항과 capacitance에 따른 DUT 전압 $(V_1)$  개형 및 dynamic range degradation 원리.

# 5. 결론

본 연구에서는 electroforming-free RRAM 소자와 선택소자 운용을 통해 RRAM의 한계점을 보완하고자 하였다. Oxide 두께를 감소시킴과 동시에 RuO2 전극을 이용하여 electroforming-free 거동을 보이도록 한 thin HfO2 RRAM을 제작하였고, 이를 selector 소자와 통합하였다. 이에 외부 케이블로 RRAM과 selector을 연결한 소자, 그리고 공정 개선을 통해 적층에 성공한 1S1R 소자를 얻었다. 전기적특성 평가 결과 RRAM의 경우 특정 범위의 oxide 두께(약 3.3 nm)를 가져야만 forming-free 특성과 적절한 current level을 보였으며, 소자는 아날로그 pulse 측정을 시도하기에 적당한 retention을 가졌다. 한편 외부 전선으로 연결한 1S1R 소자와 적층 제작한 1S1R 소자는 DC 거동에서는 큰 차이가 없었다.

이어서 1S1R 소자의 아날로그 특성에 대해 탐구하였다. 뉴로모픽컴퓨팅에 응용하기 위해서는 RRAM이 이상적인 아날로그 스위칭거동을 보이는 것이 바람직하지만, 외부 전선으로 연결한 1S1R 소자는 dynamic range degradation이 두드러지는 현상이 나타났다. 본연구에서는 이러한 현상의 주된 원인이 케이블로 인해 증가한 parasitic capacitance라고 보고, 적층한 1S1R의 병렬 커패시턴스를 조절하여커패시턴스가 1S1R 소자의 아날로그 특성에 미치는 영향을 실험적으로 증명하고자 하였다. 그 결과 증가한 커패시턴스는 dynamic range와 potentiation/depression ratio를 심각하게 악화시켰고, 약 2500 pF이상의 커패시터를 추가할 경우 스위칭이 일어나지 않을 것으로 예상되었다. 이후 회로 모델을 통해 그 원인에 대해 고찰하였으며,

커패시턴스가 소자에 충분한 전압이 걸리지 못하게 하는 현상을 설명할수 있는 논리적인 방법을 제안하였다. 이를 통해 1S1R 제작 시 외부케이블 연결이 아닌 통합된 형태로 적층 공정하고, 회로 설계 시 parasitic capacitance를 줄이는 것이 아날로그 특성 확보에 필수적임을 시사하였다.

# 참고 문헌

- [1] D. S. Jeong, R. Thomas, R. S. Katiyar, J. F. Scott, H. Kohlstedt, A. Petraru, C. S. Hwang, Reports on Progress in Physics 2012, 75, 076502.

- [2] R. Waser, M. Aono, Nature Materials 2007, 6, 833.

- [3] R. Waser, R. Dittmann, G. Staikov, K. Szot, *Advanced Materials* 2009, 21, 2632.

- [4] T. H. Park, S. J. Song, H. J. Kim, S. G. Kim, S. Chung, B. Y. Kim, K. J. Lee, K. M. Kim, B. J. Choi, C. S. Hwang, physica status solidi (RRL) Rapid Research Letters 2015, 9, 362.

- [5] G. S. Kim, H. Song, Y. K. Lee, J. H. Kim, W. Kim, T. H. Park, H. J. Kim, K. Min Kim, C. S. Hwang, ACS Applied Materials & Interfaces 2019, 11, 47063.

- [6] J. H. Yoon, S. J. Song, I.-H. Yoo, J. Y. Seok, K. J. Yoon, D. E. Kwon, T. H. Park, C. S. Hwang, Advanced Functional Materials 2014, 24, 5086.

- [7] K. M. Kim, J. Zhang, C. Graves, J. J. Yang, B. J. Choi, C. S. Hwang,

Z. Li, R. S. Williams, *Nano Letters* 2016, *16*, 6724.

- [8] An Chen, 2013 IEEE 13th Non-Volatile Memory Technology Symposium (NVMTS) 2013.

- [9] J.-J. Huang, Yi-Ming Tseng, Wun-Cheng Luo, Chung-Wei Hsu,T.-H. Hou, 2011 IEEE International Electron Devices Meeting2011.

- [10] D. Ielmini, and R. Waser, eds. Resistive switching: from fundamentals of nanoionic redox processes to memristive device applications. John Wiley & Sons, 2015.

- [11] J. Kim, H. C. Woo, T. Jeong, J.-H. Choi, C. S. Hwang, *Advanced Intelligent Systems* **2021**, *4*, 2100174.

- [12] Z. Wang, H. Wu, G. W. Burr, C. S. Hwang, K. L. Wang, Q. Xia, J. J. Yang, Nature Reviews Materials 2020, 5, 173.

- [13] J. Y. Seok, S. J. Song, J. H. Yoon, K. J. Yoon, T. H. Park, D. E. Kwon, H. Lim, G. H. Kim, D. S. Jeong, C. S. Hwang, Advanced Functional Materials 2014, 24, 5316.

- [14] T. H. Park, S. J. Song, H. J. Kim, S. G. Kim, S. Chung, B. Y. Kim, K. J. Lee, K. M. Kim, B. J. Choi, C. S. Hwang, *Scientific Reports* 2015, 5.

- [15] F.-C. Chiu, Advances in Materials Science and Engineering 2014, 2014, 1.

- [16] Y. Kim, Y. J. Kwon, J. Kim, C. H. An, T. Park, D. E. Kwon, H. C. Woo, H. J. Kim, J. H. Yoon, C. S. Hwang, *Advanced Electronic Materials* 2019, 5, 1800806.

- [17] J. Woo, J. Song, K. Moon, J. H. Lee, E. Cha, A. Prakash, D. Lee, S. Lee, J. Park, Y. Koo, C. G. Park, H. Hwang, 2014 IEEE Symposium on VLSI Technology (VLSI-Technology): Digest of Technical Papers 2014.

- [18] J. Shin, I. Kim, K. P. Biju, M. Jo, J. Park, J. Lee, S. Jung, W. Lee, S. Kim, S. Park, H. Hwang, Journal of Applied Physics 2011, 109, 033712.

- [19] M. Wang, J. Zhou, Y. Yang, S. Gaba, M. Liu, W. D. Lu, *Nanoscale* 2015, 7, 4964.

- [20] Q. Luo, X. Xu, H. Lv, T. Gong, S. Long, Q. Liu, L. Li, M. Liu, Nano Research 2017, 10, 3295.

- [21] B. J. Choi, J. Zhang, K. Norris, G. Gibson, K. M. Kim, W. Jackson, M. X. M. Zhang, Z. Li, J. J. Yang, R. S. Williams, Advanced Materials 2015, 28, 356.

- [22] B. Govoreanu, C. Adelmann, A. Redolfi, L. Zhang, S. Clima, M. Jurczak, *IEEE Electron Device Letters* **2014**, *35*, 63.

- [23] W. Lee, J. Park, J. Shin, J. Woo, S. Kim, G. Choi, S. Jung, S. Park, D. Lee, E. Cha, H. D. Lee, S. G. Kim, S. Chung, H. Hwang, 2012 IEEE Symposium on VLSI Technology (VLSIT) 2012, 37.

- [24] P. Yao, H. Wu, B. Gao, S. B. Eryilmaz, X. Huang, W. Zhang, Q. Zhang, N. Deng, L. Shi, H.-S. P. Wong, H. Qian, Nature Communications 2017, 8.

- [25] Z. Wang, C. Li, W. Song, M. Rao, D. Belkin, Y. Li, P. Yan, H. Jiang, P. Lin, M. Hu, J. P. Strachan, N. Ge, M. Barnell, Q. Wu, A. G. Barto, Q. Qiu, R. S. Williams, Q. Xia, J. J. Yang, Nature Electronics 2019, 2, 115.

- [26] M. Zhao, B. Gao, J. Tang, H. Qian, H. Wu, *Applied Physics Reviews* **2020**, *7*, 011301.

- [27] W. Wu, H. Wu, B. Gao, P. Yao, X. Zhang, X. Peng, S. Yu, H. Qian, 2018 IEEE Symposium on VLSI Technology 2018, 103.

- [28] W. Wu, H. Wu, B. Gao, N. Deng, H. Qian, *Journal of Applied Physics* **2018**, *124*, 152108.

- [29] S. Chandrasekaran, F. M. Simanjuntak, R. Saminathan, D. Panda, T.-Y. Tseng, *Nanotechnology* **2019**, *30*, 445205.

- [30] I.-T. Wang, C.-C. Chang, L.-W. Chiu, T. Chou, T.-H. Hou, Nanotechnology 2016, 27, 365204.

- [31] Y. Liao, B. Gao, F. Xu, P. Yao, J. Chen, W. Zhang, J. Tang, H. Wu,H. Qian, *IEEE Transactions on Electron Devices* 2020, 67, 1593.

- [32] H. C. Woo, J. Kim, S. Lee, H. J. Kim, C. S. Hwang, *Advanced Electronic Materials* **2022**, *8*, 2200656.

- [33] H. Liu, M. Wei, Y. Chen, Nanotechnology Reviews 2018, 7, 443.

- [34] J. Park, C. Lee, M. Kwak, S. A. Chekol, S. Lim, M. Kim, J. Woo, H. Hwang, D. Lee, *Nanotechnology* 2019, 30, 305202.

- [35] J. Woo, S. Yu, *IEEE Transactions on Very Large Scale Integration (VLSI) Systems* **2019**, *27*, 2205.

- [36] P.-Y. Chen, S. Yu, 2018 IEEE International Reliability Physics Symposium (IRPS) 2018.

#### **Abstract**

# Effects of capacitance on electroforming-free HfO<sub>2</sub> RRAM based one-selector-one-resistor (1S1R) device

Sunwoo Lee

Department of Material Science and Engineering

The Graduate School

Seoul National University

Resistive Random Access Memory (RRAM) has attracted attention as a next-generation memory to replace existing memories that are expected to reach the scaling limit. In particular, when RRAM is used as an analog synapse in a crossbar array (CBA) structure, it can be applied to neuromorphic computing, which can solve the von Neumann bottleneck and process more data with less power. However, the commercialization of RRAM has limitations, such as device variation and breakdown due to the electroforming process and leakage current in CBA. Therefore, in this study, efforts were made to make up for these limitations by exploiting electroforming—free RRAM and selector devices. An HfO<sub>2</sub>—based forming—free RRAM and a TiO<sub>2</sub>—based nonlinear selector were fabricated and integrated, and their electrical behavior was observed.

For application to neuromorphic computing, it is desirable for RRAM to exhibit ideal analog switching behavior, but one-selector-

one—resistor (1S1R) devices connected by external wires showed severe dynamic range degradation in analog behavior. Herein, the leading cause of this phenomenon was considered to be increased parasitic capacitance, and the parallel capacitance of the stacked 1S1R was adjusted to experimentally prove the effects of capacitance on the analog characteristics of the device. In addition, the cause was analyzed through a circuit model. Finally, this study suggests that it is essential to reduce parasitic capacitance by using an integrated stacking process rather than an external cable connection when manufacturing 1S1R.

Keywords: Resistive Switching Memory, Electroforming-free, Nonlinear Selector, Capacitance, Analog Switching, Nonideal Effects Student Number: 2021-27239