#### 저작자표시-비영리-변경금지 2.0 대한민국

#### 이용자는 아래의 조건을 따르는 경우에 한하여 자유롭게

• 이 저작물을 복제, 배포, 전송, 전시, 공연 및 방송할 수 있습니다.

#### 다음과 같은 조건을 따라야 합니다:

저작자표시. 귀하는 원저작자를 표시하여야 합니다.

비영리. 귀하는 이 저작물을 영리 목적으로 이용할 수 없습니다.

변경금지. 귀하는 이 저작물을 개작, 변형 또는 가공할 수 없습니다.

- 귀하는, 이 저작물의 재이용이나 배포의 경우, 이 저작물에 적용된 이용허락조건 을 명확하게 나타내어야 합니다.

- 저작권자로부터 별도의 허가를 받으면 이러한 조건들은 적용되지 않습니다.

저작권법에 따른 이용자의 권리는 위의 내용에 의하여 영향을 받지 않습니다.

이것은 이용허락규약(Legal Code)을 이해하기 쉽게 요약한 것입니다.

Disclaimer 🖃

# Ternary signaling 시스템의 구성과 구성에 따른 시뮬레이션 결과

2023년 2월

서울대학교 대학원 전기공학과 예 석 민

# Ternary signaling 시스템의 구성과 구성에 따른 시뮬레이션 결과

Introduction to Ternary signaling system and examination of simulation results

지도 교수 정 덕 균

이 논문을 공학석사 학위논문으로 제출함 2022년 11월

> 서울대학교 대학원 전기공학과 예 석 민

예 석 민의 공학석사 학위논문을 인준함 2022년 11월

위원장 김재하 (인)

부위원장 정 덕 균 (인)

위 원 최우석 (인)

# 초 록

디지털 시대의 도래 이후 공정의 집적화와 최적화로 인해 CMOS 공정과 binary signaling을 이용하여 수신기와 송신기 사이의 전송 속도는 계속해서 빨라져 왔다. 초기 시대에서의 문제는 공정이 속도를 얼마나지원해줄 수 있는지에 대한 것이었지만 현재는 상황이 다르다. 둘 사이를 연결하는 channel의 low-pass 특성으로 인해서 신호 손실이 많아지게 되었다. 이를 극복하기 위해 loss-less channel 특성을 가지는 optical을[1][2] 이용하는 방법이나 PAM4[3]같이 baud-rate를 절반으로 낮추는 대신 multi-level로 전송하는 방법이 도입되고 있다. Optical을 이용하는 경우 전기신호를 optical 신호로 전환하는 과정이 복잡하다는 단점이 있고 PAM4의 경우 지나치게 낮은 EYE height나 ISI에 의한 신호의 오염, 비대칭 EYE가 문제가 된다.

이에 본 논문에서는 Ternary signaling을 이용하여 비대칭 EYE를 극복하고 이를 통해 sampler 개수를 줄여서 저전력을 도모한다. 또한 ISI를 극복하기 위해 송신기와 수신기에 모두 equalizer를 사용해서 channel의 low-pass를 극복한다. 또한 ISI에 의한 오염을 최소화하기위해 4B3T encoding/decoding[4]을 이용하여 최적의 효율을 달성한다. 또한 공정의 미세화에 의해 커져가는 sampler의 offset을 극복하는 방법도 소개한다.

주요어 :Ternary, multi-level, equalizer, offset, modeling, high-speed

학 번:2009-23122

# 목 차

| CHAPTER 1 서론                      | 1   |

|-----------------------------------|-----|

| 1.1 배경지식                          | 1   |

| 1.2 논문의 구성                        | 2   |

|                                   |     |

| CHAPTER 2 고속 시리얼 링크               | 3   |

| 2.1 전통적인 방법                       | 3   |

| 2.1.2 바이너리 신호                     | 3   |

| 2.1.2 PAM4 신호                     | 4   |

| 2.2 Ternary 신호                    | 5   |

| 2.2.1 전통적인 방법과의 비교                | 5   |

| 2.2.2 Encoding/Decoding           | 7   |

| 2.2.3 48B36T 코딩                   | 8   |

|                                   |     |

| CHAPTER 3 전체 시스템 구조               | .12 |

| 3.1 발신기의 구성                       | 12  |

| 3.1.1 시스템 구조                      | 12  |

| 3.1.2 36:4 직렬 변환기                 | 13  |

| 3.1.3 3tap 피드포워드 이퀄라이저와 4:1 직렬변환기 | .14 |

| 3.1.4 Ternary driver              | 18  |

| 3.2 수신기의 구성                       | 20  |

| 3.2.1 시스템 구조                      | 20  |

| 3.2.2 연속 시간 선형 등화기                | 21  |

| 3.2.3 감지 증폭기의 구성                  | 22  |

| 3 2 4 Offset 취소기                  | 22  |

| 3.2.5 4tap 피드백 이퀄라이저의 구성         | 23     |

|----------------------------------|--------|

| 3.2.6 4:36 병렬 변환기                | 24     |

| 3.2.7 적응형 클락 생성                  | 25     |

| 3.2.8 적응형 피드백 이퀄라이저              | 26     |

| CHAPTER 4 시뮬레이션 결과               | 27     |

| 4.1 System verilog 모델링 시뮬레이션     | 27     |

| 4.1.1 송수신기 EYE diagram           | 27     |

| 4.1.2 Offset 취소기                 | 28     |

| 4.1.3 송수신기 적응형 피드백 이퀄라이저         | 28     |

| 4.2 아날로그 시뮬레이션                   | 30     |

| 4.2.1 3tap 피드포워드 이퀄라이저와 4:1 직렬변환 | フ] .30 |

| 4.2.2 Ternary driver             | 31     |

| 4.2.3 연속 시간 선형 등화기               | 32     |

| 4.2.4 감지 증폭기                     | 23     |

| 4.2.5 4tap 피드백 이퀄라이저             | 34     |

| CHAPTER 5 결론                     | 35     |

| 참고 문헌                            | 36     |

| Abatraat                         | 27     |

# 표 목차

| Table 1. 바이너리 신호와 PAM4, Ternary 신호의 | 비교9 |

|-------------------------------------|-----|

| Table 2. 4B3T encoding table        | 10  |

| Table 3. MMPD working truth table   | 28  |

| Table 4. DFE adaptation truth table | 29  |

# 그림 목차

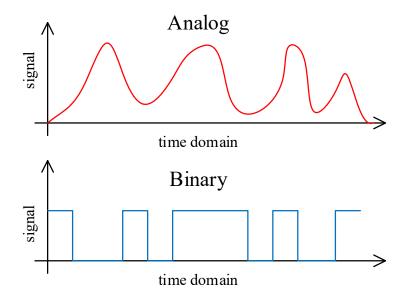

| Figure 1. 아날로그 신호와 바이너리 신호의 비교4                        |

|--------------------------------------------------------|

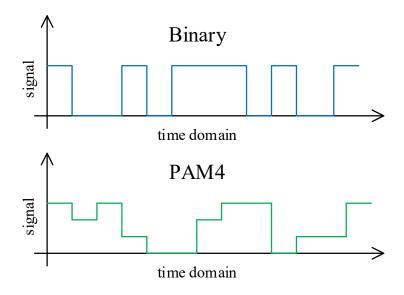

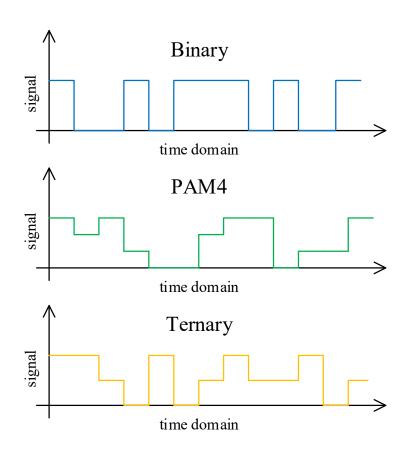

| Figure 2. 바이너리 신호와 PAM4 신호의 비교5                        |

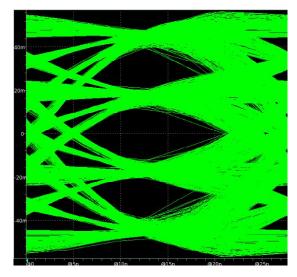

| Figure 3. PAM4 신호의 EYE diagram6                        |

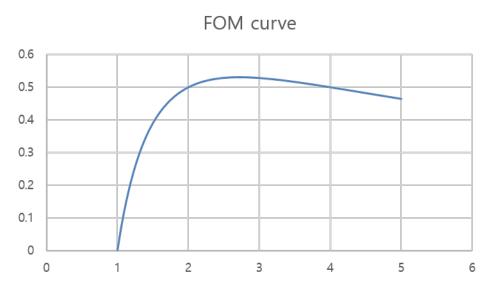

| Figure 4. Level 개수에 의한 FOM 비교7                         |

| Figure 5. 바이너리 신호와 PAM4, Ternary 신호의 비교 8              |

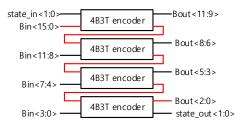

| Figure 6. Bottle of 16B12T encoder11                   |

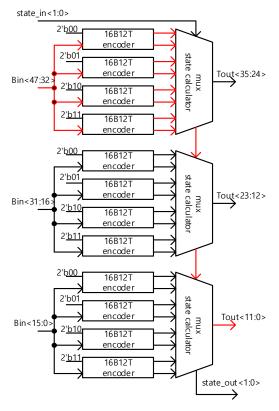

| Figure 7. Carry look ahead 16B12T encoder11            |

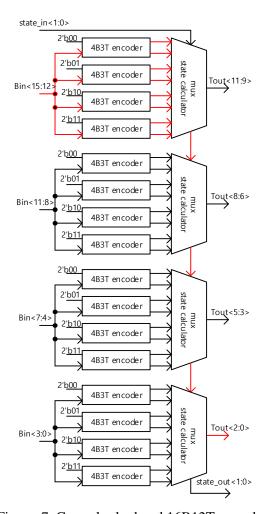

| Figure 8. Carry look ahead 48B36T encoder12            |

| Figure 9. Ternary transmitter system13                 |

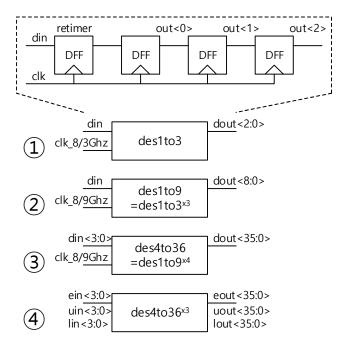

| Figure 10. 36:4 serializer15                           |

| Figure 11. 3:1 serializer15                            |

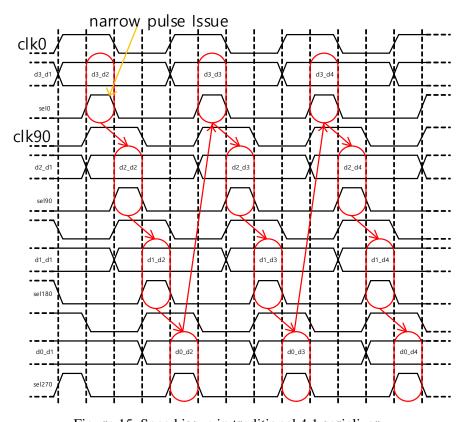

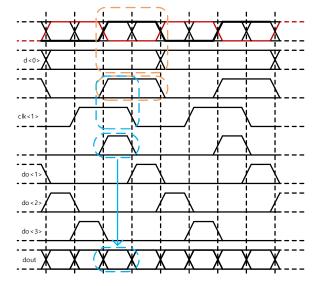

| Figure 12. 3:1 serializer timing diagram               |

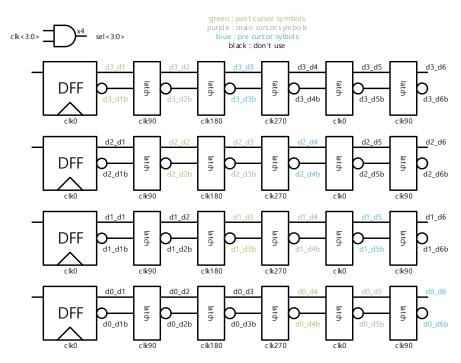

| Figure 13. Latch ladder for 4:1 serializing and FFE 17 |

|                                                        |

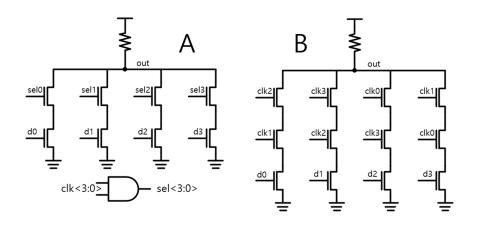

| Figure 14. Traditional CML 4:1 serializer            | 18 |

|------------------------------------------------------|----|

| Figure 15. Speed issue in traditional 4:1 serializer | 18 |

| Figure 16. Proposed pseudo CML 4:1 serializer        | 19 |

| Figure 17. Timing diagram of proposed circuit        | 19 |

| Figure 18. Working scheme at each state              | 20 |

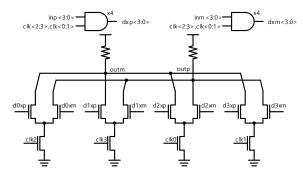

| Figure 19. Architectures of drivers                  | 21 |

| Figure 20. Channel modeling between transceiver      | 21 |

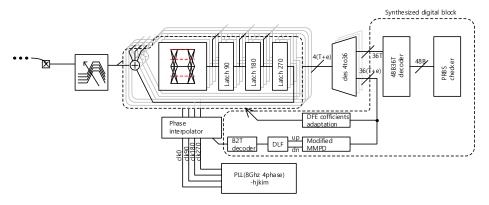

| Figure 21. Ternary receiver system                   | 22 |

| Figure 22. Cherry-hooper CTLE                        | 23 |

| Figure 23. Proposed Sens Amplifier                   | 24 |

| Figure 24. Summing scheme for DFE in one phase       | 25 |

| Figure 25. Architecture of 4:6 deserializer          | 26 |

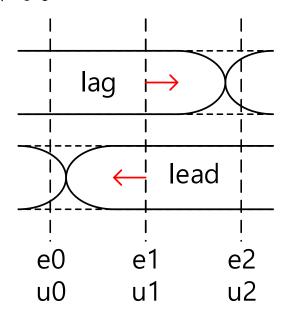

| Figure 26. MMPD working scheme                       | 27 |

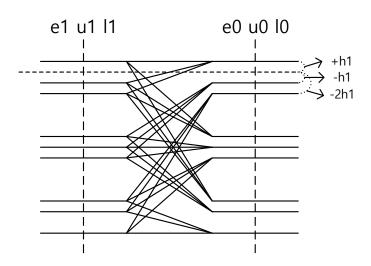

| Figure 27. DFE adaptation scheme                     | 28 |

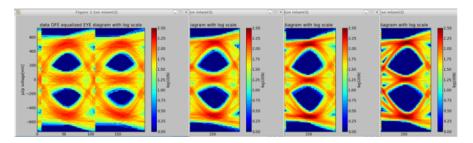

| Figure 28. EYE diagrams                              | 30 |

| Figure 29. EYE diagrams and data histograms 31            |

|-----------------------------------------------------------|

| Figure 30. Offset cancel scheme at each sampler 33        |

| Figure 31. Coefficients adaptation results 32             |

| Figure 32. High-speed 4:1 serializer timing waveform . 33 |

| Figure 33. Pre-driver with 2-tap FFE34                    |

| Figure 34. Main-driver simulation results 34              |

| Figure 35. CTLE frequency response                        |

| Figure 36. Sens amplifier working range36                 |

| Figure 37. DFE feed-back timing analysis                  |

# Chapter 1 서론

# 1.1 배경지식

최근 들어서 5G 시대를 맞아 유무선을 가리지 않고 data 소모량이 늘어나고 있다. 유선쪽에서는 USB나 DisplayPort, HDMI, Thunderbolt 등의 여러 규격이 점점고속화되고 있다. 또한 chip 내에서, chip-to-chip 통신에서의 속도는 더욱 고속화되고 있다. 이러한 상황에서 공정 내에서도 고속용 signal을 isolation시키기도 하고 chip-to-chip에서는 PCB설계에도 신경을 많이 쓰고 있다.

하지만 정도의 차이지 low-pass 특성을 가진 channel에 의해서 발생하는 ISI는 막을 수 없어서 아무리 equalizer로 극복을 하려 해도 binary 신호로는 점점 감당하기 힘들어지고 있는 상황이다. 이에 multi-signaling이 활발하게 연구 중이다.

본 논문에서는 Ternary system을 통해 PAM4의 약점을 극복하고 적절한 equalizing 방법과 효과적인 analog 설계 방법을 소개하고 이를 simulation으로 검증하겠다.

# 1.2 논문의 구성

Chapter 2에서는 먼저 전통적인 signaling 방법인 analog 신호와 binary 신호의 차이를 먼저 설명한다. 이에 현재 활발하게 연구중인 multi-signaling의 대표인 PAM4 signaling도 소개한다. 이어서 본 논문에서 다루고 있는 Ternary signaling의 장점과 4B3T encoding/decoding도 함께 소개한다. 또한 이 encoding을 수행하기 위해 digital domain에서 어떻게 구성했는지도 소개하겠다.

Chapter 3에서는 수신기와 발신기의 전체적인 구성을 설명한다. 송신기에서는 1Ghz로 동작하는 digital에서 analog로 넘어가는 36:4 serializer를 설계한 방식을 소개하고 고속으로 동작하는 4:1 serializer를 제안한다. 이런 4:1 serializer에 어떻게 FFE를 도입할 수 있는지 설명한다. 송신단에서는 마지막 analog block에 해당하는 pre-driver와 main-driver의 구성도 함께 보여준다. 수신기에서는 equalizing과 offset cancel을 수행하기 위한 CTLE를 먼저 소개하고 이어서 offset cancel과 multilevel sampling, DFE를 동시에 수행할 수 있는 sampler 구조를 제안한다. 이후 4:36 deserializer를 소개하고 이후 digital에서 phase adaptation과 DFE adaptation 방법론을 소개한다.

Chapter 4에서는 system verilog과 python을 이용한 modeling simulation 결과와 이를 바탕으로 구성된 analog block들의 설계 결과와 성능을 평가한다.

Chapter 5에서는 본 논문의 결과를 요약하고 평가한다.

# Chapter 2 고속 시리얼 링크

# 2.1 전통적인 방법

## 2.1.2 바이너리 신호

바이너리 신호는 analog 시대에서 digital 세대로 넘어오면서 가장 보편적이 된고속 송수신 방식이다. 기존의 analog 방식은 구성 방식이 쉽고 직관적이지만 time domain이나 signal domain 모두 continuous하기 때문에 각종 잡음이 signal quality에 크게 영향을 미치게 된다. 하지만 binary signal의 경우 time domain은 어쩔 수 없지만 Figure 1.같이 signal domain을 digitize해서 단순화했다. 예를 들어 0.7이라는 신호가 들어와야 된다고 가정했을 때 잡음에 의해서 0.68이나 0.72 등으로 잡음이 들어올 수 있다. 이 경우에 analog에서는 잡음으로 처리되지만 binary system에서는 0.5보다 높기 때문에 작은 잡음에 의한 효과에 상관 없이 1로 판단하게 된다.

그리고 복잡한 연산이 많아지면서 time domain 또한 digitize해서 combinational logic과 sequential logic으로 구성된 digital로 돌아가는 회로들이 급격하게 늘어났다. 이러한 system과 함께 동작하기 위해서 기존의 analog signaling의 경우 다단계 ADC/DAC가 필요했는데 binary signaling는 제일 단순한 ADC/DAC에 해당하기때문에 설계의 용이함, 저전력을 달성할 수 있고 이로 인해 고속 통신을 가능하게 한다.

Figure 1. 아날로그 신호와 바이너리 신호의 비교

#### 2.1.2 PAM4 신호

최근에 들어서 초고속 통신을 사용할 때 channel 환경 등에 의한 bandwidth가 현격하게 부족하게 되었다. 이로 인해 사용되는 4PAM은 Figure 2.같이 multi-level을 이용하여 binary와 같은 bandwidth를 이용했을 때 두 배의 전송 속도를 달성할 수 있다. 이 구조는 결정값이 2에서 4로 정확히 두 배이기 때문에 100%의 압축률을 달성할 수 있다.

하지만 같은 signal swing을 가진다고 했을 때 EYE height가 1/3밖에 되지 않기때문에 analog 회로가 가지고 있던 노이즈에 binary에 비해 3배의 민감한 특성을 가지기도 한다.

또한 Figure 3.같이 differential로 구성된 system이라도 가운데 EYE 높이와 위아래의 EYE 높이가 다를 수 밖에 없어서 이를 조정하기 위한 추가적인 sampler가 설계에 추가된다. 이에 따라서 전력소모량도 늘어날 수밖에 없다.

Figure 2. 바이너리 신호와 PAM4 신호의 비교

Figure 3. PAM4 신호의 EYE diagram

# 2.2 Ternary 신호

### 2.2.1 전통적인 방법과의 비교

Figure 4. Level 개수에 의한 FOM 비교

이와 같이 3개의 결정값을 갖는 Ternary 신호는 Figure 4.같이 기존에 사용하던 2개의 결정값을 갖는 binary와 4개의 결정값을 갖는 PAM4의 중간에 해당한다. Binary나 PAM4는 정확히 같은 FOM을 가져서 100%의 압축률을 달성할 수 있지만 Ternary는 이론상으로 더 높은 FOM을 encoding/decoding에 쓸 수 있다.

그리고 하드웨어에서의 이점도 PAM4에서보다 많다. 수신단에서 최고의 효율을을 달성하기 위해서는 Figure 3.같은 가운데 EYE와 위아래 EYE의 높이가 같아야야 최선의 BER을 가질 수 있다. 이를 달성하기 위해서는 송신단에서 MSB driver driver와 LSB driver가 정확히 2배를 달성해야 되는데 공정상의 오차나 bias값의 6

오차 등으로 인해서 정확하게 같은 높이를 달성하기는 힘들다. 또한 이러한 이유 유로 인해서 정확한 sampling 위치를 찾기 위해서는 결정값을 구분 짓기 위한 추 추가적인 2개의 sampler가 더 필요하게 된다. 이는 실제 값을 결정하기 위한 3개 개의 sampler까지 합치면 최소 5개의 sampler가 필요하게 되는데 이는 power 측 측면에서도 면적 측면에서도 많은 부담을 주게 된다.

반면 Ternary는 MSB/LSB로 이뤄지지 않은 symmetric한 구조의 driver를 사용할 수 있으므로 각종 오차에서 PAM4보다 설계가 훨씬 용이하다. 그뿐만 아니라 각종 오차가 있다고 하더라도 결국 출력으로 나타나는 EYE는 differential이므로 symmetric하게 출력된다. 이는 수신단에서 3개의 sampler로 구성을 가능하게 하여 power 측면에서도 이득을 가져올 수 있다.

Figure 5. 바이너리 신호와 PAM4, Ternary 신호의 비교

### 2.2.2 Encoding/Decoding

Line coding을 통한 최대의 장점은 DC balancing이며 이를 위해서는 최대 run-

length가 짧은 것이 좋고 그를 위해서는 transition이 잦을수록 좋다. 이에 표와 같이 encoding방법을 비교해보았다.

| Transition num | 3T       | 4T       | 5T        |  |

|----------------|----------|----------|-----------|--|

| All            | 8(3B3T)  | 16(4B4T) | 32(5B5T)  |  |

| +All-1         | 20(4B3T) | 48(5B4T) | 112(6B5T) |  |

| +All-2         | 26(5B3T) | 72(6B4T) | 192(7B5T) |  |

Table 1. 바이너리 신호와 PAM4, Ternary 신호의 비교

모든 symbol 사이에 transition이 있는 경우 binary에서 ternary로 압축했을 때전송 속도에서 이득을 볼 수 없으므로 고려할 수 없다. 더 나아가 binary 1bit이 늘어날 때마다 값이 기하급수적으로 늘어나므로 encoding decoding에 자원을 많이쏟아야 한다. 이에 실질적인 synthesize/PNR도 난이도가 올라가고 면적도 커진다. 이에 5T, 6T도 아무리 압축 효율을 양보해서 6B5T나 7B6T라 하더라도 얻어가는속도 이득에 비해 내어주는 하드웨어에서의 부담이 더 큰 문제가 된다.

이에 고려해볼 만한 encoding은 4B3T나 6B4T가 남게 되는데 뒤에 후술할 테이블을 기반으로 6B4T를 꾸며보면 DC balancing을 최대 -2에서 +2로 꾸며야 된다. 그런데 +0 state가 16개, ±1이 16개, ±2도 16개라서 총 16개 state가 모자라게 되어서 DC balance도 맞출 수가 없고 이에 transition density 도 4B3T에 비해 확보할수 없게 된다.

#### 2.2.3 48B36T 코딩

| Input |        | Accumulated DC offset |      |  |       |

|-------|--------|-----------------------|------|--|-------|

| Hex   | Binary | -1.5                  | +1.5 |  |       |

| 0     | 0000   | +0+(+2) 0-0(-1)       |      |  |       |

| 1     | 0001   | 0-+(+0)               |      |  |       |

| 2     | 0010   | +-0(+0)               |      |  |       |

| 3     | 0011   | 00+(+1)0(-2)          |      |  | 0(-2) |

| 4     | 0100   | -+0(+0)               |      |  |       |

| 5     | 0101   | -++(+1)+(-1)          |      |  |       |

| 6     | 0110   | -++(+1)+(-1)          |      |  | (-1)  |

| 7     | 0111   | -0+(+0)               |      |  |       |

| 8 | 1000 | +00(+1)         |  |           | 0—(-2)  |      |  |

|---|------|-----------------|--|-----------|---------|------|--|

| 9 | 1001 | +-+(+1)         |  |           | (-3)    |      |  |

| A | 1010 | ++-(+1) +(      |  | ++-(+1) + |         | (-1) |  |

| В | 1011 | +0-(+0)         |  |           | +0-(+0) |      |  |

| С | 1100 | +++(+3) -+-(-1) |  |           |         |      |  |

| D | 1101 | 0+0(+1) -0-(-2) |  |           | -0-(-2) |      |  |

| Е | 1110 | 0+-(+0)         |  |           |         |      |  |

| F | 1111 | ++0(+2) 00-(-1) |  |           |         |      |  |

Table 2. 4B3T encoding table

위 테이블은 MMS43 4B3T table이다[5]. 총 4개의 state 중 한 symbol당 DC 정보 값이 0인 6가지 중립 code 외의 DC 정보를 가지는 code들을 각 binary code에 두 개의 ternary code를 matching시켜서 총 4개의 state, 즉 ±1.5 범위 내에서 DC balancing을 맞춘다. 이에 따른 NEXT 성능이나 ISI reduction 성능도 PAM4(2B1Q) 비슷하게 측정되었음에도 높은 EYE height를 가져갈 수 있다.

이 encoding/decoding을 고속 통신을 담당할 analog domain으로 구성하긴 어렵다. 따라서 digital에서 처리하기 위해 병렬 처리를 해야하는데 단순한 병렬 처리로는 불가능하다. 이 전 state에 따라서 출력값이 달라지기 때문이다. Figure 6.는 16B12T를 병렬 처리했을 때의 예시이다. 각 encoder가 이전 encoder의 state를 알아야 되기 때문에 state machine path가 timing critical path가 된다. 이를 해결하기위해서 Figure 7.같이 carry look ahead 구조를 이용해 16B12T를 구성하였다.

Figure 6. Bottle of 16B12T encoder

Figure 7. Carry look ahead 16B12T encoder

이렇게 구성된 16B12T를 다시 carry look ahead 구조를 이용하여 3번 병렬화를 구성하면 48B36T encoder를 구성할 수 있다.

Figure 8. Carry look ahead 48B36T encoder

수신부 단에서는 3자리씩 묶여 있는 ternary 신호의 경계가 어딘지 알 수 없으므로 synchro pattern이 필요하다. MMS43에서는 000 이외에는 모든 codeword들이 binary에 1:1 혹은 2:1로 할당이 되어 있기 때문에 한 개의 codeword로는 synchro pattern을 생성할 수 없다. 따라서 최소 두 개의 codeword를 붙여서 pattern을 만들어야 되는데 시스템의 특성상 DC balance를 최대한 살려서는 synchro pattern을 만들 수 없어서 본 system에서는 /+++/++0/을 synchro pattern으로 사용하고 있다.

# Chapter 3 전체 시스템 구조

# 3.1 발신기의 구성

#### 3.1.1 시스템 구조

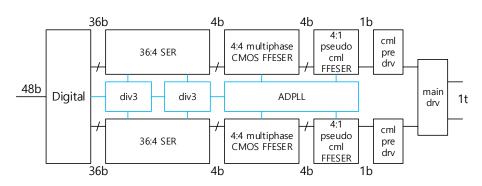

Figure 9. Ternary transmitter system

Figure 9.은 Ternary transmitter의 전체적인 구조도 이다. ADPLL은 4-phase 8Ghz로 동작하고, 삼성 40n공정에서 지원하는 최대 synthesize/PNR 속도가 1Ghz이기때문에 digital 회로는 8/9Ghz를 사용하기로 한다. 이를 위해서 8/3Ghz도 사용해서회로를 단순화하기로 한다.

송신단에서 보내고자 하는 data는 48bit 병렬 신호로 들어오게 되며 본 시스템에서는 test를 위해 PRBS15를 48bit으로 병렬화해서 data를 생성하여 48B36T encoding을 하게 된다. PAM4의 경우 2bit을 한 unit으로 했을 때 상위 bit을 MSB, 하위 bit을 LSB로 mapping을 하게 되는데 Ternary에서는 +를 2'b11, 0을 2'b01, -를 2'b00으로 mapping을 했을 때 상위 bit과 하위 bit의 가중치의 차이가 없기 때문에 상위 bit을 upper bit, 하위 bit을 lower bit으로 정의하겠다.

따라서 upper bit과 lower bit은 각각의 lane에 따라서 serializing을 하게 된다. 8/9Ghz에서 8Ghz까지 36:4 serializer를 먼저 거치게 된다. 이 36:4 serializer는 phase와 상관 없이 동작하기 때문에 전통적인 방법으로 수행이 가능하다.

다음 4:1 serializer는 4-phase로 동작하기 때문에 latch-base로 in-phase clock에 data를 mixing하는 역할을 한다. 여기서 FFE를 위한 data를 생성하기 위해 2개의

latch를 더 사용한다. 이 mixing된 data들은 각 cursor별로 pre-driver를 거치게 되고 마지막 main driver에서 upper lane의 data와 lower lane의 data가 mixing이 되어 출력으로 나가게 된다.

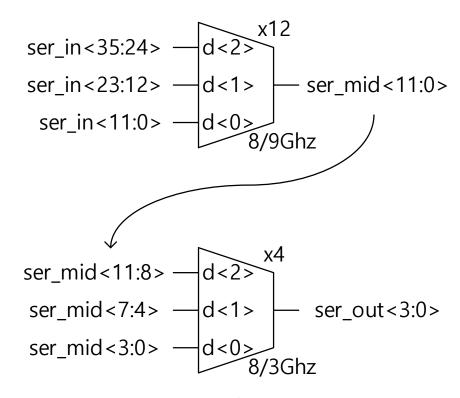

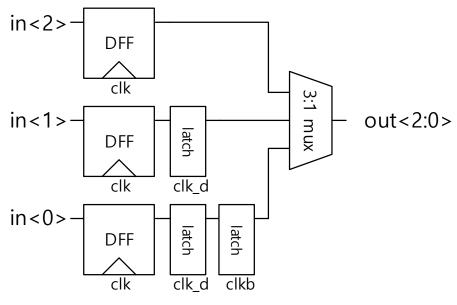

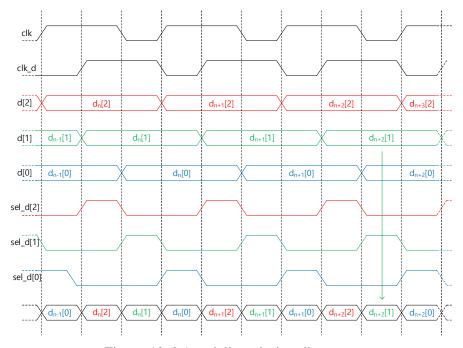

### 3.1.2 36:4 직렬 변환기

이 block은 analog system 중 제일 느리게 동작하기 때문에 fully CMOS로 구성되며 Figure 10.같이 8/9Ghz에 동작하는 3:1 clocked mux 12개와 8/3Ghz에 동작하는 3:1 clocked mux 4개로 이뤄져 있다. 기본 유닛인 3:1 clocked mux는 timing 조정을 위한 DFF와 latch, timing mixer로 구성되며 그 구조는 Figure 11.과 같다. 실제 동작하는 타이밍은 Figure 12.와 같다.

Figure 10. 36:4 serializer

Figure 11. 3:1 serializer

Figure 12. 3:1 serializer timing diagram

# 3.1.3 3tap 피드포워드 이퀄라이저와 4:1 직렬 변환기

고속 serial link에서는 channel의 low-pass filter 특성으로 인해 equalizing이 필수이다. 이 equalizing은 송신기단에서는 그 channel 특성을 특정할 수 없기 때문에 수신기에서 adaptive하게 처리하는 게 바람직하다. 하지만 loss가 많은 channel에서는 transmitter도 선제적으로 equalizing을 같이 부담해줄 수 있다. 이 시스템에

서는 main cursor를 중심으로 post cursor와 pre cursor를 이용한 FFE를 구성했다.

Figure 13. Latch ladder for 4:1 serializing and FFE

우선 36:4 SER에서 넘어온 data들을 4-phase clock 중 하나로 DFF를 이용해 retiming을 한다. 그 다음에 latch들을 통해서 각 cursor별로 serializing하기 위해각 clock에 맞게 retiming을 다시 진행한다. 이 다음은 4-phase에 맞게 data를 다음 단으로 넘겨줘야 되는데 CMOS 구조로는 32Gbps의 속도를 달성할 수 없었다. 이에 RTL구조로 muxing을 진행했지만 Figure 14.의 A 같은 traditional한 구조에서는 Figure 15.같이 selection 신호가 제일 빠르게 되고, rise/fall timing에 다른 data의 간섭이 일어나서 속도를 달성할 수 없었다. 그 selection 신호의 속도를 만들어 내는 gate를 피하기 위해 Figure 14.의 B와 같은 구조로 진행할 경우 stack된 NMOS의 숫자가 많아서 속도 달성에 실패하였다. 또한 근본적으로 이런 구조는 NMOS사이의 node에서 연산 중에 floating node가 생기게 되며 이로 인해 ISI가 발생하는 문제도 있다.

Figure 14. Traditional CML 4:1 serializer

Figure 15. Speed issue in traditional 4:1 serializer

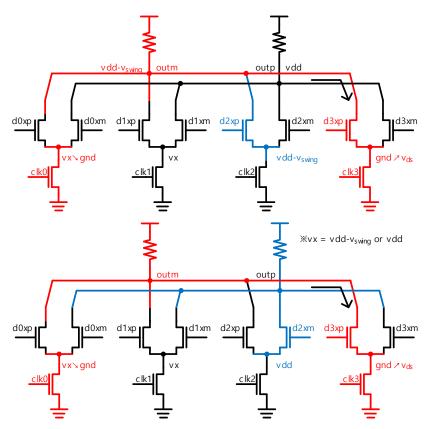

이에 Figure 16. 같은 구조로 muxing을 구성했다. Selection 신호를 만들었던 clock 중 하나를 data랑 AND gate로 합치면 dxp<3:0>, dxm<3:0>이라는 신호를 만들어 낼 수 있다. Figure 17.같이 이 신호의 bandwidth는 clock의 bandwidth와 같아지면서 narrow pulse width의 rise/fall time 문제를 피해갈 수 있다. 또한 Figure 17. 같이 dxp, dxm는 clocked gating 신호여서 clock보다 늦게 도착하게 되므로 clock을 selection 신호로 쓸 수 있다. 이 방식을 이용하면 single-ended 구조를 극복하고 differential 구조를 달성할 수 있다.

Figure 16. Proposed pseudo CML 4:1 serializer

Figure 17. Timing diagram of proposed circuit

Figure 16. 같은 구조로 회로를 구성하게 되면 Figure 18.같이 각 common node 와 floating을 방지할 수 있다.

Figure 18. Working scheme at each state

clk0과 clk3가 vdd가 되었을 때 clk1과 clk2, d0xpm, d1xpm는 0으로 각 Figure 17.같이 전류가 흐르게 된다. d0xpm은 모두 0이므로 첫 번째 common node는 0으로 잡힌다. 네 번째 노드는 differential에 따라 저항 load에 전류에 흘려줘서 outp, outm은 각각 vdd나 vdd-swing이 된다. 이에 세 번째 node는 d2xpm의 polarity에 따라서 vdd나 vdd-vswing이 되며 그 값이 두 번째 node의 vx값이 된다. vx값이 floating값이라고 생각할 수 있는데 다음 phase에서 gnd로 초기화된다.

#### 3.1.4 Ternary driver

앞에서 서술했듯이 4:1 mux는 current source를 이용한 완벽한 RTL 구조가 아니다. 따라서 바로 main driver에 보내기엔 swing의 형태가 바람직하지 않을뿐더러 4:1 mux의 out node은 load cap에 의해 속도 열화가 심각하다. 또한 FFE를 포함시키기 위해서는 각 cursor를 mixing하기 위한 역할을 위한 pre-driver가 필요하며 Figure 19.같이 구성했다. 이 두 개의 pre-driver의 출력까지는 binary로 작동하지만 Figure 19.같이 구성된 main-driver부터는 ternary로 동작하게 된다. main-drive

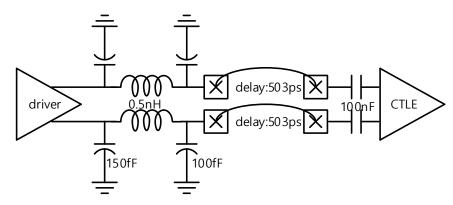

# 의 load는 Figure 20.같이 구성되었다.

Figure 19. Architectures of drivers

Figure 20. Channel modeling between transceiver

# 3.2 수신기의 구성

## 3.2.1 시스템 구조

Figure 21. Ternary receiver system

Figure 21.은 Ternary receiver의 전체적인 구조도이다. Transmitter에서 differential로 channel을 통과해 들어온 신호는 우선적으로 CTLE(continuous Time Linear Equalizer)를 거쳐서 sampler들을 거치게 된다. sampler들은 ADPLL에서 PI(Phase Interpolator)를 거쳐서 나온 4-phase 8Ghz clock으로 이뤄지며 각 phase당 3개의 sampler가 사용된다. 각각의 sampler들은 4tap DFE(Direct Feedback Equalizer)를 구성하기 위해 latch ladder를 가지고 있으며 그 결과는 4:36 deserializer를 통해 digital domain으로 넘어가게 된다.

Digital domain에서는 synchro pattern checker와 48B36T decoder를 거쳐서 PRBS pattern을 체크하여 신호의 복원 성공여부를 판단한다. 또한 정확한 sampling timing을 위해 PD(phase detector)와 DLF(Digital Loop Filter), B2T(Binary to Thermometer) decoder를 통해 PI를 컨트롤하게 되며, 다른 한편으로는 DFE의 동작을 위해 4-tap post cursor coefficients값을 계산해서 sampler들에게 전달해주게된다.

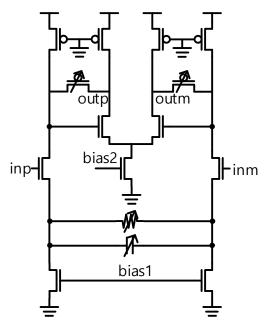

## 3.2.2 연속 시간 선형 등화기

Figure 22. Cherry-hooper CTLE

본 논문에서 사용되는 CTLE는 Figure 22.와 같은 전통적인 구조의 cherry-hooper 구조로 설계되었다. 저항들을 PMOS로 구성하고 있으며 load 저항은 PMOS gate를 gnd에 붙여서 고정값으로 작동하게 만들었으며 feed-back 저항은 PMOS gate 전압을 이용해 외부에서 조절할 수 있게 만들었다. RC bank 역시 DC gain과 zero를 외부에서 조절할 수 있게 구성하였으며 current source들도 조절 가능하게 구성하였다.

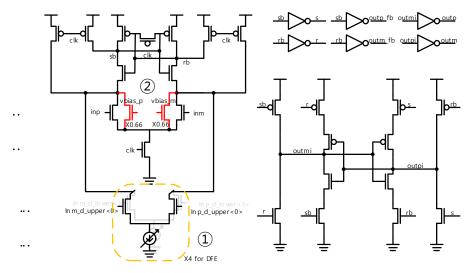

### 3.2.3 감지 증폭기의 구성

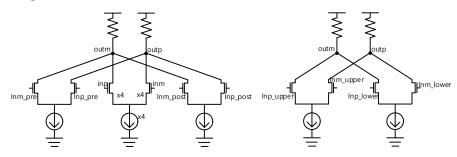

Figure 23. Proposed Sens Amplifier

SA(Sense Amplifier)한 개의 유닛은 위 Figure 23.같이 구성되었다. 기본적으로 strong arm의 구조를 가지고 있으며 동적으로 4-tap DFE 동작을 위한 summer가 differential로 추가되어 있다(①). 또한 digital domain에서 sampling level과 DFE연산을 위한 bias shifter 또한 추가 되어 있다(②). Figure 21.에서 보듯이 한 phase당 error sampler, upper EYE sampler, lower EYE sampler 3개가 들어가 있다. Error sampler의 sampling threshold를 digital에서 adaptive하게 결정되면 upper EYE sampler는 그 절반의 bias를 인가하고 lower EYE sampler는 upper EYE sampler와 반대방향의 bias를 인가하여 sampling하여 다음 latch ladder로 전달하게 된다.

#### 3.2.4 Offset 취소기

Figure 23.처럼 생긴 SA의 경우 미세한 신호를 증폭해야 되는데 입력 단에 해당하는 두 NMOS는 공정상의 문제로 성능이 달라질 수 있다. 이러한 경우에는 목적하는 값과 도출되는 값이 달라질 수 있다. 이 상황은 BER을 악화시키는 결과를만들어 내기 때문에 바람직하지 않다. 이에 본 논문에서는 이러한 mismatch가 일어나는 경우를 상정하여 offset 취소기를 설계하였다.

이 offset을 감지하기 위해서는 입력 양단에 같은 전압을 인가하여 결과값을 관찰하면 된다. 한쪽이 강하거나 약하면 sensing한 값이 한쪽으로 몰리게 된다. 이에 offset cancel phase에서는 Figure 22.의 등화기의 current source bias값을 0으로

주어서 SA에 인가되는 전압을 VDD값으로 통일한다. 이에 나오는 결과를 디지털에서 1/0의 빈도를 토대로 Figure 23.의 bias shifter(②)에 추가적으로 bias를 인가하여 공정상의 offset을 극복한다.

## 3.2.5 4tap 피드백 이퀄라이저의 구성

Figure 24. Summing scheme for DFE in one phase

4-phase 중 한 개의 set는 Figure 24.같이 구성된다. T는 upper, lower EYE sampling 결과를 묶어서 Ternary 신호에 해당하며 e는 error sampling 결과를 뜻한다. Error sampling 결과는 동적 DFE 동작과는 상관없이 digital 연산에만 이용되므로 latch ladder를 통과하지 않고 바로 descrializer로 전달된다.

총 4-tap DFE를 위해서는 1, 2, 3번째 cursor는 다른 phase set에서 전달 받게 되며 마지막 cursor는 자신의 결과이므로 Figure 24.같이 구성된다. 1<sup>st</sup> cursor로 쓰이는 값은 StrongArm latch까지 거치면 timing이 부족하므로 Figure 23.에서 outp\_fb, outm\_fb로 StrongArm 결과만 buffering해서 다음 phase로 넘겨주게 된다. 이러한 방법은 낮은 속도에서는 StrongArm이 reset 상태인 체로 다음 phase로 넘어가기때문에 쓸 수 없지만 고속에서는 reset 상태 이전에 다음 phase에서 sampling이 이루어지기 때문에 사용할 수 있다. 즉 이 set가 0°에 sampling이 일어난다고 했을 때 처음 결과는 90°, 첫 번째 latch 결과는 180°, 두 번째 latch 결과는 270°, 세 번째 latch 결과는 자기 자신에게 feedback을 하도록 구성하고 있다.

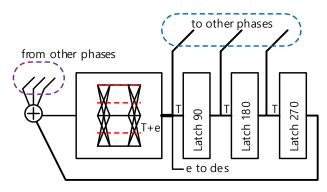

### 3.2.6 4:36 병렬 변환기

Figure 25. Architecture of 4:6 deserializer

Deserializer는 Figure 25.같이 구성된다. Clock domain이 넘어갈 때마다 metastability를 일으킬 수 있기 때문에 첫 DFF는 retimer로 동작한 다음 data를 clock에 따라 미뤄서 다음 clock domain에서 sampling 할 수 있게 한다(①). 그다음으로 clock domain을 낮추고(②) phase를 합친 다음(③) error sampler, upper EYE sampler, lower EYE sampler의 deserializer를 합친다(④). 이 결과를 digital domain으로 넘겨서 PRBS checking과 sampling phase align, DFE coefficient 계산을 수행하게 한다.

# 3.2.7 적응형 클락 생성

Figure 26. MMPD working scheme

이 system에는 Figure 26.같이 phase를 조절하는 MMPD가 이용된다. Error sampler는 upper sampler보다 높은 bias값을 가지기 때문에 adaptive loop 내에서 lower sampler의 값은 연산에 상관없다. Sampling phase 조절에 대한 조건은 표와 같다.

| condition  | u0 | u1 | u2 | e0 | e1 | e3 |

|------------|----|----|----|----|----|----|

| Phase lag  | 1  | 1  | 0  | 1  | 0  | X  |

| Phase lead | 0  | 1  | 1  | X  | 0  | 1  |

Table 3. MMPD working truth table

이렇게 생성된 phase lead/lag 정보를 DLF를 거쳐서 sampling clock의 phase를 조절하게 된다.

## 3.2.8 적응형 피드백 이퀄라이저

Figure 27. DFE adaptation scheme

위 Figure 27.은 Ternary system에서 ISI(Inter Symbol Interference) 중 첫 번째 post cursor만 있다고 가정했을 때 wave form이다. +는 center에서  $h_1$ 만큼 위로, -는 center에서  $h_1$ 만큼 아래로, 0은 center로 가게 된다. 이런 경우  $h_1$ 을 비롯하여 다른 coefficient들을 조절하게 되는 방법은 표와 같다.

| ux | ex | u0 | 10 | h <sub>x</sub> coefficient |

|----|----|----|----|----------------------------|

| 1  | 0  | 1  | 1  | up                         |

| 1  | 1  | 1  | 1  | down                       |

| 1  | 0  | 0  | 1  | down                       |

| 1  | 1  | 0  | 1  | up                         |

| 1  | 0  | 0  | 0  | down x2                    |

| 1  | 1  | 0  | 0  | up x2                      |

Table 4. DFE adaptation truth table

x에 1을 넣으면 첫 번째 post cursor이고 그 외의 나머지 post cursor들도 위 표와 같이 SS-LMS로 adaptation을 할 수 있다. 이 결과를 DLF를 거쳐서 이를 DFE sampler에 전달해 주게 된다.

# Chapter 4 시뮬레이션 결과

# 4.1 System Verilog 모델링 시뮬레이션

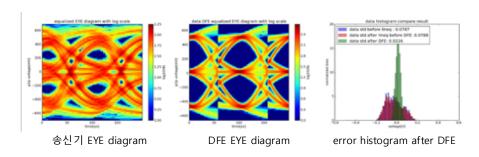

## 4.1.1 송수신기 EYE diagram

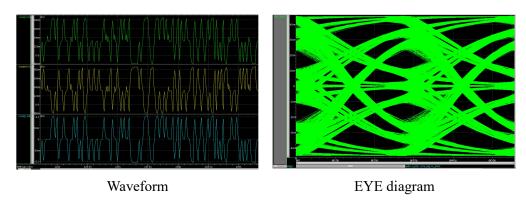

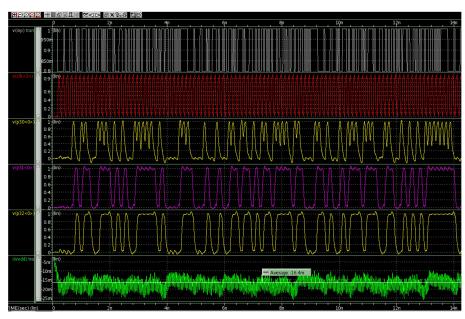

Figure 28. EYE diagrams

위 EYE diagram들은 DFE tap 수를 가늠하기 위한 simulation이다. 제일 앞이 1tap만 켰을 때며 마지막이 4tap을 켰을 때다. 각 자료는 system verilog의 test bench에서 sampling timing에 analog값을 출력으로 받아서 python으로 갈무리하였다. 각 sampler가 성공적으로 feedback을 받을 수 있다는 가정 하에 modeling 상으로 half UI를 반영하여 analog값을 출력 받았다. 아래 EYE diagram들에서는 DFE의 4-tap을 썼을 때 input과 output 그리고 edge sampler의 data histogram을 비교할수 있다.

Figure 29. EYE diagrams and data histograms

## 4.1.2 Offset 취소기

Figure 30. Offset cancel scheme at each sampler

4 phase sampler마다 각기 다른 정도의 가상의 offset을 가했을 때 각 sampler마다 각기 다른 tracing을 하는 simulation 결과를 나타낸 것이 Figure 30.이다. 이는 각 sampler의 모든 input에 vdd값이 들어가 있어서 sampling timing이나 phase는 위 과정을 수행하는데 있어서 변수가 되지 않는다. 이 과정이 끝나고 유효한 input signal이 인가되기 시작하기 전에 각 sampler마다 각기 다른 offset cancel code를 기억해 두게 된다. 그 이후 MMPD랑 DFE를 digital에서 연산해서 sampling에 반영할 때 기억해 두었던 code를 추가해서 반영하게 된다.

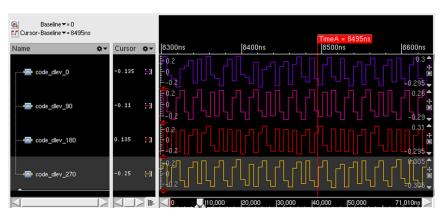

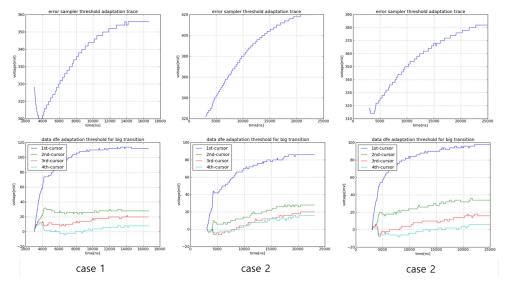

# 4.1.3 송수신기 적응형 피드백 이퀄라이저

Figure 31. Coefficients adaptation results

이 또한 system verilog상 test bench에서 code값을 file로 출력을 받아서 python으로 마무리하였다. 각기 다른 channel 환경에서 simulation한 결과이며 윗줄은 error sampler의 threshold값이며 아랫줄은 각 channel에서 DFE adaptation을 동작시켰을 때 coefficient를 찾아가는 과정이다. 각 case마다 사정은 다르지만 성공적으로 수렴하는 모습을 확인할 수 있다.

# 4.2 아날로그 시뮬레이션

# 4.2.1 3tap 피드포워드 이퀄라이저와 4:1 직렬변환기

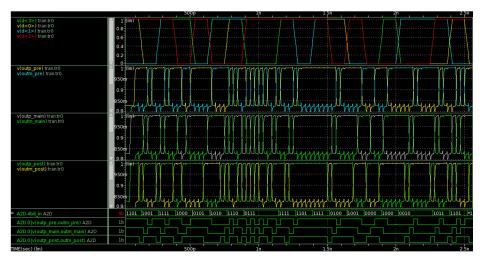

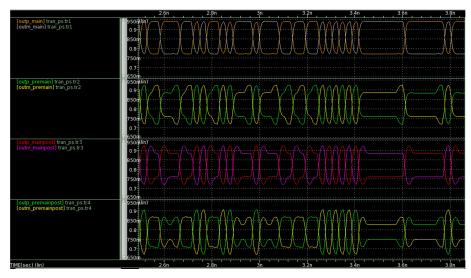

Figure 32. High-speed 4:1 serializer timing waveform

Figure 16.과 같이 회로를 구성했을 경우 resistor load를 사용하므로 출력 node가 완전히 pull-down에 들어가지 못한다. 하지만 이 고속 환경에서는 CMOS level로 구성이 불가능하기도 하며, 전력 소모에서도 이득을 가져갈 수 있다. 또한 다음 회로인 pre-driver, main-driver도 RTL 구조를 가지므로 Figure 32.와 같은 결과만으로도 driver를 구동시키기 충분하다. Pull down level에서의 잡음은 pre-driver 입력 cap과 출력 cap 등에 의해서 사라지게 된다. 또한 modeling 결과를 통해 검증된 latch ladder를 통해 FFE를 구성했을 때 정확히 동작함을 확인할 수 있다. 정확한 동작 정보는 다음 장에서 다루겠다.

#### 4.2.2 Ternary driver

Figure 33. Pre-driver with 2-tap FFE

위 waveform은 pre-driver에서 위에서부터 main cursor만 켰을 때 pre cursor만 켰을 때 post cursor만 켰을 때 마지막은 둘 다 켰을 때이다. 각 커서의 크기는 current source의 조절로 가능하게 만들었으며 upper lane과 lower lane 각각의 끝에 위치해서 main driver를 driving한다.

Figure 34. Main-driver simulation results

두 lane의 pre driver를 main cursor만을 켜놓은 상태에서 나타난 waveform과 EYE diagram이다. outp와 outm 각각만 보면 조금 흔들리는 모습을 보이지만 differential로 봤을 때는 균형적인 모습을 보이고 있다.

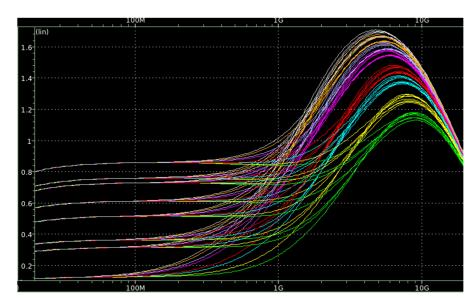

## 4.2.3 연속 시간 선형 등화기

Figure 35. CTLE frequency response

Figure 35.는 Figure 22.에서와 같이 boosting을 위한 9단계의 C값 조절과 degeneration을 위한 9단계의 R값 조절로 구성되어 있다. 이에 각 종류마다 주파수 응답특성을 그려보았다. 8Ghz에서 최대 응답특성을 보여야 하지만 부하저항으로 인한 pole 특성 때문에 과하게 zero 위치를 저주파로 설정하면 최대 응답특성의 위치가 8Ghz보다 저주파로 이동하는 특성을 보인다. 본 논문에서는 이 응답특성을 기반으로 matlab을 이용하여[6] system verilog로 modeling하여 수동으로 RC 값을 조절하여 사용한다.

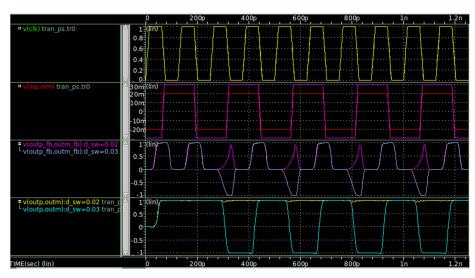

## 4.2.4 감지 증폭기

Figure 36. Sens amplifier working range

Figure 36.은 8Ghz에서 동작하는 SA의 시뮬레이션 결과이다. DFE에서 첫 번째 tap 먼저 빼준 결과가 outp\_fb, outm\_fb이며 나머지 tap들과 디지털로 들어가기 위한 결과가 outp, outm이다. Input voltage의 차이가 30mV 미만일 경우 sensing에 실패하지만 30mV 이상이면 sensing을 성공한다. Sampling timing에 관련해서는 다음장에서 다뤄보도록 하겠다.

## 4.2.5 4tap 피드백 이퀄라이저

Figure 37. DFE feed-back timing analysis

구조를 참고하면 알 수 있다시피 DFE의 1<sup>st</sup> cursor는 SR latch를 거치지 않고 SA 결정값을 바로 넘겨주게 된다. 이로 인해 SA의 reset timing에 zero로 돌아가려고 하지만 고속으로 동작할 때는 cursor값을 전달하는 데 있어서 문제가 없다. 나머지 cursor들은 static latch ladder를 통해서 각 sampler에게 전달되게 되며 8Ghz에서 성공적으로 동작함을 확인할 수 있다.

# Chapter 5 결론

계속해서 data 소모량이 늘어나는 상황에서 쾌적한 사용환경을 제공하기 위해서는 저전력과 고속 통신이 필수적이다. 공정의 미세화를 통해 어느 정도 이를 달성할 수 있었지만 channel의 low-pass 특성은 극복하지 못해 equalizer를 도입하게 되고 이는 추가적인 전력 소모를 발생시켰다. 또한 baud-rate를 낮춰서 multilevel로 system을 구성하기도 한다.

이에 본 논문에서는 binary의 단점과 PAM4의 단점을 모두 극복할 수 있는 Ternary system을 구성하는 전체 system을 소개하였다. 또한 고속 신호에 이용되는 analog block들의 설계 방법도 제시했으며 TSMC 65n 공정에서 32Gtps로 동작하는 시뮬레이션 결과도 보여주었다. 그리고 각 analog block들의 속도에 맞춰서 modeling한 결과를 이용하여 system verilog에서 simulation을 수행하였으며 그 결과는 python으로 갈무리하였다.

# 참고 문헌

- [1] W. Bae, G. -S. Jeong, K. Park, S. -Y. Cho, Y. Kim and D. -K. Jeong, "A 0.36 pJ/bit, 12.5 Gb/s forwarded-clock receiver with a sample swapping scheme and a half-bit delay line," ESSCIRC 2014 40th European Solid State Circuits Conference (ESSCIRC), 2014, pp. 447-450, doi: 10.1109/ESSCIRC.2014.6942118.

- [2] G. -S. Jeong et al., "A 20 Gb/s 0.4 pJ/b energy-efficient transmitter driver architecture utilizing constant Gm," 2015 IEEE Asian Solid-State Circuits Conference (A-SSCC), 2015, pp. 1-4, doi: 10.1109/ASSCC.2015.7387466.

- [3] J. Hwang et al., "A 64Gb/s 2.29pJ/b PAM-4 VCSEL Transmitter With 3-Tap Asymmetric FFE in 65nm CMOS," 2019 Symposium on VLSI Circuits, 2019, pp. C268-C269, doi: 10.23919/VLSIC.2019.8777952.

- [4] J. W. Lechleider, "Line codes for digital subscriber lines (ISDN basic access)," in IEEE Communications Magazine, vol. 27, no. 9, pp. 25-32, Sept. 1989, doi: 10.1109/35.35509.

- [5] "Wired Communications T-SMINTO 4B3T Second Gen. Modular ISDN NT (Ordinary)" (PDF) (Data sheet). Version 1.1. Infineon. November 2001. PEF 80902.Alexander PD case(4gbps)

- [6] 예석민, 정덕균, "Pole과 Zero 정보를 이용한 아날로그 회로 모델링 방법과 그를 이용한 시뮬레이션 결과", 한국통신학회 동계종합학술발표회, 2012.

**Abstract**

Introduction to Ternary signaling system

and examination of simulation results

Baud-rate are continuously increase through shrieked CMOS fabrication. But in these

days channel quality is more important than process refinement because of channel's

low-pass property. To overcome this property, loss-less optical channel is used and

multi-level signaling is also widely adopted such as PAM4.

In this paper, Ternary system is introduced to overcome disadvantages of binary and

PAM4. Moreover, this paper suggests modeling simulation environment and results.

Furthermore, architectures and simulation results of analog blocks also included.

Seok-Min Ye

Dept. of Electrical and Computer Engineering, Seoul National University

Keywords: Ternary, multi-level, equalizer, offset, modeling, high-speed

Student Number: 2009-23122

37