### Ph.D. DISSERTATION

# Safety Verification of Analog Mixed-Signal Circuits Using Reachability Analysis

# 도달가능성 알고리즘을 이용한 아날로그 혼성회로 시스템의 정형 안전 검증 기법

BY

Kim Seyoung

AUGUST 2023

DEPARTMENT OF ELECTRICAL ENGINEERING AND COMPUTER SCIENCE COLLEGE OF ENGINEERING SEOUL NATIONAL UNIVERSITY

### Ph.D. DISSERTATION

# Safety Verification of Analog Mixed-Signal Circuits Using Reachability Analysis

# 도달가능성 알고리즘을 이용한 아날로그 혼성회로 시스템의 정형 안전 검증 기법

BY

Kim Seyoung

AUGUST 2023

DEPARTMENT OF ELECTRICAL ENGINEERING AND COMPUTER SCIENCE COLLEGE OF ENGINEERING SEOUL NATIONAL UNIVERSITY

# Safety Verification of Analog Mixed-Signal Circuits Using Reachability Analysis

# 도달가능성 알고리즘을 이용한 아날로그 혼성회로 시스템의 정형 안전 검증 기법

지도교수 김 재 하 이 논문을 공학박사 학위논문으로 제출함

2023년 8월

서울대학교 대학원

전기·정보공학부

## 김세영

김세영의 공학박사 학위 논문을 인준함

2023년 8월

# Abstract

This dissertation proposes a methodology to verify the safe operation of analog mixed-signal (AMS) circuits under formal specifications. With integrating many AMS integrated circuits (IC) in a car, assuring the safety of the system is getting a critical issue for developing such safety-critical systems. While the operating ranges of analog circuits and their semiconductor devices such as MOSFETs and diodes should be limited under safe-operating area (SOA) specified in the process design kit (PDK) or datasheets, the existing verification procedures relying on SPICE simulations in industry lack of capability to cover all possible dynamic behavior that causes the change of the applied terminal voltages or branch current of the devices. The formal verification algorithm, especially reachability analysis (RA), can prove that the system is safe by computing all reachable states from the specified initial conditions and finding if the reachable set of states intersects with the unsafe set of states causing failures of devices or circuits. However, computing the reachable set is burdensome for practical circuits since it takes too long to compute reachable sets in a high dimensional system dynamically operating in a high frequency, due to the continuous nature of the states that require quantization to many discrete steps of continuous value. This dissertation addresses the challenges while applying reachable analysis to AMS circuits and proposes an efficient way to compute reachable sets.

The proposed RA algorithm can compute the reachable set of analog mixed-signal circuits in a fast and accurate way by proposing a novel trajectory form of zonotope, combining two main ideas using scalable geometric set representation, such as zonotope and the XMODEL algorithm that computes analog signals in a trajectory form that represents the signal in a closed functional form with few algebraic coefficients. Any analog circuits, even those containing nonlinear components can be analyzed using the efficient piecewise-linear (PWL) approximation technique that only parti-

tions the state space of the circuit depending on the operating modes of the included devices. The resulting PWL system in the partitioned state space with several subregions is more difficult to be computed with conventional RA algorithms relying on time discretization since it calls for many additional computationally expensive geometric intersection operations, resulting in exponentially increasing runtimes with the number of transitions over sub-regions. Applying the proposed trajectory form is not straightforward because the intersection between the trajectory form and the switching boundary can not maintain the same form, requiring additional segmentation of the set shapes to keep the original form as before. Recognizing that every state after the intersection starts from the boundary plane, by computing the time evolution of the boundary itself, it has been shown that the associated computation can be done with the proposed trajectory form without increasing runtime.

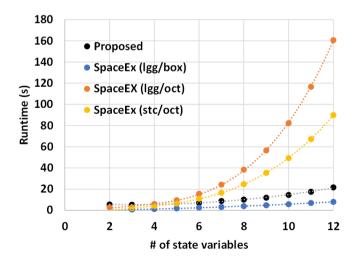

The proposed method was demonstrated by verifying the exemplary DC-DC switching converters, yielding over 107x speed-up than the existing reachability analysis algorithm in SpaceEx. The computational complexity for state dimensions was reduced by two orders than SpaceEx without losing accuracy, compared to the bound obtained equivalent Monte-Carlo simulations. Finally, SOA for DC-DC converters varying circuit parameters was derived and compared to typical 90-nm process criteria, showing the proposed method usable for verifying SOA specification of AMS circuits.

**keywords**: Reachability analysis, formal verification, safety verification, analog mixed-signal circuits, DC-DC converters, Laplace s-domain analysis, XMODEL **student number**: 2018-36370

# Contents

| Al | ostrac  | et            |                                                                 | i   |

|----|---------|---------------|-----------------------------------------------------------------|-----|

| Co | ontent  | ts            |                                                                 | iii |

| Li | st of ] | <b>Fables</b> |                                                                 | vi  |

| Li | st of I | Figures       |                                                                 | vii |

| 1  | INT     | RODU          | CTION                                                           | 1   |

|    | 1.1     | Backgi        | ound and Challenges                                             | 1   |

|    |         | 1.1.1         | Safety Verification of AMS Circuits Using Reachability Analysis | 3   |

|    |         | 1.1.2         | Hybrid System                                                   | 4   |

|    |         | 1.1.3         | Reachability Analysis                                           | 4   |

|    |         | 1.1.4         | Main Challenges                                                 | 6   |

|    | 1.2     | Main C        | Contribution                                                    | 8   |

|    | 1.3     | Thesis        | Organization                                                    | 10  |

| 2  | For     | nal Safe      | ety Verification of AMS circuits                                | 11  |

|    | 2.1     | Overvi        | ew of Model Checking                                            | 11  |

|    | 2.2     | Proble        | m Definition                                                    | 13  |

|    |         | 2.2.1         | Formal Definition of Safety Verification                        | 13  |

|    |         | 2.2.2         | Safe operation of AMS circuits                                  | 14  |

|    | 2.3     | Conver        | ntional Hybrid System Reachability Analysis                     | 14  |

|   |     | 2.3.1  | SpaceEx                                                   | 15        |

|---|-----|--------|-----------------------------------------------------------|-----------|

| 3 | TRA | AJECTO | ORY-FORM REACHABILITY ANALYSIS                            | 19        |

|   | 3.1 | Reach  | ability Analysis on Linear Circuits                       | 19        |

|   |     | 3.1.1  | General Trajectory Form of Reachable Set                  | 19        |

|   |     | 3.1.2  | Zonotope Trajectory Form of Reachable Set                 | 21        |

|   |     | 3.1.3  | Computing Trajectory Form using Laplace s-domain Transfer |           |

|   |     |        | Function                                                  | 22        |

|   |     | 3.1.4  | Example: Reachable set of RC circuit                      | 23        |

|   |     | 3.1.5  | Example: Reachable set of LC circuit                      | 25        |

|   |     | 3.1.6  | Comparison with Existing Algorithms                       | 25        |

|   | 3.2 | Hybric | 1 System Reachability Analysis                            | 28        |

|   |     | 3.2.1  | Hybrid System Representation of AMS Circuits              | 28        |

|   |     | 3.2.2  | Hybrid System Reachability Analysis Using Trajectory Form | 29        |

|   |     | 3.2.3  | Example: Switched RC Circuit                              | 30        |

| 4 | HYI | BRID S | YSTEM REACHABILITY ANALYSIS OF NONLINEAR CIR              | <b>!-</b> |

|   | CUI | Т      |                                                           | 33        |

|   | 4.1 | Piecew | vise-Linear Modeling of AMS Circuits                      | 33        |

|   | 4.2 | Piecew | vise-Linear Approximation of Nonlinear Circuits           | 34        |

|   | 4.3 | Comp   | uting Guard Intersections at PWL Switching Boundary       | 36        |

|   |     | 4.3.1  | Hybrid System Representation of PWL circuits              | 36        |

|   |     | 4.3.2  | Computing Guard Intersection Using Trajectory Form        | 36        |

|   |     | 4.3.3  | Computing Reachable Sets in New Sub-Regions               | 40        |

|   | 4.4 | Time ( | Complexity Analysis                                       | 45        |

|   |     | 4.4.1  | Trajectory Form Computation                               | 45        |

|   |     | 4.4.2  | Guard Intersection Computation                            | 46        |

|   |     | 4.4.3  | Reachable Set Computation from Guard Intersection         | 46        |

|   |     | 4.4.4  | Overall Complexity                                        | 47        |

|    | 4.5                     | Computing Safety Bounds from Reachable Sets in Trajectory Form | 47 |  |  |  |  |  |  |

|----|-------------------------|----------------------------------------------------------------|----|--|--|--|--|--|--|

|    | 4.6                     | Benchmark: Numerical Example                                   | 48 |  |  |  |  |  |  |

|    |                         | 4.6.1 Error Measures                                           | 49 |  |  |  |  |  |  |

|    |                         | 4.6.2 Comparison of accuracy and runtime                       | 50 |  |  |  |  |  |  |

|    | 4.7                     | Conclusion                                                     | 53 |  |  |  |  |  |  |

| 5  | SOA                     | VERIFICATION OF DC-DC BUCK CONVERTERS                          | 55 |  |  |  |  |  |  |

|    | 5.1                     | SOA Verification of DC-DC Buck Converters                      | 57 |  |  |  |  |  |  |

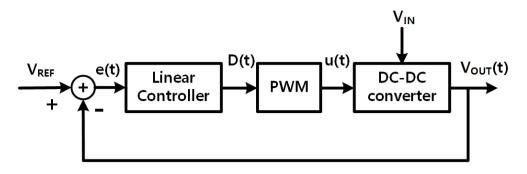

|    | 5.2                     | Open-Loop Verification with PWM Control                        | 57 |  |  |  |  |  |  |

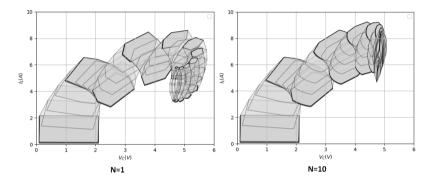

|    |                         | 5.2.1 Experimental Scalability                                 | 62 |  |  |  |  |  |  |

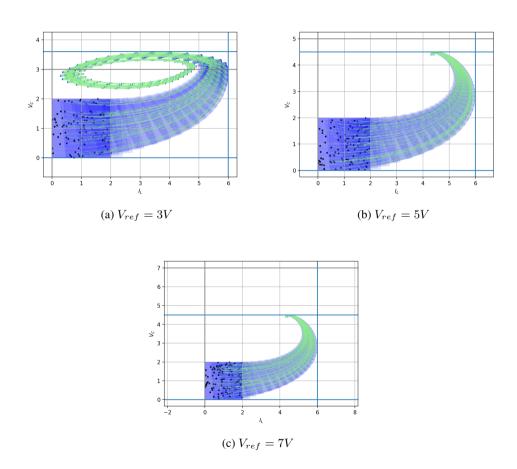

|    | 5.3                     | Closed-Loop Verification with PWM Control                      | 64 |  |  |  |  |  |  |

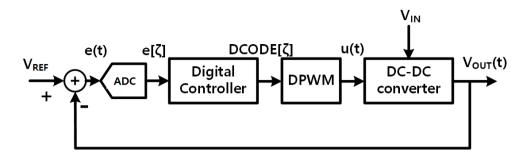

|    |                         | 5.3.1 DC-DC Buck Converter with Digital Pulse-Width Modulation |    |  |  |  |  |  |  |

|    |                         | (DPWM) Control                                                 | 65 |  |  |  |  |  |  |

|    | 5.4                     | Verifying Safe Operating Area (SOA)                            | 69 |  |  |  |  |  |  |

| 6  | CON                     | NCLUSION                                                       | 72 |  |  |  |  |  |  |

| 7  | APP                     | PENDIX                                                         | 76 |  |  |  |  |  |  |

|    | 7.1                     | Code Implementation                                            | 76 |  |  |  |  |  |  |

|    |                         | 7.1.1 Example: Trajectory Form Reachable Set                   | 76 |  |  |  |  |  |  |

| Ał | Abstract (In Korean) 82 |                                                                |    |  |  |  |  |  |  |

# **List of Tables**

| 5.1 | Default Circuit Parameters |  |  |  |  |  |  |  |  | • | • | • |  |  |  |  | • |  |  |  |  |  | • |  | 5 | 9 | 1 |

|-----|----------------------------|--|--|--|--|--|--|--|--|---|---|---|--|--|--|--|---|--|--|--|--|--|---|--|---|---|---|

|-----|----------------------------|--|--|--|--|--|--|--|--|---|---|---|--|--|--|--|---|--|--|--|--|--|---|--|---|---|---|

# **List of Figures**

| 1.1 | Analog verification challenge vs. digital. (a) Logical AND gate and (b)        |    |

|-----|--------------------------------------------------------------------------------|----|

|     | analog OP amp. Analog formal verification requires additional quan-            |    |

|     | tization, resulting in the dimensional complexity problem                      | 3  |

| 1.2 | Simple hybrid automata example with two discrete states                        | 5  |

| 1.3 | Difference between (a) test-bench simulations and (b) reachability anal-       |    |

|     | ysis. Simulation may not capture hidden bugs while reachability anal-          |    |

|     | ysis exhaustively finds possible set of states from the initial set of states. | 5  |

| 1.4 | Over-approximation depending on geometrical set representations                | 6  |

| 1.5 | Over-approximation depending on time steps.                                    | 7  |

| 2.1 | Concepts of model checking in discrete systems represented as a finite         |    |

|     | state machine (FSM)                                                            | 12 |

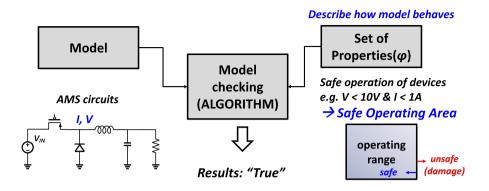

| 2.2 | Concepts of safety verification.                                               | 13 |

| 2.3 | Model checking of safe operation of circuits.                                  | 15 |

| 2.4 | SOA verification of a circuit with two state variables                         | 16 |

| 2.5 | Conventional reachability analysis tool SpaceEx.                               | 17 |

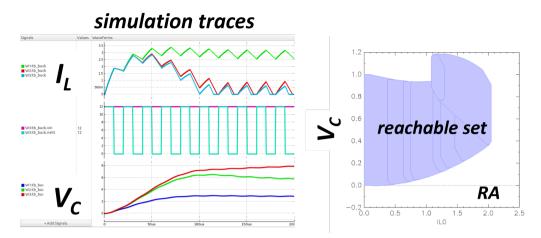

| 2.6 | Reachable set obtained in SpaceEx compared to simulation traces in             |    |

|     | XMODEL                                                                         | 18 |

| 3.1 | Simple exemplary circuits (a) RC circuit (b) LC circuit                        | 24 |

| 3.2 | Reachable set of the exemplary circuits (a).                                   | 24 |

| 3.3  | Reachable set of the LC harmonic oscillator circuit. (a) $I_L$ -t (b) $V_C$ -t           |    |

|------|------------------------------------------------------------------------------------------|----|

|      | (c) $V_C$ - $I_L$                                                                        | 26 |

| 3.4  | Reachable set in SpaceEx (a) $I_L$ -t (b) $V_C$ -t (c) $V_C$ - $I_L$                     | 27 |

| 3.5  | Reachable set in SpaceEx (a) $I_L$ -t (b) $V_C$ -t (c) $V_C$ - $I_L$                     | 28 |

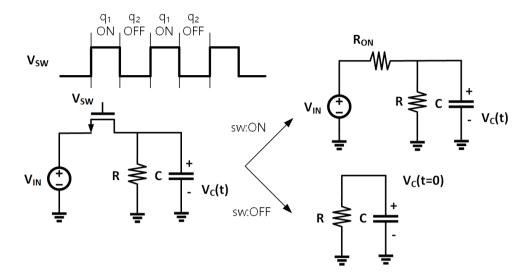

| 3.6  | Switched RC Circuit with cyclic pulse inputs and the corresponding                       |    |

|      | linear circuits.                                                                         | 31 |

| 4.1  | PWL partitioning of the circuit with a diode                                             | 34 |

| 4.2  | The problem of computing the guard intersection $\mathcal{R}(t) \cap \mathcal{G}$ in PWL |    |

|      | system representation.                                                                   | 35 |

| 4.3  | The overall algorithm to compute the guard intersection at the disjoint                  |    |

|      | regions $S_p$ and $S_{p'}$ .                                                             | 37 |

| 4.4  | Search process for the best $l_k$ 's in the procedure for approximating                  |    |

|      | $\mathcal{R}(t) \cap \mathcal{G}$ with low over-approximation error getOrthogonalBasis   | 38 |

| 4.5  | The procedure getIntersect2D for computing the range of segment                          |    |

|      | $[m, M]$ in a $(w, l_k)$ -plane.                                                         | 41 |

| 4.6  | Case when external discrete state $m(t)$ changes its state at $t = T$ while              |    |

|      | the reachable set $\mathcal{R}(t)$ is crossing in $t = [t_1, t_2]$ .                     | 45 |

| 4.7  | Hybrid automata of the LC oscillating system.                                            | 48 |

| 4.8  | Error measure $err_1$ using MC integration method                                        | 49 |

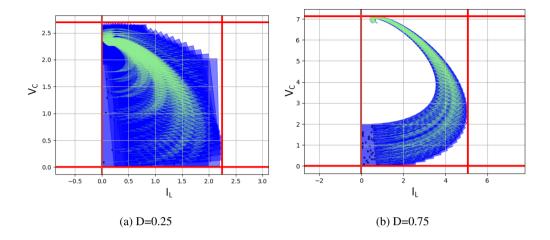

| 4.9  | Reachable sets computed for a 2-D linear hybrid system example with                      |    |

|      | a guard hyperplane                                                                       | 51 |

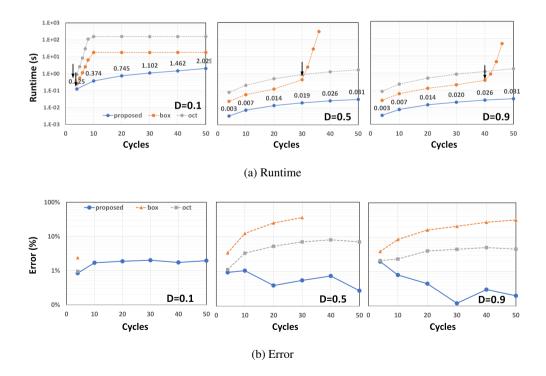

| 4.10 | Increasing $err_1$ as the number of cycles (guard intersections)                         | 52 |

| 4.11 | Safety bound of state $x(t)$                                                             | 53 |

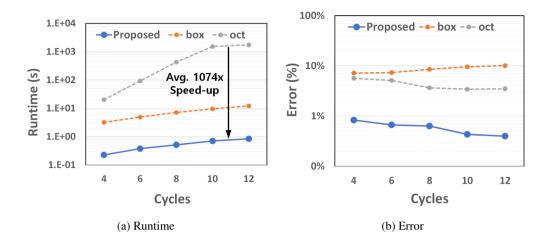

| 4.12 | Runtimes and error comparison vs. SpaceEx algorithms $(err_2)$                           | 54 |

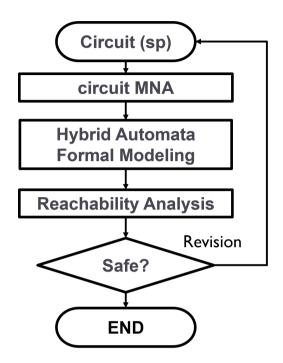

| 5.1  | Overall flow of safety verification methodology for a given circuit                      | 56 |

| 5.2  | Switching power supplies operating as switched-linear systems                            | 56 |

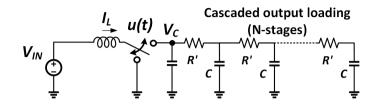

| 5.3  | DC-DC buck converter operating in DCM                                                    | 58 |

| 5.4  | The reachable set computed for the DC-DC buck converter circuit        | 61 |

|------|------------------------------------------------------------------------|----|

| 5.5  | Performance for open-loop operation including DCM                      | 61 |

| 5.6  | Buck converter circuit with multiple RC loadings                       | 63 |

| 5.7  | Reachable set with multiple RC loadings.                               | 63 |

| 5.8  | Scalability as the number of state dimensions compared to SpaceEx.     | 63 |

| 5.9  | DC-DC buck converter with PWM feedback loop                            | 64 |

| 5.10 | DC-DC buck converter with Digital PWM feedback loop                    | 65 |

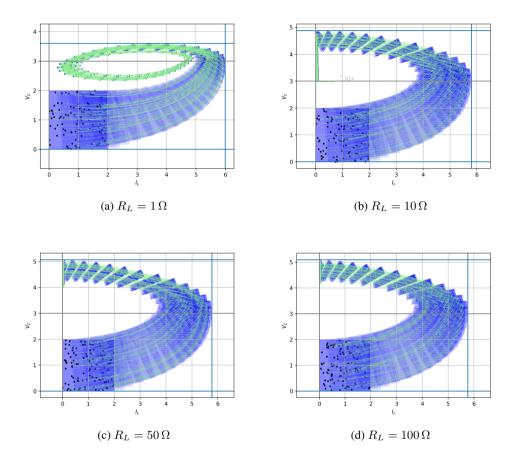

| 5.11 | Reachable sets varying $V_{REF}$ for PWM DC-DC buck converter          | 66 |

| 5.12 | Reachable sets varying $V_{REF}$ for PWM DC-DC buck converter          | 67 |

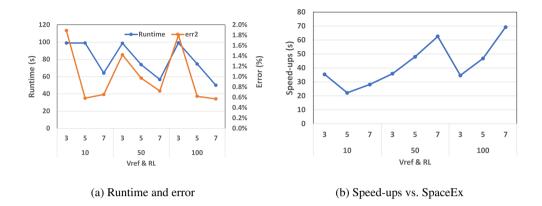

| 5.13 | Performance comparison for PWM DC-DC buck converter                    | 68 |

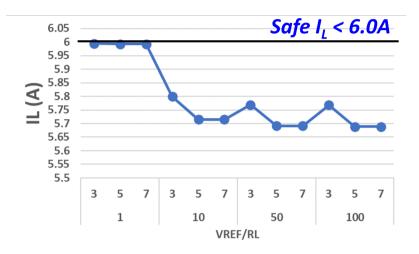

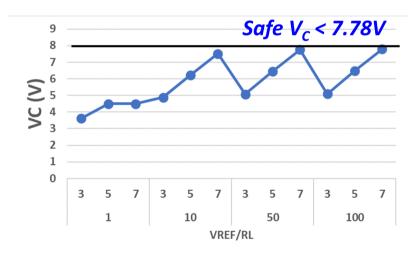

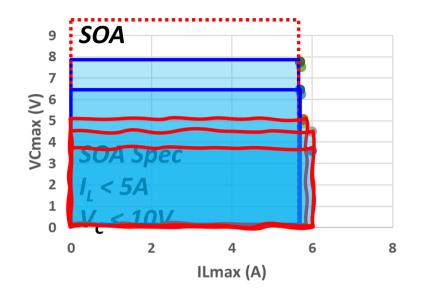

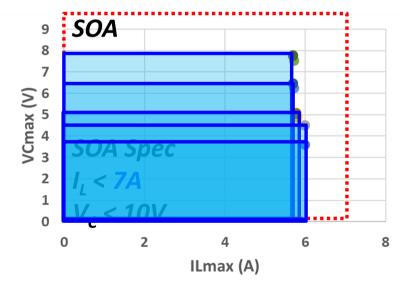

| 5.14 | Verifying safe operating area of the circuit under verification        | 70 |

| 5.15 | Verifying safe operating area of the circuit under verification        | 71 |

|      |                                                                        |    |

| 6.1  | Conservative error compared to simulations                             | 73 |

| 6.2  | Backward reachability analysis extending the proposed trajectory-form. | 74 |

## Chapter 1

## **INTRODUCTION**

#### **1.1 Background and Challenges**

With emerging autonomous systems such as electrical vehicles, drones, and robots, verifying such safety-critical systems becomes a significant issue today, since failures or malfunction of these systems can lead to severe economical loss or environmental damage and even risks to human lives. For example, Toyota's recent brake problems were known as software defects due to incomplete verification and Toyota's market capitalization of \$25 billion was lost in the two months with the recalls in January 2010 [1]. The famous floating-point division (FDIV) bug in the Pentium IV processor in the 90s cost \$475M charge for Intel to cover the replacement of every defective CPU [2]. As, however, the number of its parameters that interacts with each block in the system increases with the growing design complexity, randomly generated test benches mostly failed to detect the rare bug hidden in the deep state of complex designs, which is like hitting the center of the target with a dart [3]; therefore, formal verification is necessary and indispensable for state-of-the-art complex mixed-signal integrated circuits (IC) and system-on-chips (SoC).

In particular, semiconductor devices such as MOSFETs and diodes, and other metal interconnection layers are vulnerable to exposure to high current or voltage. Therefore, analog circuit designers generally ensure reliable operation of their AMS circuits according to the *safe-operating area* (SOA) specification for all devices and circuits [4], which is specified in process design kits (PDK) that describes the behaviors and requirements of the design components including active elements such as MOSFETs and passive interconnecting elements such as metal layers or resistors of the corresponding manufacturing process used. Circuit designers should verify that the devices used in their circuits should operate within the allowed regions defined in terms of voltages and currents. However, the conventional design methodology for analog circuits relies on limited simulation-based methodologies that only simulate parts of test cases based on heuristics, leading to incomplete verification and most of them can cause malfunction of the entire system such as car accidents. In addition, due to the scaling of the process, the design window for SOA is getting smaller than before and the complex interaction between analog and digital blocks also becomes more threats of unexpected behavior, increasing the likelihood of such critical design errors.

Formal verification can prove the correctness of the systems with given specifications considering every possible state of the system with mathematical algorithms [5], while simulations never guarantee. Numerous formal verification solutions have been developed for verifying complicated control algorithms for software and hardware after the success story of Pentium bug hunting [2] with the development of algorithmic logical reasoning such as *model checking* [5] and *theorem proving* methodologies [6]; however, compared to the rich achievements for fore-mentioned areas, a way towards formally verifying analog mixed-signal (AMS) circuits is still far from the sight.

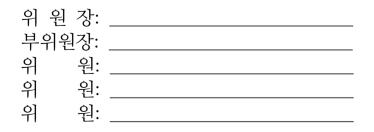

The main difficulty comes from the fact that the analog circuits operate with continuous state values represented in the state space with continuous time. For example, let's assume that one needs to verify the function of two circuits given shown in Fig. 1.1 [7]. While the possible states of the logical AND gate with two inputs and single output have only four cases, verifying an analog op-amp circuit requires exploring an infinite

2

Figure 1.1: Analog verification challenge vs. digital. (a) Logical AND gate and (b) analog OP amp. Analog formal verification requires additional quantization, resulting in the dimensional complexity problem.

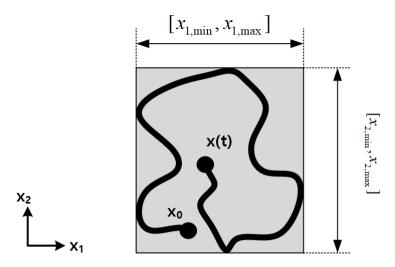

number of cases for exhaustively exploring possible states due to the continuous nature of the input and state variables. This requires quantization of a set of continuous states, leading to additional dimensional complexity problems that require exponentially increasing complexity with respect to the number of state dimensions at least. In addition, as one uses more accurate shapes for reducing the over-approximation error, the computational time will be further increased. This work addresses a way to verify the safety of AMS circuits by efficiently modeling AMS circuits and computing their states fast and accurately with tacking the time complexity problem from the quantization of continuous value.

#### 1.1.1 Safety Verification of AMS Circuits Using Reachability Analysis

We focus on verifying the safety of AMS circuits in this dissertation. In practice, safety verification of analog circuits involves two steps: i) **Formal abstraction**: abstraction of circuits to explore reachable states such as *hybrid system* and ii) **Reachability anal**-

ysis: computing the evolution of continuous states with time t by computing the set containing the states and their time evolution; therefore, it requires computationally efficient set structure with less approximation errors.

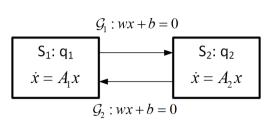

#### 1.1.2 Hybrid System

We model AMS circuits as hybrid systems in this study. A hybrid system can capture every possible dynamic behavior of AMS circuits, which is a system combining the behavior of both discrete variables  $q \in Q$  and continuous variable  $x \in X$ , where we can apply formal analysis techniques. Its model is represented by hybrid automata

$$M = \langle X, Q, E, F, \mathcal{G} \rangle \tag{1.1}$$

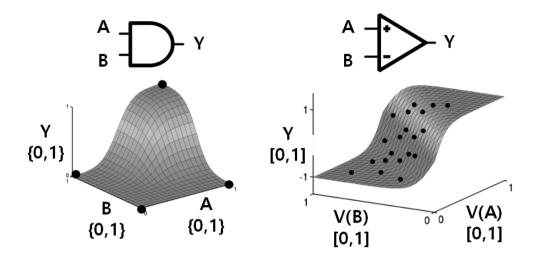

which can be considered as a graph structure, where each node corresponds to a continuous system associating its differential equations F, a set of discrete transitions, the guard  $\mathcal{G}$  that conditions for the variable that triggers the discrete transition in E(or jump in the different literature) and assignment associated with the transition (or reset). Each differential equation F can be linear or nonlinear; when every differential equation F is linear, then the automata M is defined by linear hybrid automata, which we address how to efficiently transform the nonlinear circuits to this class of automata that we mainly use through the dissertation. A simple example of hybrid automata is illustrated in Fig. 1.2. The automata has two discrete states, also referred to as a location. The transition between the locations in the automata is determined by the value of continuous variable t. When the variable t becomes greater than T, it switches its location and the associated differential equation simultaneously.

#### **1.1.3 Reachability Analysis**

The main topic of this dissertation is reachability analysis [8, 9, 10, 11, 12, 13, 14, 15, 16, 17, 18, 19, 20, 6, 21, 22, 23, 24, 5], which is one of the most prominent formal algorithms for checking the model that can prove the safety property of the system;

Figure 1.2: Simple hybrid automata example with two discrete states.

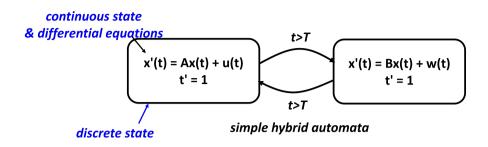

Figure 1.3: Difference between (a) test-bench simulations and (b) reachability analysis. Simulation may not capture hidden bugs while reachability analysis exhaustively finds possible set of states from the initial set of states.

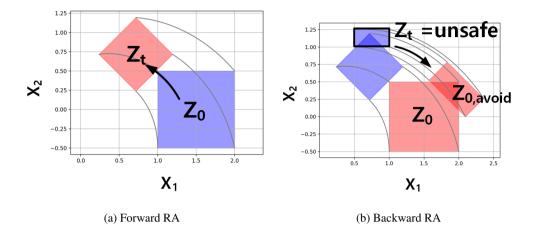

it is originally developed for verifying complex communication protocols in 70s and expanding its application area even for continuous systems. While original automata can only consider the case that its continuous variable and their derivative is limited as constant such as  $\dot{x} = 1$ , so-called timed automata, the system we focus on in this dissertation is the linear hybrid system mentioned above. The main difference is that the derivative of the continuous variable has the linear equation of the variable. Same to the general cases, hybrid reachability analysis verifies safety by finding all hybrid states that can be reached from a specified range of initial states and checking if the reachable states are within a target range.

Safety verification using reachability analysis is a formal procedure that finds every

Figure 1.4: Over-approximation depending on geometrical set representations.

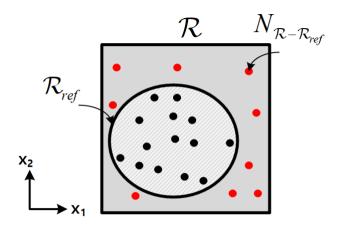

reachable state from the initial states  $X_0$  and then collecting the resulting states yields the set of reachable states  $\mathcal{R}$ , commonly referred as *reachable set*, and this procedure is called *reachability analysis*. We can conclude the system is safe if the reachable set  $\mathcal{R}$  does not contain any unsafe states defined in unsafe set  $\mathcal{U}$ .

#### **1.1.4 Main Challenges**

The main challenge in computing the reachable sets for an AMS circuit is three-fold.

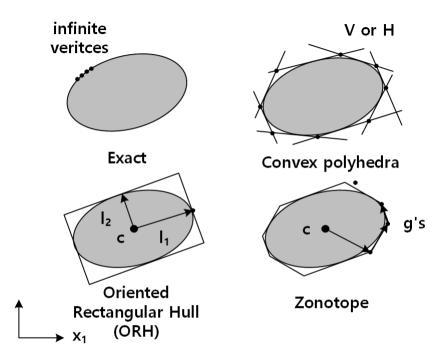

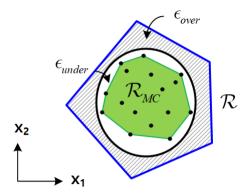

**Space discretization problem** First, as shown in Fig. 1.4, computing a set of analog states in the state space introduces a geometrical shape that encloses every possible state and is represented by a set of vectors representing the vertices or faces. However, exact representation for an arbitrary region of reachable sets  $\mathcal{R}$  is impossible because it requires an infinite number of vertices or faces; thus, one needs to conservatively

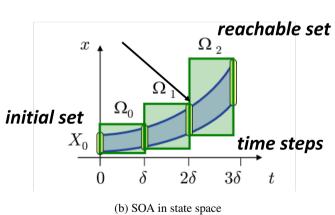

Figure 1.5: Over-approximation depending on time steps.

approximate the exact one with efficient geometrical shapes with fewer vertices and should balance the *trade-off* between the accuracy and the computational efficiency of the geometry. As shown in the Fig. 1.4, an oriented rectangular set (ORH) using fewer vectors causes a large over-approximation error due to its coarse shape, while the complex and fine shape using more vectors can reduce the resulting over-approximation error but increase the runtime of the analysis. After decades of efforts for finding computationally efficient geometrical set representations, several set representations using linear algebra are gaining popularity for this purpose, such as oriented rectangular hull [25], ellipsoid [18], convex polyhedra [16] and zonotopes [14]. These set representations are very efficient for computing the reachable set in linear systems even with hundreds of state variables, but have limitations in that they can only be applied to linear systems.

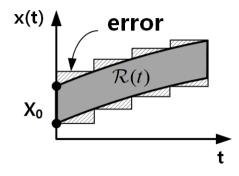

**Time discretization problem** Secondly, to compute the change of a set of states for a given time period, conventional reachability algorithms first segment the analysis time duration into several discrete steps of time and then compute the reachable sets by iteratively multiplying the system matrix with the sets at each time steps, incurring a large computational cost. Furthermore, mixed with the first problem concerning space discretization, it needs to split the period with more fine time steps if it fails to

accurately represent the trajectory of the set with the selected set representation with given error tolerance. However, there have been few approaches to address this issue yet.

**nonlinearity** Lastly, typical analog circuits are nonlinear, while those methods described above are applied only for linear systems; thus, they need to be linearized into several disjoint sub-regions. However, the computational cost for the transition between each region grows fast with the number of time steps to compute the time evolution of the reachable sets.

The most simple and efficient approach is converting them into a piecewise linear system that operates in different differential equations in each region segmented by specified switching conditions [26, 27]. However, we found that conventional reachability tools suffer from computing the transition at the switching boundary, which is commonly referred to as a guard intersection and is a computationally expensive geometrical intersection operation. *guard* set is equivalent to the set enclosing the switching condition, and their intersection should be computed in other sub-region of the PWL system with its own set of differential equations. While sliding the reachable set with time over the boundary, it intersects with the boundary and generates infinite sets of intersections. With the conventional method with time discretization reachable set computation, the analysis incurs a tremendous number of computations proportional to  $N_t \times N_t$  where  $N_t$  is the number of steps resulting from time discretization. Even worse, every increasing number of states to be computed is multiplied by each other, generating an exponential increase with respect to the number of discrete transitions over the guard.

### **1.2 Main Contribution**

This work proposes a methodology for verifying the safe operation of AMS circuits using a fast trajectory-form reachability analysis algorithm. The key idea is to reduce the number of evaluations at the discrete time steps to represent the trajectory of the reachable sets  $\mathcal{R}$  as a sequence of sets  $\{\mathcal{R}_t, ..., \mathcal{R}_{N_t}\}$ , where the number of time steps by discretizing the period of continuous time [0, T]. Instead, in this work, the reachable set is represented by a closed and exact form of the function  $\mathcal{R}(t)$ , where each vertex follows a trajectory described by an exact, analytical function of time t.

This approach has mainly two advantages. At first, it can compute the exact trajectory from the initial set at once without discrete evaluation at discrete time steps of t similar to the numerical integration method in the simulation algorithm. This adopts the idea of [28] representing analog signals as s-domain signals using the coefficients representing the poles, zeros, and gains of the signal. In this way, it outperformed typical numerical solvers when solving AMS circuit behaviors, demonstrating wide ranges of AMS circuits and systems such as switching power supplies, decision feedback equalizers (DFE), phase-locked loops (PLL) and etc. Therefore, it efficiently avoids the concern of trade-offs scarifying the resulting accuracy to get better performance. One can represent the exact trajectory  $\mathcal{R}(t)$  starting from the initial set  $X_0$  as shown in Fig. 1.5.

Second, this idea can further improve the scalability especially when computing the reachable set of hybrid systems, which increases the number of computations proportional to  $N_t \times N_t$ . This limitation prohibits most of the existing reachability tools fails to evaluating the practical nonlinear circuits even for simple and trivial circuits. Using the proposed trajectory-form reachability analysis, one can accurately compute the guard intersection  $\mathcal{R}(t) \cap \mathcal{G}$  without generating additional time steps to get an accurate intersecting range or region. The subsequent reachable set from the guard intersection also can be efficiently evaluated.

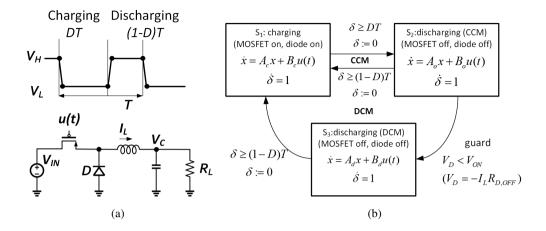

The dissertation demonstrates that the proposed method can verify the safe operation of practical switching power supply circuits: buck converters and various switching pulse control schemes. Firstly, we demonstrate the basic buck converter circuits operating in continuous conduction mode (CCM) changing their behavior depending on the duty cycle of the input pulse applied to its transistor switch to show the computational scalability for simple hybrid systems. Secondly, we demonstrate a more general buck converter exhibiting discontinuous conduction mode (DCM) operation due to the non-linear characteristic of the diode, showing the improved performance when computing the continuous guard intersection  $\mathcal{R}(t) \cap \mathcal{G}$  occurs. The term *continuous* means that the intersections occur in the continuous time period  $[t_1, t_2]$  not at the specific time instant.

In the experiment, resulting accuracy was estimated compared to the equivalent Monte-Carlo simulations, and the performance is compared to one of the reachability analysis tools, SpaceEx [17], which implements the convex polyhedra set-based reachability analysis tool using the support function and the other advanced algorithms. It serves as a golden reference for evaluating the performance of the new reachability analysis algorithm owing to its flexibility.

### 1.3 Thesis Organization

Chapter 2 explains the concepts of formal verification of circuits. Chapter 3 describes the proposed trajectory-form reachability analysis in detail with mathematical definition and derivation. Chapter 4 presents the proposed reachability analysis algorithm for non-linear circuits. Chapter 5 demonstrates the proposed methodology with practical circuit examples for verifying their safe operations. Chapter 6 draws the conclusion of this thesis.

## Chapter 2

## Formal Safety Verification of AMS circuits

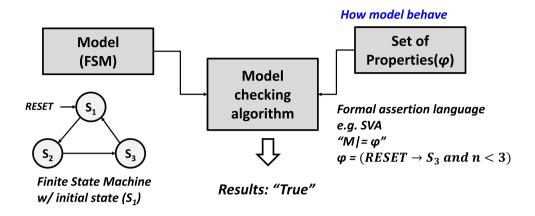

This chapter explains the concepts of formal safety verification of AMS circuits. With the growing complexity of hardware design having millions of lines of code, human verification reached its limitation, creating tons of trivial bugs and imposing critical system risks. Consequently, formal verification gains attention for decades from theoretical to practical views. Its category can be classified by its intent to verify: equivalence checking, model checking, and theorem proving. At the beginning of the 70s, there were approaches using logical inductive reasoning like human proof with penciland-paper, which we call theorem proving. This is ideal proof, but hard for a nonexpert to use. Instead, with the recent great improvement of computing capability with massively parallel computing, more practical methods gain more attention, so-called model checking. In this chapter, we explain how we can guarantee the safe operation of AMS circuits using formal model-checking techniques, and reachability analysis.

### 2.1 Overview of Model Checking

Model Checking is a general concept of a computer-assisted method for the analysis of dynamical systems that can be modeled by state-transition systems. Model checking is now widely used for formal verification of software and hardware in industry,

Figure 2.1: Concepts of model checking in discrete systems represented as a finite state machine (FSM).

including many mathematical algorithms with model structure abstracting given systems. Model checking consists of three main concepts: modeling, specification, and algorithms. As we stated in the definition, its model has the form of a finite-state machine. It can be applied to any dynamical system and can be represented in the form of a state transition system. Second, verifying a system requires specifying the design intent formally. It is typically given by the description of the system specification, which should be transformed into a formal representation. For example, temporal logics such as LTL and CTL, or Synopsys Verification Assertion (SVA) language are used in industry for formal verification. Finally, there is a decision procedure for determining (i.e. verifying) that the given *model* behavior always satisfies the given specification. This concept of model checking can be summarized as shown in Fig. 2.1. The procedure of model checking is to check if model M satisfies the specification  $\varphi$ , where the system starts from the state  $S_1$  and reaches the state  $S_3$  in less than three steps if not, it produces the counterexample. One can see that the result will become true because the FSM reaches  $S_3$  in two steps.

The main challenge of model checking is the state-explosion problem due to its exhaustive nature, increasing its runtime proportionally. The resulting number of states

Figure 2.2: Concepts of safety verification.

to explore exponentially increase with a combinatorial number of bit size of states (e.g. memory of computer program or number of flip-flops of digital system). Therefore, computing directly the model of a given system in the real world is impossible; instead, one needs to model the system in an efficient way.

### 2.2 **Problem Definition**

In this section, we formally define the problem of verifying the safe operation of circuits and highlight the goal of this thesis.

#### 2.2.1 Formal Definition of Safety Verification

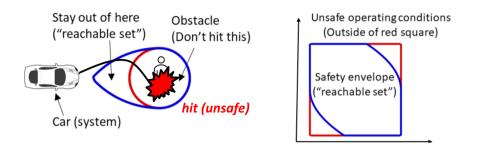

Safety verification is widely used in verifying safety-critical hybrid dynamic systems such as robots, autonomous control of cars and drones, etc. The goal of dynamic control of these hybrid systems is not to hit critical obstacles such as humans or valuable objects. This is a reachability problem that checks if all the reachable states from any possible initial conditions after the finite duration of time reach safe or unsafe regions as shown in Fig. 2.2.

Formally, this model checking problem of any safety property can be reduced to the reachability problem of deciding reachability to a set of bad state  $\mathcal{U}$ . If  $M \models \varphi$ , then  $\varphi$  is called an *invariant* of model M. That is, collecting every reachable state, i.e. *reachable set*  $\mathcal{R}$  is equivalent to getting invariant  $\varphi$  of the model M; therefore, safety verification is a reachability problem that checks if there is any state s satisfying:

$$(s \in \mathcal{R} \subseteq \varphi) \land (s \in \mathcal{U}). \tag{2.1}$$

This is equivalent to finding the intersection of  $\mathcal{R} \cap \mathcal{U}$  and if there is any state in  $\mathcal{U}$ . We can apply this concept of safety verification to verify the safe operation of circuits in the same manner in the state space of circuits.

#### 2.2.2 Safe operation of AMS circuits

Verifying the safe operation of circuits not to be damaged by high operating voltages or current applied to devices also can be represented in the safety verification problem of (2.1). Fig. 2.3 illustrates the concepts in terms of verifying the safety of circuits. In this case, the reachable set  $\mathcal{R}(t)$  can be computed by a set of the moving states x(t)in the state space of circuit state variables consisting of capacitor voltages  $V_C(t)$  and inductor currents  $I_L(t)$ . Then, if the reachable set  $\mathcal{R}(t)$  containing the circuit states x(t) intersects the unsafe region  $\mathcal{U}$  that is defined in terms of critical voltage or current specified safe operating area (SOA) in PDKs.

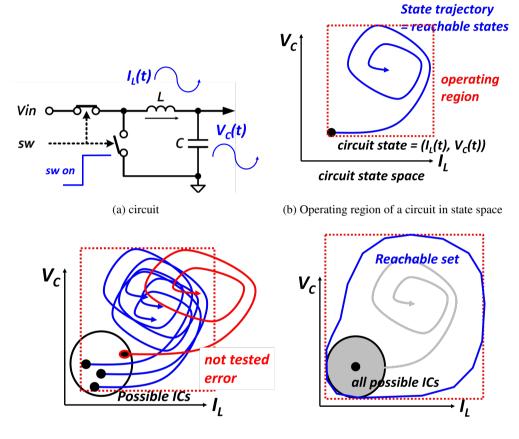

Fig. 2.4 illustrates the problem of verifying if the operating region of a circuit is kept within the allowed safe-operating area in the state space. Given a circuit as Fig. 2.4, the behavior of the circuit is described with two continuous state variables  $I_L$  and  $V_C$  as Fig. 2.4 (b). However, the circuit can start with any initial values of the state variables  $I_L$  and  $V_C$ , leaving the possibility of un-tested errors that may cause damage to circuits. Reachability analysis can compute the reachable set of circuits from a set of initial conditions given by specification, leading to correct verification results as illustrated in Fig. 2.4 (d).

#### 2.3 Conventional Hybrid System Reachability Analysis

Conventional hybrid system reachability analysis methods are mostly based on hybrid system abstraction and set-based reachability analysis. The algorithm can compute the

Figure 2.3: Model checking of safe operation of circuits.

time evolution of a set of states using efficient set representation and hybrid dynamics formally specified by the hybrid automata model.

As we mentioned above, the efficiency of this technique highly depends on the selected set representation. In this section, we review the formal definition of the widely used set representation and their fundamental limitations. Lastly, we also explain the state-of-the-art reachability analysis tool SpaceEx, to which we will compare the proposed method.

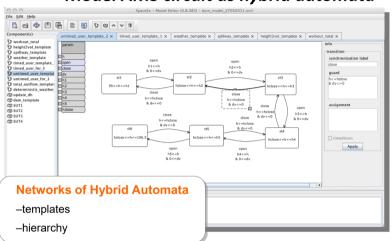

#### 2.3.1 SpaceEx

The SpaceEx is a tool platform implementing algorithms related to reachability and safety verification suitable for continuous hybrid dynamic systems. It models the target system as hybrid automata with hierarchical automata and templates. The model editor for model hybrid automata is implemented with visual user interfaces as shown in Fig. 2.5.

It basically based on computing reachable sets depending on time steps multiplied by  $\delta$ . Then, the resulting reachable sets in each time interval are computed as in  $\Omega_0, \Omega_1, \ldots$ . There are several options to express the reachable set depending on the options depending on target accuracy and the resulting reachable sets are displayed over the output user interfaces as blue polygons as in Fig. 2.6, which shows the comparison

(c) Undiscovered bugs with set of initial conditions (d) Operating region obtained from reachable sets

Figure 2.4: SOA verification of a circuit with two state variables.

## Model AMS circuit as hybrid automata

(a) circuit

(c) borrin state space

Figure 2.5: Conventional reachability analysis tool SpaceEx.

(a) Simulation results varying load resistances using (b) Reachable set using SpaceEx until t=10us. XMODEL.

Figure 2.6: Reachable set obtained in SpaceEx compared to simulation traces in XMODEL.

of the output simulation traces for currents and voltages of the exemplary circuits.

However, it fails to run until the end of the analysis due to exponentially increasing runtimes for our initial model describing the piecewise linear behavior of the typical circuits with MOSFETs or didoes. The rest of the dissertation tackles the problem associated with the conventional reachability analysis algorithm based on time discretization similar to the numerical integration algorithm of analog simulators such as SPICE simulators.

## Chapter 3

## **TRAJECTORY-FORM REACHABILITY ANALYSIS**

This chapter presents the main idea of the proposed trajectory-form reachability analysis methodology for analog/mixed-signal (AMS) circuits. We consider here specifically a linear hybrid system, which is a hybrid system, and its behavior in each continuous system is described by a linear system. First, we transform the linear circuit from topology to state space representation using the modified nodal analysis technique (MNA). Then, the obtained system matrices are transformed into transfer functions using the XMODEL algorithm. Combined with the s-domain input expression, we can obtain the trajectory form of the reachable set from the circuits.

#### 3.1 Reachability Analysis on Linear Circuits

#### 3.1.1 General Trajectory Form of Reachable Set

If a system representing the circuit is linear, computing reachable sets is straightforward. The dynamics of the continuous variable in the subset S of the state space,  $x(t) \in S \subseteq \mathbb{R}^n$  and the output  $y(t) \in \mathbb{R}^{n_o}$  with the input  $u(t) \in \mathbb{R}^{n_i}$  in a ndimensional system are defined by

$$\dot{x}(t) = Ax(t) + Bu(t), \qquad (3.1)$$

$$y(t) = Cx(t) + Du(t)$$

(3.2)

where the system matrices  $A \in \mathbb{R}^{n \times n}$ ,  $B \in \mathbb{R}^{n \times n_i}$ ,  $C \in \mathbb{R}^{n_o \times n}$ , and  $D \in R^{n_o \times n_i}$ .  $n_i$ and  $n_o$  are the numbers of inputs and outputs, respectively. Then, the state trajectory  $x(t) \in \mathbb{R}^n$  from the initial condition,  $x_0 \in X_0$  governed by the linear system (3.1) is given by

$$x(t) = e^{At}x_0 + \int_0^t e^{A(t-\tau)} Bu(\tau) d\tau$$

(3.3)

Therefore, the reachable set  $\mathcal{R}(t)$  from the initial conditions  $X_0 \subseteq \mathbb{R}^n$  in the linear system (3.1) is defined by set of state trajectories (3.3) as

$$\mathcal{R}(t) = \{x(t) = e^{At}x_0 + \int_0^t e^{A(t-\tau)} Bu(\tau) d\tau \mid x_0 \in X_0\}.$$

(3.4)

It has been shown in [28] that when each of the input variable u(t) has the form:

$$u(t) = \sum_{j} c_{j} t^{m_{j}} e^{-a_{j}t}$$

(3.5)

where the coefficients  $a_j$ 's and  $c_j$ 's are complex numbers and  $m_j$ 's are non-negative integers, then the time-domain solutions for the state variables x(t) and output variables y(t) governed by (3.1) can be represented by the identical form again. That is, if the set of initial condition  $\mathcal{R}_0$  is specified by vector set  $C = \{v_1, v_2, ..., v_k \in \mathbb{R}^n\}$  by

$$\mathcal{R}_0 = \{\lambda_1 v_1 + \lambda_2 v_2 + \dots \mid v_i \in C, \lambda_i \in \mathbb{R}, i = 1, 2, \dots\}.$$

(3.6)

Recognizing that each vector changes with time t and the scaling factor  $\lambda_i$ 's remains constant, we only need to compute the time evolution of vector  $v_i$ 's; thus, applying the trajectory form of (3.5), we get the identical form with (3.6) having its vector element as trajectory form of (3.5) as:

$$\mathcal{R}(t) = \{x(t) = \sum_{i} \lambda_i v_i(t) \mid v_i(t) = \sum_{j} c_{ij} t^{m_{ij}} e^{-a_{ij}t}, \lambda_i \in \mathbb{R}\}.$$

(3.7)

This general form of the reachable set can express any states x(t) starting from the vector set  $R_0$  including the initial conditions  $X_0$  at arbitrary time t by a linear combination of vector  $v_i$ 's expressed as a set of real coefficients  $\{(Re(c), Im(c), Re(a), Im(a), m)_j, ...\}$ . In addition, a set of states sampled at a specific time instant t',  $\mathcal{R}(t')$  have an identical form with the initial condition set  $\mathcal{R}_0$ , from which we can iteratively compute the discrete change of the input u(t) or the system matrices of the circuit. This concept can be extended to any kind of set representations introduced in the previous chapter. However, we focus on representing a reachable set with zonotope owing to its scalability.

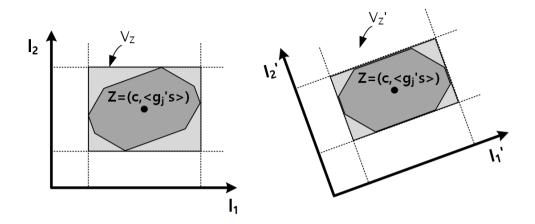

#### 3.1.2 Zonotope Trajectory Form of Reachable Set

Let assume that the range of initial states  $\mathcal{R}(t=0)$  is given as a zonotope  $\mathcal{Z}$ , which is described by a point, referred as center  $c \in \mathbb{R}^n$  and a set of generators  $g_i$ 's  $\in \mathbb{R}^n$  [14]:

$$\mathcal{Z} = (c, \langle g_1, ..., g_r) = \{ c + \sum_{i=1}^r \alpha_i g_i \mid \alpha_i \in [0, 1] \}$$

(3.8)

which is a special case of (3.7) having 1 + r vectors and its scaling factors have range of values  $\lambda_0 = 1$  for center and  $\lambda_i = \alpha_i = [0, 1]$  for k = 1, ..., r for the others. This is the special case of (3.6) when the one of vectors in set C is point c and the other vectors  $g_i$ 's are vectors originating from the point, referred to as an affine combination [29]. Therefore, any point within a zonotope can be expressed as a linear combination of generator  $g_i$ 's from the center c. Its computational complexity for a linear map depends on the number of generators r, yielding

This is also a linear combination of vectors with constant scaling factor  $\alpha_i$  thus we can define its trajectory form of reachable set  $\mathcal{R}_{\mathcal{Z}}(t)$  having input u(t) of (3.5)[30] as:

$$\mathcal{R}_{\mathcal{Z}}(t) = (c(t), \langle g_1(t), ..., g_i(t) \rangle)$$

(3.9)

$$= \{c(t) + \sum_{i} \alpha_{i} g_{i}(t) \mid \alpha_{i} \in [0, 1], g_{i} = \sum_{j} c_{ij} t^{m_{ij}} e^{-a_{ij}t}, \}$$

(3.10)

is the zonotopic trajectory form of the reachable set  $\mathcal{R}_{\mathcal{Z}}(t)$ . For convenience, after that, simply we denote the trajectory form reachable set  $\mathcal{R}(t)$  for the zonotopic trajectory form of reachable set  $\mathcal{R}_{\mathcal{Z}}(t)$ .

## 3.1.3 Computing Trajectory Form using Laplace s-domain Transfer Function

In this subsection, we explain a procedure named *getTrajectoryZonotope()* that computes the trajectory form of  $\mathcal{R}(t)$  from the zonotope range of the initial states  $\mathcal{R}(t = 0)$ defined by zonotope  $\mathcal{Z}$  in (3.8) and the inputs expressed in the form of (3.5). For instance, the time-domain expressions of u(t) in (3.5) can be transformed into the Laplace *s*-domain expression U(s):

$$u(t) = \sum_{j} c_{j} t^{m_{j}} e^{-a_{j}t} \to U(s) = \sum_{j} \frac{b_{j}}{(s+a_{j})^{m_{j}+1}}$$

(3.11)

and the Laplace-domain transform of resulting state trajectory x(t), X(s) can be computed using the matrices in (3.1) as:

$$X(s) = (sI - A)^{-1}BU(s) + (sI - A)^{-1}x(0),$$

(3.12)

which can be transformed back to a time-domain expression in (3.5). The zonotope reachable set  $\mathcal{R}(t)$  is computed by applying this procedure to the vectors of the initial zonotope  $\mathcal{Z}$ . That is, the Laplace transform of vectors in the zonotope  $\mathcal{Z}$  is computed by the same matrices derived from the given circuit as:

$$c(s) = (sI - A)^{-1}BU(s) + (sI - A)^{-1}c(0)$$

(3.13)

$$g_i(s) = (sI - A)^{-1}BU(s) + (sI - A)^{-1}g_i(0),$$

(3.14)

and its time domain solution is given by its inverse Laplace transform

$$c(t) = \sum_{j} c_{0j} t^{m_{0j}} e^{-a_{0j}t}$$

(3.15)

$$g_i(t) = \sum_j c_{ij} t^{m_{ij}} e^{-a_{ij}t}.$$

(3.16)

That is, keeping a set of coefficients  $\{(a_{00}, c_{00}, m_{00}), ..., (a_{ij}, c_{ij}, m_{ij}), ...\}$  in the expression (3.16), one can sample arbitrary states in the reachable set  $\mathcal{R}(t)$  for range of time  $t \in [0, t]$ . Lets define it as the *canonical* form the zonotopic reachable set  $\mathcal{R}(t)$ , which is

$$\mathcal{R}(t) = \{(a, c, m)_{ij} \mid i = (0, ..., r), j = (0, ..., N_p)\}$$

(3.17)

where *a*'s, and *c*'s are complex-numbered vectors  $\in \mathbb{R}^n$  and *m*'s are integers  $\in \mathbb{C}^n$ . The coefficient of i = 0 denotes that of center vector *c* and the others are for those of generators  $g_i$ 's. It has been shown that the coefficients can be computed by the partial fraction decomposition of s-domain expression and the number of coefficients  $N_p$  increase with the number of resulting first order poles in [28]. Therefore, we can express a continuous set of states until time *t* using a zonotope reachable set with *r* generators by  $(r + 1) \times 5N_p$  number of real vectors  $\in \mathbb{R}^n$ .

To avoid redundant matrix computations of the transfer function  $(sI - A)^{-1}$  and  $(sI - A)^{-1}B$ , we define the expression of transfer function

$$H(s) = (sI - A)^{-1}.$$

(3.18)

for the same linear differential equation in (3.1), we keeps the previously computed transfer function H(s) and reuse in the the remaining computation. For example, given a zonotope having comprising two generators  $\mathcal{Z}_0 = (c(0), \langle g_1(0), g_2(0) \rangle)$ , the reachable set from the zonotope  $\mathcal{Z}_0$ , is obtained as c(s) = H(s)(BU(s) + Ec(0)) and  $g_1(s) = H(s)(Eg_1(0)), g_2(s) = H(s)(Eg_2(0))$  in s-domain. The time-domain state of the reachable set can be obtained from the inverse Laplace transform, i.e. the form in (3.16).

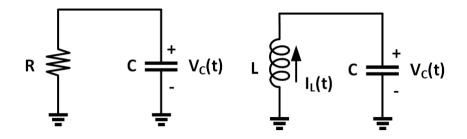

#### 3.1.4 Example: Reachable set of RC circuit

Now, assume that a linear circuit having a resistor R and capacitor C in Fig 3.1 with a range of initial condition  $V_c(0) = [1, 2]$ . Then, applying nodal analysis to the given circuit, the behavior of the state variable  $V_c$  can be represented as a first-order linear

Figure 3.1: Simple exemplary circuits (a) RC circuit (b) LC circuit.

Figure 3.2: Reachable set of the exemplary circuits (a).

system of a state space representation as:

$$\dot{V}_c = -\frac{1}{RC}V_c \tag{3.19}$$

Then, its reachable set  $\mathcal{R}(t)$  of the form (3.17) from the initial condition  $V_c(0)$  can be obtained as:

$$\mathcal{R}_{V_C}(t) = \{ c = (\frac{1}{RC}, 1.5, 1), \langle g_0 = (\frac{1}{RC}, 0.5, 1) \rangle \}$$

(3.20)

This represents the set of trajectories having infinite states from the initial states  $X_0$  until t in the circuit using only two sets of algebraic coefficients. Fig. 3.2 illustrates the resulting reachable set.

#### 3.1.5 Example: Reachable set of LC circuit

In the same manner, the example of LC circuits exhibits harmonic oscillating behavior repeating charging and discharging the LC energy storage elements. The state space representation of the circuit is given by :

$$\dot{I}_L = -\frac{1}{L}V_c \tag{3.21}$$

$$\dot{V}_c = \frac{1}{C} I_L \tag{3.22}$$

and the corresponding system matrix  $A \in \mathbb{R}^2$  can be derived from (3.22) as

$$A = \begin{pmatrix} 0 & -1/L \\ 1/C & 0 \end{pmatrix}.$$

(3.23)

In the same manner, its reachable set  $\mathcal{R}_{LC}(t)$  is defined by a two-dimensional zonotope having a single 2-D generator vector as:

$$\mathcal{R}_{LC}(t) = \{ c = \begin{pmatrix} \{(\frac{1}{RC}, 1.5, 1)\} \\ \{(\frac{1}{RC}, 1.5j, 1)\} \end{pmatrix}, \langle g_0 = \begin{pmatrix} \{(\frac{1}{RC}, 0.5, 1)\} \\ \{(\frac{1}{RC}, 0.5j, 1)\} \end{pmatrix} \rangle \}$$

(3.24)

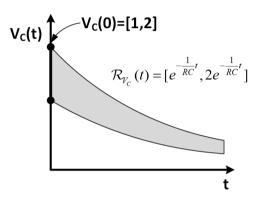

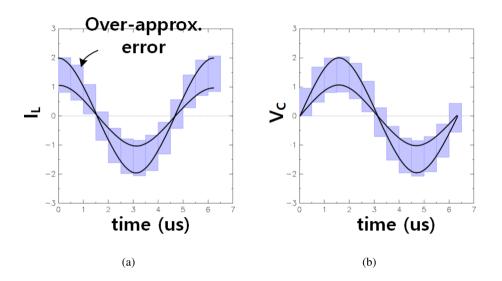

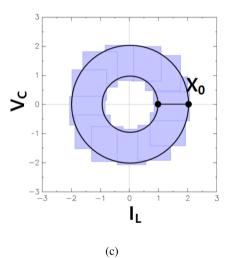

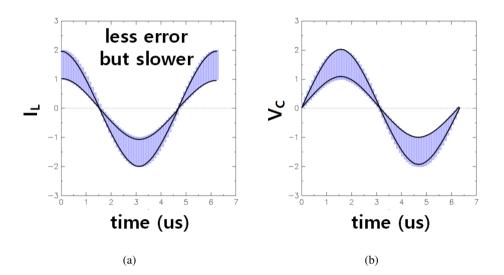

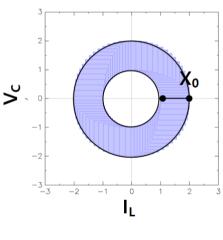

Fig. 3.3 shows that the proposed reachable set of the circuit can accurately represent every state  $x(t) = (I_L(t), V_c(t))$  from  $x_0 \in X_0$  with respect to a single period of time  $t \in [0, 2\pi\sqrt{LC}]$  by a linear sum of the trajectory of center point c(t) and scaled generator vector  $g_1(t)$ . Each circuit element has the value of  $L = 1 \mu$ H and  $C = 1 \mu$ F, respectively, resulting in the harmonic oscillation with the frequency of  $\omega_0 = 2\pi f_0 = 1/\sqrt{LC} = 1 \frac{\text{Mrad}}{\text{s}}$ .

#### 3.1.6 Comparison with Existing Algorithms

Conventional reachability analysis algorithm iteratively computes the reachable set at each time step  $t_k = \{k\Delta t \mid k = 0, ..., N_t\}$  where the size of the unit time step  $\Delta t = T/N_t$ , resulting in the trade-off between the accuracy and the runtime of the computation of reachable sets. In this subsection, we compare the results of the equivalent LC harmonic oscillator system performed in SpaceEx.

(c)

Figure 3.3: Reachable set of the LC harmonic oscillator circuit. (a)  $I_L$ -t (b)  $V_C$ -t (c)  $V_C$ - $I_L$ .

Fig. 3.4 shows the reachable set computed using the size of the unit time step  $\Delta t = 0.5 \,\mu$ s. It took 0.004 s to compute a single period of oscillation but exhibits a large over-approximation error compared to the ideal time-domain response having a form of sine wave as shown in Fig. 3.3. With finer time steps of  $\Delta t = 0.1 \,\mu$ s, it shows a more accurate reachable set compared to the ideal one, but the computation time increased 5× than that of coarse time steps. Furthermore, if the circuit operates with a higher frequency, this discrepancy would become larger, which is the problem

Figure 3.4: Reachable set in SpaceEx (a)  $I_L$ -t (b)  $V_C$ -t (c)  $V_C$ - $I_L$ .

that recent reachability analysis suffers from. The proposed trajectory-form reachable set can obtain the exact reachable set within  $26 \,\mu\text{s}$ , outperforming the conventional algorithm by  $69 \times$ .

(c)

Figure 3.5: Reachable set in SpaceEx (a)  $I_L$ -t (b)  $V_C$ -t (c)  $V_C$ - $I_L$ .

## 3.2 Hybrid System Reachability Analysis

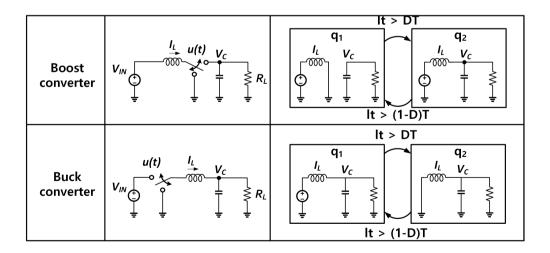

#### 3.2.1 Hybrid System Representation of AMS Circuits

Analog and mixed-signal circuits are in general non-linear so they require hybrid system representation, i.e. hybrid automata. This is a finite state machine that has continuous and discrete variables, of which each discrete state  $q \in Q$  has continuous states  $x \in X \subseteq \mathbb{R}^n$  that operate as a different linear system represented by a set of differential-algebraic equations F. Mixed signal circuits change their discrete states that represent the topology of the circuit depending on the state of the switches connecting the remaining circuit. Then, in the selected linear system, the time evolution of the continuous variable x(t) is iteratively computed from the set of continuous states  $x_0 = x(t')$  in the previous discrete state. The resulting hybrid automata are defined by  $M = \langle Q, X, F, E, G \rangle$  where E is a set of discrete transitions that describe the switching condition of the circuit, and  $\mathcal{G}$  is a set of guard condition that determines when to transit to next discrete state.

#### 3.2.2 Hybrid System Reachability Analysis Using Trajectory Form

From the hybrid automata M representing a given circuit and the initial conditions  $X_0 \subseteq X$  and  $q_0 \in Q$ , the proposed algorithm computes the reachable set  $\mathcal{R}(t)$  of the continuous variable  $x(t) \subseteq X$  and discrete variable  $m(t) \subseteq Q$ . The resulting hybrid reachable set is a series of tuples consisting of values of discrete state m(t) and each continuous reachable set  $\mathcal{R}_{\zeta}(t)$  and the corresponding each time segment  $[t_{\zeta-1}, t_{\zeta}]$  the trajectory form of the reachable set  $\mathcal{R}(t)$  of (3.16) as :

$$\mathcal{R}(t) = \{ (m_1, [t_0, t_1], \mathcal{R}_1(t)), (m_2, [t_1, t_2], \mathcal{R}_2(t)), ..., (m_{\zeta}, [t_{\zeta-1}, t_{\zeta}], \mathcal{R}_{\zeta}(t), ...) \}$$

(3.25)

where  $\zeta$  is the index of each time period of operating the linear system of  $\zeta$ -th discrete state of the sequence  $m_{\zeta} \in Q$ .

Algorithm 1 summarizes the described iterative procedure to compute the reachable set with given conditions. This assumes the number of cycles for analysis is bounded to  $N_{cycle}$  to avoid undecidable conditions such as infinite loops. In each loop, the procedure *GetTrajectoryZonotope()* computes the reachable set of continuous state x(t) in the discrete state  $m(t) = q_{\zeta}$ , i.e.  $\mathcal{R}_q(t), t \in [t_{\zeta}, t_{\zeta+1}]$  using the trajectory form in (3.16). This begins with the last set of states sampled at the previous discrete state Algorithm 1: Computing hybrid reachable set  $\mathcal{R}(t)$ .

Input : M,  $(q_0, Z_0)$ Output:  $\mathcal{R}(t)$  $\mathcal{R}(t) \leftarrow \emptyset$ ; 2 for  $\zeta \in (1, ..., N_{cycle})$  do  $\begin{vmatrix} \mathcal{R}_j(t) \leftarrow GetTrajectoryZonotope(\zeta, Z_0) \triangleright \zeta$ -th trj. form  $(q', t_{\zeta+1}) \leftarrow GetNextState(\zeta, \mathcal{R}_{\zeta}(t))$ ;  $\mathcal{R}(t) \leftarrow \mathcal{R}(t) \cup \{(q_0, [t_{\zeta}, t_{\zeta+1}], \mathcal{R}_{\zeta}(t))\};$  $q_0 \leftarrow q'$ ;  $\begin{vmatrix} Z_0 \leftarrow \mathcal{R}_{\zeta}(t_{\zeta+1} - t_{\zeta}); \\ \mathbf{8} \text{ end} \\ \mathbf{9} \text{ return } \mathcal{R}(t) \end{vmatrix}$

at  $t_{\zeta}$ ,  $Z_0$ . It returns the resulting reachable set  $\mathcal{R}_{\zeta}(t)$  for the time range  $t = [t_{\zeta}, t_{\zeta+1}]$ . The hybrid reachability analysis algorithm iteratively computes the reachable set using this procedure until the bounded number of cycles  $N_{cycle}$ . Then, the procedure *GetNextState* determines the next value of the continuous and discrete states, q' and  $\mathcal{R}_{\zeta}(t_{\zeta+1} - t_{\zeta})$  from the next beginning time  $t_{\zeta+1}$  by computing the guard intersection  $\mathcal{R}_{\zeta}(t) \cap \mathcal{G}$ . However, in this section, we limit the scope of analysis by assuming that the guard set is only set for the time variable t, i.e. timed automata with a hybrid system, not by the internal continuous state variable x(t), which will be discussed at the next chapter.

#### 3.2.3 Example: Switched RC Circuit

As an illustrative example, we analyze the behavior of an AMS circuit, switched RC circuit controlled by input pulses for switches. It is simple but represents the basic building block of a wide range of circuit applications such as charge pumps, DRAM cells, and other switching power supplies. This can be equivalently modeled by a switched linear system as previously studied in [28].

Figure 3.6: Switched RC Circuit with cyclic pulse inputs and the corresponding linear circuits.

Fig. 3.6 shows the circuit under analysis, which changes its discrete state  $q \in Q$ depending on the input level  $V_{sw}$  of the switch transistor, which is often controlled by pulse-width modulation or pulse-frequency modulation control. We assume it has two discrete states  $q_1, q_2 \in Q$  and switched depending on the  $T_{on}, T_{off}$ , periodically, where  $q_1$  corresponds to the charging state where the external voltage  $V_{IN}$  charges the capacitor C and  $q_2$  is discharging state where the charges in the capacitor C discharges to the shunt resistor R. When the input  $V_{sw}$  is larger than the threshold of the transistor  $(q = q_1)$ , the control switch is turned on or is turned off  $(q = q_2)$ , elsewhere. Therefore, the set of discrete transitions depending on the switch state q is defined by  $E = \{q_1 \rightarrow q_2(\text{sw:off}), q_2 \rightarrow q_1(\text{sw:on})\}$ . Each linear system corresponding to two discrete states  $q_1$  and  $q_2$  is derived using basic circuit analysis as :

$$\dot{V}_c = -(\frac{1}{RC} + \frac{1}{R_{ON}C})V_c + \frac{1}{R_{ON}C}V_{IN} \text{ for } q_1$$

(3.26)

$$\dot{V}_c = -\frac{1}{RC} V_c \text{ for } q_2 \tag{3.27}$$

The trajectory form from (3.27) can be solved by using the Laplace technique in

(3.25). For switch on state  $q_1$ , the resulting trajectory-form reachable set is :

$$V_c(s) = \frac{V(0)}{s + \frac{1}{RC} + \frac{1}{R_{ON}C}} + \frac{1}{s + \frac{1}{RC} + \frac{1}{R_{ON}C}} \cdot \frac{V_{IN}}{sR_{ON}C}$$

(3.28)

The second term in (3.28) results in two sets of coefficients by the partial fraction decomposition  $\frac{a'}{s} + \frac{b'}{s + \frac{1}{RC} + \frac{1}{R_{ONC}}}$  where  $b' = -a' = \frac{V_{IN}}{R_ON} / (\frac{1}{RC} + \frac{1}{R_{ONC}})$ . That is, we require three tuples of coefficients for representing the voltage  $V_c$  when the circuit is in the charging state  $q_1$  with a range of initial condition  $V_c(0) = [V_{c,lb}, V_{c,ub}]$ . Therefore, the resulting reachable set is given by :

$$\mathcal{R}_{q_1}(t) = \{ c = \{ (\omega_{p1}, V'_c, 1), (\omega_{p2}, a', 1), (\omega_{p1}, b', 1) \} \\ \langle g = \{ (\omega_{p1}, V''_c, 1), (\omega_{p2}, a', 1), (\omega_{p1}, b', 1) \rangle \}$$

(3.29)

where at the beginning of the analysis the initial voltage is given by  $V'_c = (V_{c,lb} + V_{c,ub})/2$  and  $V''_c = (V_{c,lb} - V_{c,ub})/2$  for the center  $c_{q1}$  and the generator  $g_{q1}$ , respectively, and each system pole  $\omega_{p1} = \frac{1}{RC} + \frac{1}{R_{ONC}}$  and  $\omega_{p2} = 0$ . The reachable set in discharging state  $q_2$  also can be solved in the same manner, yielding :

$$\mathcal{R}_{q_2}(t) = \{ c = (\omega_p, V'_c, 1), \\ \langle g = (\frac{1}{RC} + \frac{1}{R_{ON}C}, V''_c, 1) \rangle \}$$

(3.30)

where the initial values  $V'_c$  and  $V''_c$  are computed at the last time in the previous discrete state  $q_1$ . The resulting reachable set is given by a set of (3.29) and (3.30).

$$\mathcal{R}(t) = \{ (q_1, [t_0, t_1], \mathcal{R}_{q_1}(t)), \\ (q_2, [t_1, t_2], \mathcal{R}_{q_2}(t)), ... \\ (q_1, [t_2, t_3], \mathcal{R}_{q_1}(t)), \\ (q_2, [t_3, t_4], \mathcal{R}_{q_2}(t)), ... \}$$

(3.31)

## **Chapter 4**

# HYBRID SYSTEM REACHABILITY ANALYSIS OF NONLINEAR CIRCUIT

We discussed the hybrid system with linear circuits in the previous chapter. In this chapter, we present the methodology for the hybrid system including nonlinear circuit behavior [31].

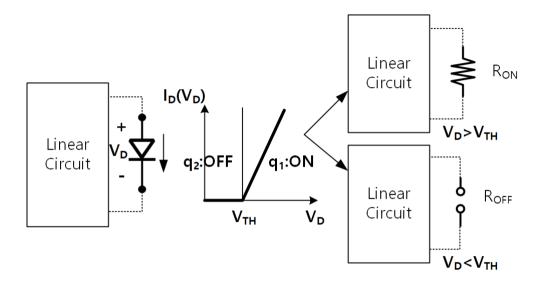

## 4.1 Piecewise-Linear Modeling of AMS Circuits

The most prevalent approach for analyzing nonlinear circuits is to model them as a piecewise-linear (PWL) system that divides a state space having nonlinear dynamics into several regions operating in linear systems. It has been announced that most analog circuits are nonlinear owing to two nonlinear elements, diodes, and MOSFETs; their non-linear characteristics are efficiently and accurately modeled by PWL model with the threshold voltage  $V_{TH}$  and the on-resistance  $R_{ON}$  [26].

As shown in Fig. 4.1, when any circuit has a diode, the circuit can be represented by two linear systems depending on the terminal voltage  $V_D$ , and each linear system is represented in two systems having  $R_{ON}$  and  $R_{OFF}$  (or open). In addition, the MOS-FET characteristics also can be efficiently represented with two PWL diodes, and the resulting system would be partitioned by four linear systems. Using this PWL parti-

Figure 4.1: PWL partitioning of the circuit with a diode.

tioning, we can model a nonlinear AMS circuit and apply hybrid reachability analysis.

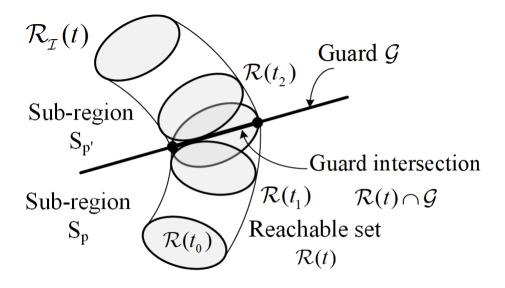

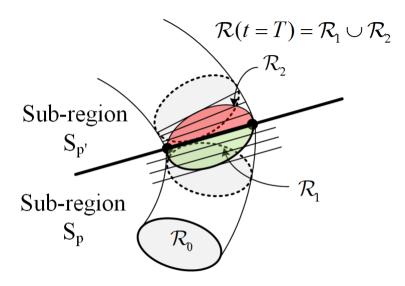

### 4.2 Piecewise-Linear Approximation of Nonlinear Circuits

In the PWL approximation, the continuous state space of a non-linear system is partitioned into a set of disjoint sub-regions  $\{S_1, ..., S_p, ..., S_{N_r}\}$ , and the continuous state  $x(t) \in S_p$  is governed by a different linear system depending on the sub-region x(t)belong to, where each sub-region  $S_p$  for  $p = 1, ..., N_r$  corresponds to the discrete state  $d(t) \in \{1, ..., N_r\} \in Q_d$ . The key challenge in computing the reachable set  $\mathcal{R}(t)$  of x(t) and d(t) (or with m(t)) representing the change of linear system due to time t lies mainly with computing the guard intersection  $\mathcal{R}(t) \cap \mathcal{G}$ . This chapter addresses how to compute this guard intersection of continuous state x(t) efficiently and accurately.

The challenges in computing the guard intersection  $\mathcal{I} = \mathcal{R}(t) \cap \mathcal{G}$  in conventional methods are two-fold. First, when the reachable set  $\mathcal{R}(t)$  is evaluated at discrete steps of time t, the guard intersection must be computed repeatedly for each time step, incurring a large computational cost. In addition, this cost further increases when comput-

Figure 4.2: The problem of computing the guard intersection  $\mathcal{R}(t) \cap \mathcal{G}$  in PWL system representation.

ing the subsequent reachable set from the guard intersection  $\mathcal{I}$  since each intersection requires computing the successor reachable set  $R_{\mathcal{I}}(t)$ , resulting in the exponential increase of runtime with respect to the number of guard intersection, referred to *cycles* here.

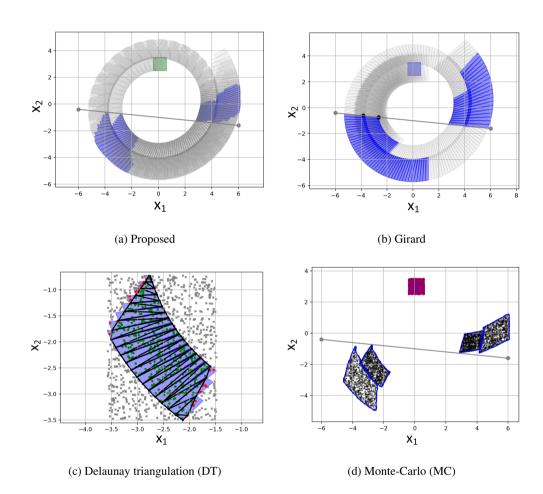

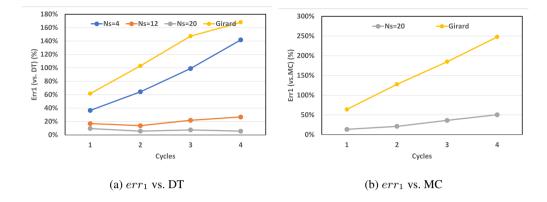

To address this challenge, this work proposed an efficient, scalable way of computing the guard intersection of reachable set  $\mathcal{R}(t)$  represented in a trajectory form of (3.16). In the previous chapter, it has been shown that for linear hybrid systems, computing the time evolution of  $\mathcal{R}(t)$  within a region  $S_i$  does not need the evaluation of  $\mathcal{R}(t)$  at discrete steps of time. Instead  $\mathcal{R}(t)$  can be represented using a set of vertices, where each vertex follows a trajectory described by an exact and analytical function of time t of (3.7). The proposed method can compute the intersection of  $\mathcal{R}(t)$ in this trajectory form with a linear guard  $\mathcal{G}$ , and also a new reachable set  $\mathcal{R}(t)$  starting from the computed intersection  $\mathcal{I}$ , both in the trajectory forms that do not rely on time discretization. The proposed method also adopts the scalable method in [15] that computes the intersections in the high-dimensional state space using only two-dimensional operations via projections.

## 4.3 Computing Guard Intersections at PWL Switching Boundary

#### 4.3.1 Hybrid System Representation of PWL circuits

The continuous state space of the PWL approximated circuit is partitioned into a set of sub-regions  $S_p$  for  $p = 1, ..., N_p$  by a set of linear hyperplane guards  $\mathcal{G}'s$ :

$$\mathcal{G}_h: w_h \cdot x + b_h = 0 \text{ for } h = 1, 2, \dots$$

(4.1)

where  $w_h \in \mathbb{R}^n$  is an unit vector normal to each hyperplane and  $b_h \in \mathbb{R}^n$  is an offset. Within a sub-region  $S_p$  and for a given discrete state  $d(t) \in 1, ..., q$ , the continuous state variable  $x(t) \in \mathbb{R}^n$ , the input  $u(t) \in \mathbb{R}^{n_i}$ , and the output  $y(t) \in \mathbb{R}^{n_o}$  are governed by a linear differential equation :

$$\dot{x}(t) = A_p x(t) + B_p u(t),$$

$$y(t) = C_p x(t) + D_p u(t)$$

(4.2)

where  $A_p \in \mathbb{R}^{n \times n}$ ,  $B_p \in \mathbb{R}^{n \times n_i}$ ,  $C_p \in \mathbb{R}^{n_o \times n}$ , and  $D_p \in \mathbb{R}^{n_o \times n_i}$ ; and p denotes the index of the operating sub-region of PWL system. Then, the trajectory of x(t) starting from an initial state  $x_0$  can be represented by the hybrid system trajectory form  $\mathcal{R}(t)$  of (3.25). Each transfer function  $H_p(s) = (sI - A_p)^{-1}$  for the system matrices in (4.2) is computed in the same manner in the previous chapter, indexed by the sub-region  $S_p$ .

#### 4.3.2 Computing Guard Intersection Using Trajectory Form

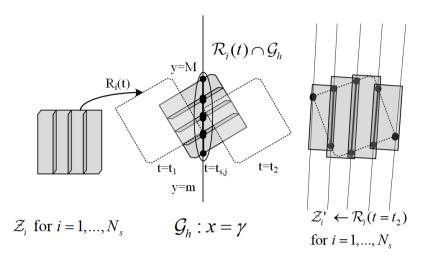

This section describes the proposed algorithm for computing the guard intersection  $\mathcal{I} = \mathcal{R} \cap \mathcal{G}_h$ . For a zonotope reachable set  $\mathcal{R}(t)$  in (3.16) and a hyperplane guard  $\mathcal{G}_h$  in (4.1), using a set of orthogonal unit vectors  $l_k$ 's to the vector  $w_h$  of the guard  $\mathcal{G}_h$ . The pseudo-codes of the overall algorithm are listed in Algorithm 2.

Figure 4.3: The overall algorithm to compute the guard intersection at the disjoint regions  $S_p$  and  $S_{p'}$ .

The algorithm first obtains the reachable set in the initial sub-region  $S_p$  as:

$$\mathcal{R}_{\bar{i}}(t) = getTrajectoryZonotope(p, \mathcal{Z}_{\bar{i}}).$$

(4.3)

where p is the index for the corresponding linear system and  $\bar{i}$  denotes the index for the initial zonotopes, previously segmented by  $\bar{i} = 1, ..., N_s$ . Then, the reachable set in the sub-region  $S_p$  is added by  $\mathcal{R}(t) = \mathcal{R}(t) \cup \{\mathcal{R}_{\bar{i}}(t)\}$  at each iteration of  $\bar{i} = 1, ..., N_s$ .

Then, the algorithm can determine the time range  $[t_1, t_2]$  for which the intersection  $\mathcal{R} \cap \mathcal{G}_h \neq \emptyset$ . The procedure named *findCrossZonotope()* finds the values of  $t_1$  and  $t_2$  by solving the equation

$$c(t)w_h + \sum_i |g_i(t) \cdot w_h| = 0$$

(4.4)

iteratively until the time t reaches the maximum time bound T.

Since the guard intersection  $\mathcal{R}(t) \cap \mathcal{G}$  does not yield a closed-form expression in terms of t, the algorithm computes the approximate intersections of  $\mathcal{R}(t)$  sampled at  $N_s + 1$  time steps spanning the range  $[t_1, t_2]$  as :

$$t_{s,\bar{j}} = t_1 + \bar{j} \frac{t_2 - t_1}{N_s} \text{ for } \bar{j} = 1, ..., N_s$$

(4.5)

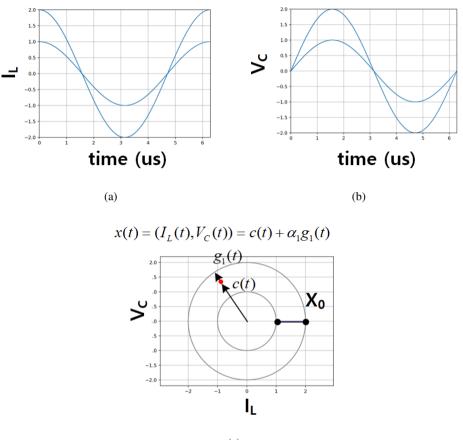

Figure 4.4: Search process for the best  $l_k$ 's in the procedure for approximating  $\mathcal{R}(t) \cap \mathcal{G}$ with low over-approximation error *getOrthogonalBasis*.

In addition, this algorithm adopts the projection method introduced in [15], which computes the guard intersection of the reachable set  $\mathcal{R}(t)$  projected into a two-dimensional space instead of the original high-dimensional reachable set  $\mathcal{R}(t)$  itself. The resulting intersections are obtained as the same zonotopes using the same set of projection vectors  $l_k$  for k = 1, ..., n - 1, which are easy to combine with the subsequent step of computing the reachable set explained in the next section.

The procedure *getOrthogonalBasis()* finds the set of optimal orthogonal basis vectors

$$D = \{l_k \in \mathbb{R}^n \mid k = 1, ..., n - 1\}$$

(4.6)

, with which one can describe a minimum-volume hypercube enclosing the zonotope  $\mathcal{R}(t)$  at  $t = t_{mid} = (t_1 + t_2)/2$ . The search process guarantees that one of the basis vectors in D in (4.6) is selected from the generators  $g_j$ 's and finds the set of basis vectors that minimizes the volume computed by the oriented rectangular hull (ORH) as:

$$V = \prod_{k=1}^{n-1} \sum_{i=1}^{r} |g_i \cdot l_k|.$$

(4.7)

Fig. 4.4 illustrates how the procedure chooses the best basis vectors  $l_k$ 's. The initial

selection of  $l_k$ 's shows a large over-approximation of the hypercube from  $l_k$ 's approximating the zonotope  $Z' = \mathcal{R}(t_{mid})$ , whereas when the volume  $V'_{\mathcal{Z}}$  is the minimum among every  $V_{\mathcal{Z}}$ , the hypercube of with  $l_k$  can tightly enclose the zonotope  $\mathcal{Z}$ . This search process assumes that the time evolution of zonotope Z is so slow for the intersecting time range  $[t_1, t_2]$  that the approximation can fit the zonotope well with the chosen  $l_k$ 's when the time in the middle of the period,  $t_{mid}$ . Therefore, it leaves further research issues for the method to find a better basis.

Using the vector  $l_k$  in D, the algorithm projects the zonotope reachable set  $\mathcal{R}(t)$ different two-dimensional planes, each of which is spanned by the normal vector of the guard hyperplane  $w_h$  in (4.1) and one of the basis vectors  $l_k$  for k = 1, ..., n - 1. The projection operator  $\Pi(w_h, l_k)$  [15] is a linear transformation on the trajectory form x(t) in (3.5) defined by

$$\Pi_{w,l_k}(x(t)) = (w \cdot x(t), l_k \cdot x(t)).$$

(4.8)

Note that the resulting dot product of vectors w,  $l_k$  remains with the same form of the reachable set due to linearity.

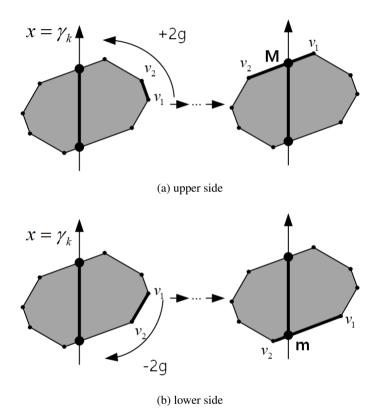

Then, the procedure getIntersect2D() computes the intersection of the zonotope reachable set  $\mathcal{R}_{\bar{i}}(t_{s,\bar{j}})$  for  $\bar{i} = 1, ..., N_s$  sampled at each time step  $t_{s,\bar{j}}$  in (4.5) for  $\bar{j} = 0, ..., N_s$  using the projections on zonotopes  $\prod_{l_k,w}(\mathbb{Z}_{\bar{i}\bar{j}})$  in (4.8) as :

$$\tilde{\mathcal{Z}}_{i\bar{j}k}(t) = (\Pi_{w_h, l_k}(c(t)), \langle (\Pi_{w_h, l_k}(g_1(t)), \Pi_{w_h, l_k}(g_2(t)), \ldots \rangle)$$

(4.9)

where k = 1, ..., (n - 1) and guard hyperplane  $\mathcal{G}_h$  is also projected in the same way, resulting in the line  $x = \gamma_k = b/|w_h|$  in the k-th projected plane as shown in Fig. 4.3. Computing intersection in the projected plane is reduced into simple two-dimensional intersection problems that can be solved in an algebraic way. Given a line segment  $\overline{v_1v_2}$  in a 2-D plane, its intersection with the line  $x = \gamma_k$  is

$$y = (\gamma_k - v_{1x})\frac{v_{2y} - v_{1x}}{v_{2x} - v_{1x}} + v_{1y}$$

(4.10)

where  $v_1 = (v_{1x}, v_{1y})$  and  $v_2 = (v_{2x}, v_{2y})$ . The procedure getIntersect2D() for zonotope initially set the first point  $v_1 = c + g_0$  by picking the generator  $g_0$  so that  $v_1$  is most close to the guard line  $x = \gamma_k$ ; and then, the next point is iterated adding  $2g_{next}$ as:

$$v_{next,1} = v_2$$

$$v_{next,2} = v_2 + 2g_{next}$$

(4.11)

where  $g_{next}$  is picked from the first element in the sorted generators  $g = (g_x, g_y)$ 's in the tangent order (i.e.  $arctan(g_x/g_y)$ ) and this process ends when the sorted set becomes empty. This iteration is performed in two ways, upper and lower side of vertices of the zonotope  $\tilde{Z}_{i\bar{j}k}(t)$  until finding two intersecting values y = M and y = m, respectively. This pair of values indicates the range of scaling factor  $[m, M]_{i\bar{j}k}$  applied to basis vector  $l_k$ . Connecting them with the vector  $l_k$  into a (n-1)-dimensional hypercube yields the approximate intersection of the exact  $\mathcal{R}_{\bar{i}}(t_{s,\bar{j}}) \cap \mathcal{G}$  lying on the guard hyperplane  $\mathcal{G}_h$ .

When computing the guard intersections of multiple reachable sets  $\mathcal{R}_{\bar{i}}(t)$ , sampled zonotopes  $\mathcal{Z}_{\bar{i}\bar{j}}$  shares same direction  $l_k$  at time  $t = t_{s,\bar{j}}$  in the guard-crossing time interval  $[t_1, t_2]$ . The procedure *mergeSegments*() combines the range segments  $[m, M]_{\bar{i}\bar{j}k}$ 's for the same sampling instant  $t = t_{s,\bar{j}}$  and the same basis vector  $l_k$ . This reduces the resulting  $N_s \times N_s$  zonotopes representing the approximate guard intersections to  $N_s$ , yielding the guard intersection by a range of segments

$$\mathcal{I} = \{ [m, M]_{\bar{j}k} \mid \bar{j} = (1, ..., N_s), k = (1, ..., n-1) \}.$$

(4.12)

This procedure prevents the exponential growth of the number of reachable sets, keeping it at  $N_s$ .

#### 4.3.3 Computing Reachable Sets in New Sub-Regions

Algorithm 3 lists the algorithm for computing the  $N_s$  subsequent reachable sets  $\mathcal{R}_{\mathcal{I}}(t)$ from the  $N_s + 1$  guard intersections  $\mathcal{I}$  of (4.12). Note that these intersections are