#### 저작자표시-비영리-변경금지 2.0 대한민국

### 이용자는 아래의 조건을 따르는 경우에 한하여 자유롭게

• 이 저작물을 복제, 배포, 전송, 전시, 공연 및 방송할 수 있습니다.

#### 다음과 같은 조건을 따라야 합니다:

저작자표시. 귀하는 원저작자를 표시하여야 합니다.

비영리. 귀하는 이 저작물을 영리 목적으로 이용할 수 없습니다.

변경금지. 귀하는 이 저작물을 개작, 변형 또는 가공할 수 없습니다.

- 귀하는, 이 저작물의 재이용이나 배포의 경우, 이 저작물에 적용된 이용허락조건 을 명확하게 나타내어야 합니다.

- 저작권자로부터 별도의 허가를 받으면 이러한 조건들은 적용되지 않습니다.

저작권법에 따른 이용자의 권리는 위의 내용에 의하여 영향을 받지 않습니다.

이것은 이용허락규약(Legal Code)을 이해하기 쉽게 요약한 것입니다.

# Ph.D. DISSERTATION

# Characterization of Atomic Layer Deposited Lanthanum Silicate Films for a Gate Oxide of Si and Ge Devices

by

Yu Jin Choi

February 2014

Department of Materials Science and Engineering College of Engineering Seoul National University

# Characterization of Atomic Layer Deposition Lanthanum Silicate Films for a Gate Oxide of Si and Ge Devices

Advisor: Prof. Hyeong Joon Kim

by

# Yu Jin Choi

A thesis submitted to the Graduate Faculty of Seoul National

University in partial fulfillment of the requirements for the

Degree of Doctor of Philosophy

Department of Materials Science and Engineering

February 2014

Approved

by

Chairman of Advisory Committee: Cheol Seong Hwang

Vice-chairman of Advisory Committee: Hyeong Joon Kim

Advisory Committee: Ho Won Jang

Advisory Committee: <u>Jaeyeong Heo</u>

Advisory Committee: Seok-Jun Won

# Abstract

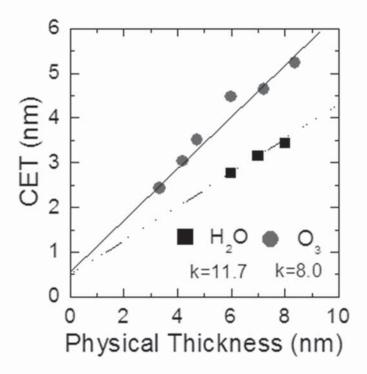

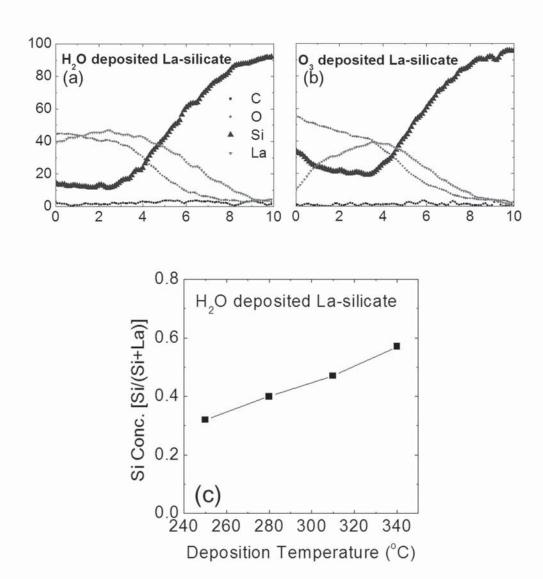

The effect of oxygen sources, i.e.  $O_3$  or  $H_2O$ , on chemical composition, dielectric constant and leakage current density of atomic-layer-deposited La-silicate films on Si substrate was examined. The dielectric constant of La-silicate films grown on Si substrate using  $O_3$  was  $\sim 8.0$ , which was lower than that of La-silicate films grown using  $H_2O$ ,  $\sim 11.7$  due to the higher Si concentrations. However, leakage current density of La-silicate films grown using  $O_3$  was about 3 orders of magnitude lower than that of La-silicate films grown using  $H_2O$  at an identical capacitance-equivalent-thickness (but almost half the physical thickness), due to the higher Si concentrations and less La-carbonate formation.

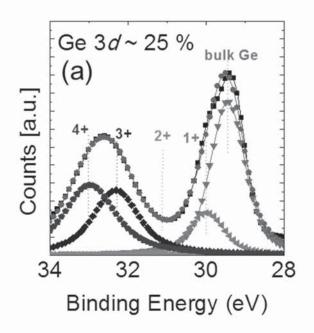

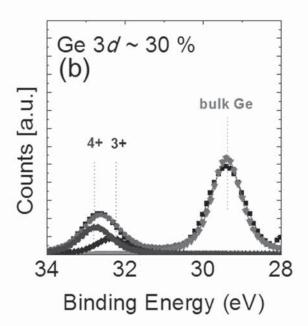

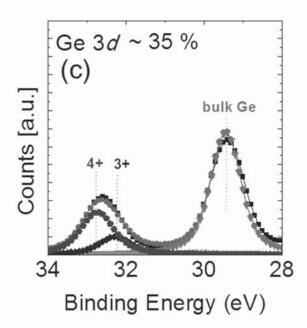

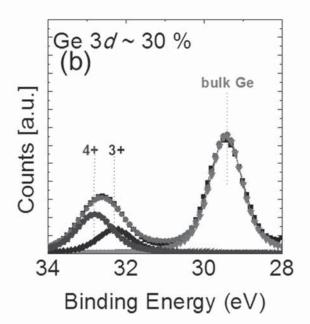

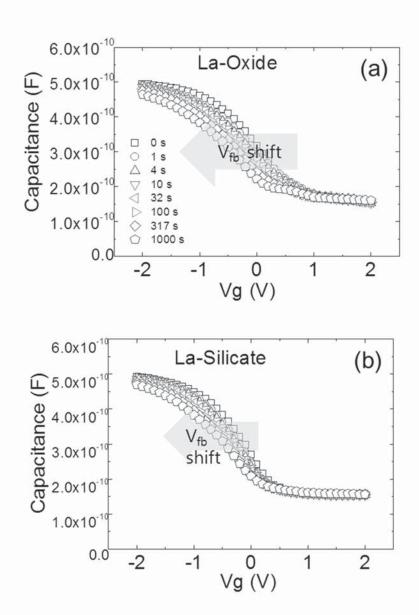

We have investigated the effects of Si concentrations in La-silicate film formed by ALD on Ge substrate of the electric property especially in reduction of C-V hysteresis. La-silicate film with Si concentration increment (~ 25 % to ~ 35 %) on Ge substrate effectively reduced C-V hysteresis due to suppression of Ge sub-oxide generation calculated from XPS analysis.

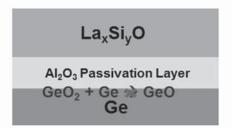

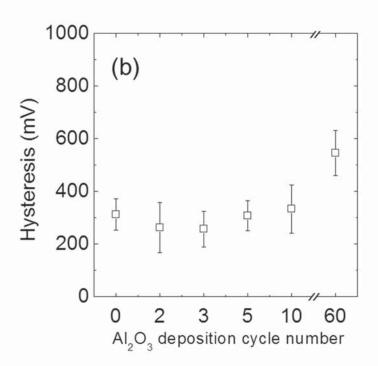

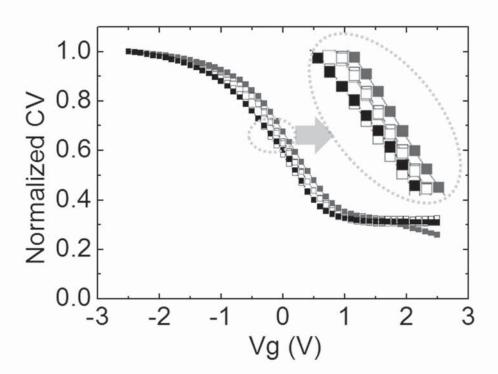

La-silicate film with very thin Al<sub>2</sub>O<sub>3</sub> interface passivation layer on Ge substrate obtained smaller C-V hysteresis as ~238 mV due to lower interface state density by suppression of Ge sub-oxide formation. BEMAS-SiO<sub>2</sub> capping La-silicate film with Al<sub>2</sub>O<sub>3</sub> interface passivation layer showed smaller Ge sub-oxide formation as smaller C-V hysteresis shown. Al<sub>2</sub>O<sub>3</sub> interface passivation La-silicate film and SiO<sub>2</sub> capping La-silicate film with Al<sub>2</sub>O<sub>3</sub> interface passivation layer has tendency of low leakage current density. It is also found that

the Al<sub>2</sub>O<sub>3</sub> thickness of 1–2 monolayer and SiO<sub>2</sub> capping is critical for the reduction of the

interface state density.

In conclusion, the ALD-Al<sub>2</sub>O<sub>3</sub> interfacial passivation layer and SiO<sub>2</sub> capping, whose

thickness can be precisely controlled, is effective for controlling the formation of Ge

oxides at high-k/Ge interfaces.

Keywords : high-κ, ALD, La-silicate, La<sub>2</sub>O<sub>3</sub>, Al<sub>2</sub>O<sub>3</sub>, SiO<sub>2</sub>, Si, Ge, deposition behavior,

Ozone, leakage current mechanism, XPS

Student Number: 2009-30899

Yu Jin Choi

ii

# **Table of contents**

| Abstracti                                                              |

|------------------------------------------------------------------------|

| Table of contentsiii                                                   |

| List of Tablesvii                                                      |

| List of Figures Viii                                                   |

|                                                                        |

| I. Introduction                                                        |

|                                                                        |

| II. Literature Review                                                  |

| 2.1. Scaling limit for Si-based gate oxide7                            |

| 2.2. High-k gate dielectric                                            |

| 2.2.1. Necessity for high-k dielectric                                 |

| 2.2.2. La-based Oxide films                                            |

| 2.3. High mobility channel Ge                                          |

| 2.3.1. Desorption and disproportionation characteristics of Ge oxide22 |

| 2.3.2. Introduction for Ge Passivation Techniques                      |

| 2.3.3. Oxidation treatment                                             |

| 2.3.4. Nitridation                                                     |

| 2.3.5. Direct Deposition of high- <i>k</i> Dielectrics                                                                             |

|------------------------------------------------------------------------------------------------------------------------------------|

| 2.3.6. Si-Passivation                                                                                                              |

| 2.3.7. Sulfur Passivation                                                                                                          |

| 2.4. Interface characterization techniques                                                                                         |

| 2.4.1. Conductance Method                                                                                                          |

|                                                                                                                                    |

| III. Experiments and Analysis                                                                                                      |

| 3.1. Atomic Layer Deposition of La-based oxide                                                                                     |

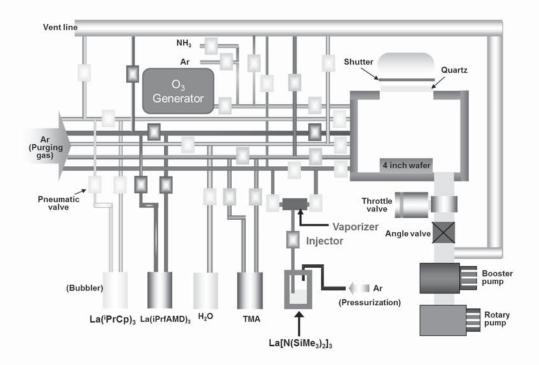

| 3.1.1. Deposition of La-silicate thin films using La[N(SiMe <sub>3</sub> ) <sub>2</sub> ] <sub>3</sub> precursor with liquid       |

| injection system58                                                                                                                 |

| 3.1.2. Deposition of La-oxide thin films using La(iPrCp) <sub>3</sub> with bubbler system66                                        |

| 3.2. Atomic Layer Deposition of various passivation interfacial layers and capping                                                 |

| layers70                                                                                                                           |

| 3.2.1. La-silicate thin films as a bulk layer on Ge and as a passivation interface layer                                           |

| of HfO <sub>2</sub> film using La[N(SiMe <sub>3</sub> ) <sub>2</sub> ] <sub>3</sub> , BEMAS and BDEAS-SiO <sub>2</sub> precursor70 |

| 3.2.2. Deposition of Si concentration controlled La-silicate thin films using                                                      |

| La[N(SiMe <sub>3</sub> ) <sub>2</sub> ] <sub>3</sub> , BEMAS and BDEAS-SiO <sub>2</sub> precursor74                                |

| 3.2.3. Deposition of SiO <sub>2</sub> and Al <sub>2</sub> O <sub>3</sub> passivation interface layers and capping layers           |

| for La-Silicate thin film                                                                                                          |

| 3.2.4. Deposition of ultra-thin Al <sub>2</sub> O <sub>3</sub> passivation interface layers for La-Silicate                        |

| thin film                                                                                                                          |

| 3.2.5. Deposition of Multi-stack La-silicate thin film. (Ultra-thin Al <sub>2</sub> O <sub>3</sub> passivation                       |

|--------------------------------------------------------------------------------------------------------------------------------------|

| interface layers and SiO <sub>2</sub> capping layer)                                                                                 |

| 3.3. Sample preparation and analyses of the deposited film83                                                                         |

|                                                                                                                                      |

| IV. Results and Discussions84                                                                                                        |

| 4.1. La-Silicate thin film on Si substrate84                                                                                         |

| 4.1.1. Introduction                                                                                                                  |

| 4.1.2. Deposition characteristics and Electrical properties of La-silicate                                                           |

| 4.1.3. MOSCAP fabrication89                                                                                                          |

| 4.1.4. Electrical and Chemical Analysis of La-silicate film with different oxidants91                                                |

| 4.1.5. Band gap Analysis of La-silicate film with different oxidants99                                                               |

| 4.2. La-silicate film on Ge on substrate                                                                                             |

| 4.2.1. Introduction                                                                                                                  |

| 4.2.2. Effects of La-silicate film as passivation layer of HfO <sub>2</sub> film107                                                  |

| 4.2.3. Effects of Si concentrations in La-based oxide film                                                                           |

| 4.2.4. Effect of SiO <sub>2</sub> and Al <sub>2</sub> O <sub>3</sub> as passivation interface layer and capping layer of La-silicate |

| film126                                                                                                                              |

| 4.2.5. Adoption of Al <sub>2</sub> O <sub>3</sub> interface passivation layer                                                        |

| $4.2.6.\ Multi \ stack\ layer:\ La-silicate\ film\ with\ Al_2O_3\ passivation\ and\ SiO_2\ capping\ layer\ \dots 148$                |

|                                                                                                                                      |

| V. Conclusions161                                                                                                                    |

| VI. References               | 164 |

|------------------------------|-----|

| List of related publications | 178 |

| Abstract (in Korean)         | 186 |

# **List of Tables**

- Table 2-1. Conduction band offset to conduction band of Si  $(\Phi_b)$ , tunneling effective masses  $(m_{eff})$ , and relative permittivities (k) for several gate dielectrics.

- Table 2-2. Electric characteristics of  $La_2O_3$  and  $HfO_2$ , dielectric constant (k), bandgap ( $E_g$ ), conduction band offset (CBO), merits and drawbacks.

- Table 2-3. The characteristics of several potential channel materials at 300 K.

- Table 2-4. Material characteristics of Ge oxide and Si oxide.

- Table 2-5. Co-ordination of the different metals in the GeO<sub>x</sub> matrix after geometry relaxation of GeMO<sub>2</sub>/Ge (100) structures.

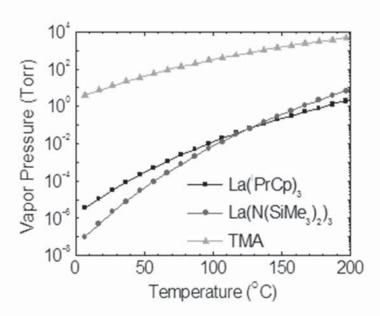

- Table 3-1. Vapor Pressure and Melting point for La metal precursors.

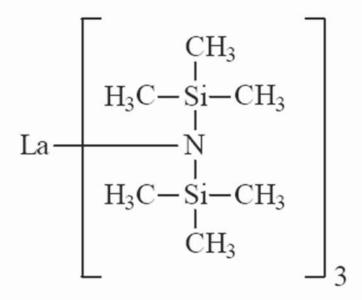

- Table 3-2. Physical and chemical properties of La[N(SiMe<sub>3</sub>)<sub>2</sub>]<sub>3</sub> precursor.

- Table 3-3. Process conditions of thermal ALD grown with La[N(SiMe<sub>3</sub>)<sub>2</sub>]<sub>3</sub>.

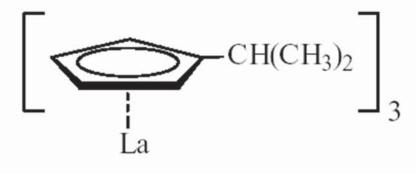

- Table 3-4. Physical and chemical properties of La(iPrCp)<sub>3</sub>.

- Table 3-5. Process conditions of thermal ALD grown with La(iPrCp)<sub>3</sub>.

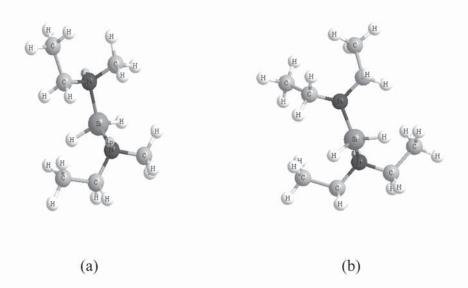

- Table 3-6. Physical and chemical properties of SiH<sub>2</sub>(NC<sub>2</sub>H<sub>5</sub>CH<sub>3</sub>)<sub>2</sub> (BEMAS) and SiH<sub>2</sub>(N(C<sub>2</sub>H<sub>5</sub>)<sub>2</sub>)<sub>2</sub> (BDEAS) precursor.

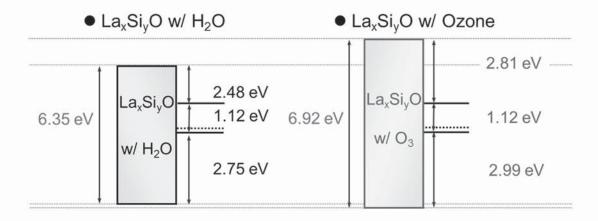

- Table 4-1. The deduced VBO, E<sub>g</sub> and CBO of La-silicate grown with H<sub>2</sub>O and O<sub>3</sub>.

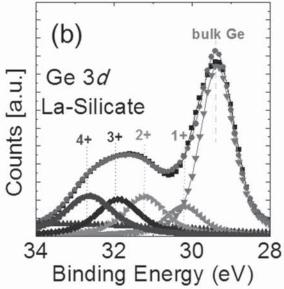

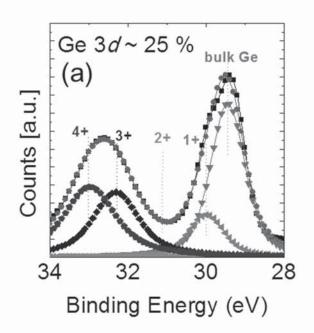

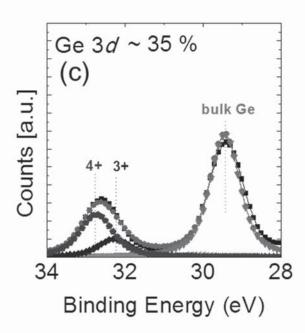

- Table 4-2. Ge 3*d* spectra related to Ge oxide (Ge<sup>1+</sup>, Ge<sup>2+</sup>, Ge<sup>3+</sup> and Ge<sup>4+</sup>) with BE shifts of 0.8, 1.8, 2.6, and 3.4 eV from Ge bulk peak.

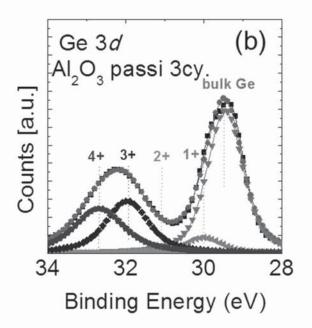

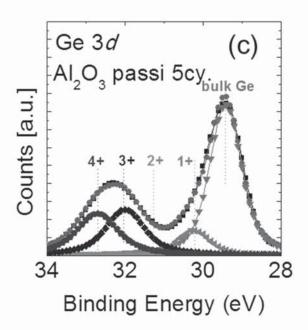

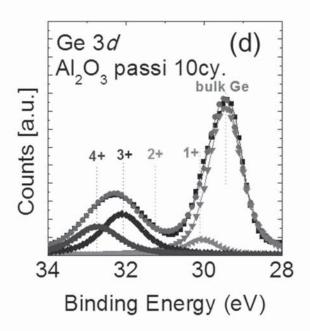

- Table 4-3. Ge 3d core level for the La-silicate film with various deposition cycles of ultra-thin Al<sub>2</sub>O<sub>3</sub> passivation interface layer related to Ge oxide with BE shifts from Ge bulk peak.

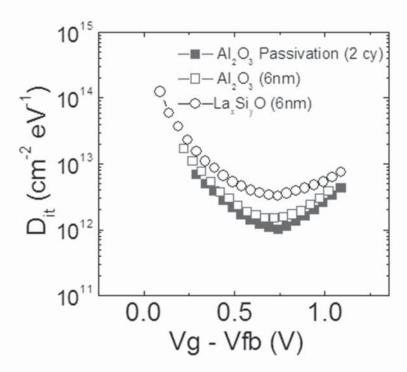

- Table 4-4. C-V hysteresis, XPS GeO BE shift from Ge bulk peak, D<sub>it</sub> and V<sub>fb</sub> shift from CVS measurement for La-silicate/Ge and La-silicate/Al<sub>2</sub>O<sub>3</sub> (2 cycles)/Ge.

- Table 4-5. C-V hysteresis, XPS GeO BE shift from Ge bulk peak, D<sub>it</sub> and V<sub>fb</sub> shift from CVS measurement for BEMAS- and BDEAS SiO<sub>2</sub> capped La-silicate Al<sub>2</sub>O<sub>3</sub> (2 cycles) interface passivation layer on Ge.

# **List of Figures**

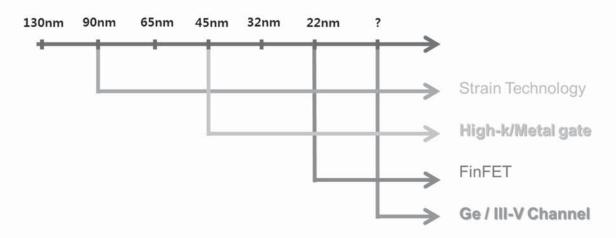

- Figure 1-1. Schematic diagram of CMOS scaling trend.

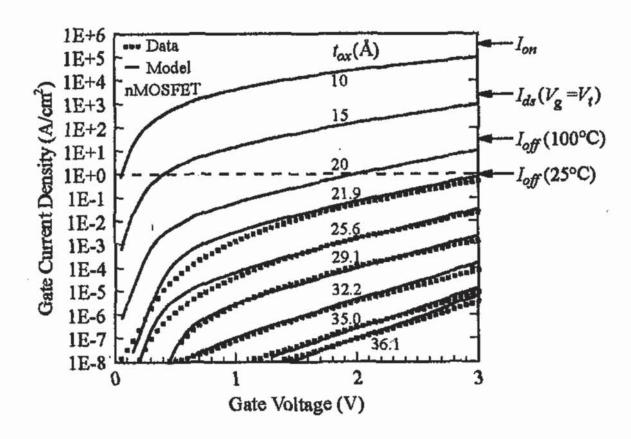

- Figure 2-1. Measured and calculated oxide. Tunneling current versus gate voltage for different oxide thicknesses.

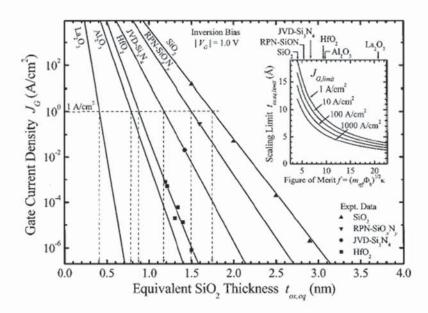

- Figure 2-2. Gate current density J<sub>G</sub> at a fixed inversion gate bias as a function of the equivalent oxide thickness t<sub>ox,eq</sub>. for five different gate dielectrics. Solid lines are from the model, Extraction of gate dielectric scaling limits is also shown based on a maximum tolerable gate leakage J<sub>Glimit</sub> of 1 A/cm<sup>2</sup> and the supply voltage V<sub>DD</sub> of 1 V. Scaling limits as a function of the gate dielectric figure of merit is described in the inset.

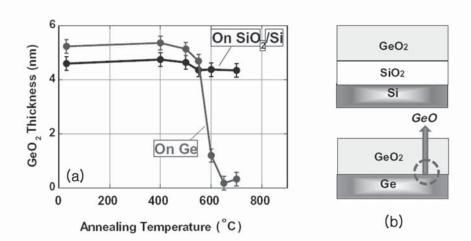

- Figure 2-3. (a) GeO<sub>2</sub> thickness changes on Ge and on SiO<sub>2</sub>/Si as a function of annealing temperature and (b) Schematic view of GeO desorption in GeO<sub>2</sub>/SiO<sub>2</sub>/Si stack vs. GeO<sub>2</sub>/Ge stack.

- Figure 2-4. Schematics of GeO desorption mechanism from GeO<sub>2</sub>/Ge stacks.

- Figure 2-5. XPSpectra Ge 3d peak core spectra for Ge disproportionation effect for GeO generate  $GeO_2 + Ge$  in terms of annealing temperature.

- Figure 2-6. XPSpectra of (a) Ge 3d and (b) Si 2p core level spectra as a function of annealing temperature for the ultra thin oxide layers on the Ge and Si surface, respectively.

- Figure 2-7. Bidirectional C-V characteristics of GeO<sub>2</sub> MOSCAP on Ge, Si, and thermally oxidized Si substrates, fabricated by a conventional PDA treatment at 600°C.

- Figure 2-8. Large C-V hysteresis for HfO<sub>2</sub>/GeO<sub>2</sub>/p-Ge.

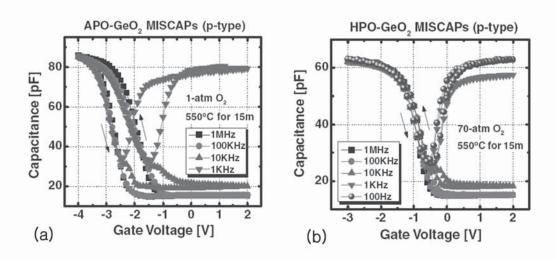

- Figure 2-9. Bidirectional C-V curves of Au/GeO<sub>2</sub>/p-Ge MOS capacitor, where GeO<sub>2</sub> was grown by atmosperic pressure oxidation and high pressure oxidation at 550°C for 15min.

- Figure 2-10. C-V hysteresis of  $HfO_2/p$ -Ge (100) gate stack with Pt as top electrode: (a) without  $O_2$  plasma passivation and (b) with  $O_2$  plasma passivation.

- Figure 2-11. Interface state density of GeON films extracted by quasi C-V techniques with and without F.G. annealing treatment at 300 °C (a) *p*-type (b) *n*-type Ge substrates.

- Figure 2-12. Electronic density of states of the relaxed  $Ge(M)O_2/Ge$  (100) structures vs. energy relative to the valence band edge ( $E_v$ ) of the Ge slab.

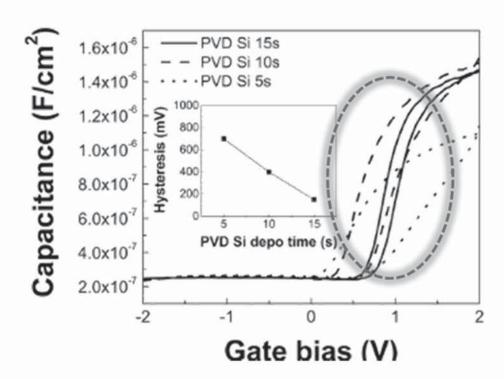

- Figure 2-13. Reduction of bidirectional sweep C-V hysteresis function of PVD Si depo time.

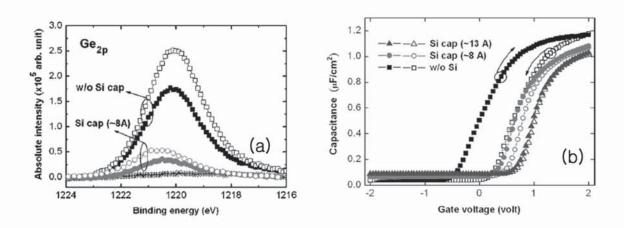

- Figure 2-14. XPS (a) Ge 2*p* spectra of Pt/HfO<sub>x</sub>N<sub>y</sub>/Ge gate stacks before (solid symbols) and after (open symbols) dielectric annealing at 500°C for 5 min, (b) Bidirectional sweep C-V curves of Pt/HfO<sub>x</sub>N<sub>y</sub>/Ge gate stacks lacking and containing a Si capping layer.

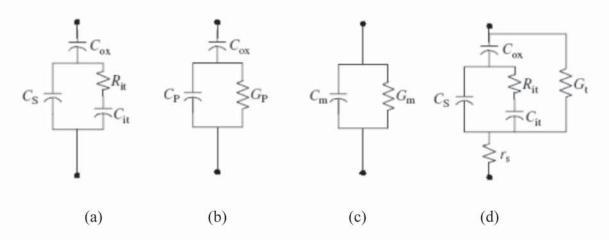

- Figure 2-15. Equivalent circuit models for conductance measurements; (a) MOS capacitor with interface traps, (b) simplified circuit of MOSCAP, (c) measured circuit and (d) including series resistance and tunnel conductance due to gate leakage.

- Figure 3-1. Schematic diagram of thermal-ALD system used in these experiments with direct liquid injection system and bubbler system for La-precursors.

- Figure 3-2. The Vaporize Pressure of La(iPrCp)<sub>3</sub>, La[N(SiMe<sub>3</sub>)<sub>2</sub>]<sub>3</sub> and TMA precursors.

- Figure 3-3. The molecular structure of  $La[N(SiMe_3)_2]_3$ .

- Figure 3-4. The molecular structure of La(iPrCp)<sub>3</sub>.

- Figure 3-5. The molecular structure of (a) SiH<sub>2</sub>(NC<sub>2</sub>H<sub>5</sub>CH<sub>3</sub>)<sub>2</sub> (BEMAS) precursor and (b) SiH<sub>2</sub>(N(C<sub>2</sub>H<sub>5</sub>)<sub>2</sub>)<sub>2</sub> (BDEAS) precursor.

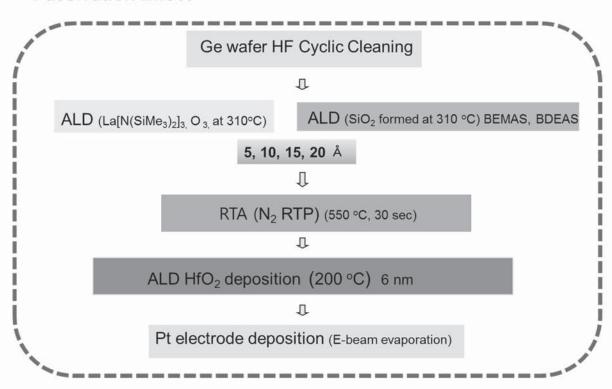

- Figure 3-6. Experimental flow for La-silicate and SiO<sub>2</sub> thin film as a passivation interface layer of HfO<sub>2</sub> film.

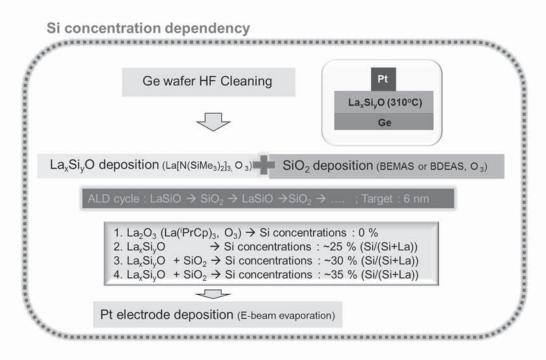

- Figure 3-7. Experimental flow for Si concentration controlled La-silicate thin films.

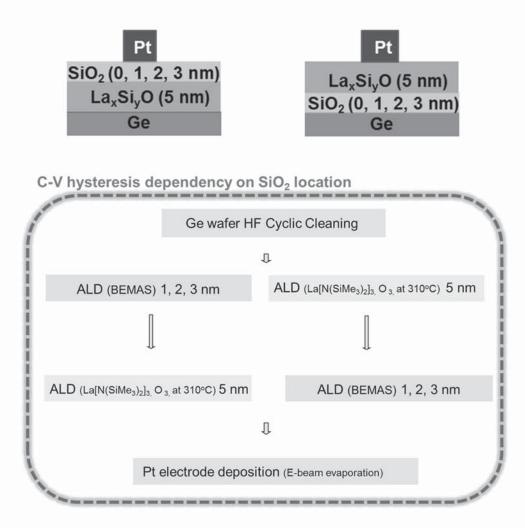

- Figure 3-8. Experimental flow and schematic diagrams for thermal-ALD grown Lasilicate film with SiO<sub>2</sub> passivation interface layer and capping layer.

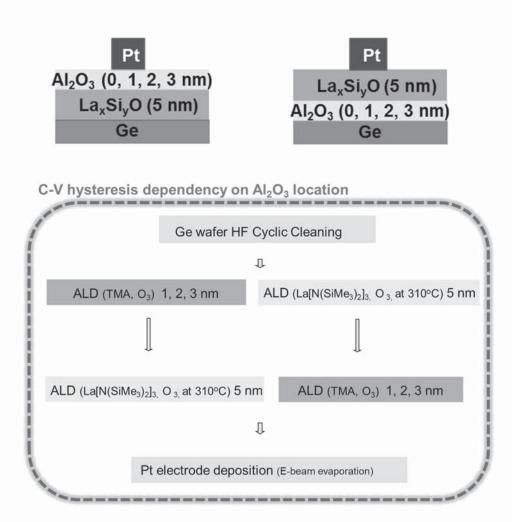

- Figure 3-9. Experimental flow and schematic diagrams for thermal ALD grown Lasilicate film with Al<sub>2</sub>O<sub>3</sub> passivation interface layer and capping layer.

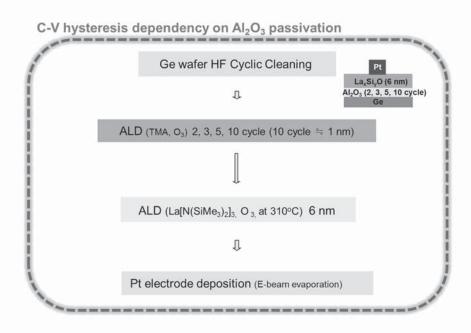

- Figure 3-10. Experimental flow and schematic diagrams for thermal ALD grown Lasilicate film with an ultra-thin Al<sub>2</sub>O<sub>3</sub> passivation interface layer.

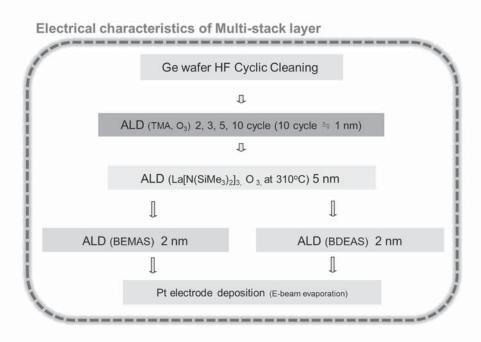

- Figure 3-11. Experimental flow and schematic diagrams for thermal ALD grown multistack La-silicate film (with an ultra-thin Al<sub>2</sub>O<sub>3</sub> passivation interface layer and 2.0 nm thickness of SiO<sub>2</sub> capping layer).

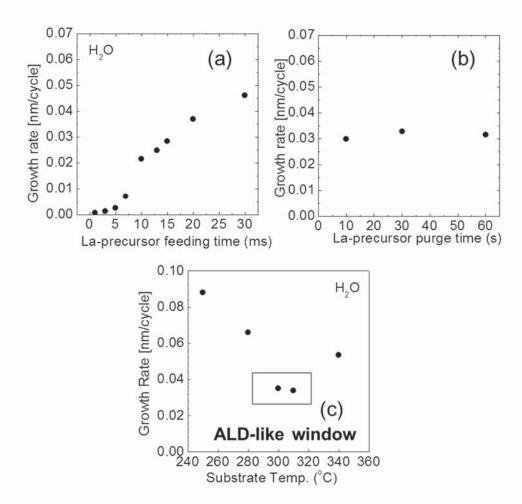

- Figure 4-1. The film growth rate depending on La[N(SiMe<sub>3</sub>)<sub>2</sub>]<sub>3</sub> precursor (a) feeding time, (b) purge time and (c) the deposition temperature, respectively.

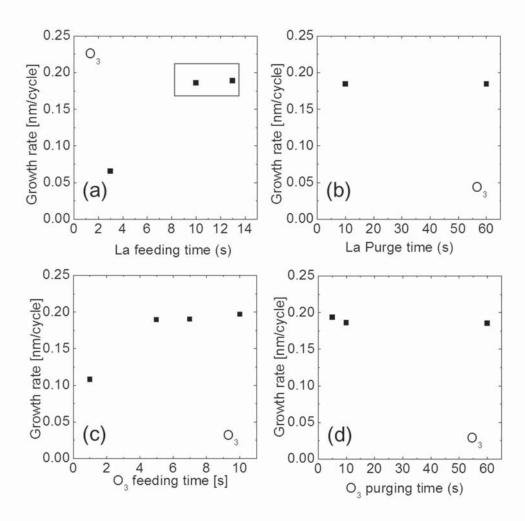

- Figure 4-2. The film growth rate depending on La[N(SiMe<sub>3</sub>)<sub>2</sub>]<sub>3</sub> precursor (a) feeding time, (b) purge time, (c) ozone feeding time and (d) purge time, respectively.

- Figure 4-3. The schematic diagram of fabricated MOSCAP with deposited La-silicate film for this experiment.

- Figure 4-4. CET vs. physical thickness of deposited La-silicate film with different oxidants water and ozone.

- Figure 4-5. AES depth profiles of the La-silicate films grown with (a) H<sub>2</sub>O, (b) O<sub>3</sub> and (c) Si concentrations of La-silicate film grown H<sub>2</sub>O as a function of deposition temperature calculated from XPS measurement.

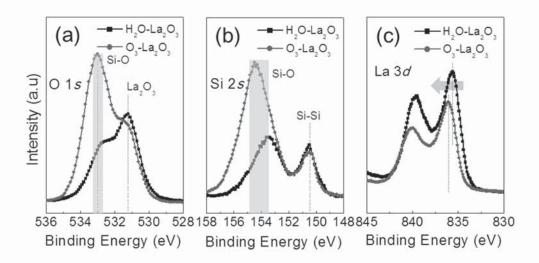

- Figure 4-6. XPS spectra of (a) O 1s, (b) Si 2s and (c) La 3d core level of the La-silicate films grown with oxidants as a H<sub>2</sub>O and an O<sub>3</sub>.

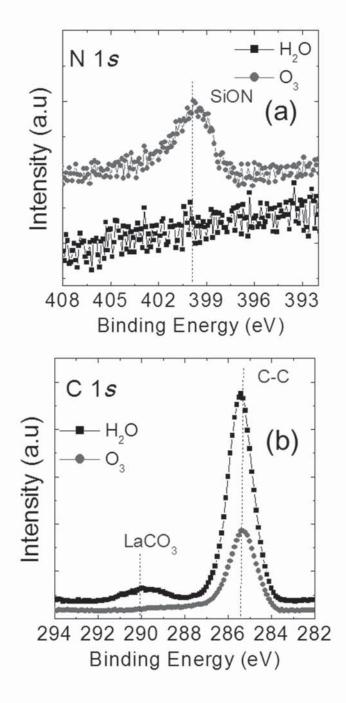

- Figure 4-7. XPS spectra of (a) N 1s and (b) C 1s core level of the La-silicate films grown with H<sub>2</sub>O and O<sub>3</sub>.

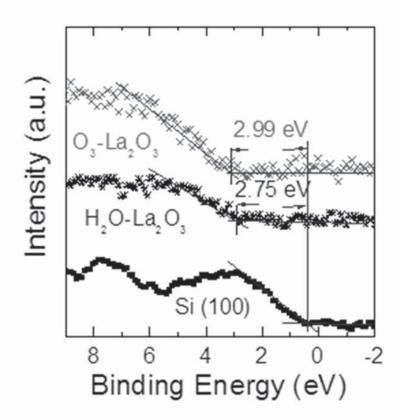

- Figure 4-8. XPS spectra of Valence band for Valance Band Offset of La-silicate film grown H<sub>2</sub>O and O<sub>3</sub>.

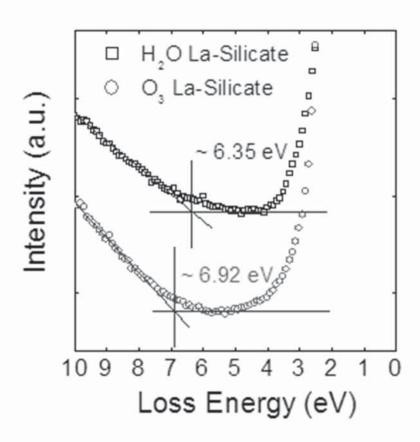

- Figure 4-9. O 1s loss spectra for bandgap energy of La-silicate film grown H<sub>2</sub>O and O<sub>3</sub>.

- Figure 4-10. Reconstructed band structures for La-silicate films grown with  $H_2O$  and  $O_3$ .

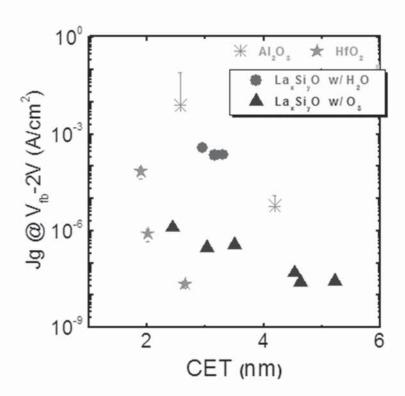

- Figure 4-11. Insulating properties of La-silicate films grown with H<sub>2</sub>O and O<sub>3</sub>, references for ALD Al<sub>2</sub>O<sub>3</sub> and ALD HfO<sub>2</sub> film were inserted.

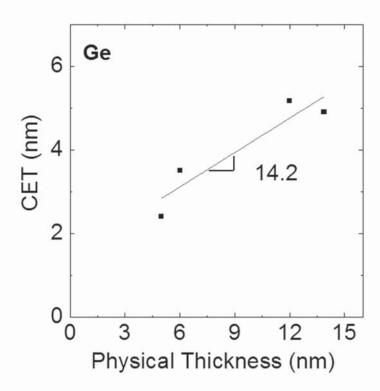

- Figure 4-12. CET vs. physical thickness of deposited La-silicate film on Ge substrate.

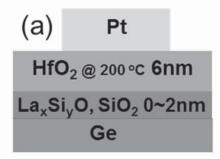

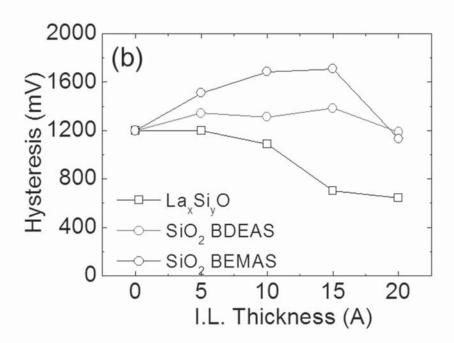

- Figure 4-13. (a) Schematic view and (b) C-V hysteresis change of La-silicate film, BEMAS and BDEAS SiO<sub>2</sub> film as passivation layer for HfO<sub>2</sub> on Ge substrate as a function of interface passivation layer thickness.

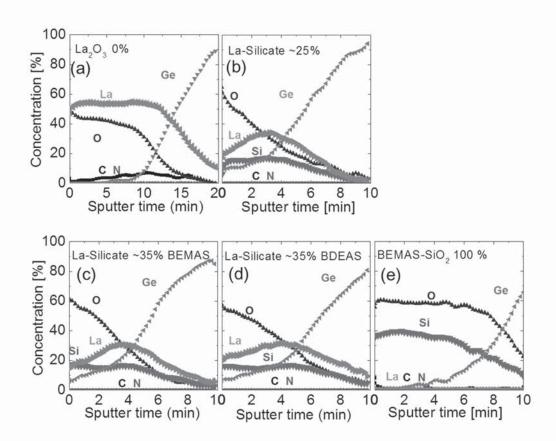

- Figure 4-14. AES depth profiles of (a) La-oxide thin film, (b) La-silicate thin film, Si concentrations controlled La-silicate film by (c) BEMAS-Si precursor, (d) BDEAS-Si precursor and (e) SiO<sub>2</sub> thin film by BEMAS precursor.

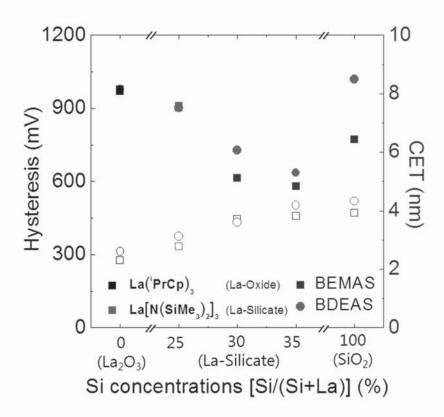

- Figure 4-15. C-V Hysteresis and CET as a function of Si concentrations of La-based oxide film.

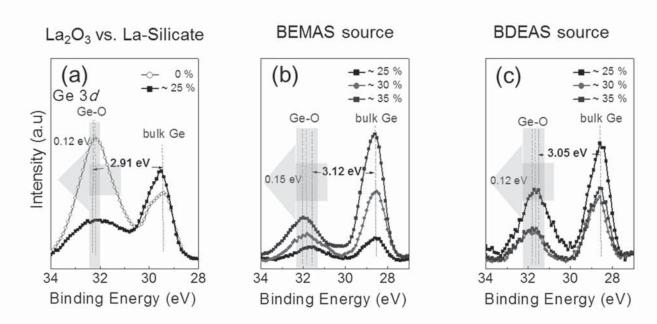

- Figure 4-16. Ge 3d core level of (a) pure- La-oxide and pure- La-silicate film with a Si concentration of ~ 25%, (b) Si concentrations controlled La-silicate film using BEMAS precursor and (c) Si concentrations controlled La-silicate film using BDEAS precursor.

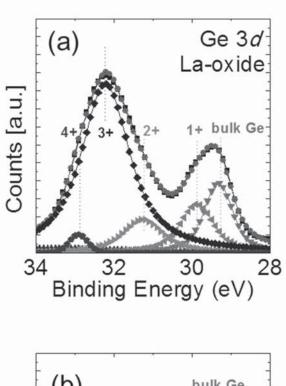

- Figure 4-17. Ge 3d core level for the explicit deconvolution for Ge-oxide (a) pure- La-oxide and (b) pure- La-silicate film (with a Si concentration of  $\sim 25\%$ ).

- Figure 4-18. Ge 3d core level for the explicit deconvolution for Ge-oxide (a) pure-Lasilicate film with a Si concentration of  $\sim 25\%$ , La-silicate film with a Si concentration of (b)  $\sim 30\%$  and (c)  $\sim 35\%$  using BEMAS precursor.

- Figure 4-19. Ge 3d core level for the explicit deconvolution for Ge-oxide (a) pure-Lasilicate film with a Si concentration of  $\sim 25\%$ , La-silicate film with a Si concentration of (b)  $\sim 30\%$  and (c)  $\sim 35\%$  using BDEAS precursor.

- Figure 4-20. C-V curves for CVS (with a gate stress voltage of -2.5 V) on MOS capacitor with the structures of (a) Pt/La-oxide/p-Ge and (b) Pt/La-silicate (~25 % Si concentration)/p-Ge.

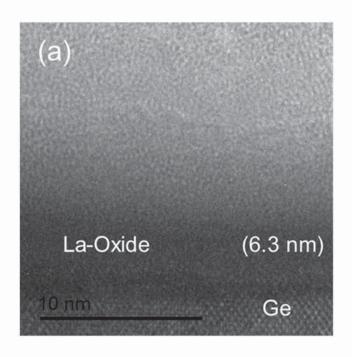

- Figure 4-21. TEM images for (a) La-oxide and (b) La-silicate films on Ge.

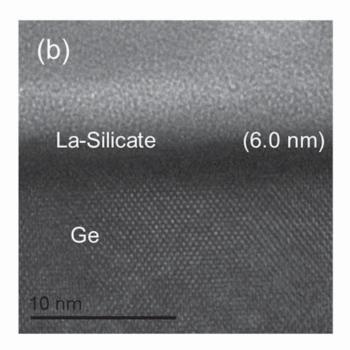

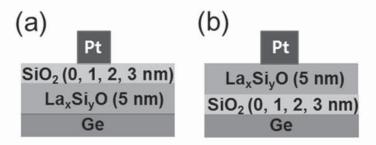

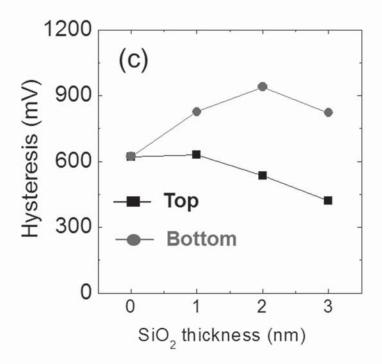

- Figure 4-22. Schematic diagrams of La-silicate MOSCAP for (a) SiO<sub>2</sub> capping, (b) SiO<sub>2</sub> passivation interface layer and (c) C-V hysteresis change as a function of SiO<sub>2</sub> thickness change.

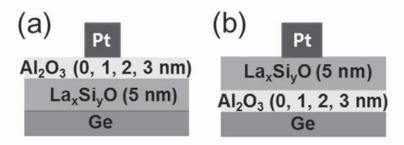

- Figure 4-23. Schematic diagrams of La-silicate MOSCAP for (a) Al<sub>2</sub>O<sub>3</sub> capping, (b) Al<sub>2</sub>O<sub>3</sub> passivation interface layer and (c) C-V hysteresis change as a function of Al<sub>2</sub>O<sub>3</sub> thickness change.

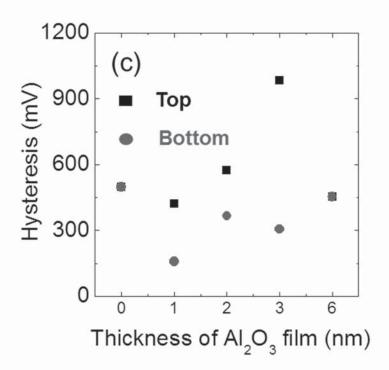

- Figure 4-24. Schematic views for (a) SiO<sub>2</sub> capping effect as Ge disproportionation and (b) Al<sub>2</sub>O<sub>3</sub> passivation layer effect as suppressing GeO desorption.

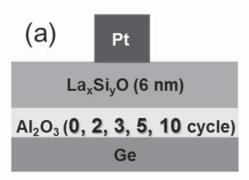

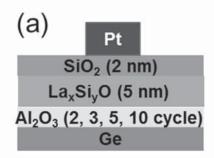

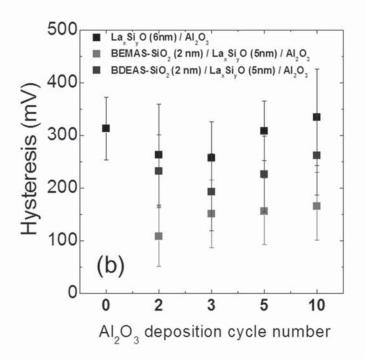

- Figure 4-25. (a) Schematic diagrams of La-silicate MOSCAP with ultra-thin Al<sub>2</sub>O<sub>3</sub> passivation interface layer and (c) C-V hysteresis as a function of Al<sub>2</sub>O<sub>3</sub> deposition cycles.

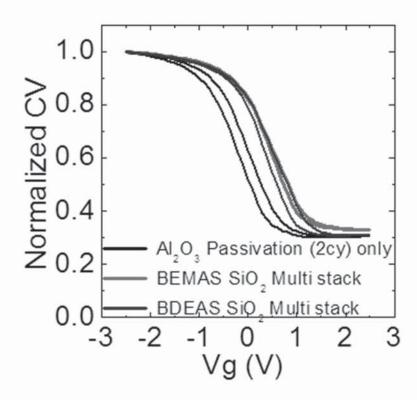

- Figure 4-26. Normalized C-V curves of La-silicate film with ultra-thin Al<sub>2</sub>O<sub>3</sub> passivation interface layer as a function of Al<sub>2</sub>O<sub>3</sub> deposition cycles.

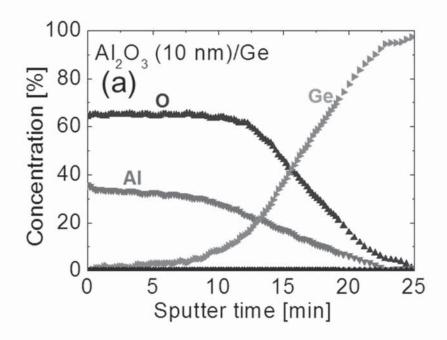

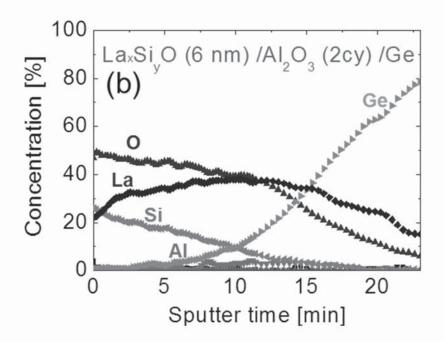

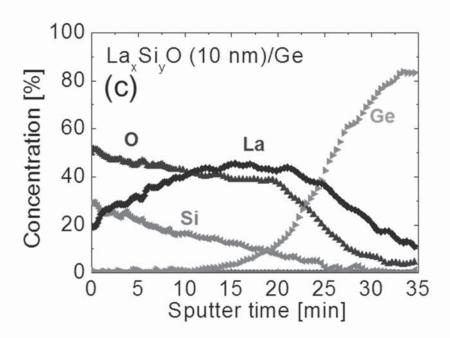

- Figure 4-27. AES depth profiles of (a)  $Al_2O_3/p$ -Ge, (b) La-silicate/  $Al_2O_3(2 \text{ cycles})/p$ -Ge and (c) La-silicate/ p-Ge.

- Figure 4-28. Ge 3d core level for the La-silicate film with various deposition cycles of ultra-thin Al<sub>2</sub>O<sub>3</sub> passivation interface layer.

- Figure 4-29. Ge 3d core level for the explicit deconvolution for Ge-oxide (a) La-Silicate /Al<sub>2</sub>O<sub>3</sub> (2 cycles)/p-Ge, (b) La-silicate/ Al<sub>2</sub>O<sub>3</sub> (3 cycles)/ p-Ge,(c) La-silicate/ Al<sub>2</sub>O<sub>3</sub> (5 cycles)/ p-Ge and (d) La-silicate/ Al<sub>2</sub>O<sub>3</sub> (10 cycles)/ p-Ge.

- Figure. 4-30. Interface state density vs. V<sub>g</sub>-V<sub>fb</sub> of Al<sub>2</sub>O<sub>3</sub>/Ge, La-silicate/Al<sub>2</sub>O<sub>3</sub> (2 cycles)/Ge and La-silicate/Ge.

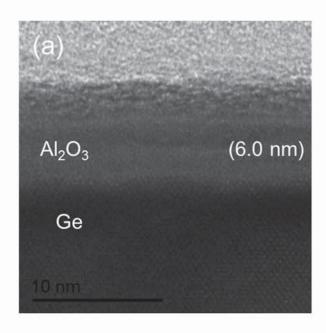

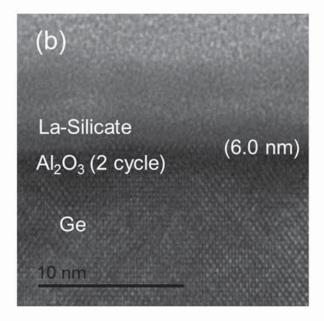

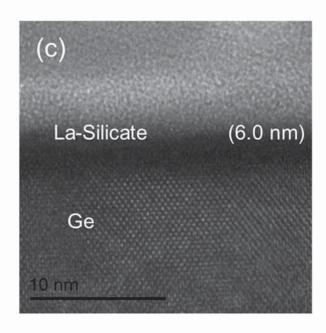

- Figure 4-31. TEM images for (a) Al<sub>2</sub>O<sub>3</sub>/Ge, (b) La-silicate/Al<sub>2</sub>O<sub>3</sub> (2 cycles)/Ge and (c) La-silicate/Ge.

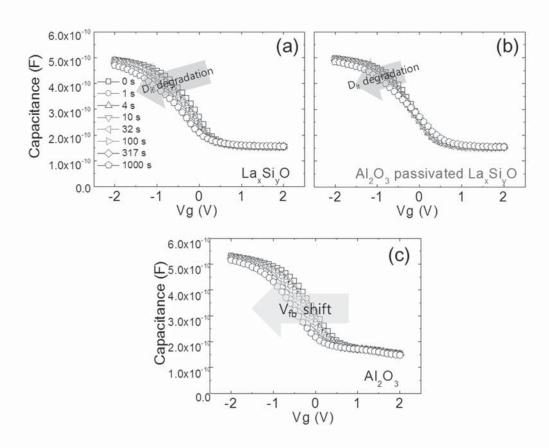

- Figure 4-32. C-V curves of CVS for (a) Al<sub>2</sub>O<sub>3</sub>/Ge, (b) La-silicate/Al<sub>2</sub>O<sub>3</sub> (2 cycles)/Ge and (c) La-silicate/Ge.

- Figure 4-33. (a) Schematic diagrams of La-silicate MOSCAP with BEMAS- and BDEAS SiO<sub>2</sub> capped La-silicate Al<sub>2</sub>O<sub>3</sub> (2 cycles) interface passivation layer on Ge and (b) C-V hysteresis as a function of Al<sub>2</sub>O<sub>3</sub> deposition cycles.

- Figure 4-34. Normalized C-V curves for (a) BEMAS- and (b) BDEAS SiO<sub>2</sub> capped La-silicate Al<sub>2</sub>O<sub>3</sub> (2 cycles) interface passivation layer on Ge.

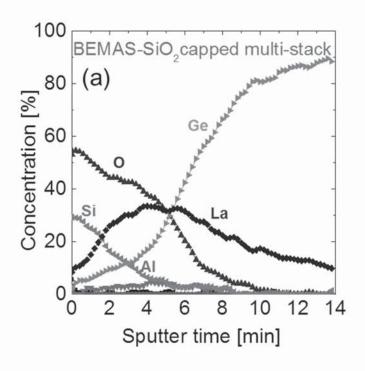

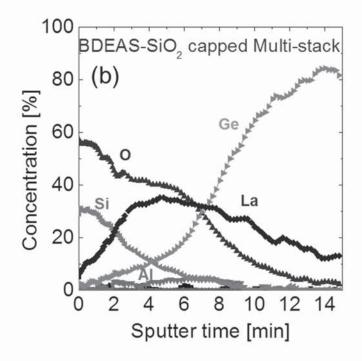

- Figure 4-35. AES depth profiles for (a) BEMAS- and (b) BDEAS SiO<sub>2</sub> capped Lasilicate Al<sub>2</sub>O<sub>3</sub> (2 cycles) interface passivation layer on Ge.

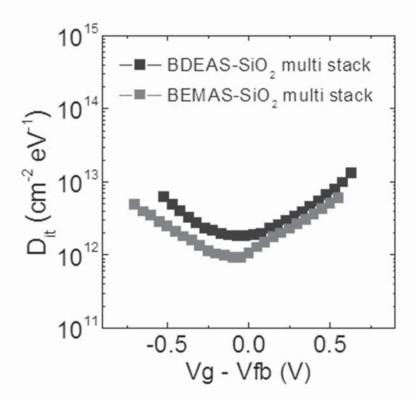

- Figure 4-36. Interface state density vs. V<sub>g</sub>-V<sub>fb</sub> for (a) BEMAS- and (b) BDEAS SiO<sub>2</sub> capped La-silicate Al<sub>2</sub>O<sub>3</sub> (2 cycles) interface passivation layer on Ge.

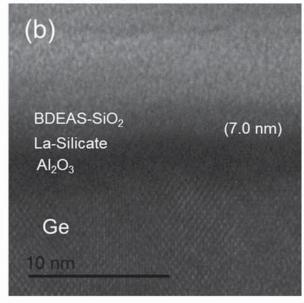

- Figure 4-37. TEM images for (a) BEMAS- and (b) BDEAS SiO<sub>2</sub> capped La-silicate Al<sub>2</sub>O<sub>3</sub> (2 cycles) interface passivation layer on Ge.

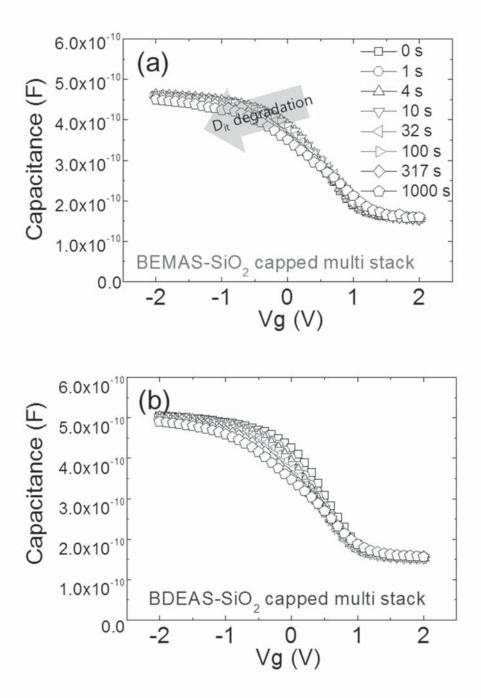

- Figure 4-38. C-V curves for CVS (a) BEMAS- and (b) BDEAS SiO<sub>2</sub> capped Lasilicate with Al<sub>2</sub>O<sub>3</sub> (2 cycles) interface passivation layer on Ge.

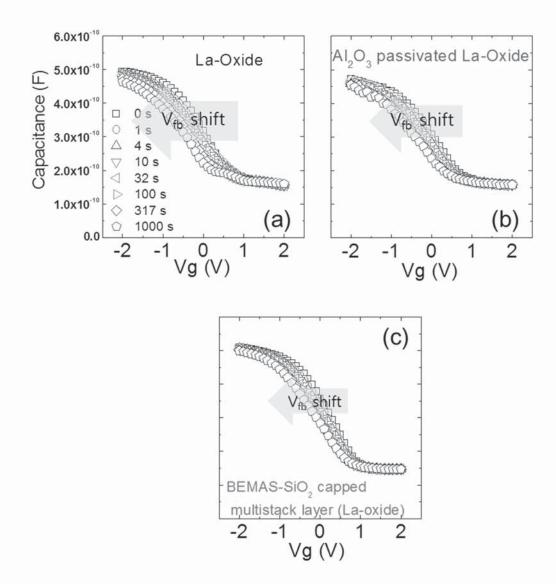

- Figure 4-39. C-V curves for CVS (a) La-oxide, (b) La-oxide with Al<sub>2</sub>O<sub>3</sub> (2 cycles) passivation interface layer and (c) BEMAS-SiO<sub>2</sub> capped La-oxide with Al<sub>2</sub>O<sub>3</sub> (2 cycles) passivation interface layer.

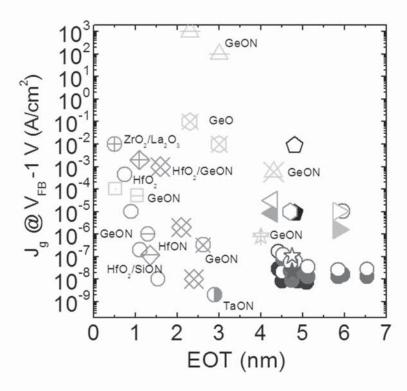

- Figure 4-40. Insulating properties for various high-k thin films deposited by thermal ALD.

# 1. Introduction

Since the invention of Si-based metal-oxide-silicon field effect transistor (MOSFET) [1, 2], there has been an unprecedented evolution in semiconductor industry shown as Fig. 1. For complementary metal oxide semiconductor (CMOS) scaling beyond the 45/32 nm technology node, HfO<sub>2</sub> as a high dielectric constant (high-*k*) material is used to replace SiO<sub>2</sub> or oxynitrides, because of excessive leakage current and reliability concerns. [3] The thickness shrinkage of the dielectric layer for a higher capacitance produces problems of a high leakage current by electron tunneling and device instability. [4, 5] To circumvent above mentioned problems, metal oxides with higher dielectric constants (*k*) than those of SiO<sub>2</sub> or Si<sub>3</sub>N<sub>4</sub> have been investigated intensively since the same capacitance was obtained from thicker film of high-*k* materials with tunneling current reduction. It is an urgent task to find a proper high-*k* material to replace SiO<sub>2</sub> as the gate dielectric in order to further improve the performance of CMOS devices

High-*k* materials, such as Al<sub>2</sub>O<sub>3</sub>, HfO<sub>2</sub>, ZrO<sub>2</sub>, HfSiO, La<sub>2</sub>O<sub>3</sub>, LaAlO<sub>3</sub> and LaSiO have been attracted a great deal of interest as the gate dielectrics of the application to CMOSFET. [6-11] The equivalent oxide thickness (EOT) of high-*k* thin films should fall below 1 nm with the guarantee of dielectric reliability in both applications and an acceptable interface quality with Si for device working and controllability of threshold voltage are needed for the gate dielectric in the CMOSFET. [12-14]

Atomic layer deposition (ALD) is known as the most feasible and competitive process in fabrication of high quality gate dielectric thin films with conformal deposition and high

# **CMOS Scaling Trend**

Figure 1-1. Schematic diagram of CMOS scaling trend.

accuracy in thickness control, making it excellently compatible with the semiconductor fabrication technology for mass-production. As the next generation high-k dielectric film as well as the threshold voltage control layer [13, 14], La<sub>2</sub>O<sub>3</sub> film are attracting much attention nowadays due to their high dielectric constant (~30) [2, 15] and large conduction band offset (CBO) with Si (~2.3 eV). [2] However, ALD of La-containing films have several challenges such as the limited selection of precursors and inducement of unstable film growth due to its hygroscopic behavior. [16] Additionally, serious Si diffusion from the substrate into the La<sub>2</sub>O<sub>3</sub> film during deposition has been reported. [17]

The use of Si-containing Tris[bis(trimethylsilyl)amino]lanthanum, La[N(SiMe<sub>3</sub>)<sub>2</sub>]<sub>3</sub>, as a La precursor was reported as the promising way to intentionally incorporate Si in La<sub>2</sub>O<sub>3</sub> film to prevent the diffusion of Si from Si substrates. [18] Since, significant Si diffusion during ALD of La<sub>2</sub>O<sub>3</sub> film and post-deposition annealing degrades the gate controllability by increasing permittivity of the gate oxide films, the use of La-silicate film instead of La<sub>2</sub>O<sub>3</sub> film is more attractive. Even though the chemical properties of ALD La-silicate films using La[N(SiMe<sub>3</sub>)<sub>2</sub>]<sub>3</sub> and H<sub>2</sub>O were reported [19-22], a systematic study on the influence of the type of oxygen source, H<sub>2</sub>O or O<sub>3</sub>, on the growth behavior and electrical properties of La-silicate films using La[N(SiMe<sub>3</sub>)<sub>2</sub>]<sub>3</sub> has been rarely reported. [23]

Furthermore, the carrier injection velocity of Si-based channel is going to saturate, which determine the drive current in the devices and difficult to improve more by conventional scaling technology due to the relatively low carrier mobility of Si, thus many researches have been exploring other channel materials with high carrier mobility such as Ge or III-V compound substrate to replace Si substrate shown as Fig.1. Ge is a one of candidate to replace Si as the channel material of MOSFET for beyond 14 nm

technology nodes due to its higher electron (twice) and hole (four times) mobilities than Si. [24, 25]

Similar to SiO<sub>2</sub>/Si in Si-MOSFET, GeO<sub>2</sub>/Ge has been generally regarded as the most fundamental interface in Ge MOSFET. [26-29] Nonetheless, the lack of thermodynamic stability at the GeO<sub>2</sub>/Ge interface hampers the development of Ge MOSFET. Many previous studies have demonstrated that the GeO<sub>2</sub>/Ge interface degrades due to the GeO desorption or GeO volatilization upon thermal annealing above 420°C in vacuum or N<sub>2</sub> ambient owing to interfacial reaction. [28, 29] A typical example of electrical degradation by GeO desorption is very large hysteresis in the capacitance-voltage (C-V) curves which is attributed to the electrically active defects near the interface. [29]

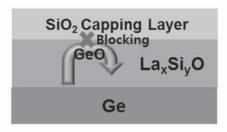

In contrast, thermodynamic calculation shows that the GeO<sub>2</sub> + Ge have a lower Gibbs free energy than 2 GeO at typical processing temperature and pressure, suggesting that effective isolation of the GeO<sub>2</sub>/Ge system from the atmosphere could suppress the adverse interfacial reaction which is called GeO proportionation. [30, 31] Considering these factors, there could be two possible solutions to solve the interfacial reaction problem; one is to adopt the capping layer, and the other is to adopt interfacial passivation (or barrier layer) to separate the GeO<sub>2</sub> and Ge physically. There have been many reports on the various interfacial passivation layers, such as the ultra-thin Si capping layers [32], Ge nitride interfacial layers [33, 34], AlN<sub>x</sub> [35] and La<sub>2</sub>O<sub>3</sub> dielectric interlayers [36, 37], high quality GeO<sub>2</sub> interfacial layer formed by plasma oxidation or high pressure oxidation. [38] Among the various passivation techniques, Si capping layer on a Ge substrate has drawn a great deal of attention due to its superior electrical performance.

Cheng et al. reported that the Si capping layer on a Ge substrate retards GeO

volatilization and suppresses the C-V hysteresis of the HfO<sub>x</sub>N<sub>y</sub> gate dielectric films in the MOS structure. The reduced C-V hysteresis by the Si capping layer was explained by the fact that Si-O bonds have larger Gibbs free energies and higher thermodynamic stabilities than Ge-O bonds, so that the reaction between the oxide and Ge substrate could be efficiently suppressed. [39] In most of the previous studies, Si capping layer on a Ge substrate was formed by either epitaxial growth of several mono-layers of Si or annealing in a SiH<sub>4</sub> (or Si<sub>2</sub>H<sub>4</sub>) ambient. [32] However, not much of the studies related to the ALD Si-containing passivation layers on a Ge substrate have been reported.

Houssa et al. simulated the atomic configuration of the interface between various rareearth oxide material and Ge by first principles calculation. [40] This result gives feasibility of La<sub>2</sub>O<sub>3</sub> and Al<sub>2</sub>O<sub>3</sub> as effective passivation layer on Ge to suppress dangling bonds than HfO<sub>2</sub>. Kato et al. reported an Al<sub>2</sub>O<sub>3</sub> interlayer effectively suppresses the formation of a Ge oxide interlayer in a La-oxide/Al<sub>2</sub>O<sub>3</sub>/Ge gate stack structure. The formation of GeO<sub>x</sub> is suppressed with increasing thickness of the Al<sub>2</sub>O<sub>3</sub> interfacial layer up to 1 nm. [41] In contrast, the adoption of capping layer, which could suppress the volatilization of GeO from the GeO<sub>2</sub> surface, and, thus, the accompanying interfacial reaction, has not been well studied compared with the interfacial passivation layer approach.

In this study, the ALD behavior and electrical properties of La-silicate films on Si substrate according to the type of oxygen source were examined. In particular, leakage current properties depends on the changes in Si concentration of the ALD La-silicate film grown on Si substrate using the Si contained La precursor La[N(SiMe<sub>3</sub>)<sub>2</sub>]<sub>3</sub> were focused.

The ALD ultra-thin Al<sub>2</sub>O<sub>3</sub> and SiO<sub>2</sub> layers were adopted as the interfacial passivation

and capping layers, respectively, for the La-silicate film on Ge substrate. During deposition of La-silicate films,  $SiH_2(NC_2H_5CH_3)_2$ , (BEMAS) and  $SiH_2(N(C_2H_5)_2)_2$ , (BDEAS) were additionally injected in order to control the Si concentrations (Si/(La+Si)) in the high-k film and its effect on electrical properties.

An ultrathin interfacial  $Al_2O_3$  layers of which thickness was controlled by deposition cycles (~2, 3, 5, 10 cycles) were formed between the La-Silicate film and Ge substrate by another ALD.

Additionally, ALD SiO<sub>2</sub> was chosen as the material for the capping layer on La-silicate film. The multi stack of Al<sub>2</sub>O<sub>3</sub> passivation, high-k La-silicate, and capping SiO<sub>2</sub> layers was effectively decreased the C-V hysteresis down to 80 mV, which is one of the best results reported up to date.

# 2. Literature Review

# 2.1. Scaling limit for Si-based gate oxide

The current gate dielectric SiO<sub>2</sub> thickness decreased less than 1 nm but there are several problems induced by gate dielectric oxide thickness reduction such as a high leakage current and reliability aspects. In ultrathin SiO<sub>2</sub> gate dielectrics, charge carriers flow through the dielectric film by direct tunneling process. [9, 10] Since the tunneling probability increases exponentially as the SiO<sub>2</sub> layer thickness decreased, the decrease of SiO<sub>2</sub> layer results in large increase of the gate leakage current.

$$I_{D,sat} = \frac{W}{L} \mu C \frac{(V_g - V_t)^2}{2} \tag{1}$$

Another issue related to SiO<sub>2</sub> thickness scaling concerns reliability aspects. During the operation of MOSFET in integrated circuits, charge carriers flow through the device, resulting in the generation of defects in the SiO<sub>2</sub> gate layer and at the Si/SiO<sub>2</sub> interface. [42-44] When a density of defects reaches to the critical level, breakdown (or quasi-breakdown) of the gate layer occurs, resulting in the failure of the device. [45-47] It was shown by Degraeve et al. that the time-to-breakdown distributions of ultrathin SiO<sub>2</sub> layers could be quite well reproduces by a percolation approach, assuming that breakdown occurred via the formation of a percolation path between defects generated during the electrical stress. [45]

The maximum gate voltage  $V_{G,max}$  that can be applied to a MOSFET is presented in Fig. 2-1 as a function of the  $SiO_2$  gate layer thickness at different temperatures and for the following specifications [ref 14]: gate dielectric lifetime fixed at 10 years, failure rate

fixed at 0.01% and chip area of 0.1 cm<sup>2</sup>. These curves (solid line in Fig. 2-1) were obtained from extrapolations of time-dependent dielectric breakdown measurements performed at high stress voltages, according to gate voltage, failure percentile and area scaling laws. [45, 48]

Figure 2-1. Measured and calculated oxide. Tunneling current versus Gate voltage for different oxide thicknesses.

#### 2.2. High-k gate dielectric

#### 2.2.1. Necessity for high-k dielectric

In the case of increasing the gate capacitance, consider a parallel plate capacitor,

$$C = \kappa \varepsilon_0 \frac{A}{t} \tag{2}$$

where k is the dielectric constant of the material,  $\varepsilon_0$  is the permittivity of free space (= 8.85 X  $10^{-14}$  F/cm), A is the area of the capacitor, and t is the thickness of the dielectric. This expression for C can be rewritten in terms of capacitance equivalent oxide thickness (CET) and  $k_{ox}$  (= 3.9, dielectric constant of SiO<sub>2</sub>) of the capacitor. The term CET represents the theoretical thickness of SiO<sub>2</sub> that would be required to achieve the same capacitance density as the dielectric. The physical thickness of an alternative dielectric employed to achieve the equivalent thickness of CET = 1 nm can be obtained from the simple expression,

$$t_{high-k} = \frac{\kappa_{high-k}}{3.9} CET \tag{3}$$

A dielectric with a relative permittivity of 16 therefore affords a physical thickness of  $\sim$  4 nm to obtain CET = 1 nm.

Interface engineering schemes have been developed to form oxynitrides and oxide/nitride reaction barriers between these high-k metal oxide materials and Si in an attempt to prevent or at least minimize reaction with the underlying Si. The passivating properties of such reaction barriers are widely reported. [49] In most cases, this amounts to further scaling the approaches used to form oxynitrides, discussed in the previous

section. These barrier layers have been shown to reduce the extent of reaction between the high-k dielectric and Si, as well as to help maintain high channel carrier mobility.

It is important to note, however, that using an interfacial layer of  $SiO_2$  or another low permittivity material, will limit the highest possible gate stack capacitance, or equivalently, the lowest achievable  $t_{ox}$  value. In addition, the increased process complexity for the deposition and control of additional ultrathin dielectric layers, as well as scalability to later technology nodes, remains a concern. This effect of reduced capacitance can be seen by noting that when the structure contains several dielectrics in series, the lowest capacitance layer will dominate the overall capacitance and also set a limit on the minimum achievable  $t_{ox}$  value. For example, the total capacitance of two dielectrics in series is given by

$$\frac{1}{C_{tot}} = \frac{1}{C_1} + \frac{1}{C_2} \tag{4}$$

where  $C_1$  and  $C_2$  are the capacitances of the two layers, respectively. If one considers a dielectric stack structure such that the bottom layer (layer 1) of the stack is  $SiO_2$ , and the top layer (layer 2) is the high-k alternative gate dielectric, Eq. (4) is simplified (assuming equal areas) to

$$t_{eq} = t_{SiO_2} + \frac{k_{ox}}{k_{high-k}} t_{high-k}$$

(5)

It is clear from Eq. (5) that the minimum achievable equivalent oxide thickness [defined as  $t_{ox}$  in Eq. (5)] will never be less than that of the lower-k (in this case pure SiO<sub>2</sub>) layer. Therefore, much of the expected increase in the gate capacitance associated with the high-k dielectric is compromised. The implications of current transport through such

stacked structures will be considered further later.

#### 2.2.2. La-based oxide films

Lanthanum oxide ( $La_2O_3$ ) is considered as a promising material which can offer better dielectric performance than Hf-based materials due to its larger conduction band offset ( $\sim$  2.3 eV) although it has a marginally higher dielectric constant ( $\sim$  30). [2, 3, 50, 51] Table 2-1 and table 2-2 shows comparison of relevant properties for high-k candidates. Yeo et al. simulated the theoretical direct tunneling current densities modeled by semi-empirical equation. [51]  $La_2O_3$  films are attracting much attention nowadays as the next generation high-k dielectric film as well as the threshold voltage control layer. [9, 10] Figure 2-2 shows the gate current density at a fixed  $V_G$  as a function of  $t_{ox}$ .  $La_2O_3$  film shows lowest current density at same EOT. This theoretical value was calculated considering dielectric constant, effective electron mass and barrier height, thus the leakage current characteristic of  $La_2O_3$  film is attribute to large conduction band offset and dielectric constant. [51]

Table 2-1. Conduction band offset to conduction band of Si  $(\Phi_b)$ , tunneling effective masses  $(m_{\text{eff}})$ , and relative permittivities (k) for several gate dielectrics. [2]

| Material:                           | $La_2O_3$ | $Al_2O_3$ | $HfO_2$           | $JVD$ - $Si_3N_4$ | RPNf-SiON         | SiO <sub>2</sub> |

|-------------------------------------|-----------|-----------|-------------------|-------------------|-------------------|------------------|

| Tunneling<br>mechanism <sup>b</sup> | ECB       | ECB       | ECB               | HVB               | ECB               | ECB              |

| $\Phi_b$ (eV)                       | 2.30°     | 2.80°     | 1.13 <sup>d</sup> | 1.90e             | 3.04 <sup>f</sup> | 3.10             |

| $m_{\rm eff} (m_0)$                 | 0.26      | 0.35      | 0.17              | 0.41e             | 0.21              | 0.40             |

| $\alpha^{g}$                        | 0.1       | 0.6       | 0.8               | 1.0e              | 0.4               | 0.6              |

| K                                   | 27        | 10        | 24                | 7                 | 5.08 <sup>f</sup> | 3.9              |

Table 2-2. Electric characteristics of  $La_2O_3$  and  $HfO_2$ , dielectric constant (k), bandgap ( $E_g$ ), conduction band offset (CBO), merits and drawbacks.

| Dielectric                     | k   | Eg          | СВО     | merits                                             | Drawbacks                                              |

|--------------------------------|-----|-------------|---------|----------------------------------------------------|--------------------------------------------------------|

| La <sub>2</sub> O <sub>3</sub> | ~27 | 5.8         | 2.3     | Higher-k<br>Large<br>conduction<br>band offset     | Moisture<br>absorption                                 |

| HfO <sub>2</sub>               | ~20 | 5.6~<br>5.7 | 1.3~1.5 | Most suitable<br>compare to<br>other<br>candidates | crystallization,<br>silicate and<br>silicide formation |

Figure 2-2. Gate current density  $J_G$  at a fixed inversion gate bias as a function of the equivalent oxide thickness  $t_{\text{ox,eq}}$  for five different gate dielectrics. Solid lines are from the model, Extraction of gate dielectric scaling limits is also shown based on a maximum tolerable gate leakage  $J_{Glimit}$  of 1 A/cm<sup>2</sup> and the supply voltage  $V_{DD}$  of 1 V. Scaling limits as a function of the gate dielectric figure of merit is described in the inset. [51]

#### 2.3. High mobility channel Ge

As the aggressive scaling of Si-based complementary metal-oxide semiconductors (CMOS) approaches the fundamental limit, various attempts such as modified channel materials have been investigated in attempts to improve device performance by enhancing the carrier mobility in the channel region. One possible modification of the channel region being considered at present involves replacing the conventionally used Si by alternative semiconductor materials such as Ge and III-V compound semiconductors. Ge or III-V compound substrate has been considered as a promising candidate as channel material for future technology nodes because of its lower effective conductivity mass. Large drive current is highly favorable for applications, because it determines the switch time of CMOS devices, which is believed to be limited by the velocity of carrier injection from the source into the channel in short channel devices. [52] One way of increasing the drive current is the conventional scaling technology. However, as mentioned previously, this Si-based dimension shrinkage is approaching its limitation, and high-k dielectrics are needed for further scaling. It was reported that Ge substrate has two times higher electron mobility and four times higher hole mobilities compared to the Si substrate. [27, 40] Therefore, the higher mobility as well as smaller band gap of Ge as a channel material has advantages owing to the improvement in injection current density and the scaling of the supply voltage, which results in high speeds and a low power consumption. The replacement of the conventional channel material Si with a higher carrier mobility channel material like Ge can also allow for further improvement of the drive current.

The integration of high-k dielectrics on Ge-FET Scaling technology plays important roles for further improving the performance and reducing costs of CMOS devices,

together with the replacement of Si substrate with high mobility channel materials such as Ge substrate. Since further scaling caused large tunneling current in Si-based devices is due to the relative smaller dielectric constant of  $SiO_2$  (k > 3.9), a new insulating material with high-k is highly desirable for Ge-based CMOSFET.

Ge-FET has attracted much attention due to their excellent electrical properties. Ge substrate has higher carrier mobility compared with Si substrate. The low-field electron mobility in Ge is more than double that of Si (3900 vs. 1500 cm²/V-sec) and the increase is four-fold for holes (1900 vs. 450 cm²/V-sec). [24, 25] This advantage makes Ge attractive for high speed circuit applications. The mobility of electron and hole is also more symmetric in Ge than in Si, and this means that the area of *p*-MOSFET can be reduced, and allow for more CMOS logic gates to be integrated in one unit clip.

As a part of mobility compensation scheme, the replacement of Ge substrate has lots of merits. However, it also induce the increase of reverse current density of a pn-junction in Ge. Table 2-3 summarized the characteristics of several potential channel materials at 300 K. Compared to the other Group IV and III-V semiconductor materials, the bulk hole mobility of Ge shows the highest values. Furthermore, the much lower melting point of Ge indicates that it is possible to fabricate Ge-based transistors with lower thermal budget processes, and requirements for thermal stability can be relaxed to some extent to integrate novel materials like metal gate electrode and high-*k* dielectrics into advanced transistors. [53, 54] In comparison with Si, Ge has as smaller band gap, which is related to a smaller supply voltage in applications. This is more compatible with the trend of scaling of the supply voltage as specified in ITRS. [3] The electrical performance of Ge *n*-MOSFET, and electrically active carrier concentration in the *n*-type diffusion layer is at

present not enough to reach the level required for the 14 nm node in the ITRS. Therefore, it may be useful to investigate the feasibility of III-V MOSFETs because bulk electron mobility in most III-V materials is higher than in Ge.

Besides, it is possible to realize the systematical integration of electronic, microwave, and photonic devices on Ge-based technology, since Ge has a small lattice mismatch with GaAs photonic material. The fact that the lattice constant of Ge is close to that of GaAs is expected to facilitate integration of III-V *n*-MOSFET and optical devices on Ge substrates in the future. Despite the above advantages of using Ge-based technology, Ge has not established a strong presence as an electronic material for ubiquitous microelectronic applications because it does not have a stable gate dielectric, which is critical for gate stacks formation.

Although Ge has the excellent properties, the lack of a stable passivation oxide and the necessity of a lower temperature process have hindered the fabrication of Ge-based devices. Ge has lower thermal stability, it starts to melt at 938°C, which sets the maximum temperature that can be used in a Ge containing process. In addition, Ge is easily oxidized in various environments and form an oxide layer consisting of a mixture of mainly mono oxide (GeO) and dioxide (GeO<sub>2</sub>) species. Material characteristics of Ge oxide and Si oxide are summarized in Table 2-4. GeO<sub>2</sub> is a polymorph, and the characteristics of GeO<sub>2</sub> obviously depend on the oxidation state and crystallinity. GeO<sub>2</sub> is transformed from hexagonal phase to tetragonal phase at 1033°C by annealing. Since hexagonal or amorphous GeO<sub>2</sub> is a major phase at room temperature, GeO<sub>2</sub> is soluble in water. In contrast, GeO(s) is insoluble. The most important reaction is GeO<sub>2</sub> + Ge  $\rightarrow$  2 GeO (s) or 2 GeO (g), which indicates that GeO<sub>2</sub> consumes Ge at the interface. Moreover,

GeO<sub>2</sub> on Ge not only decomposes into GeO(s) but also desorbs as gas-phase GeO(g). In other words, the narture of the interface between the Ge oxide and Ge substrate gives a decrease in the desorption temperature. Since GeO(g) has the nature of a reducing agent, this reaction can degrade the electrical properties of a high-k/Ge gate stack. Since the dielectric constant of Ge oxide is as low as 6, complete absence of Ge oxide at the high-k/Ge interface is likely to be necessary in achieving a thin equivalent oxide thickness (EOT) below 0.5 nm, as required in the ITRS. [3] One of the effective methods to decrease the amount of Ge oxide prior to high-k film deposition on the Ge substrate is HF pretreatment. However, a certain amount of Ge suboxide (GeO<sub>x</sub>, x < 2) remains even after the pretreatment.

Therefore, how to passivate Ge surface is one of the most important issues for fabricating high performance Ge-FET. Intensive studies have been carried out to find an appropriate passivation material for Ge surface. Many different passivation methods have been proposed such as oxidation, hydrogen (H), sulfur (S), and Fluorine (F) passivation, and nitridation.

Table 2-3. The characteristics of several potential channel materials at 300 K.

|                                                                                           | Ge                      | Si                      | GaAs                   | InSb                   | InP                    |

|-------------------------------------------------------------------------------------------|-------------------------|-------------------------|------------------------|------------------------|------------------------|

| Bandgap, E <sub>g</sub> (eV)                                                              | 0.66                    | 1.12                    | 1.42                   | 0.17                   | 1.35                   |

| Electron affinity, χ(eV)                                                                  | 4.05                    | 4.0                     | 4.07                   | 4.59                   | 4.38                   |

| Hole mobility,<br>µ <sub>h</sub> (cm <sup>2</sup> V <sup>7 1</sup> s <sup>7 1</sup> )     | 1900                    | 450                     | 400                    | 1250                   | 150                    |

| Electron mobility,<br>μ <sub>e</sub> (cm <sup>2</sup> V <sup>7 1</sup> s <sup>7 1</sup> ) | 3900                    | 1500                    | 8500                   | 80 000                 | 4600                   |

| Effective density of states in valence band, $N_{\rm v}({\rm cm}^{7.5})$                  | 6.0 × 10 <sup>18</sup>  | 1.04 × 10 <sup>19</sup> | 7.0 × 10 <sup>18</sup> | 7.3 × 10 <sup>18</sup> | 1.1 × 10 <sup>19</sup> |

| Effective density of states in conduction band, N <sub>c</sub> (cm <sup>7 3</sup> )       | 1.04 × 10 <sup>19</sup> | 2.8 × 10 <sup>19</sup>  | 4.7 × 10 <sup>17</sup> | 4.2 × 10 <sup>16</sup> | 5.7 × 10 <sup>17</sup> |

| Lattice constant, a(nm)                                                                   | 0.565                   | 0.543                   | 0.565                  | 0.648                  | 0.587                  |

| Dielectric constant, k                                                                    | 16.0                    | 11.9                    | 13.1                   | 17.7                   | 12.4                   |

| Melting point, T <sub>m</sub> (*C)                                                        | 937                     | 1412                    | 1240                   | 527                    | 1060                   |

Table 2-4. Material characteristics of Ge oxide and Si oxide.

|                                         | GeO              |                | SiO <sub>2</sub> |                 |           |

|-----------------------------------------|------------------|----------------|------------------|-----------------|-----------|

| Crystallinity                           | Amorphous        | Hexagonal      | Tetragonal       | Amorphous       | Amorphous |

| Dielectric constant                     | ( <del>-</del> 1 | 7              | 12               | -               | 3.9       |

| Solubility<br>(g/100g H <sub>2</sub> O) | insoluble        | 0.453<br>@25°C | 0.00023<br>@25°C | 0.5184<br>@30°C | insoluble |

| Density<br>(g/cm³)                      | -                | 4.228          | 6.239            | 3.637           | 2.2       |

| Transition temperature (°C)             | -                | 1033           | 1033             | -               | 867       |

| Melting point<br>(°C)                   | 710              | 1116           | 1116             | -:              | -1600     |

| Sublimation<br>Temperature<br>(°C)      | 700              | -              | -                |                 | -         |

# 2.3.1. Desorption and disproportionation characteristics of Ge oxide

The GeO desorption mechanism was researched by Toriumi groups. [26, 29, 55] In order to investigate GeO desorption, GeO<sub>2</sub> films were deposited by sputtering system, and the changes in the thickness of sputtered-GeO<sub>2</sub> films after annealing were addressed as shown in Fig. 2-3 (a). There was no GeO<sub>2</sub> thickness change on the Ge substrate until ~ 400°C, but the GeO<sub>2</sub> thickness decreases significantly at 400 to 600°C. However, the GeO<sub>2</sub> thickness on a thermally oxidized Si substrate shows the negligible change even at temperatures at 700°C. These results indicate that the GeO desorption over 400°C is mainly due to the interface reaction at GeO<sub>2</sub>/Ge. The schematic was also shown in Fig. 2-3 (b).

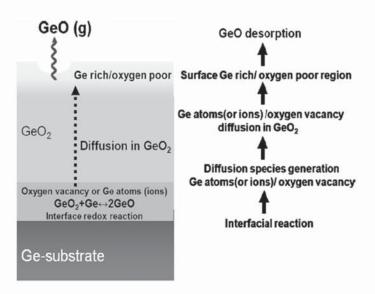

The diffusion species generation at the interface at the GeO<sub>2</sub>/Ge substrate causes the gradient of diffusion species concentration from the interface to the surface. Redox reaction at GeO<sub>2</sub>/Ge interface generates diffusion species at the interface, which triggers Ge atoms or ions or oxygen vacancy (V<sub>o</sub>) diffusion in film. Diffusion of Ge or V<sub>o</sub> in GeO<sub>2</sub> will causes a Ge rich or oxygen poor region at the GeO<sub>2</sub> surface, where volatile GeO is generated, which was schematically shown in Fig. 2-4.

On the basis of comparing GeO desorption in  $GeO_2/Ge$  and  $GeO_2/SiO_2/Si$  stacks, S. K. Wang et al. suggested there is a reversible reaction called GeO proportionation at the  $GeO_2/Ge$  interface. [56] Thermodynamic calculation shows that the  $GeO_2 + Ge$  have a lower Gibbs free energy than 2 GeO at typical processing temperature and pressure (disproportionation reaction of  $GeO_2 + Ge \rightarrow 2$  GeO has a positive Gibbs free energy change), suggesting that effective isolation of the  $GeO_2/Ge$  system from the atmosphere could suppress the adverse interfacial reaction. The result of XPS Ge 3d spectra as a

Figure 2-3. (a) GeO<sub>2</sub> thickness changes on Ge and on SiO<sub>2</sub>/Si as a function of annealing temperature and (b) Schematic view of GeO desorption in GeO<sub>2</sub>/SiO<sub>2</sub>/Si stack vs. GeO<sub>2</sub>/Ge stack. [55]

Figure 2-4. Schematics of GeO desorption mechanism from GeO<sub>2</sub>/Ge stacks. [56]

Figure 2-5. XPSpectra Ge 3d peak core spectra for Ge disproportionation effect for GeO generate  $GeO_2 + Ge$  in terms of annealing temperature. [30, 31]

function of annealing temperature is shown on Fig. 2-5.

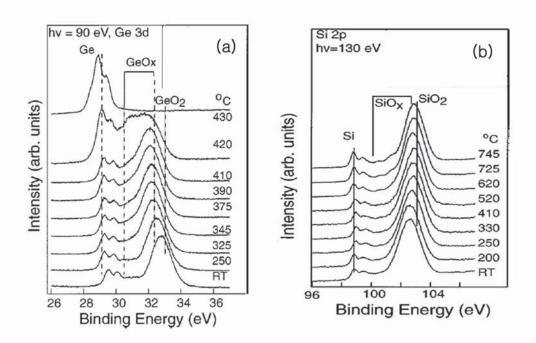

The comparision of the thermal decomposition pathway for a ultrathin oxide layer on surface of Ge (100) and Si (100) substrate was also reported. [28] Figures 2-6 (a) and (b) shows Ge 3d and Si 2p spectra as a function of temperature for the ultra thin oxide layers on the Ge and Si surface, respectively. As-prepared oxide layer consists of a mixture of oxides (sub oxides) and dioxides, on both the surfaces. The oxide layers decompose and desorb as monoxides. However, the decomposition pathways are different from each other. On annealing of Ge oxides, GeO<sub>2</sub> species transform to GeO and remain at the surface and desorb at about 420°C, and complete desorption was took place at 430°C, leading to the formation of a clean surface. In contrast, annealing of Si oxides results in the transformation of SiO to SiO<sub>2</sub> up to temperatures of about 780°C close to the desorption. At high temperatures auch as above 700 to 800°C, SiO<sub>2</sub> decomposes and desorbs, implying a reverse transformation to volatile SiO species.

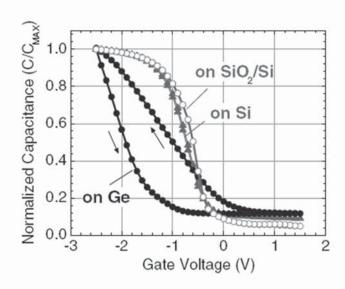

The effect of GeO desorption on C-V characteristics were widely reported. [26, 55] Figure 2-7 shows the bidirectional C-V characteristics of sputter deoposited GeO<sub>2</sub> metal oxide semiconductor capasitors (MOSCAP) on Ge, Si, and thermally oxidized Si substrates, fabricated by a conventional PDA at 600°C. The capacitor fabricated on the Ge substrate shows the characteristics of huge hysteresis and stretch-out, while quite good electric characteristics are obtained from the capacitors on Si and SiO<sub>2</sub>/Si substrates. It is believed that the deterioration of the C-V characteristics of the GeO<sub>2</sub>/Ge MOSCAP originated from the interface reaction to drive GeO volatilization. This suggest that GeO desorption should leave huge amount of interface states density or traps at the interface. These C-V distortion was also observed when ALD-HfO<sub>2</sub> was deposited onto the Ge

substrate.

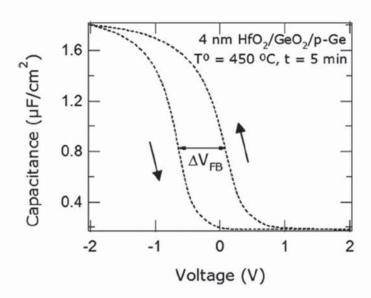

Figure 2-8 shows large C-V hysteresis was observed for HfO<sub>2</sub>/GeO<sub>2</sub>/*p*-Ge [28], which can be explained by the fact that oxidant during the initial ALD cycles may induce an intermixing reaction with the uncovered Ge surface and the adsorbed Hf pecursors before the formation of a continuous HfO<sub>2</sub> film, which resulted in a non-uniform interface and more intermixing between HfO<sub>2</sub> and Ge substrate, and occured large C-V hysteresis.

Figure 2-6. XPSpectra of (a) Ge 3d and (b) Si 2p core level spectra as a function of annealing temperature for the ultra thin oxide layers on the Ge and Si surface, respectively. [28]

Figure 2-7. Bidirectional C-V characteristics of GeO<sub>2</sub> MOSCAP on Ge, Si, and thermally oxidized Si substrates, fabricated by a conventional PDA treatment at 600°C. [55]

Figure 2-8. Large C-V hysteresis for HfO<sub>2</sub>/GeO<sub>2</sub>/p-Ge. [28]

## 2.3.2. Introduction for Ge Passivation Techniques

Due to aggressive down-scaling of the MOSFET devices, the introduction of alternative substrate materials such as Ge is necessary. High carrier mobilities and a low dopant activation temperature are the main advantages of Ge substrates compared to Si substrate. Despite of the successful realization of Ge based MOSFET and numerous improvements, the device performance reported still below theoretical predictions, mainly due to insufficient Ge oxide interface passivation. Therefore several capable approaches for Ge surface passivation techniques have been reported.

Various passivation techniques have attracted attention for the Ge interface passivation. Some studies have been carried out to explore the use of hydrogen (H) to passivate Ge surface. [57-59] H terminated Ge surface exhibits oxide free surface [59], but the surface is rough and unstable when exposed to the ambient. [58, 60] Some researchers studied the electrical properties of sulfur (S) passivated Ge surface. [61, 62] Frank et al. reported that HfO<sub>2</sub>/GeO<sub>x</sub>S<sub>y</sub>/Ge stacks exhibit lower fixed charge and interface state density than conventional HfO<sub>2</sub>/GeO<sub>x</sub>S<sub>y</sub> /Ge stacks. [61] Xie et al. further found that the S passivated Ge surface can improve thermal stability of HfO<sub>2</sub>/GeO<sub>x</sub>S<sub>y</sub> /Ge stacks while maintaining the low gate leakage current. [63] Some studies also used Chloride (Cl) [60, 64, 65] and fluorine (F) [66, 67] as Ge interface passivation. Lu et al. reported that Cl terminated Ge surface is stable, but that Cl cannot passivate Ge surface effectively, and some oxygen or carbon will be incorporated on the surface. [64] For F passivated Ge surface, Lee et al. showed that the interface defect states at HfO<sub>2</sub>/Ge interface can be effectively passivated by F incorporation. [67] Xie et al. reported that Ge-based MOS structures incorporated with F exhibit good electrical properties and low interface state density. [66, 68] In

addition, Ba passivation [69], As passivation [70] and Si thin passivation layer [71] have been proposed to Ge passivation techniques.

However, a good quality interface layer is required before the deposition of a high-k dielectric. Hole mobility above 300 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> was demonstrated for Ge PMOS with GeON passivation. Ge NMOS exhibited poor drive current and low mobility both in our experiments and by several demonstrations worldwide. [72-75] Better characterization and understanding of interface traps can be helpful to investigate Ge NMOS problem. An interfacial passivation layer with low interface state density and good electrical quality is required before the deposition of a high-k dielectric to improve PMOS performance and to solve Ge NMOS problem.

Ge interface passivation has been a critical challenge. Direct deposition of a high-*k* dielectric on Ge has exhibited poor electrical characteristics. Many attempts have been made with different high-*k* materials including HfO<sub>2</sub> [33], ZrO<sub>2</sub> [76], Al<sub>2</sub>O<sub>3</sub> [74] and LaAlO<sub>3</sub> [75] to find a suitable dielectric materials for Ge.

#### 2.3.3. Oxidation treatment

Among several passivation methods, oxidation, nitridation or their combination GeO<sub>x</sub>N<sub>v</sub> has attracted much more interest because they are compatible to current fabrication processes. In contrast, extensive applications of SiO<sub>2</sub> in Si based technology; Ge oxides have not received much attention as gate dielectrics for Ge based MOS devices because they were thought thermally and chemically instable previously. [77] More recently, attention has been paid gradually on using GeO<sub>2</sub> to passivate Ge surface due to the fact of the unavoidable formation of GeO<sub>x</sub> during growth of high-k oxides on Ge surface directly. [78-85] Various oxidation processes have been proposed. [79-81, 83-85] Some papers reported that GeO<sub>2</sub> can also acts as a promising electrical passivation layers for high-k gate dielectric deposited by the ALD. However large C-V hysteresis was observed for the HfO2 or ZrO2 gate stacks by using thermally grown GeO2 passivation layers [86, 87], recently, a high quality of GeO<sub>2</sub> was obtained by using high pressure oxidation (HPO) and oxygen plasma oxidation. [78, 88] C. H. Lee et al. reported that the HPO of Ge, in terms of controlling the Ge desorption, and demonstrated the significant improvement in electical properties of GeO<sub>2</sub>/Ge MOSCAP. [38, 88] Although GeO<sub>2</sub> in this paper was not used as the passivation layers, it was addressed that GeO desortion from GeO<sub>2</sub>/Ge stacks could be efficiently suppressed HPO. Figure 2-9 shows C-V curves of Au/GeO<sub>2</sub>/p-Ge structure. GeO<sub>2</sub> grown by atmosperic pressure oxidation shows large amounts of C-V hysteresis, which means the huge amount of interface and bulk traps, while in the case of GeO<sub>2</sub> grown by HPO shows significant reduction of C-V hysteresis and frequency dispersion. Therefore calcurated interface state density of Au/GeO<sub>2</sub>/p-Ge was 2 x 10<sup>11</sup> eV<sup>-1</sup> cm<sup>-2</sup>. This means GeO<sub>2</sub> grown by high pressure oxidation can be used for the passivation layer between high-k gate dielectrics and Ge substrate.

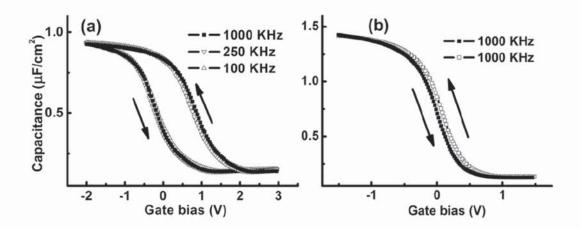

Afanas'ev et al. reported that Ge oxide layers were formed when using ALD to grow HfO<sub>2</sub> on Ge, and found that the band alignment at GeO<sub>x</sub>/Ge (001) interface determined by internal photoemission (IPE) spectroscopy is large enough to minimize possible carrier tunneling. [79, 84] Molle et al. compared three oxidation processes, and showed that a large percentage (~ 98 %) of GeO<sub>2</sub> in GeO<sub>x</sub> layer was formed using atomic oxygen source at 300°C. [80] Delabie et al. used pure O<sub>2</sub> to oxide Ge surface in the atmospheric pressure at 350°C, and found that GeO<sub>2</sub> passivated Ge MOS structures showed well-behaved C-V characteristics. [81] Matsubara et al. reported thermally oxidized Ge surface using pure O<sub>2</sub> at the atmospheric pressure, and found a low interface trap density in GeO<sub>2</sub>/Ge MOS structures, with the minimum trap density that is lower than  $\sim 10^{11}$  cm<sup>2</sup> eV<sup>-1</sup> at 575°C. [85] Q. Xie et al. reported that C-V hysteresis was substantially reduced from 900 to 50 mV for the HfO<sub>2</sub>/Ge gate stacks by using in situ O<sub>2</sub> plasma passivation. [78] Figure 2-10 shows C-V hysteresis characteristics for the Pt/HfO<sub>2</sub>/GeO<sub>2</sub>/p-Ge MOSCAP without and with surface passivation. Very large C-V hysteresis (~ 900 mV) was observed for the sample without surface passivation independent of the measured frequency, while O<sub>2</sub> plasma pretreated sample shows much narrower hysteresis (~ 50 mV) was obtained although the HfO<sub>2</sub> deposition process is similar when compared to the MOSCAP without passivation. The reduction of C-V hysteresis was explained by the more uniform and stable GeO<sub>2</sub> interfacial layer created by O<sub>2</sub> plasma treatment when it is conducted directly prior to the ALD process. For the MOSCAP without O<sub>2</sub> plasma pretreatment, the O<sub>2</sub> plasma during the initial ALD cycles may induce an intermixing reaction with the uncovered Ge surface and also the adsorbed Hf metal precursors before the formation of a

Figure 2-9. Bidirectional C-V curves of Au/GeO<sub>2</sub>/p-Ge MOS capacitor, where GeO<sub>2</sub> was grown by atmosperic pressure oxidation and high pressure oxidation at 550°C for 15min. [88]

Figure 2-10. C-V hysteresis of  $HfO_2/p$ -Ge (100) gate stack with Pt as top electrode: (a) without  $O_2$  plasma passivation and (b) with  $O_2$  plasma passivation. [78]

continuous HfO<sub>2</sub> film. This results in a nonuniform interface and more intermixing between HfO<sub>2</sub> and Ge substrate and, therefore, a larger C-V hysteresis.

Afanas'ev et al. studied electronic properties of GeO<sub>x</sub>/Ge stack, and noted that the band gap of Ge sub oxide is significantly lower than that of GeO<sub>2</sub>, resulting in an insufficient barrier height to block carrier tunneling. [84] Although GeO<sub>2</sub> has been extensively studied, there are still some issues remain. For example, the growth of good quality of GeO<sub>2</sub> is still challenging, which is of importance for applications since the electronic properties of GeO<sub>x</sub> is dependent on its oxidation states. Moreover, the value of valance band offset (VBO) obtained by Afanas'ev et al. using IPS [79, 84] is much smaller than that determined by XPS directly [83], and the mechanism has not been well studied yet.

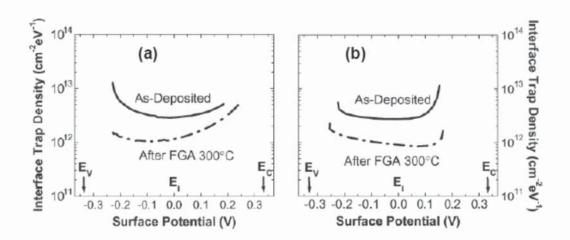

## 2.3.4. Nitridation

GeON has been widely used to passivate germanium and fabricate MOSFETs. [72, 73, 89-92] The advantage of GeON over Ge oxides is the improved chemical and thermal stability. Nitrogen can be incorporated by either thermal [72] or plasma nitridation. [90, 93] However, it was shown that interface state density was high and MOSFET had mobility degradation due to Coulomb scattering. [94] Interface state density above  $\sim 10^{12}$  cm<sup>-2</sup> eV<sup>-1</sup> and even as high as  $\sim 10^{13}$  cm<sup>-2</sup> eV<sup>-1</sup> of GeON was measured using n- and p-type Ge substrate. Nitrogen incorporation in GeON films was less than 30%. Figure 2-11 shows that forming gas annealing helps to reduce interface state density. However, the effect of H passivation seems to be minor compared to the H passivation of Si dangling bonds, widely used in CMOS technology.

Ge<sub>3</sub>N<sub>4</sub> has been studied as a promising alternative surface passivation material for Ge-FET due to its excellent mechanical, thermal, and electronic properties. [95] For examples, Van Elshocht et al. found Ge MOS structures with surface pretreatments in NH<sub>3</sub> ambient may result in smoother films with strongly reduced diffusion of Ge in the HfO<sub>2</sub> film, and this also leads to a much better electrical performance. [96] Maeda et al. used plasma N source to nitride Ge surface, and fabricated MOS structures with a smooth interface layer and good electrical properties. [97] Nitridation processes with atomic N source have also been proposed. Maeda et al. reported a method for growing high quality Ge<sub>3</sub>N<sub>4</sub> on Ge surface using atomic N source at low temperature. [98]

In a later study, they also fabricated a Ge-MOS structure with  $Ge_3N_4$  as the gate dielectrics, and found that the interface trap density is as low as  $1.8 \times 10^{11} \text{ cm}^{-2} \text{ eV}^{-1}$ . [92] Furthermore, Wang et al. investigated nitrided Ge surface using atomic N source also, and 38

determined the band alignments and thermal stability of Ge<sub>3</sub>N<sub>4</sub>/Ge (001) interface using XPS measurement. [99] Besides, Lieten et al. found that mono-crystalline Ge<sub>3</sub>N<sub>4</sub> can be formed on Ge (111) surface using plasma N source at atmospheric pressure at 800°C, and it has high thermal stability. [100]

However, although many researches have been carried on the possibility of using  $Ge_3N_4$  to passivate Ge surface, the studies on electronic properties of  $Ge_3N_4$  are still limited, and the optical dielectric and intrinsic defect properties of  $Ge_3N_4$  have not been well understood yet. Moreover, it is highly favorable to obtain more information about the interface properties of  $Ge_3N_4/Ge$  such as atomic interface structures, interface stability, and band alignments.

Figure 2-11. Interface state density of GeON films extracted by quasi C-V techniques with and without F.G. annealing treatment at 300 °C (a) *p*-type (b) *n*-type Ge substrates. [94]

# 2.3.5. Direct Deposition of high-k Dielectrics

High-k dielectrics have been under research in the last two decades to replace SiO<sub>2</sub> in CMOS technology. Significant progress has been made to improve the electrical quality of high-k dielectrics by academia and industry. In early 2007, Intel announced the deployment of Hf-based high-k dielectrics in conjunction with a metallic gate for components built on 45 nm Si CMOS technology node. A broad range of high-k dielectrics have also been tried on Ge to find a suitable gate dielectric for CMOS applications. Rare earth oxides also pay attention to the good passivation layers of Ge devices because these oxides has compatibility with Ge, which produce well behaving Ge device characteristics. A possible reason for this behavior is that rare earth oxides react strongly with the substrate resulting in catalytic oxidation of Ge and in the spontaneous formation of stable interfacial layers. [101] HfO2 [33], ZrO2 [102], Al2O3 [74] and LaAlO<sub>3</sub> [75] were deposited directly on Ge substrate after chemical cleaning. Native oxide was removed from Ge surface mostly by DI water or HF, or a repetitive application of both. MOS capacitor results show that interface state density is high and gate leakage is prominent for those devices. Besides, Ge MOSFET with the gate stacks of high-k dielectric directly deposited on Ge exhibits even lower mobilities than Si MOSFET. Thus, with thicker physical thickness for the same EOT, high-k materials can reduce leakage current flowing from devices greatly. Similar to the requirements of its integration on Sibased FETs, however, the alternative high- k material on Ge FET should also have to satisfy thermal stability, large band gap (Eg), CBO, VBO and low Dit.

Based on these requirements, intensive studies have been carried out to find the appropriate high-k materials either in amorphous or epitaxial growth on Ge substrate.

Amorphous high-k dielectrics are favorable because they are isotropic and can avoid grain boundaries at the interface with substrate. The grain boundary at the interface is believed to be the current tunneling path, which can lead to larger leakage current in devices. Various amorphous high-k dielectrics such as HfO<sub>2</sub> [103, 104], ZrO<sub>2</sub> [102, 105, 106], and Al<sub>2</sub>O<sub>3</sub> [107] have been grown on Ge by using different methods, and their electrical properties were studied. One of the candidate for the rare earth oixde is CeO<sub>2</sub> [104, 105],  $CeO_2$  reduces the density of states to  $\sim 10^{12} \, cm^{-2} \, eV^{-1}$  or below. However, it suffers from high leakage due to the low energy gap of CeO<sub>2</sub> (~ 3.3 eV) and its scalability to low EOT values. It was reported that HfO<sub>2</sub> on CeO<sub>2</sub> passivating layer can overcome leakage current issues. [102, 106] Gd<sub>2</sub>O<sub>3</sub> also has attracted interest mainly because it can be grown in crystalline form on Ge with abrupt interfaces. [102] However, there is not enough evidence at the moment about its dielectric quality and its suitability as a gate dielectric for Ge devices. It was found that the leading high-k dielectric in Si substrate, HfO<sub>2</sub>, is not suitable for Ge substrate directly, because it can react with Ge substrate, and form Germanide, which is unstable and would lead to the large leakage current in devices. [103, 108] In contrast, although Zr-related high-k dielectrics were screened as gate dielectrics on Si-based FET due to the fact that they would react with Si to form unstable Silicides, Ge-MOS structures with Zr-related high-k dielectrics exhibit good electrical properties [105, 109], and there is no interfacial layer at ZrO<sub>2</sub>/Ge interface. [110] Moreover, it is noted that that gate dielectrics on Ge that have good electrical performance are GeON [33, 34], GeAlON [35], GeZrO [76], and GeZrSiO [111].

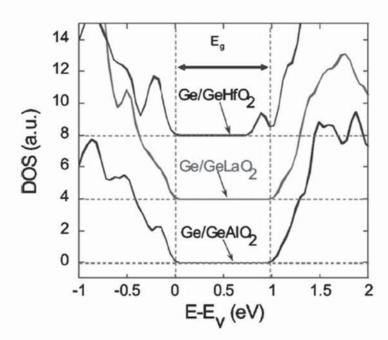

However, the formation of Ge oxides during the annealing process is a serious problem for integrating amorphous high-k oxides on Ge substrate directly due to the thermal 42

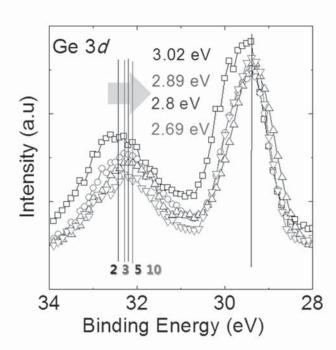

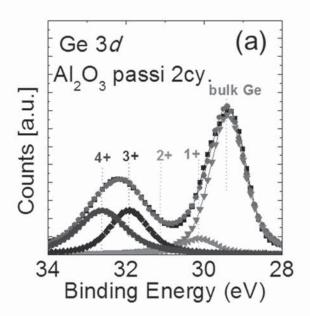

instability of Ge oxides [77], although it was found that they can be slightly reduced with incorporated Al into high-k oxides during the growth process. [112] Ge might diffuse into high-k oxides, which would also lead to interior interface properties. [113] In addition, La<sub>2</sub>O<sub>3</sub> on Ge is also an alternative route to obtain good passivation and nearly ideal C-V characteristics although the reason for this good behavior is not understood at present. [114, 115] Houssa et al. reported the structural and electronic porpoerties of Ge(M)O<sub>2</sub>/Ge interface, with M = Al, La or Hf, using density function theory. [36] Table 2-5 shows coordination of the different metals in the GeO<sub>x</sub> matrix after geometry relaxation of Ge(M)O<sub>2</sub>/Ge (100) structures, and Fig. 2-12 shows electronic density of states of the relaxed Ge(M)O<sub>2</sub>/Ge (100) structures as a function of energy relative to the valence band edge (E<sub>v</sub>) of the Ge slab. This simulations results suggest that because La is 4 fold coordinated in LaGeO<sub>x</sub>, it produces state-free interfaces with Ge, which could explain the experimentally estimated low Dit values. This should be contrasted with the HfO2/Ge case where Hf is 5 fold co-ordinated, giving rise to interface states peak near the conduction band, which, in turn, hampers the electrical performance of Ge devices. In addition, it was also commented that other rare-earth elements like Ce, Gd, Dy, and Lu have a partially filled 4 f-electron shell that has to be included as valence states in the structural and electronic computation of the slab models, which is not straightforward using a classical density function theory (DFT) approach. However, since all these elements tend to be 6 fold co-ordinated in their bulk metal-oxide phase, like La<sub>2</sub>O<sub>3</sub>, it was expected that they would also adopt a 4 fold co-ordination in the GeO<sub>x</sub> interlayer for typical metal concentration below about 10 at.%. Consequently, these rare-earth elements, in contact with Ge, would also lead to a surface-state free Ge energy band gap.