### 저작자표시-비영리-변경금지 2.0 대한민국

# 이용자는 아래의 조건을 따르는 경우에 한하여 자유롭게

• 이 저작물을 복제, 배포, 전송, 전시, 공연 및 방송할 수 있습니다.

### 다음과 같은 조건을 따라야 합니다:

저작자표시. 귀하는 원저작자를 표시하여야 합니다.

비영리. 귀하는 이 저작물을 영리 목적으로 이용할 수 없습니다.

변경금지. 귀하는 이 저작물을 개작, 변형 또는 가공할 수 없습니다.

- 귀하는, 이 저작물의 재이용이나 배포의 경우, 이 저작물에 적용된 이용허락조건 을 명확하게 나타내어야 합니다.

- 저작권자로부터 별도의 허가를 받으면 이러한 조건들은 적용되지 않습니다.

저작권법에 따른 이용자의 권리는 위의 내용에 의하여 영향을 받지 않습니다.

이것은 이용허락규약(Legal Code)을 이해하기 쉽게 요약한 것입니다.

# Ph.D. DISSERTATION

# Interfacial Characterization of GaAs MOS Capacitors and Passivation using High Pressure Oxidation and Ti Scavenging Effect

by

**Hajin Lim**

February 2015

Department of Materials Science and Engineering

College of Engineering

Seoul National University

# Interfacial Characterization of GaAs MOS Capacitors and Passivation using High Pressure Oxidation and Ti Scavenging Effect

Advisor: Prof. Hyeong Joon Kim

# By Hajin Lim

A thesis submitted to the Graduate Faculty of Seoul National

University in partial fulfillment of the requirements for the

Degree of Doctor of Philosophy

Department of Materials Science and Engineering

February 2015

Approved by

Chairman of Advisory Committee: Cheol Seong Hwang

Vice-chairman of Advisory Committee: <u>Hyeong Joon Kim</u>

**Advisory Committee: Young-Chang Joo**

Advisory Committee: <u>Jae Kyeong Jeong</u>

**Advisory Committee: Seok-Jun Won**

## **Abstract**

Recently GaAs has attracted great attention as a promising channel material for sub-10nm logic metal-oxide-semiconductor field effect transistor (MOSFET) due to its high electron mobility and relative large band gap, which allows a high speed operation and low off-state current of the resulting FETs compared to their conventional silicon devices. However, many problems to limit the realization of the MOSFET have still remained unsolved in spite of enormous amount of researches accumulated over the past 3 decades. For such problems, thermal instability of GaAs native oxide can be firstly considered as one of the most crucial issues. The instability of GaAs oxides tends to induce high density of interface states, resulting in Fermi level pinning and frequency dispersion in capacitance-voltage (C-V) curve.

In this study, MOS capacitors using GaAs and various gate dielectric films were fabricated. Electrical characterizations were performed to evaluate the interface properties through C-V hysteresis, frequency dispersion, E<sub>F</sub> movement efficiency and interface states density. Especially to evaluate the deep level interface states of GaAs, C-V and G-V measurements at elevated temperature up to 125 °C were tried in this study. Interfacial analysis by XPS, AES, and TEM were also performed to investigate the compositions and structures of GaAs surface.

Firstly electrical characterizations of GaAs MOS devices were examined to

evaluate the interface states. Significant frequency dispersions in depletion region at high temperature suggest that higher density of interface states exist near the mid-gap. Consistent results were also obtained in the  $D_{it}$  distribution, extracted from conductance method. It was confirmed that huge interface states more than  $x10^{13}$  cm<sup>-2</sup>eV<sup>-1</sup> was observed in the mid-gap region not band edge unlike Si showing the U-shape profiles.

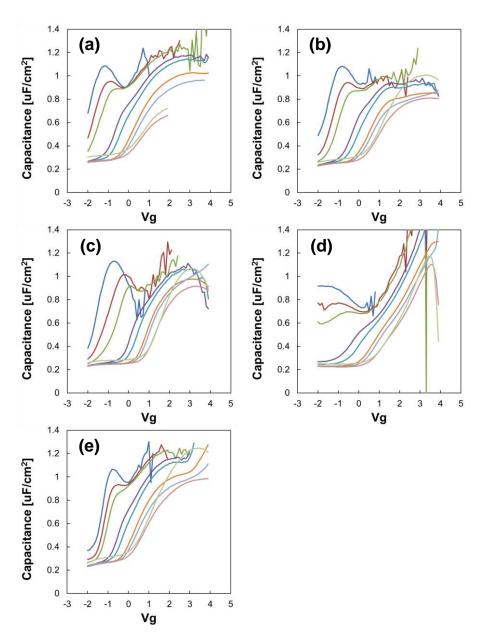

To investigate the origin of the high mid-gap D<sub>it</sub>, the effects of Ga oxide at GaAs interface were examined by adopting the thin Ga<sub>2</sub>O<sub>3</sub> insertion layer, which was deposited by ALD on GaAs prior to gate dielectric film. For the Ga<sub>2</sub>O<sub>3</sub> inserted samples, two times larger hysteresis and huge frequency dispersions in C-V curves compared to the control Al<sub>2</sub>O<sub>3</sub> were observed indicating that the Ga<sub>2</sub>O<sub>3</sub> acts as the defective species inducing high interface states. Different electrical results according to dielectric materials could be explained correlated with the amount of interface Ga<sub>2</sub>O<sub>3</sub> which can be naturally formed during thermal process.

For the passivation of the GaAs interface, new approaches using high pressure oxidation and Ti scavenging effect were employed to suppress the  $Ga_2O_3$  generation. For high pressure oxidation samples, hysteresis and frequency dispersion at the depletion range were substantially improved. Significant reduction of mid-gap  $D_{it}$  was also observed down to  $3.4 \times 10^{12}$  cm<sup>-2</sup>eV<sup>-1</sup> at  $E_i + 0.25$  eV and  $6.2 \times 10^{12}$  cm<sup>-2</sup>eV<sup>-1</sup> at  $E_i - 0.2$  eV in upper half and lower half band gap respectively, which was less than half level of unpassivated samples. These improvements are attributed to the composition

rearrangement converting to As excess and Ga deficient surface. This

composition surface can be obtained by selective oxidation of Ga and

subsequent removing of Ga<sub>2</sub>O<sub>3</sub> through high pressure oxidation and HF wet

etching, respectively. This surface structure can effectively block oxygen

transfer to the GaAs substrate and suppress the generation of interfacial Ga<sub>2</sub>O<sub>3</sub>.

In this case, high pressure process was also verified to be more effective to

form As layer compared to atmospheric pressure process.

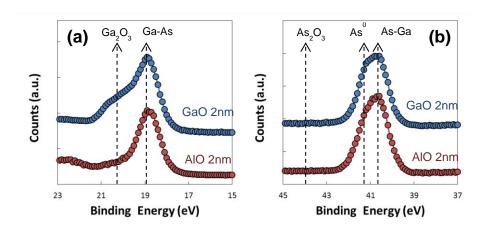

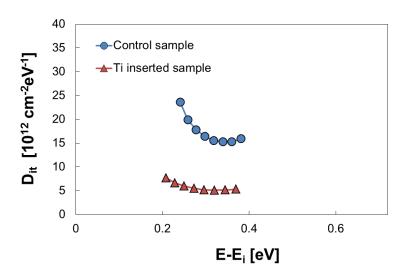

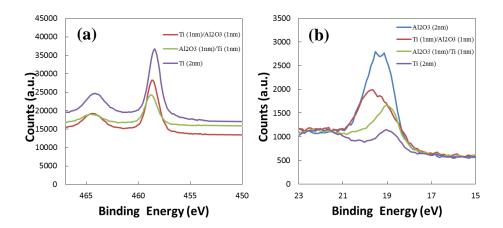

For Ti passivation, reductions of hysteresis and interface states by ~40%

were also obtained. From the XPS analysis much less Ga<sub>2</sub>O<sub>3</sub> were observed in

Ti inserted sample compared to control sample. Scavenging effect due to high

oxygen affinity of Ti is believed to effectively suppress the surface oxidation

resulting Ga<sub>2</sub>O<sub>3</sub>.

In conclusion, high pressure oxidation and insertion of Ti scavenging film

are the effective ways to passivate the GaAs interface for controlling the

formation of Ga<sub>2</sub>O<sub>3</sub> at the interface.

Keywords: GaAs, Ga oxide (Ga<sub>2</sub>O<sub>3</sub>), elemental As, interface state,

high pressure oxidation, scavenging effect

**Student Number: 2011-30194**

Hajin Lim

iii

# **Table of Contents**

| Abstract                                                               | i    |

|------------------------------------------------------------------------|------|

| Table of Contents                                                      | iv   |

| List of Tables                                                         | viii |

| List of Figures                                                        | ix   |

| 1. Introduction                                                        | 1    |

| 2. Literature Review                                                   | 7    |

| 2.1. Oxide formation of GaAs                                           | 7    |

| 2.1.1. Stable oxidation states on GaAs                                 | 7    |

| 2.1.2. Ga-suboxides                                                    | 11   |

| 2.2. Oxide deposition on GaAs by ALD                                   | 16   |

| 2.2.1. Precursors and oxidizers for ALD                                | 16   |

| 2.2.2. ALD Al <sub>2</sub> O <sub>3</sub> and HfO <sub>2</sub> on GaAs | 19   |

| 2.3. Electrical behaviors of III–V MOS devices                         | 24   |

| 2.3.1. Frequency dispersion in C–V measurements                        | 24   |

| 2.3.1.1. Nicollian and Brews model                                     | 24   |

| 2.3.1.2. Hasegawa and Sawada model                                     | 29   |

| 2.3.2. Hysteresis in C–V measurements                                                   |

|-----------------------------------------------------------------------------------------|

| 2.3.3. Temperature dependence of trap response                                          |

| 2.3.4. Conductance method for D <sub>it</sub> extraction41                              |

| 2.4. Surface passivation of III-V semiconductors                                        |

| 2.4.1. Ga <sub>2</sub> O <sub>3</sub> (Gd <sub>2</sub> O <sub>3</sub> ) gate dielectric |

| 2.4.2. Si interface passivation layer                                                   |

| 2.4.3. Sulfur passivation                                                               |

| 2.4.4. Hydrogen annealing                                                               |

|                                                                                         |

| 3. Experiments and Analysis 52                                                          |

| 3.1. Experimental procedures for sample preparations52                                  |

| 3.1.1. Fabrication of MOS capacitors with different dielectric                          |

| materials52                                                                             |

| 3.1.2. Fabrication of MOS capacitors using HPO passivated                               |

| GaAs60                                                                                  |

| 3.1.3. Fabrication of MOS capacitors using Ti scavenging                                |

| effect64                                                                                |

| 3.2. Electrical and chemical characterization                                           |

| 3.2.1. Electrical evaluation using C-V and G-V measurements66                           |

| 3.2.2. Chemical and structure analysis of GaAs interface68                              |

| 4. Results and Discussions                                                           | 69    |

|--------------------------------------------------------------------------------------|-------|

| 4.1. Evaluation of interface states of GaAs                                          | 69    |

| 4.1.1. High temperature measurement for mid-gap analysis                             | 69    |

| 4.1.2. Electrical characterization of GaAs MOS capacitors                            | 72    |

| 4.2. Effects of interfacial oxides on GaAs                                           | 82    |

| 4.2.1. Electrical characterization with different dielectric films                   | s82   |

| 4.2.2. Effects of interface and bulk of dielectric films                             | 89    |

| 4.2.3. Effects of insertion of Ga <sub>2</sub> O <sub>3</sub> film at GaAs interface | 93    |

| 4.2.4. Formation of Ga <sub>2</sub> O <sub>3</sub> depending on dielectric films     | 101   |

| 4.3. Passivation of GaAs using high pressure oxidation (HPO) .                       | 103   |

| 4.3.1. Effects of HPO passivation on electrical characteristics.                     | 103   |

| 4.3.2. Interfacial analysis of HPO passivated surface                                | 111   |

| 4.3.3. Effects of oxidation temperature and pressure                                 | 119   |

| 4.4. Passivation of GaAs using Ti scavenging effect                                  | 133   |

| 4.4.1. Effects of insertion of Ti film on electronic                                 | rical |

| characteristics                                                                      | 133   |

| 4.4.2. Interfacial analysis of Ti passivated surface                                 | 138   |

|                                                                                      |       |

| 5. Conclusions                                                                       | .141  |

| S References                                                                         | 144   |

| List of publications | 157 |

|----------------------|-----|

| Abstract (in Korean) | 163 |

| Acknowledgement      | 166 |

# **List of Tables**

- Table 2.1. List of stable InGaAs-oxides and their bulk oxide Gibbs free energies. Also shown are XPS core-level binding energies of the stable oxides.

- $Table~2.2.~~ALD~precursors~and~oxidizers~studies~on~In_{_{X}}Ga_{_{(1-x)}}As~surfaces.$

- Table 3.1. Deposition conditions of thermal ALD in detail

# **List of Figures**

- Figure 1.1. 2011 ITRS "Equivalent Scaling" Process Technologies Timing.

- Figure 2.1. XPS core-level spectra showing the oxidation states of GaAs native oxide.

- Figure 2.2. (a) Ga 2p XPS spectrum for an As capped In<sub>0.53</sub>Ga<sub>0.47</sub>As substrate following thermal desorption of the As cap. (b) Ga 2p XPS spectrum of an In<sub>0.53</sub>Ga<sub>0.47</sub>As substrate following decapping and Ga<sub>2</sub>O deposition.

- Figure 2.3. XPS core-level spectrum showing the two interfacial oxidation states of Ga. The suboxide is present for any surface exposed to oxygen or hydroxyls.

- Figure 2.4. XPS of the interfacial reactions after atomic layer deposition of  $Al_2O_3$  and  $HfO_2$ . The reactions with the surface oxides exhibit precursor specific and oxidation state-specific behavior.

- Figure 2.5. Commonly observed frequency dispersion in accumulation for  ${\rm TaN/Al_2O_3} \ \ {\rm stack} \ \ {\rm on} \ \ {\rm both} \ \ {\rm n-} \ \ {\rm and} \ \ {\rm p-type} \ \ ({\rm inset}) \ \ {\rm GaAs} \ \ {\rm MOS}$  capacitor structures.

- Figure 2.6. Modeled GaAs C-V characteristics including classical interface states capacitance.

- Figure 2.7. Simulated C-V characteristics of MOS capacitors on both n-type

- and p-type GaAs using the Hasegawa-Sawada C<sub>it</sub> model.

- Figure 2.8. Band diagram of an n-type MOS structure with a bias voltage  $V_g$  applied between metal and semiconductor.

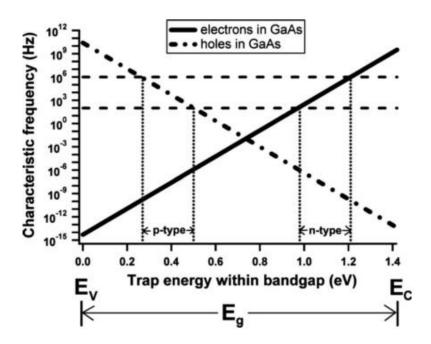

- Figure 2.9. Characteristics emission frequencies of trapped charge in GaAs at room temperature.

- Figure 2.10. Characteristic emission frequencies of trapped charge carriers in GaAs at 150°C. The emission time for electrons (solid line) and holes (dashed-dotted line) is shown.

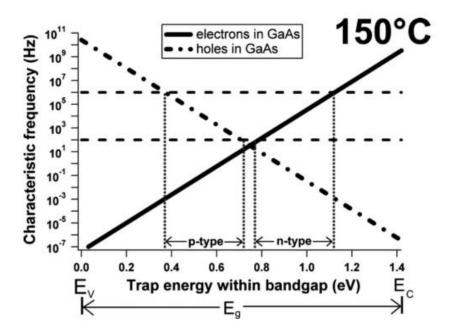

- Figure 2.11. Capacitance- and conductance- voltage measurements on 200um diameter  $GaAs/Al_2O_3$  MOS capacitors at 25°C and 150°C for n-type GaAs and at 25°C and 120°C for p-type GaAs.

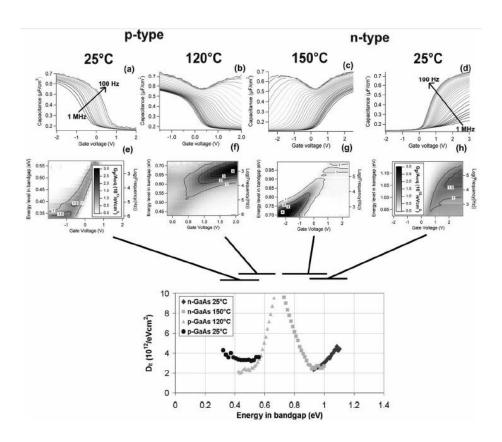

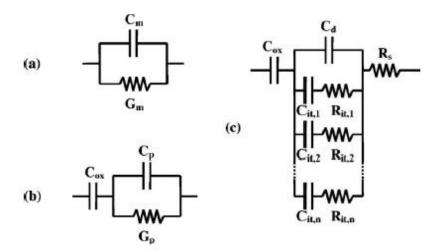

- Figure 2.12. (a) Equivalent circuit of the capacitance (Cm) and parrallel conductance ( $G_m$ ) measured by the experimental equipment. (b) Equivalent circuit showing the oxide capacitance ( $C_{ox}$ ) and the substrate capacitance ( $C_p$ ) and parallel substrate conductance ( $G_p$ ), (c) Equivalent circuit of the total MOS structure, showing the oxide capacitance , the depletion capacitance ( $C_d$ ), the series resistance ( $R_s$ ), and the interface state capacitance ( $C_{it,i}$ ) and the resistance ( $R_{it,i}$ ).

- Figure 2.13. C-V characteristics for an  $Al_2O_3(3nm)/GGO(4.5nm)/In_{0.2}Ga_{0.8}As/GaAs$  MOS diode RTA to  $800^{\circ}C$  with the Au gate

- deposited afterwards.

- Figure 2.14. Dependence of C-V stretch-out and frequency dispersion on the Si interface passivation layer thickness. The  $\Delta C_{max}$  value is normalized to the accumulation capacitance at 1 MHz. The C-V slope is measured at  $C(V_{fb})$  and  $C(V_{fb}+0.3\ V)$ .

- Figure 2.15. Room temperature C-V frequency variation (200 Hz to 100 kHz) of (a) 22%, (b) 10%, (c) 5%, and (d) 1%,  $(NH_4)_2S$  treated,  $Au/Ni/\sim 8nm\ Al_2O_3/n-In_{0.53}GaAs_{0.47}/InP\ devices.$

- Figure 2.16. The C-V characteristics of forming gas annealed  $Pt/Al_2O_3/In_{0.53}Ga_{0.47}As, \ measured \ at \ room \ temperature. \ The \ inset$  shows C-V characteristics of the as-grown  $Pt/Al_2O_3/In_{0.53}Ga_{0.47}As$  measured at room temperature.

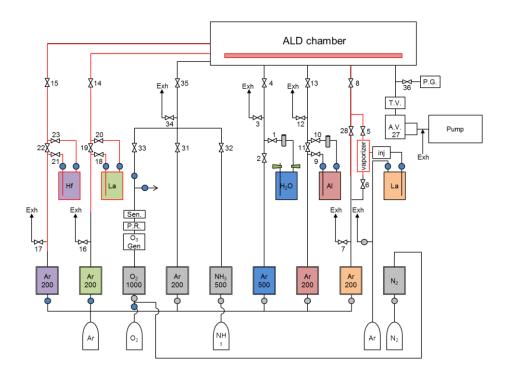

- Figure 3.1. Schematic configuration of thermal ALD equipment employed in these experiments. Red line indicates heating zone.

- Figure 3.2. Process flow for GaAs MOS capacitors using  $Al_2O_3$ ,  $SiO_2$ ,  $La_2O_3$  and  $HfO_2$ .

- Figure 3.3. Process flow for GaAs MOS capacitors with double stacked layers: HfO<sub>2</sub> on SiO<sub>2</sub> and SiO<sub>2</sub> on HfO<sub>2</sub>.

- Figure 3.4. Process flow for GaAs MOS capacitors with and without  $Ga_2O_3$  interfacial layer.

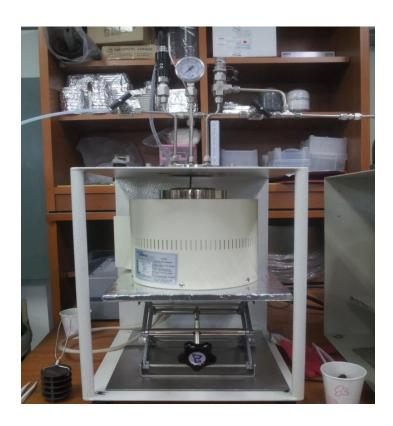

- Figure 3.5. High pressure oxidation equipment employed in this study.

- Figure 3.6. Process flow for GaAs MOS capacitors with HPO passivation.

- Figure 3.7. Process flow for GaAs MOS capacitors with Ti scavenging effect.

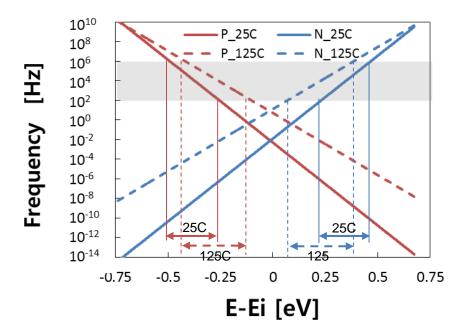

- Figure 4.1. Characteristic frequency versus trap energy showing the temperature dependence of measureable trap location under usual frequency range shaded by gray.

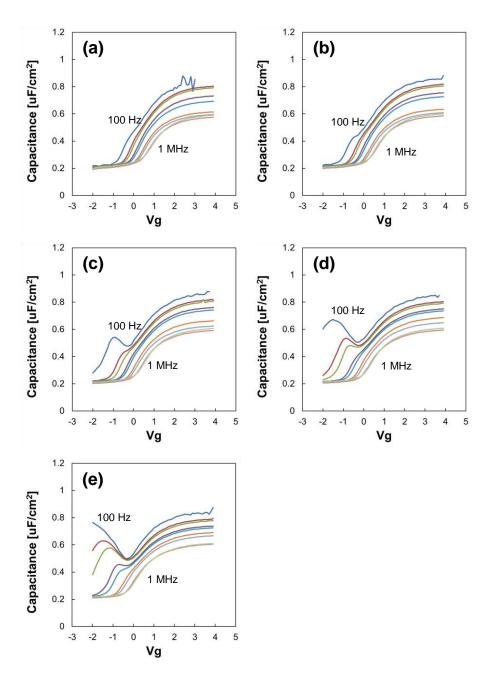

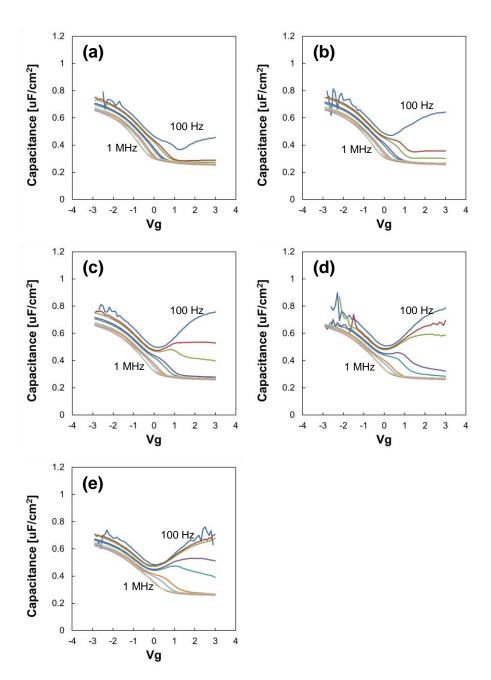

- Figure 4.2. C-V frequency dispersions measured at (a) 25 °C, (b) 50 °C, (c) 75 °C, (d) 100 °C, and (e) 125 °C for La<sub>2</sub>O<sub>3</sub>/n-GaAs MOS capacitors.

- Figure 4.3. C-V frequency dispersions measured at (a) 25 °C, (b) 50 °C, (c) 75 °C, (d) 100 °C, and (e) 125 °C for  $La_2O_3/p$ -GaAs MOS capacitors.

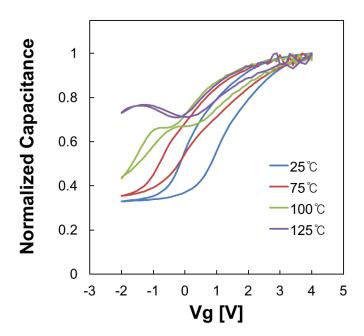

- Figure 4.4. C-V hysteresis behaviors dependent on measurement temperatures.

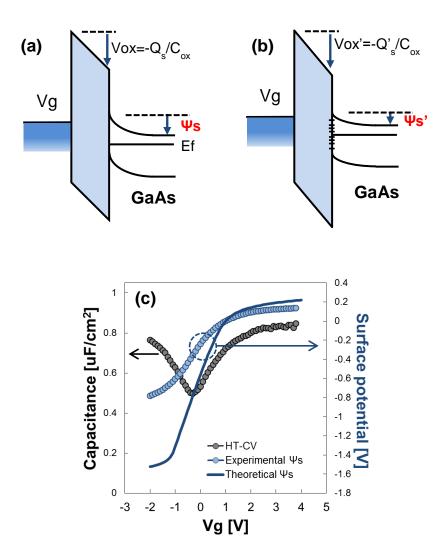

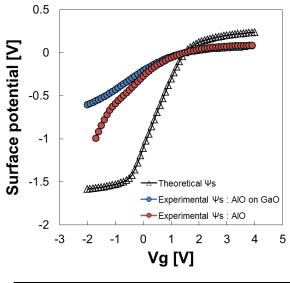

- Figure 4.5. Band structures of MOS capacitors of (a) ideal case ( $D_{it}$ =0) and (b) real case ( $D_{it}$ ≠0). Comparison of experimental and theoretical surface potentials ( $\Psi_s$ ) of La<sub>2</sub>O<sub>3</sub>/GaAs MOS capacitors in (c). Experimental  $\Psi_s$  can be derived from HT-CV.

- Figure 4.6.  $D_{it}$  distribution as a function of trap energy for  $La_2O_3/GaAs$  MOS capacitor.

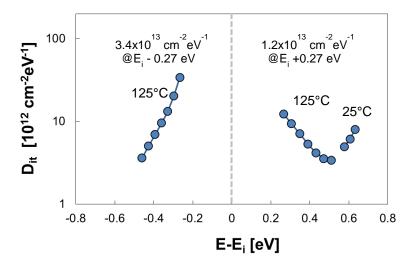

- Figure 4.7. C-V hysteresis for (a) Al<sub>2</sub>O<sub>3</sub>, (b) SiO<sub>2</sub>, (c) La<sub>2</sub>O<sub>3</sub>, and (d) HfO<sub>2</sub>

Distributions of hysteresis voltages are shown in (e).

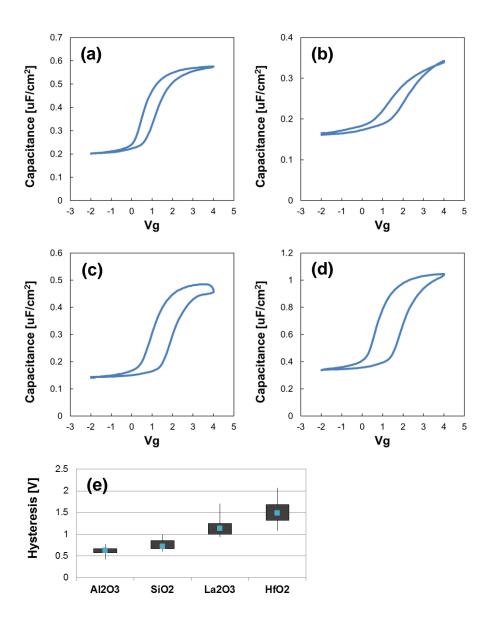

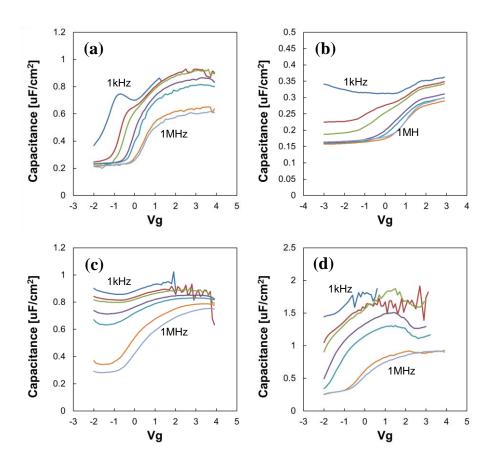

- Figure 4.8. C-V frequency dispersions measured at 25 °C for (a)  $Al_2O_3$ , (b)  $SiO_2$ , (c)  $La_2O_3$ , and (d)  $HfO_2$ .

- Figure 4.9 C-V frequency dispersions measured at 125 °C for (a)  $Al_2O_3$ , (b)  $SiO_2$ , (c)  $La_2O_3$ , and (d)  $HfO_2$ .

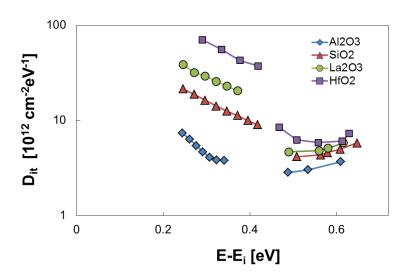

- Figure 4.10.  $D_{it}$  distributions as a function of trap energy for  $Al_2O_3$ ,  $SiO_2$ ,  $La_2O_3$ , and  $HfO_2$ .

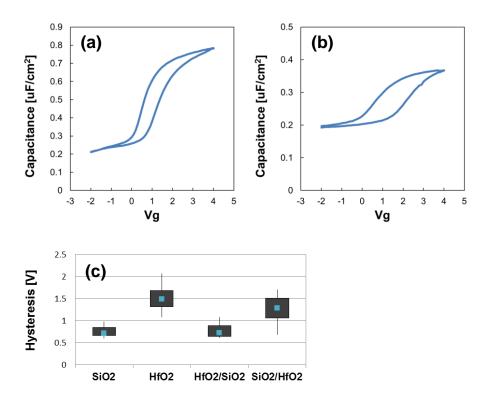

- Figure 4.11. C-V hysteresis for (a)  $HfO_2$  on  $SiO_2$  and (b)  $SiO_2$  on  $HfO_2$ .

Distributions of hysteresis voltages are shown in (c).

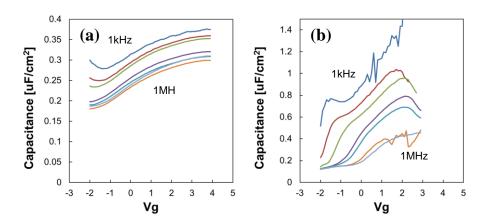

- Figure 4.12. C-V frequency dispersions measured at 125 °C for (a)  $HfO_2$  on  $SiO_2$  and (b)  $SiO_2$  on  $HfO_2$ .

- Figure 4.13. XPS spectra of (a) Ga 3d and (b) As 3d for 2nm thin  $Al_2O_3$  and  $Ga_2O_3$  samples.

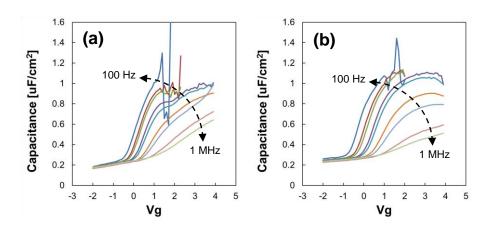

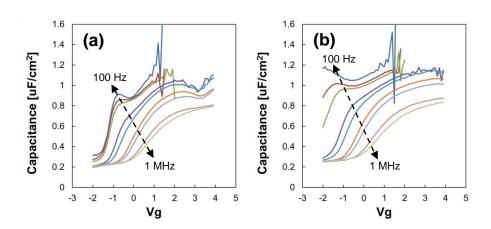

- Figure 4.14. C-V frequency dispersions measured at 25 °C for (a)  $Al_2O_3$  and (b)  $Al_2O_3$  on  $Ga_2O_3$ .

- Figure 4.15. C-V frequency dispersions measured at 125 °C for (a)  $Al_2O_3$  and (b)  $Al_2O_3$  on  $Ga_2O_3$ .

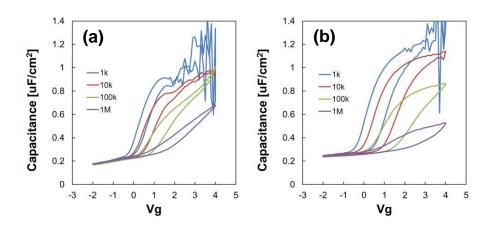

- Figure 4.16. C-V hysteresis measured at the frequency of 1 kHz, 10 kHz, 100 kHz, and 1 MHz for (a)  $\text{Al}_2\text{O}_3$  and (b)  $\text{Al}_2\text{O}_3$  on  $\text{Ga}_2\text{O}_3$ .

- Figure 4.17. Surface potential variations as a function of gate voltage and  ${\rm E_F}$  movement efficiencies as a criterion of Fermi level pinning for

- Al<sub>2</sub>O<sub>3</sub> and Al<sub>2</sub>O<sub>3</sub> on Ga<sub>2</sub>O<sub>3</sub>.

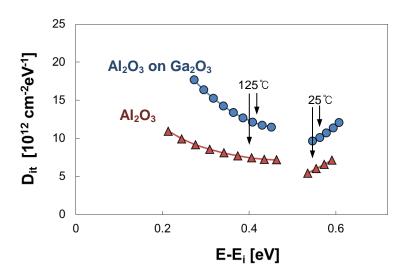

- Figure 4.18.  $D_{it}$  distribution profiles as a function of trap energy measured at 25 °c and 125 °C for  $Al_2O_3$  and  $Al_2O_3$  on  $Ga_2O_3$ .

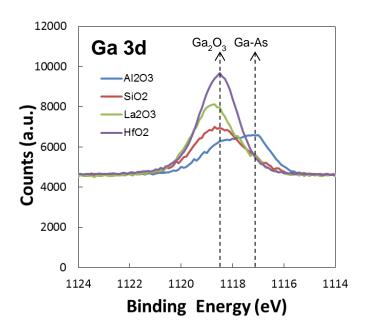

- Figure 4.19. XPS spectra of Ga2p for (a)  ${\rm Al_2O_3}$ , (b)  ${\rm SiO_2}$ , and (c)  ${\rm La_2O_3}$ , and (d)  ${\rm HfO_2}$

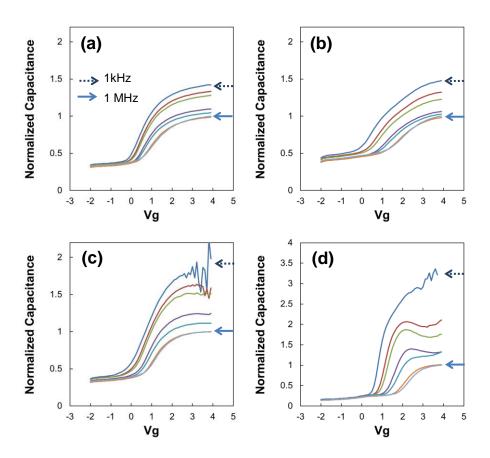

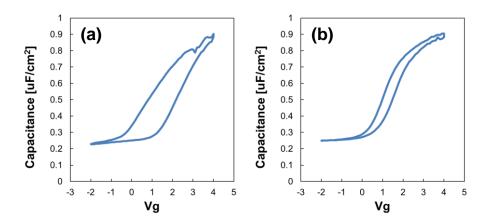

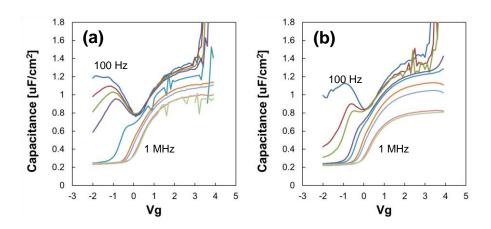

- Figure 4.20. C-V hysteresis for (a) control sample and (b) HPO passivated sample.

- Figure 4.21. C-V frequency dispersions measured at 125° for (a) control sample and (b) HPO passivated sample.

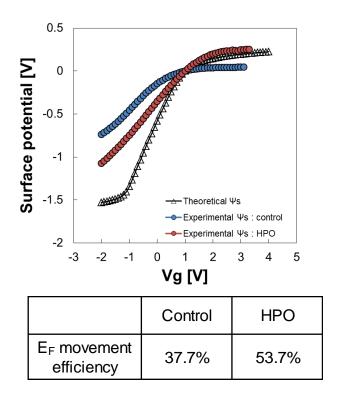

- Figure 4.22. Surface potential variations as a function of gate voltage and  $\rm E_{\rm F}$  movement efficiencies for control sample and HPO passivated sample.

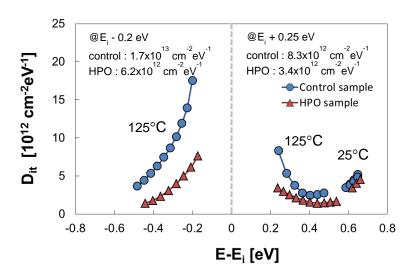

- Figure 4.23.  $D_{it}$  distributions in the GaAs band gap of the control and HPO MOS capacitors. They were extracted from the conductance method at 25 °C and 125 °C using n-type and p-type GaAs MOS capacitors.

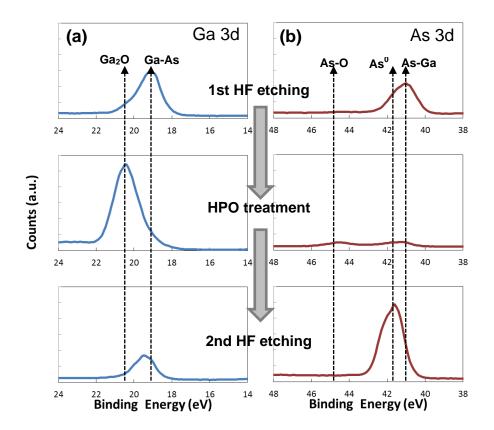

- Figure 4.24. (a) Ga 3d and (b) As 3d XPS spectra showing the chemical evolution of a GaAs substrate after the HPO treatment and subsequent HF etching process.

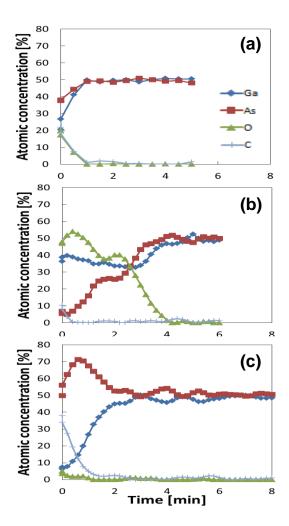

- Figure 4.25. AES depth profiles after the (a) 1st HF etching, (b) HPO and (c) subsequent 2nd HF etching of GaAs substrate.

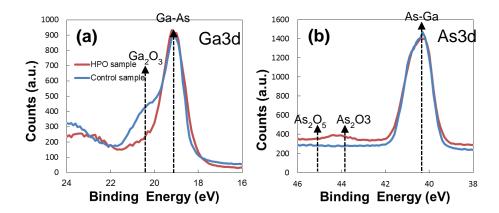

- Figure 4.26. (a) Ga 3d and (b) As 3d XPS spectra showing the Ga-oxide

- (Ga3+) and As-oxide (As3+) on the GaAs surface after  ${\rm Al_2O_3}$  deposition and subsequent annealing at 550 °C among the HPO and control sample.

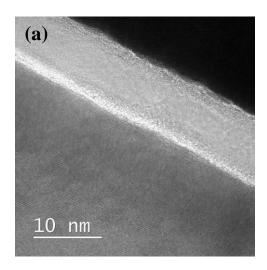

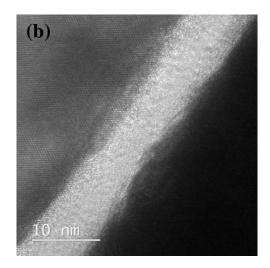

- Figure 4.27. TEM images showing Pt/Al<sub>2</sub>O<sub>3</sub>/GaAs MOS structure for (a) control sample and (b) HPO passivated sample.

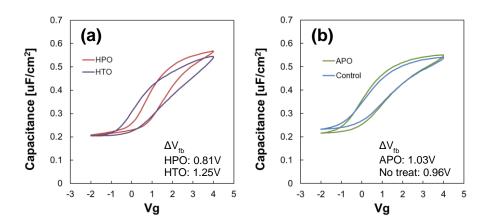

- Figure 4.28. C-V hysteresis of (a) HPO and HTO, and (b) APO and control sample.

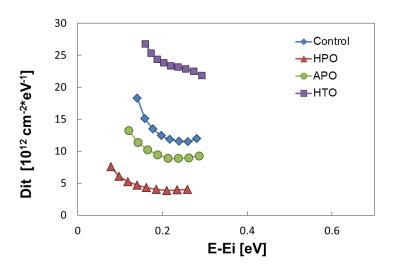

- Figure 4.29. Dependence of  $D_{it}$  distributions on thermal passivation: HPO, APO, HTO and control sample.

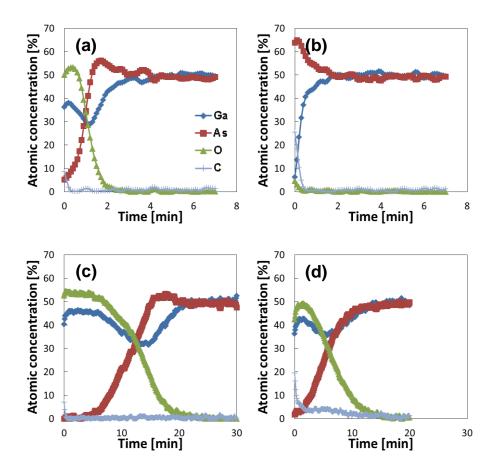

- Figure 4.30. AES depth profiles after thermal oxidation and HF wet etching for APO and HTO sample: (a) after APO, (b) after HF etching of APO sample, (c) after HTO, and (d) ater HF etching of HTO sample.

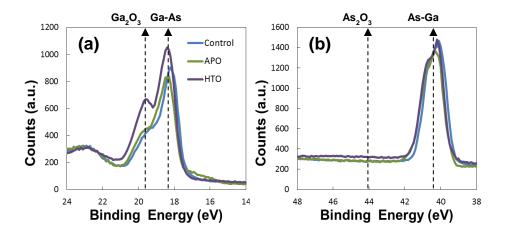

- Figure 4.31. (a) Ga 3d and (b) As 3d XPS spectra for APO, HTO and control sample.

- Figure 4.32. Detailed split conditions for thermal oxidation changing temperature and process time. Numbers in table indicate the oxide thickness in nm grown by thermal oxidation. Four samples in red shaded cell were selected to evaluate the electrical properties.

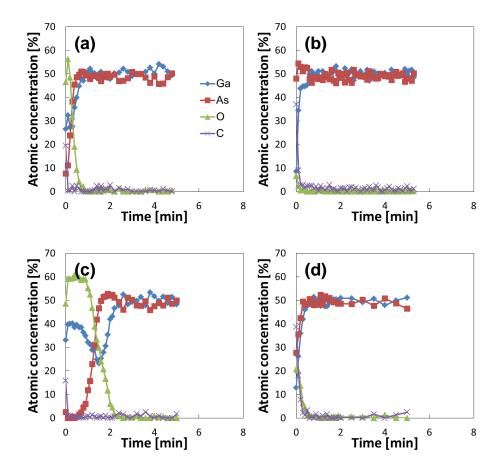

- Figure 4.33. AES depth profiles after thermal oxidation in (a), (c), (e), and (g) and subsequent HF etching in (b), (d), (f), and (h): (a), (b)

- 400°C-4hour, (c), (d) 450°C-2hour, (e), (f) 500°C-1hour, and (g), (h) 550°C-0.5hour.

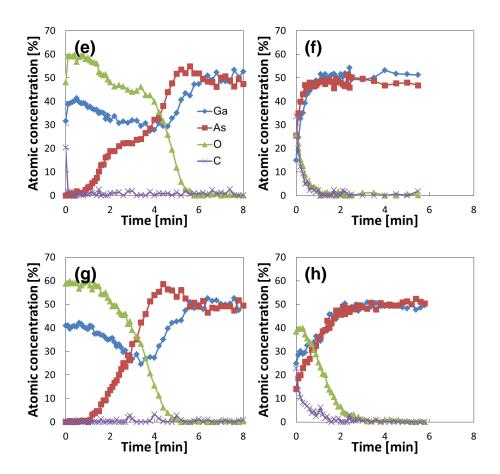

- Figure 4.34. (a) Ga 3d and (b) As 3d XPS spectra for four different annealed samples: 400°C-4hour, 450°C-2hour, 500°C-1hour, and 550°C-0.5hour.

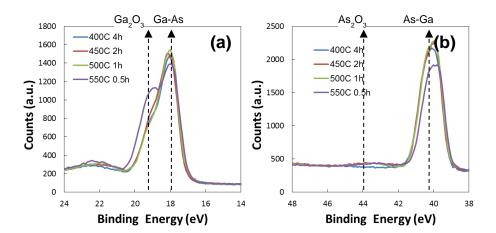

- Figure 4.35. C-V frequency dispersions measured at 125° for (a) 400°C-4hour, (b) 450°C-2hour, (c) 500°C-1hour, (d) 550°C-0.5hour, and (e) control sample.

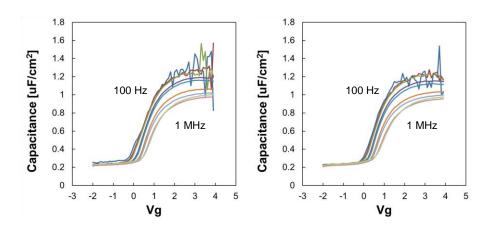

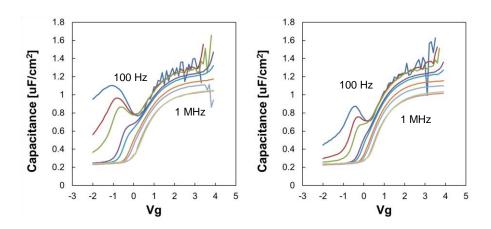

- Figure 4.36. C-V frequency dispersions measured at 25° for (a) control sample and (b) Ti inserted sample.

- Figure 4.37. C-V frequency dispersions measured at 125° for (a) control sample and (b) Ti inserted sample.

- Figure 4.38.  $D_{it}$  distribution profiles with trap energy measured at 125  $^{\circ}$ C for control sample and Ti inserted sample.

- Figure 4.39. XPS spectra showing (a) Ti 2p for  $Ti(1nm)/Al_2O_3(1nm)$ ,  $Al_2O_3(1nm)/Ti(1nm), \ and \ Ti(2nm) \ and \ (b) \ Ga \ 3d \ for \ Al_2O_3(2nm),$   $Ti(1nm)/Al_2O_3(1nm), \ Al_2O_3(1nm)/Ti(1nm), \ and \ Ti(2nm).$

# 1. Introduction

The continuing shrinkage of semiconductor devices is required for high performance and low power consumption. From Moor's law, 30% scaling down is needed at every generation node. However, for 30 - 40nm range devices, dimension scaling will reach the ultimate limitation with only conventional semiconductor materials and technologies due to technical difficulties associated with nanoscale shrinkage. The representative issues would be short channel effect and  $V_{th}$  mismatch for smaller transistors, and large gate leakage current for thinner gate oxides. To overcome these problems, many researches for replacement of conventional SiON/Poly-Si with new high-k/metal gate have been performed [1-9] and for the first time the high-k/metal gate technologies began to be employed in semiconductor industry in 2007 [10, 11].

On the other hand, since the next generation devices beyond 20nm have the obvious limits for improving the performance in the further scaled device using only high-k/metal gate process, intensive researches for introduction of new materials and structures to solve these problems have been performed [12]. Generally three major topics are discussed for future technologies: ultimate EOT scaling, multi-gate transistor, and high mobility channel device as depicted in Fig. 1.1 [13].

For ultimate EOT scaling, introduction of higher-k dielectrics as substitute

Figure 1.1. 2011 ITRS "Equivalent Scaling" Process Technologies Timing [13].

for current HfO<sub>2</sub> and suppression of low-k interfacial layer using scavenging effect have been primarily studied [14, 15].

For the multi-gate transistor, high speed operation is possible through the increased area of current path [16-18]. In addition, improvement of short channel effect can be obtained by better electrostatic control. Recently many device makers adopted this technology for 20nm and 10nm range logic devices.

In case of high mobility channel device, Ge and III-V compound semiconductors have been studied for long times as potential candidates for replacement of conventional Si substrate [19-25]. It has been proposed that n-and p-channels are separately formed using GaAs and Ge respectively. Some of leading semiconductor companies published the research of quantum well field effect transistor (QWFET) using InGaAs [26-28]. However, while the semiconductor road map for 20nm and 10nm range devices clearly suggest the prospective technologies like ultimate EOT scaling and multi-gate transistors, there is still no definite solutions for sub-10nm device in spite of exploring of Ge and III-V materials for next generation channel devices beyond Si.

For GaAs, a great deal of attention has been attracted as a promising channel material for sub-10nm devices due to its high electron mobility and relative large band gap, which allows a high speed operation and low off-state current of the resulting FETs compared to their conventional silicon counterparts [29-32]. However, many problems to limit the realization of the

metal-oxide-semiconductor field effect transistor (MOSFET) have still remained unsolved in spite of enormous amount of researches accumulated over the past 3 decades.

For such problems, thermal instability of GaAs native oxide can be firstly considered as a most crucial issue [33-38]. In the case of Si MOSFETs, the thermal SiO<sub>2</sub> film has excellent interfacial properties and thermal stability with respect to the Si substrate, which allows a low D<sub>it</sub> and low subthreshold gate swing of the resulting FETs. On the other hand, the thermal oxides of GaAs tend to induce unwanted interfacial defects due to lower stabilities. It is well known that such these defects can generate the high density of interface states that can induce Fermi level pinning and hence deteriorate the frequency dispersion and hysteresis properties in capacitance-voltage (C-V) curves [30, 39-44]. Reliability issues such as V<sub>th</sub> shift or dielectric breakdown originated from these interfacial defects are also concerned. In order to passivate the interfacial defects, various approaches have been proposed including epitaxial growth of Ga<sub>2</sub>O<sub>3</sub>(Gd<sub>2</sub>O<sub>3</sub>) [45-47], Ge [48] or Si [49-51] passivation layers, hydrogen passivation [50, 52], sulfur treatment [53-60], and arsenic decapping of GaAs surfaces [61]. However, unfortunately, we have no enough information about the fundamental degradation mechanisms of the GaAs interface. Therefore, understandings of defective species leading the interface degradation as well as the improvement of the interface quality are required for high performance GaAs channel devices.

Secondly, it can be pointed out that selection of appropriate high-k oxides

for GaAs MOSFET are not decided yet. Various high-k oxides for GaAs devices have been examined whereas Hf based oxides were fixed for Si devices [62-65]. Until now, several positive results have been reported including Ga<sub>2</sub>O<sub>3</sub>(Gd<sub>2</sub>O<sub>3</sub>) grown by molecular beam epitaxy (MBE), which is not compatible with mass production. Therefore it becomes key issue to decide suitable high-k oxides having superior electrical characteristics as well as high productivity.

Thirdly, the difficulties of mass-production can also be regarded as critical obstacle in adopting new technologies. There are no practical methods for epitaxial growth of Ge or III-V semiconductors on 300mm Si substrate except MBE showing very low productivity. Many buffer layers to reduce the stress induced by difference of lattice constants can make the process complex and expensive.

This study is primarily focused on the first and second topics which were mentioned above: thermal instabilities of GaAs enabled to induce the interface states and selection of appropriate high-k dielectrics which can mitigate these interfacial defects. Defects species at the interface and its degradation mechanisms are also discussed. Furthermore, new passivation methods using high pressure oxidation (HPO) and insertion of Ti scavenging layer to suppress the interfacial defects will be presented in detail. For HPO, the passivation effect will be explained through the evolution of surface composition of GaAs analyzed by x-ray photoelectron spectroscopy (XPS) and auger electron spectroscopy (AES). For Ti scavenging passivation,

suppression of defect species will be addressed in terms of strong oxygen affinity of Ti.

This dissertation is organized with 5 chapters. In Chapter 2, thermal stabilities of the native oxides of GaAs and electrical characterization of the MOS devices in literature are described. Various passivation processes of GaAs surface are also given with recently published paper. Chapter 3 shows experiments and analysis methods employed in our study. Fabrication of MOS capacitors using various dielectrics and surface treatments are illustrated in detail. Different methodologies of electrical characterization of GaAs samples compared to Si are introduced based on C-V and G-V measurements. Chapter 4 provides the degradation mechanism and the passivation processes to improve the interface qualities. To evaluate the mechanism, the effects of Ga<sub>2</sub>O<sub>3</sub> at the GaAs interface on electrical properties are discussed. Electrical properties depending on high-k gate dielectrics are explained relating to Ga<sub>2</sub>O<sub>3</sub>. Two passivation methods using high pressure oxidation and Ti scavenging effect are presented. In HPO part, different oxidation conditions are also examined and compared with HPO condition to investigate the effect of pressure and temperature during thermal oxidation. Finally, Chapter 5 summarizes the conclusions of this study.

# 2. Literature Review

## 2.1. Oxide formation of GaAs

### 2.1.1. Stable oxidation states on GaAs

It is well known that As<sub>2</sub>O<sub>3</sub>, As<sub>2</sub>O<sub>5</sub>, Ga<sub>2</sub>O<sub>3</sub>, Ga<sub>2</sub>O, and GaAsO<sub>4</sub> can be generated by the oxidation of GaAs [33-35, 66-69]. Gibbs free energies of the relevant bulk native oxides of InGaAs are shown in Table 2.1 [39, 42, 67, 69, 70]. In terms of the relative stabilities of Ga-oxides and As-oxides, these Gibbs free energies can provide the useful guideline that the lower free energy indicate the more stable oxide. From the comparison of the Metal<sub>2</sub>O<sub>3</sub>, it is clearly shown that the As-oxides are the most unstable while the Ga-oxides are the most stable. This holds true for other oxidation states like Metal<sub>2</sub>O. From these trends, the progression of native oxides on the substrate can be easily expected when the high temperature processes are given. Therefore less stable oxides like As<sub>2</sub>O<sub>3</sub> can be easily removed or converted to the more stable oxides, in particular Ga<sub>2</sub>O<sub>3</sub>. Because of the stability of this particular oxidation state, this stable oxide can remain during typical chemical processing or relatively low temperature thermal desorption.

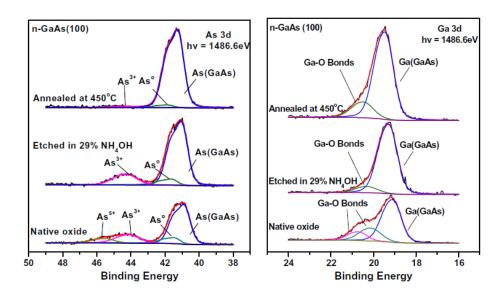

As shown in Fig. 2.1, native oxides composed mainly of As 5+, As 3+, Ga 3+, and Ga 1+ oxidation states and a small amount of elemental As can be

Table 2.1. List of stable InGaAs-oxides and their bulk oxide Gibbs free energies. Also shown are XPS core-level binding energies of the stable oxides [39, 42, 67, 69, 70].

| Oxide              | Gibbs free energy,<br>$\Delta G$ (kcal/mol)<br>-75.3 | XPS core-level binding energy (eV) |           |

|--------------------|------------------------------------------------------|------------------------------------|-----------|

| Ga <sub>2</sub> O  |                                                      | 1117.3 (2p3/2)                     | 19.6 (3d) |

| $Ga_2O_3$          | -238.6                                               | 1117.9 (2p3/2)                     | 20.2 (3d) |

| GaAsO <sub>4</sub> | -212.8                                               | 1118.8 (2p3/2)                     | 21.1 (3d) |

| $In_2O_3$          | -198.6                                               | 444.7 (3d)                         |           |

| InAsO <sub>4</sub> | -209.4                                               | 445.3 (3d)                         |           |

| $As_2O_3$          | -137.7                                               | 1325.4 (2p3/2)                     | 43.7 (3d) |

| $As_2O_5$          | -187                                                 | 1326.7 (2p3/2)                     | 45.0 (3d) |

Figure 2.1. XPS core-level spectra showing the oxidation states of GaAs native oxide [68, 69].

created at the low growth temperature [68, 69]. However if the oxides are formed at higher temperature or annealed under an increased thermal budget, the composition of the oxide can change dramatically. As-oxides become less pronounced due to less stability as the temperature increases and eventually sublimate from the oxide layer or oxidize the GaAs resulting in the formation of stable oxides like Ga<sub>2</sub>O<sub>3</sub> [39]. As-oxide can be further reduced by a postetch, in situ anneal in vacuum up to 450 °C. From the XPS analysis of the O1s for the annealed surface, it is found that the O intensity for the etched surface and the annealed surface is comparable, suggesting that no significant oxygen loss occur. Therefore it implies that the bond conversion from As–O bonding to Ga–O bonding arises under such annealing treatments. For temperatures above 500 °C, As-oxide is below the detection limit while the oxide becomes almost completely Ga<sub>2</sub>O<sub>3</sub>. According to Eq. (2.1) [67],

$$As_2O_3 + 2GaAs \rightarrow Ga_2O_3 + 4As \tag{2.1}$$

elemental As should also appear for these higher temperature process which is reported in most of the literatures[68, 69]. As expected in the reaction (2.1), this elemental As is primarily located at the interface. Some of elemental As may diffuse through the oxide layer to form GaAsO<sub>4</sub> or As-oxide which is highly unstable and easily evaporate during annealing [71].

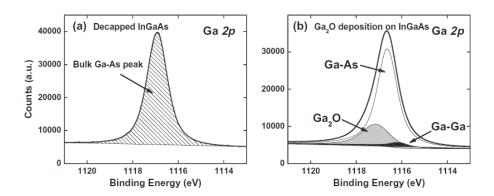

### 2.1.2. Ga-suboxides

Because the As-oxides are very unstable and easily decomposed to elemental As under chemical and thermal process, the role of Ga-oxides are important in terms of the interface characteristics [30, 42, 68, 69, 72]. From the analysis mentioned above, substantial Ga-oxides obviously form on the surface. As shown in Fig. 2.2 (a), reference binding energy and linewidth for Ga 2p spectra of Ga-As bond can be given through in situ XPS analysis of a thermally decapped InGaAs surface without chemical contamination. It was confirmed that oxidized species or spurious carbon were not detected from the inspection of related spectra [68]. These results can be also obtained from the hydrogen cleaned GaAs samples as well. Subsequent Ga<sub>2</sub>O beam exposure on the decapped InGaAs results in different feature of Ga 2p spectra, which is asymmetric and measurably broader, compared to the initial decapped surface [73-75]. At this time As-O and spurious C were not detected.

From the comparison of the Ga 2p spectra between initial decapped surface and Ga<sub>2</sub>O exposed surface, it was confirmed that the minimum two additional spectral features were created. The feature at 0.55eV higher binding energy than the bulk peak is therefore due to the Ga 1+ oxidation state, originating from Ga<sub>2</sub>O on the surface. In addition, small amount of Ga-Ga bonding originating from the powder source used in this experiment may bring on the slightly detectable feature at ~1116.1 eV. Similar results are obtained for GaAs as well.

Figure 2.2. (a) Ga 2p XPS spectrum for an As capped  $In_{0.53}Ga_{0.47}As$  substrate following thermal desorption of the As cap. (b) Ga 2p XPS spectrum of an  $In_{0.53}Ga_{0.47}As$  substrate following decapping and  $Ga_2O$  deposition [68, 69].

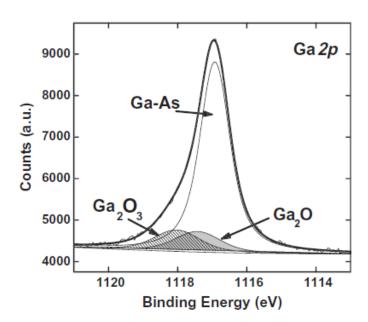

As described above, higher oxidation states of Ga can be shown for In<sub>x</sub>Ga<sub>(1-</sub> x) As surfaces as well. It is generally known that Ga–O bonds are located at the 1–2 eV higher binding energies than the bulk Ga–As peak. After wet cleaning of native oxide using NH<sub>4</sub>OH, a large shoulder on the high binding energy side of the bulk peak appears extending above 1 eV from the bulk peak, indicating the existence of another oxidation state of Ga. These spectra can be convoluted by two oxidation states of Ga, the Ga 1+ oxidation state (Ga<sub>2</sub>O) and the Ga 3+ oxidation state (Ga<sub>2</sub>O<sub>3</sub>) as seen in Fig. 2.3 [42, 68, 69, 76]. Since binding energies of the bulk Ga-As peak and Ga 1+ peak were already determined from the experiments of thermally decapped and Ga<sub>2</sub>O exposed surfaces, the peak position of Ga 3+ can be derived from the deconvolution of the full spectra of Ga 2p resulting in the binding energy located at 1.2 eV above the bulk peak. For the samples with substantially thick oxides, a higher binding energy state near 1.6 eV above the bulk peak may also appear. Several states including GaAsO<sub>4</sub>, Ga(AsO<sub>3</sub>)<sub>3</sub> as well as Ga(OH)<sub>3</sub> [67] are possible for this thick sample. These sates are easily removed under chemical treatment. However through the careful analysis of Ga 2p spectra Ga-suboxides (Ga 1+: Ga<sub>2</sub>O) are conformed to remain stable on all substrate that have had any exposure to oxygen, hydroxyls, etc. despite of its relatively high (less stable) Gibbs free energy. For example, the HF treated GaAs surface has also Ga 1+ as well as Ga 3+ as shown in Fig. 2.3. The reason for the generation of Ga 1+ cannot be explained by the thermodynamic data of bulk oxides. Since the almost of suboxides are found at the substrate interface [42], the effect from

Figure 2.3 XPS core-level spectrum showing the two interfacial oxidation states of Ga. The suboxide is present for any surface exposed to oxygen or hydroxyls [42, 68, 69].

other elements near the interface rather than intrinsic bulk effects are thought to be more dominant. Such suboxides have been characterized by various analysis methods including scanning tunneling microscopy (STM) [73], high-resolution transmission electron microscopy [75], high resolution electron energy loss spectroscopy [77] or XPS [78]. Evaluation of the interfacial effects depending on Ga oxidation states can be regarded as a crucial work to solve the instability of MOS devices.

# 2.2. Oxide deposition on GaAs by ALD

### 2.2.1. Precursors and oxidizers for ALD

Various process conditions for ALD oxide deposition including deposition temperature, delivery system, and ALD process cycle are determined by the precursor characteristics such as vapor pressure, decomposition behavior, sticking coefficient and reaction chemistry. If the oxide deposition are subjected under the temperatures less than 400 °C and 300 °C for GaAs [79] and InAs [80] respectively, desorption of elemental As from the substrate surface would not occur. Thermal instability of III-V substrates could not be caused by ALD process itself.

Two kinds of metal precursors for ALD oxide: metalorganic and inorganic precursors are primarily selected. Halide precursors as the most common inorganic precursors have widely been used in semiconductor industry. Especially HfCl<sub>4</sub> is representative Hf halide compound for ALD and CVD HfO<sub>2</sub>. Although the halide precursors have highly reactivity and thermal stability even up to 750 °C, they have the disadvantages such as low vapor pressure or particle generation due to solid phase. ALD HfO<sub>2</sub> films deposited using HfCl<sub>4</sub> and water below 300–350 °C were known to have high residual impurities such as chlorine and hydrogen [81]. Tri-methyl-aluminum (TMA) as a alkyl precursor, is ideal metalorganic precursors for ALD Al<sub>2</sub>O<sub>3</sub>

containing direct bonding between the metal ion and carbon. In contrast, alkoxides and amides include oxygen and nitrogen bonding between the metal and alkyl groups, respectively. In general, alkyl precursors are highly volatile and very reactive with water through hydrolysis. On the other hand, they often have the relatively low decompose temperature. For example, decompositions occur at the temperatures higher than 275 °C for both TMA and Tetrakis(ethylmethylamido)hafnium (TEMA-Hf) [82, 83]. Thermal stability can be enhanced by the chelation of C (b-diketonates), O (cyclopentadienyls) and N (amidinates) with alkyls to a metal compared to single bond precursors. However they often have low volatility due to their bulky ligands leading low vapor pressure at the deposition temperature.

H<sub>2</sub>O is most widely used as a oxygen source resulting in a OH-terminated surface in metal oxide ALD. However long purge time are required due to its high sticking coefficient on the surface. For O<sub>3</sub> as an alternative oxidant, unreacted or physisorbed O<sub>3</sub> is easily removed out of the chamber during purge period leading the enhanced throughput of ALD process. For ALD HfO<sub>2</sub>, O<sub>3</sub> was also reported to improve the electrical properties with Tetrakis(dimethylamino)hafnium (TDMA-Hf) on Si and decrease the C contamination in the films [84]. However, there still remain unavoidable risks such as surface oxidation of III-V substrates due to its strong oxidation power which can cause undesirable electrical results. Table 2.2 summarizes representative examples for ALD precursors and oxidants [85].

Table 2.2. ALD precursors and oxidizers studies on  ${\rm In_x Ga_{(1-x)}}{\rm As}$  surfaces [69, 85] .

| Dielectric/substrate                     | Precursor                                                                                                                             | Vapor pressure [200] |             |            | Oxidizer/nitridizer                  | $T_{\text{dep}}$ (°C) | $T_{\text{max}}$ (°C)               |

|------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|----------------------|-------------|------------|--------------------------------------|-----------------------|-------------------------------------|

|                                          |                                                                                                                                       | 20 °C                | 100 °C      | 200 °C     |                                      |                       |                                     |

| Al <sub>2</sub> O <sub>3</sub> /n-GaAs   | Al(CH <sub>3</sub> ) <sub>3</sub> [TMA]                                                                                               | 8.6                  | 315         | -          | H <sub>2</sub> O                     | 300                   | 600 O <sub>2</sub>                  |

| Al <sub>2</sub> O <sub>3</sub> /n-InGaAs | Al(CH <sub>3</sub> ) <sub>3</sub> [TMA]                                                                                               | 8.6                  | 315         | -          | H <sub>2</sub> O                     | 300                   | 550 O <sub>2</sub>                  |

| Al <sub>2</sub> O <sub>3</sub> /p-GaAs   | Al(CH3)3 [TMA]                                                                                                                        | 8.6                  | 315         | -          | (CH <sub>3</sub> ) <sub>2</sub> CHOH | 400                   | -                                   |

| AIN/n-, p-InGaAs                         | $AI(N(CH_3)_2)_3$ [TDMA-AI]                                                                                                           |                      |             |            | NH <sub>3</sub>                      | 250                   | 550 N <sub>2</sub>                  |

| HfO2/p-InGaAs                            | HfCl <sub>4</sub>                                                                                                                     | $10^{-6}$            | 0.006       | 5.1        | H <sub>2</sub> O                     | 320                   | 500 O <sub>2</sub> , N <sub>2</sub> |

| HfO <sub>2</sub> /n-InGaAs               | $Hf(NCH_3C_2H_5)_4$ [TEMA-Hf]                                                                                                         | 0.005                | 1.7         | 155        | H <sub>2</sub> O                     | 200                   | -                                   |

| HfO2/n-, p-GaAs                          | $Hf(N(CH_3)_2)_4$ [TDMA-Hf]                                                                                                           | 0.06                 | 15          | 1074       | H <sub>2</sub> O                     | 200                   | 500 N <sub>2</sub>                  |

| Hf-aluminate/n-, p-GaAs                  | Al(CH <sub>3</sub> ) <sub>3</sub>                                                                                                     | 8.6                  | 315         | -          | H <sub>2</sub> O                     | 300                   | 600 N <sub>2</sub>                  |

|                                          | HfCl <sub>4</sub>                                                                                                                     | $10^{-6}$            | 0.006       | 5.1        |                                      |                       |                                     |

| La-aluminate/n-InGaAs                    | Al(CH <sub>3</sub> ) <sub>3</sub><br>La( <sup>i</sup> PrNCHN <sup>i</sup> Pr) <sub>3</sub> [( <sup>i</sup> Pr <sub>2</sub> -fmd)3-La] | 8.6<br>0.008         | 315<br>0.06 | -<br>0.256 | H <sub>2</sub> O                     | 200                   | -                                   |

## 2.2.2. ALD Al<sub>2</sub>O<sub>3</sub> and HfO<sub>2</sub> on GaAs

Ye and coworkers firstly reported depletion mode MOSFET using ALD dielectrics directly on GaAs (100) with 8–16 nm thick  $Al_2O_3$  [86, 87]. During the MOSFET process, GaAs substrate met with vacuum break to transfer into the ALD chamber for  $Al_2O_3$  deposition after MBE GaAs growth. GaAs surface exposed to the atmospheric ambient made inevitably thin native oxide layer consisting of Ga- and As-oxides. It should be noted that the native oxide and elemental As on the GaAs surface can be removed during the ALD process using TMA and  $H_2O$  remaining a only 0.6 nm Ga oxide interfacial layer. Interface state densities  $D_{it} \sim 10^{12}/\text{cm}^2$  eV were extracted for this gate stack [88].

Frank and coworkers reported a subsequent more detailed study using HfO<sub>2</sub> as well as Al<sub>2</sub>O<sub>3</sub> deposition by ALD [62]. It was found that the interfacial layer formed on GaAs surface was significantly affected by the ALD process. Vacuum pre-annealing at 300 °C prior to ALD deposition resulted in a only small decrease of the native oxide suggesting that oxide removal on the substrate hardly occur through this annealing, consistent with prior reports. About 2.5 nm thick oxides on GaAs substrate was generally detected for the GaAs surface. Through the comparison of ALD oxides, ~1 nm thick native oxide was observed for Al<sub>2</sub>O<sub>3</sub> using TMA/H<sub>2</sub>O while a thicker native oxide of ~2-2.5 nm was detected for the HfO<sub>2</sub> using HfCl<sub>4</sub>/H<sub>2</sub>O on either the native oxide or an HF-last surface. Authors suggested that the significantly reduced

interfacial layer from the Al<sub>2</sub>O<sub>3</sub> deposition can be attributed to formation of volatile products in the oxides or conversion of the native oxides to Al<sub>2</sub>O<sub>3</sub> during the ALD process. The difference in accordance with ALD precursors can be explained by the reactivity of Al(CH<sub>3</sub>)<sub>3</sub> compared to HfCl<sub>4</sub> based upon formation enthalpies.

This self-cleaning effect on interfacial oxide has been also observed by others [62, 89-91]. Dalapati and coworkers studied MOS capacitors using Al<sub>2</sub>O<sub>3</sub> (TMA/water), HfO2 (HfCl<sub>4</sub>/water) and nanolaminating layers by ALD on HCl + (NH<sub>4</sub>)<sub>2</sub>S treated GaAs (100) surfaces [62]. Frequency dispersion behaviors of capacitance–voltage (C–V) curves were examined with n-GaAs and p-GaAs at room temperature. Since the capacitance of interface state are directly associated with the frequency, measured total capacitance is also dependent on the frequency. The maximum capacitances shown at the accumulation region of C-V curves generally decrease with an increase of the measurement frequency. Recently such behavior has also been reported by others as well utilizing PVD [49] and ALD [39, 92] dielectrics, and the utilization of Si (or Ge) interfacial passivation layers noted above, and/or post-deposition annealing, improves the dispersion problems on GaAs [93].

Dalapati et al. also investigated the chemical nature of the interface using Al<sub>2</sub>O<sub>3</sub>, HfO<sub>2</sub>, and Al<sub>2</sub>O<sub>3</sub>/HfO<sub>2</sub> nanolaminates [62]. XPS studies revealed that the interfacial oxides consist of Ga- and As-oxides and C-V characteristics can be affected by these interfacial oxides. In addition, they regarded the difference of interfacial oxidation between n- and p-GaAs as dopant-

dependent oxidation process [94, 95] which can result in different C-V behaviors. However, it was reported in recent studies that chemically identical oxide on both n- and p-GaAs was formed and the difference in C-V behaviors was attributed to the capture time constants for electrons and holes rather than any dopant-dependent effects [41].

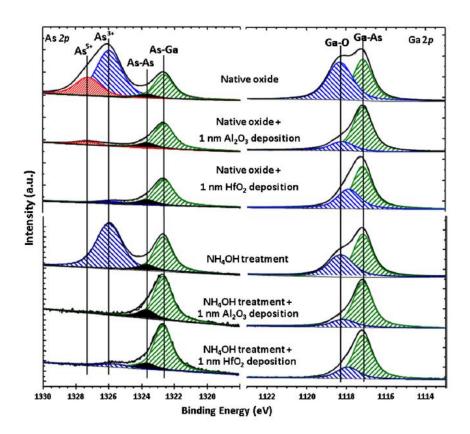

Results of XPS analysis on GaAs surface can be significantly dependent on the surface passivation process or analysis environment such as in situ or ex situ analysis. As shown in Fig. 2.4, in situ analysis performed on the surface oxides before and after formation of 1 nm thin ALD films indicates that almost of the interfacial oxides can be removed below the detection limit of XPS due to ALD self-cleaning effect depending on the oxidation states and ALD precursors [96]. Especially the surface oxide with higher oxidation states which is weakly bonded are completely removed by wet cleaning such as NH<sub>4</sub>OH prior to ALD deposition. In contrast, previous literature also indicates that surface oxide species remain after ALD [62, 97, 98].

The XPS results [30, 69, 96] shown in Fig. 2.4 reveal a reaction mechanism, whereby Al from the TMA preferentially reacts with the As3+ and Ga3+ oxidation states, resulting in bond conversion to Al-oxide. In contrast, the reaction between the 3+ oxidation state and Hf from the TEMA-Hf precursor is less efficient, but the 5+ state is still effective indicating a more complex process. In either case, the weakly bonded oxides may decrease during the ALD process, while the stronger Ga–O bonding, including potential Ga sub-oxide species, can remain at the interface. Therefore it is likely that a

Figure 2.4. XPS of the interfacial reactions after atomic layer deposition of  $Al_2O_3$  and  $HfO_2$ . The reactions with the surface oxides exhibit precursor specific and oxidation state-specific behavior [30, 69, 96].

significant portion of interfacial oxidation can be controlled by precursor-mediated reactions, and detrimental electrical results can be induced by the defects from uncontrolled oxidation such as Fermi level pinning and C–V frequency dispersion [99, 100].

Shift of the Ga–O peak in the Ga 2p spectra toward lower binding energy was observed upon ALD film growth in Fig. 2.4. Such chemical shifts can be explained by the M–O–Ga bonding (where M = Al or Hf), the presence of Ga sub-oxides species (such as O–Ga–O; Ga 1+) in addition to Ga 3+ ( $Ga_2O_3$ ), as well as band bending effects [41, 101].

## 2.3. Electrical behaviors of III–V MOS devices

#### 2.3.1. Frequency dispersion in C–V measurements

#### 2.3.1.1. Nicollian and Brews model

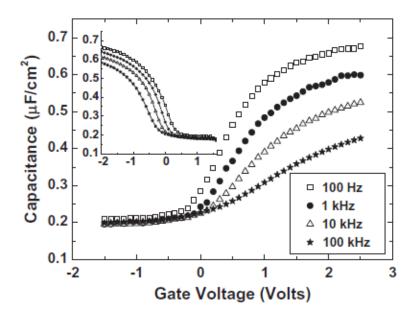

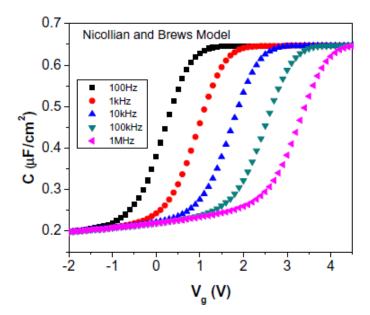

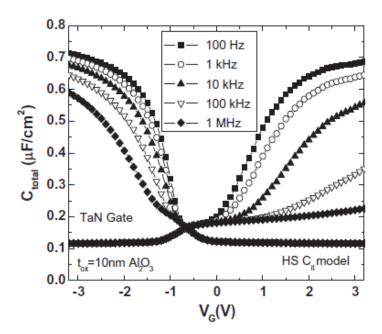

In III-V semiconductors, maximum capacitances in C-V curves generally vary in accordance with measurement frequency as shown in Fig. 2.5 [69]. This anomalous behavior which is referred to as frequency dispersion is known to be observed in numerous III-V semiconductors [102-104]. In case of GaAs, the dispersion characteristic is more prominent in n-type GaAs compared to p-type GaAs MOS capacitors. For  $In_xGa_{1-x}As$ , the effect is intimately dependent on the Indium concentration showing the strong dispersions for low Indium contents and weak dispersions or even no dispersions for x = 0.53 and above.

In general, frequency dispersion can be induced by the high series resistance or high density of interface states. For series resistance, contact resistance, substrate bulk resistance and measurement cable resistance are the possible causes for frequency dispersion [105]. However, because the typical value of series resistance obtained by dielectric breakdown method is approximately  $20~\Omega$ , strong dispersion behavior measured in GaAs MOS capacitors cannot be explained by only this series resistance. According to

Figure 2.5. Commonly observed frequency dispersion in accumulation for  $TaN/Al_2O_3$  stack on both n- and p-type (inset) GaAs MOS capacitor structures [69].

previous numerous researches, it was reported that this frequency dispersion is primarily attributed to a high density of interface states on III-V semiconductors [29, 102, 104, 106-108]. In Fig. 2.6, n-GaAs C–V characteristics were modeled including classical interface state capacitance corresponding to an extremely high interface state density of 1 x 10<sup>13</sup> cm<sup>-2</sup>eV<sup>-1</sup> uniformly distributed in band gap [109]. Simulation of C–V characteristics was performed using a classical model of the total semiconductor charge. Using the surface potential from this solution, the capacitance associated with interface states (C<sub>it</sub>), averaged over band bending, and for a p-type substrate, was calculated numerically as a function of frequency [110].

$$C_{it} = \frac{qD_{it}(2\pi\sigma_s^2)^{-1/2}}{2\omega\tau_p} \int_{-\infty}^{\infty} \exp\left(\frac{-v^2}{2\sigma_s^2}\right) \exp(-v) \tan^{-1}\left(2\omega\tau_p \exp(v)\right) dv \quad (2.2)$$

$$\tau_p = \frac{1}{\bar{\nu}\sigma_p p_s} \quad (2.3)$$

where  $\sigma_s^2$  is the variance of band bending in units of kT/q,  $\omega$  is the measurement frequency in radians,  $\tau_p$  is the characteristic capture time constant for holes, v is band bending,  $\overline{v}$  is the thermal velocity of the carriers (typically  $10^7$  cm/s in silicon at room temperature),  $\sigma_p$  is the capture cross-section for holes, and  $p_s$  is the density of free holes at the substrate surface. The total capacitance ( $C_{tot}$ ) for the MOS capacitor at a given gate voltage ( $V_g$ ) is then obtained using

Figure 2.6. Modeled GaAs C-V characteristics including classical interface states capacitance [39].

$$C_{tot} = \left[ (C_{it} + C_{sub})^{-1} + C_{ox}^{-1} \right]^{-1}. \tag{2.4}$$

The calculated results indicate a frequency-dependent kink in the depletion region of the C-V curve, which is similar to that of silicon but quite different with that of GaAs. In accumulation, since the free electron density ( $n_s$ ) at the semiconductor surface is enough large indicating small trapping time constant according to above Eq. (2.3), all of the interface states can respond to the measurement frequencies and  $C_{it}$  is approximately equal to  $qD_{it}$ . Approaching toward strong depletion,  $n_s$  exponentially decrease resulting in very large  $\tau_n$ . Therefore, interface trap cannot respond with measurement frequencies and  $C_{it}$  approaches zero. In the gate bias range between strong accumulation and strong depletion, only limited interface traps respond to the frequencies. In this case, the value of  $C_{it}$  is between  $qD_{it}$  and zero. The classical interface state capacitance cannot reproduce the measured behavior of many compound semiconductors [111].

#### 2.3.1.2. Hasegawa and Sawada model

The frequency dispersion behaviors observed in III-V semiconductors well coincide with a model developed by Hasegawa and Sawada[103, 104, 107]. According to the classical theory of interface state capacitance, only defects on the interface not in the bulk dielectric can respond to the AC signal during the C-V measurement. However, Deep Level Transient Spectroscopy (DLTS) measurements of interface states performed by Hasegawa and Sawada indicated that the measured trapping time constants did not consistent with the value predicted from the classical assumption. From the trapping time constants extracted by DLTS, it was suggested that an interfacial region located at 0.33 eV lower level than conduction band minimum of GaAs is associated with a thin disordered interfacial layer at the interface and the related disorder-induced gap states (DIGS) where the defects are distributed in both energy and space. Hasegawa and Sawada found that assumption that the distribution of trap into the dielectric is subject to exponential decay satisfying the below equation can explain the dispersion observed in III-V semiconductor.

$$N_T(x) = N_{TO} \exp(-\alpha x) \tag{2.5}$$

where  $N_T(x)$  is the trap density as a function of position and  $\alpha$  is the decay constant. Assuming tunneling into these defects [112], the following

relationship was obtained for the interface state capacitance:

$$C_{it} = \frac{q^2 N_{TO}}{2\kappa_0} (\omega \tau_0)^{(\frac{\alpha}{2\kappa_0})} \int_0^{1/\omega \tau_0} z^{(\frac{\alpha}{2\kappa_0})} \tan^{-1}(z^{-1}) dz$$

(2.6)

assuming,  $\tau(x) = \tau_0 \exp(2\kappa_0 x)$  where  $\kappa_0$  is the quantum-mechanical decay constant of electron wave function, and  $\tau_0$  is the time constant of the trap located at the interface. In Fig. 2.7, total capacitance considering interface state capacitance simulated by means of Hasegawa and Sawada model are given with both n-type and p-type GaAs MOS capacitor, indicating good agreement with the real C-V behavior depending on frequency as shown in the Fig.2.5 [113]. The difference of the dispersions between n-type and p-type GaAs is primarily originated from the difference in trapping time constants for n-type vs. p-type and the energy distribution of interface states [41].

Figure 2.7. Simulated C-V characteristics of MOS capacitors on both n-type and p-type GaAs using the Hasegawa-Sawada  $\rm C_{it}$  model [113].

### 2.3.2. Hysteresis in C–V measurements

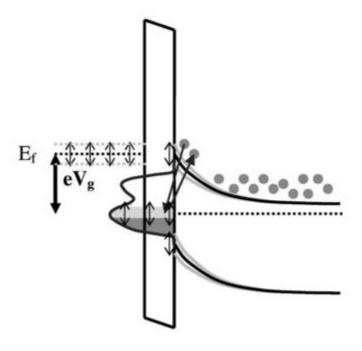

Fig. 2.8 shows band diagram of a typical MOS structure [114], where a certain gate voltage (Vg) is applied between the metal and the semiconductor, leading the band bending of semiconductor characterized as surface potential. Distribution of interface state at the semiconductor-oxide interface is also described in the band diagram. When small AC signal with frequency f and amplitude of several tens of mV superposed on DC bias is applied on gate metal electrode to measure the capacitance as a function of gate voltage, energy bands of the semiconductor move up and down having the same period with AC signal, leading repetitive variation of surface potential. This variation can make the interface states located near the Fermi level filled and emptied. Only if the interface traps placed around the Fermi level have a characteristic response time that is of the order of the measurement frequency f, they can interact with the measurement AC signal and play a role as interface states capacitance. As described in the previous chapter, this capacitance can finally affect the total capacitance of the MOS capacitor depending on measurement frequency.

The characteristic time  $\tau_e$  which it takes for trapped charge to emit from the trapped level  $E_t$  in a semiconductor interface can be calculated from standard Fermi–Dirac statistics and is given by [114, 115]

$$\tau_e = \tau_t \exp(\Delta E/kT) \tag{2.7}$$

Figure 2.8. Band diagram of an n-type MOS structure with a bias voltage  $V_{\rm g}$  applied between metal and semiconductor [114].

where  $\Delta E$  is the energy difference between the majority carrier band-edge energy and the trapping state energy  $E_t$ , k is the Boltzmann constant, T is the semiconductor temperature, and  $\tau_t$  is the charge carrier trapping time constant, given by

$$\tau_t^{-1} = \sigma v_t N \tag{2.8}$$

here  $\sigma$  is the capture cross section of the trapping state,  $v_t$  is the thermal velocity of the majority charge carriers, and N is the density of states in the majority carrier band. (Equation (2.3) is a p-type form of equation (2.9).) From this characteristic emission time  $\tau_e$ , the characteristic response frequency of the corresponding trapping state can be extracted using the equation of  $f_e = 1/2\pi\tau_e$ . This equation reveals that the characteristic emission frequency correlates exponentially with the depth of trapping level in the band gap. As the distance of the trap level from the band edge increases, emission of trapped charge occurs very slowly due to exponential term.

During sweeping the gate bias voltage, Fermi level moves through the band gap. When the characteristic response frequency at a certain position of Fermi level in the band gap become equal to the measurement frequency, this trap lied at the specific Fermi level can react with the outer signal and the capacitance and resistance can be measured by the C-V equipment. From this measurement, information on interface state density as a function of trap level in the band gap can be derived. In Fig. 2.9, the characteristic emission

Figure 2.9. Characteristics emission frequencies of trapped charge in GaAs at room temperature [114, 115].

frequency of traps in GaAs as a function of the position of the trap in the band gap is shown. It is noted that only small portions of the band gap can be accessed using typical range of measurement frequency of 100 Hz to 1 MHz, because of the large band gap of GaAs. The mid-gap interface states cannot be probed by usual measurement conditions, neither on p-type nor on n-type MOS capacitors. These mid-gap traps have extremely small characteristic frequencies on the order of  $10^{-3}$  s<sup>-1</sup> corresponding to characteristic times of the order of 1000 s [59, 114, 115]. Once a charge carrier is trapped in such a mid-gap trap it takes long time extending several tens of minutes to hours to emit from the deep trap. Since these extremely slow traps cannot be accessed using usual measurement frequency of 100 Hz to 1 MHz, trap density at these positions in the band gap are completely veiled. They might just eventually induce the C-V hysteresis which can occur when the trapped charge carriers stay for long time and emit very slowly from such deep interface trap.

#### 2.3.3. Temperature dependence of trap response

There are two solutions to measure the slow mid-gap states. One is extremely low frequency method such as quasi-static C-V which is slow enough to access the deep trap [116]. Another solution is high temperature method which enables the trapped charges at the deep states to be emitted as fast as they can respond with even usual measurement frequency as expected from the exponential term of equation (2.7) [114, 115]. At elevated temperature, even deep level states have reasonable value of characteristic emission time which is measurable using conventional equipment [114, 115, 117]. Fig. 2.10 shows the characteristic emission frequencies as a function of trap energy in the band gap of GaAs at a substrate temperature of 150 °C, assuming a typical capture cross section of 10<sup>-14</sup> cm<sup>2</sup>. The characteristic emission frequencies at 150 °C become 4 orders of magnitude larger than at room temperature, which can measure the mid-gap states using frequencies of the order of 100 Hz. Therefore application of conductance method at room temperature as well as at elevated temperatures up to 150 °C enables extraction of interface states distribution over most GaAs band gap.

Fig. 2.11 shows capacitance ( $C_m$ ) and conductance ( $G_p/A\omega q$ ) as a function of gate bias and frequency respectively for the  $GaAs/Al_2O_3$  samples [114]. To extract the interface states over wide range of band gap, 25 and 150 °C measurements were performed on both n- and p-type MOS capacitors. Every one of the four measurements probes a different energy region in the GaAs

Figure 2.10. Characteristic emission frequencies of trapped charge carriers in GaAs at 150°C. The emission time for electrons (solid line) and holes (dashed-dotted line) is shown [114, 115].

Figure 2.11. Capacitance- and conductance- voltage measurements on 200um diameter  $GaAs/Al_2O_3$  MOS capacitors at 25°C and 150°C for n-type GaAs and at 25°C and 120°C for p-type GaAs [114].

band gap. Densities of interface states measured at room temperature show about ~10<sup>12</sup> cm<sup>-2</sup>eV<sup>-1</sup> on both n- and p-type GaAs corresponding to upper and lower half band gap respectively. However high-temperature measurements up to 150 °C show a very rapid increase of density of interface states toward the mid-gap from the each band edges, leading the interface states more than 10<sup>13</sup> cm<sup>-2</sup>eV<sup>-1</sup>. These huge interface states can affect the Fermi level movement [118-120]. Especially passing of Fermi level through this mid-gap point is effectively suppressed. Since the existence of these high densities of interface states can even induce the Fermi level pinning, we faced the serious problem that surface potential cannot be easily modulated by a gate bias for GaAs MOS devices.

### 2.3.4. Conductance method for D<sub>it</sub> extraction

The conductance method, proposed by Nicollian and Goetzberger [121], has the advantages of high sensitivity and relative simplicity to extract the interface states compared to other methods. Especially conductance method has been widely employed for III-V semiconductors with only MOS structure. In conductance method, D<sub>it</sub> can be determined from the measured capacitance and conductance of the structure under testing [43, 110, 121-123]. Total MOS structure including the interface states can be depicted as the feature like Fig. 2.12 (c), showing the contributions from the oxide capacitance ( $C_{ox}$ ), the capacitance of the depletion region (C<sub>d</sub>), the capacitances (C<sub>it,i</sub>), and resistances ( $R_{it,i}$ ) of the interface states of time constant  $R_{it,i}C_{it,i}$ , as well as the series resistance (R<sub>s</sub>). Simplified equivalent circuit of this MOS structure is shown in Fig. 2.12 (b). Therefore parallel capacitance (C<sub>p</sub>) and conductance  $(G_p)$  in this circuit contain information related with interface states through  $C_{it}$ and R<sub>it</sub>. Fig. 2.12 (a) shows final equivalent circuit of MOS capacitor assumed at the measurement equipment described using capacitance C<sub>m</sub> and conductance G<sub>m</sub>.

From the measured capacitance  $C_m$  and conductance  $G_m$ , one can extract the density of the interface states. Firstly, using equivalent relation of total impedances between two circuits shown in the Fig. 2.12 (a) and (b), conversion from measured value of  $G_m$  and  $C_m$  to  $G_p$  can be derived as the following equation [110],

Figure 2.12. (a) Equivalent circuit of the capacitance (Cm) and parrallel conductance ( $G_m$ ) measured by the experimental equipment. (b) Equivalent circuit showing the oxide capacitance ( $C_{ox}$ ) and the substrate capacitance ( $C_p$ ) and parallel substrate conductance ( $G_p$ ), (c) Equivalent circuit of the total MOS structure, showing the oxide capacitance, the depletion capacitance ( $C_d$ ), the series resistance ( $C_s$ ), and the interface state capacitance ( $C_{it,i}$ ) and the resistance ( $C_{it,i}$ ) [114].

$$G_p = \frac{G_m}{(G_m/\omega C_{ox})^2 + (1 - C_m/C_{ox})^2}$$

(2.9)

Second step is the extraction of  $D_{it}$  from  $G_p$  which is correlated with  $C_{it}$  and  $R_{it}$  as shown in the Fig. 2.12 (b) and (c). Using the equivalent relation, we can obtain the  $D_{it}$  which is linearly proportional to the peak value of a conductance  $G_p/\omega$  as a function of measured frequency f as following equation [110].

$$D_{it}(V_g) \approx 2.5 \frac{(G_p)_{max}}{A\omega q}$$

(2.10)

Here A is the area of the MOS capacitor under testing,  $\omega=2\pi f$ , and q is the charge of the majority charge carrier. Maximum value of  $G_p/\omega$  occurs when the measured frequency is equal to the characteristic emission frequency of the interface states located at a certain energy level in the band gap, which is determine by a given gate bias. As sweeping the gate bias, we can determine energy distribution of  $D_{it}$  showing the interface states as a function of the trap energy level.

## 2.4. Surface passivation of III-V semiconductors

## 2.4.1. Ga<sub>2</sub>O<sub>3</sub>(Gd<sub>2</sub>O<sub>3</sub>) gate dielectric

Hong and coworkers reported Ga<sub>2</sub>O<sub>3</sub>(Gd<sub>2</sub>O<sub>3</sub>) (GGO) grown by MBE on GaAs [45]. In this work, capability of the Ga<sub>2</sub>O<sub>3</sub>(Gd<sub>2</sub>O<sub>3</sub>) deposition processes to provide improved interface qualities between oxide and GaAs was demonstrated. Ex situ process which includes thermal desorption of native oxides of GaAs and subsequent Ga<sub>2</sub>O<sub>3</sub>(Gd<sub>2</sub>O<sub>3</sub>) deposition on GaAs showed low surface recombination velocity S of 9000 cm/s corresponding to D<sub>it</sub> of 10<sup>10</sup> cm<sup>-2</sup>eV<sup>-1</sup> indicating excellent interfacial characteristics.

Systemaic study in terms of the composition of Gd was carried out by Kwo et al [46]. Dependence of dielectric properties of  $(Ga_2O_3)_{1-x}(Gd_2O_3)_x$  on the Gd (x) content exhibits best passivation effect when x exceeds 14%. Low leakage current and low density of interface states could be obtained in films with  $x \ge 14\%$ .

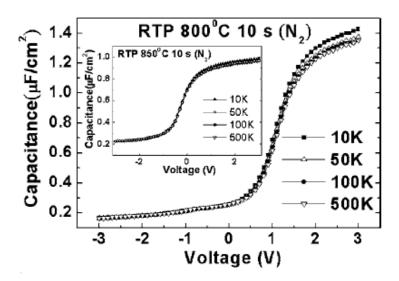

Shiu et al. investigated 1 nm thin passivation layer of  $Ga_2O_3(Gd_2O_3)$  on  $In_{0.2}Ga_{0.8}As$  [47]. Dielectric films comprising  $Al_2O_3/GGO$  revealed atomically sharp smooth interface even after high temperature annealing up to 850 °C. Weak frequency dispersion and low density of interface states in the low  $10^{11}$  cm<sup>-2</sup>eV<sup>-1</sup> could be attained as shown in Fig. 2.13.

Figure 2.13. C-V characteristics for an  $Al_2O_3(3nm)/GGO(4.5nm)/In_{0.2}Ga_{0.8}As/GaAs$  MOS diode RTA to  $800\,^{\circ}C$  with the Au gate deposited afterwards [47].

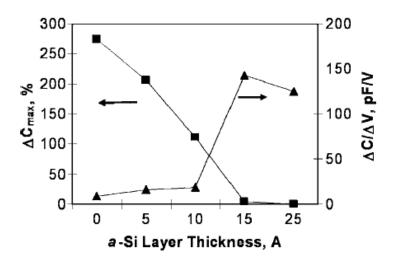

## 2.4.2. Si interface passivation layer

Koveshnikov and coworkers reported the electrical properties of MOS capacitors including in situ passivated with ultrathin amorphous Si (a-Si) layer and with ex situ deposited HfO<sub>2</sub> gate oxide and TaN metal gate on molecular beam epitaxial GaAs [49]. In situ encapsulation of GaAs surface with an amorphous Si resulted in low stretch-out and frequency dispersion in C-V curves, indicating good interfacial properties. In addition, low leakage current densities of <1.0 mA/cm<sup>2</sup> with equivalent oxide thickness of 2.1 nm was also obtained. As shown in Fig. 2.14, minimum thickness of the Si interface passivation layer of 1.5 nm is required to avoid the Fermi level pinning. From transmission electron microscopy analysis, it was revealed that the Si layer was oxidized up to 1.4 nm during ex situ processing while the interface between the GaAs and a-Si remained atomically sharp without any interfacial reaction.

Figure 2.14. Dependence of C-V stretch-out and frequency dispersion on the Si interface passivation layer thickness. The  $\Delta C_{max}$  value is normalized to the accumulation capacitance at 1 MHz. The C-V slope is measured at  $C(V_{fb})$  and  $C(V_{fb}+0.3\ V)$  [49].

## 2.4.3. Sulfur passivation

First sulfur passivation was performed by Sandroff and coworkers using Na<sub>2</sub>S·9H<sub>2</sub>O [53]. They reported that significant current gain with a factor of sixty in GaAs/AlGaAs heterostructure bipolar junction transistor could be achieved by spin coating thin films of Na<sub>2</sub>S·9H<sub>2</sub>O. That passivation mechanism was explained by two step process, comprising removal of native oxide or elemental arsenic and strong sulfur bonding to exposed surface resulting in stable sulfur compound such as GaS and As<sub>2</sub>S<sub>3</sub>.

Carpenter et al. reported the effect of  $(NH_4)_2S$  treatment on surface passivation in GaAs schottky contact [54]. While not-treated sample showed Fermi level pinning leading same schottky barrier regardless of metal work function,  $(NH_4)_2S$  surface treatment resulted in a reduced Fermi level pinning and hence the barrier height could be modulated by the metal work function.

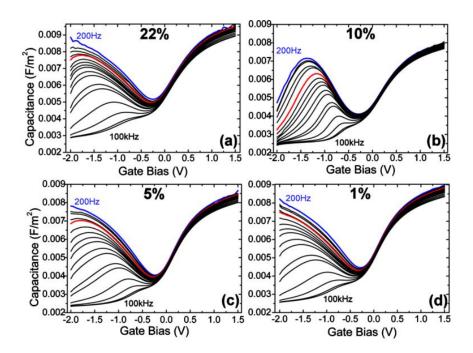

O'Connor presented the effectiveness of  $(NH_4)_2S$  concentrations in the passivation of n-type and p-type  $In_{0.53}Ga_{0.47}As$  MOS capacitors as shown in Fig. 2.15 [60, 124]. Samples were immersed in aqueous  $(NH_4)_2S$  solutions of concentrations 22%, 10%, 5%, or 1% for 20 min at 295 K. Lowest frequency dispersion was obtained in 10% conditions (Fig.2. 15 (b)). Extraction of interface state density were also performed for the optimum 10%  $(NH_4)_2S$  passivated  $In_{0.53}Ga_{0.47}As$  devices, showing  $D_{it}$  of ~2.5 x  $10^{12}$  cm<sup>-2</sup> with the peak density positioned in the middle of the  $In_{0.53}Ga_{0.47}As$  band gap at approximately 0.37 eV (±0.03 eV) from the valence band edge.

Figure 2.15. Room temperature C-V frequency variation (200 Hz to 100 kHz) of (a) 22%, (b) 10%, (c) 5%, and (d) 1%,  $(NH_4)_2S$  treated, Au/Ni/~8nm  $Al_2O_3/n$ -In<sub>0.53</sub> GaAs<sub>0.47</sub>/InP devices [60].

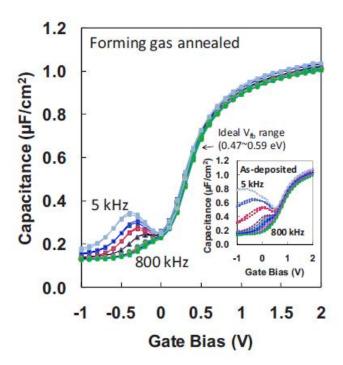

## 2.4.4. Hydrogen annealing

Kim et al. presented charge trapping defects in Al<sub>2</sub>O<sub>3</sub>/n-In<sub>0.53</sub>Ga<sub>0.47</sub>As MOS capacitors and their passivation by hydrogen annealing [125]. In this study, it was found that the trapping in Al<sub>2</sub>O<sub>3</sub>/n-In<sub>0.53</sub>Ga<sub>0.47</sub>As at accumulation occur at not interface traps but border traps in the Al<sub>2</sub>O<sub>3</sub> layer near interface, judged from experimental observation such as temperature independent capacitance. The reason is because tunneling of charges into border traps is affected by only frequency while the trapping and detrapping of interface states is dependent on temperature. Hydrogen annealing at 400 °C shows suppression of frequency dispersion in accumulation and reduction of C-V stretch-out through depletion as shown in Fig. 2.16. Therefore these results indicate that the hydrogen annealing effectively passivates these border traps in the oxides and some, but not all, Al<sub>2</sub>O<sub>3</sub>/InGaAs interface states corresponding to depletion region.

Figure 2.16. The C-V characteristics of forming gas annealed  $Pt/Al_2O_3/In_{0.53}Ga_{0.47}As$ , measured at room temperature. The inset shows C-V characteristics of the as-grown  $Pt/Al_2O_3/In_{0.53}Ga_{0.47}As$  measured at room temperature [125].

## 3. Experiments and Analysis

## 3.1. Experimental procedures for sample preparations

# 3.1.1. Fabrication of MOS capacitors with different dielectric materials

2 inch n- and p-type GaAs wafers doped with Si concentration of  $7.1 \times 10^{17}$  cm<sup>-3</sup> and Zn concentration of  $6.7 \times 10^{17}$  cm<sup>-3</sup> were used for fabrication of GaAs MOS capacitors, respectively. After the dicing of GaAs wafers into ~1cm length, pre-cleaning prior to gate oxide deposition were performed by dipping diluted HF solution of 1.75% concentration. Each piece of GaAs sample is transferred to the deposition chamber within few minutes to prevent the formation of natural oxide on GaAs.

For fabrication of MOS capacitors, 7nm thick Al<sub>2</sub>O<sub>3</sub>, HfO<sub>2</sub>, La<sub>2</sub>O<sub>3</sub>, and SiO<sub>2</sub> films were deposited on cleaned GaAs at 310 °C using a traveling-wave type thermal ALD chamber as depicted in Fig. 3.1. Trimethylaluminium (Al(CH<sub>3</sub>)<sub>3</sub>, TMA), tris(dimethylamino)silane (SiH[N(CH<sub>3</sub>)<sub>2</sub>]<sub>3</sub>, TDMAS), Tris[bis (trimethylsilyl)amino]lanthanum (La[N(Si(CH<sub>3</sub>)<sub>3</sub>)<sub>2</sub>]<sub>3</sub>), and tetrakis (ethylmethylamino)hafnium (Hf[N(C<sub>2</sub>H<sub>5</sub>)(CH<sub>3</sub>)]<sub>4</sub>, TEMAHf) were used as the metal precursors for Al, Si, La, and Hf respectively. Bubbling system for Al, Hf, and Si and liquid delivery system for La were employed. O<sub>3</sub> of 110 g/Nm<sup>3</sup>

Figure 3.1. Schematic configuration of thermal ALD equipment employed in these experiments. Red line indicates heating zone.

was used as a oxidant for each oxide. Detailed conditions for ALD depositions are listed in Table 3.1. The thicknesses of oxides were measured by a spectroscopic ellipsometry. Post deposition annealing was carried out at  $550 \, ^{\circ}$ C in  $N_2$  ambient during 30 seconds.

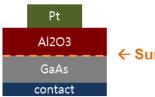

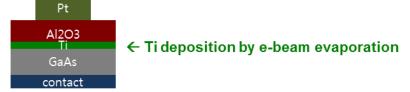

Platinum film, as the metal electrode of the MOS capacitor, was deposited by electron beam evaporation through shadow mask with area of  $6.6 \times 10^4 \, \mu m^2$  placed on each sample to form patterned gate electrode. Indium paste was used as the backside body contact. Process flow employed in chapter 4.1.2 and 4.2.1 is schematically illustrated in Fig. 3.2.

For the evaluation of double stacked dielectric layer which will be discussed in chapter 4.2.2, MOS capacitors with the structures of Pt/HfO<sub>2</sub>(5nm)/SiO<sub>2</sub>(2nm)/GaAs and Pt/SiO<sub>2</sub>(5nm)/HfO<sub>2</sub>(2nm)/GaAs were prepared. For both capacitors, total dielectric thickness including HfO<sub>2</sub> and SiO<sub>2</sub> were 7nm, which were identical with single gate oxide mentioned above. All other process conditions for fabrication of MOS capacitor are also same with the previous single gate oxide MOS capacitors. Fig. 3.3 shows the process flow for the MOS capacitors in detail.