공학박사 학위논문

# Improvement of Low Temperature Solution-processed Oxide Thin Film Transistors by O<sub>2</sub> plasma, UV radiation and Biased-H<sub>2</sub>O annealing

O<sub>2</sub> 플라즈마, 자외선 조사, Biased-H<sub>2</sub>O 어닐링을 통한 저온 용액공정을 이용한 산화물 박막트랜지스터의 특성 향상에 대한 연구

2013년 8월

서울대학교 대학원

전기·컴퓨터 공학부

이정수

## Improvement of Low Temperature Solution-processed Oxide Thin Film Transistors by O<sub>2</sub> plasma, UV radiation and Biased-H<sub>2</sub>O annealing

지도교수 한 민 구

이 논문을 공학박사학위논문으로 제출함 2013년 8월

> 서울대학교 대학원 전기·컴퓨터 공학부 이 정 수

이정수의 박사학위논문을 인준함 2013년 7월

### 학위논문 원문제공 서비스에 대한 동의서

본인의 학위논문에 대하여 서울대학교가 아래와 같이 학위논문 저작물을 제공하는 것에 동의합니다.

1. 동의사항

본인의 논문을 보존이나 인터넷 등을 통한 온라인 서비스 목적으로 복제할 경우 저작물의 내용을 변경하지 않는 범위 내에서의 복제를 허용합니다.

② 본인의 논문을 디지털화하여 인터넷 등 정보통신망을 통한 논문의 일부 또는 전부의 복제·배포 및 전송 시 무료로 제공하는 것에 동의합니다.

2. 개인(저작자)의 의무

본 논문의 저작권을 타인에게 양도하거나 또는 출판을 허락하는 등 동의 내용을 변경하고자 할 때는 소속대학(원)에 공개의 유보 또는 해지를 즉시 통보하겠습니다.

3. 서울대학교의 의무

(1) 서울대학교는 본 논문을 외부에 제공할 경우 저작권 보호장치(DRM)를 사용하여야 합니다.

② 서울대학교는 본 논문에 대한 공개의 유보나 해지 신청 시 즉시 처리해야 합니다.

논문제목: Improvement of Low Temperature Solution-processed Oxide Thin Film Transistors by O<sub>2</sub> plasma, UV radiation and Biased-H<sub>2</sub>O annealing

> 학위구분: 석사 □· 박사 ■ 학 과: 전기·컴퓨터 공학부 학 번: 2008-20944 연 락 처: autxider@naver.com 저 작 자: 이 정 수 (인)

제 출 일:2013년 8월 2일

서울대학교총장 귀하

### Abstract

# Improvement of Low Temperature Solution-processed Oxide Thin Film Transistors by O<sub>2</sub> plasma, UV radiation and Biased-H<sub>2</sub>O annealing

Jeong-Soo Lee

Department of Electrical Engineering and Computer Science College of Engineering Seoul National University

Solution-processed oxide thin film transistors (TFTs) with zinc-tin-oxide (ZTO) and indium-gallium-zinc-oxide (IGZO) have attracted considerable attention for the driving elements of active matrix display, instead of Si-based TFTs and organic TFTs, because of high mobility, visible light transparency, flexibility, wide range of materials, and controllability of electrical properties by atomic composition. Solution-processed oxide TFTs show superior performance for active matrix liquid crystal display (AMLCD) and active matrix organic light emitting diode (AMOLED) display backplanes, compared with solution-processed oxide TFTs are compatible with large area due to good uniformity and high throughput, so that could be a method for achieving low cost fabrication contrary to vacuum processes.

Among various ZnO-based oxide semiconductors, ZTO TFTs employing tin (Sn) material maybe promising candidates for achieving low cost processes because Sn is a quite low cost material compared with widely used indium (In).

Solution-processed ZTO TFTs need to be fabricated on inexpensive and flexible substrates such as glass and plastic for additional cost reduction and application extension to a flexible display. For solution-processed ZTO TFTs fabrication with these flexible substrates, low temperature processes are necessary because these substrates are easily damaged at high annealing temperatures. At low annealing temperature, however, solution-processed ZTO TFTs have poor performance such as low on-current, high threshold voltage and low mobility, so a rather high annealing temperature exceeding 500 °C is required in solutionprocessed ZTO TFTs. To improve the device characteristics of solution-processed oxide TFTs even at low annealing temperature on an active layer, a study of the effects of annealing temperature on the electrical characteristics of solutionprocessed oxide TFTs and the efforts to achieve high device characteristics of solution-processed oxide TFTs even at low annealing temperature on active layer are desired. There were some efforts to investigate the effects of annealing temperature on solution-processed oxide TFTs, but the electrical and chemical mechanisms of annealing temperature on solution-processed oxide TFTs have been scarcely studied.

The purpose of this thesis is to fabricate oxide TFTs employing solution-process for an oxide semiconductor active layer with various annealing temperatures to investigate the effects of annealing temperature on the electrical characteristics of solution-processed oxide TFTs such as threshold voltage, saturation mobility, and reliability, and to improve the electrical characteristics of low temperature solution-processed oxide TFTs for low cost, stable, and flexible active matrix display backplane.

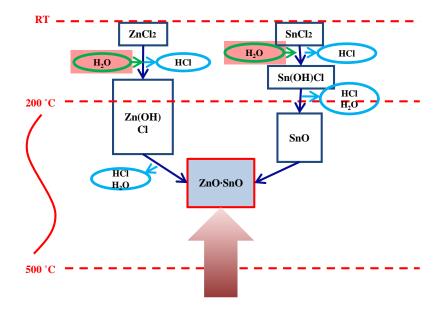

The effects of annealing temperature on the bonding structure of ZTO active layer in solution-processed ZTO TFTs were investigated and the chemical formation equation of the ZTO active layer with regard to the annealing temperature was established.

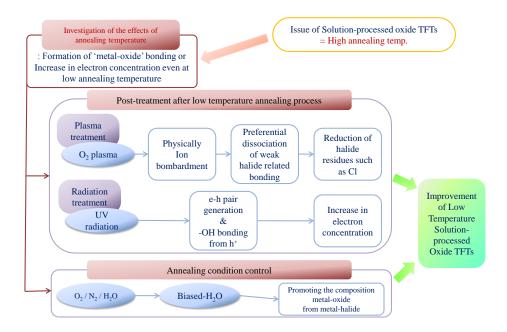

To improve the electrical characteristics of low temperature solution-processed oxide TFTs according to the investigation of effects of annealing temperature in regard of the chemical formation of ZTO active layer, O<sub>2</sub> plasma treatment, UV radiation treatment, and the biased-H<sub>2</sub>O annealing were proposed to achieve high device characteristics of solution-processed oxide TFTs even at low annealing temperature. Moreover, the effects on electrical and chemical characteristics of solution-processed oxide TFTs with proposed methods were investigated in detail. These proposed methods to improve the electrical characteristics of low temperature solution-processed oxide TFTs would be suitable for the low cost, stable, and flexible active matrix display backplane.

Keywords: Oxide thin film transistor, Solution-process, Annealing temperature,  $O_2$  plasma, Ultra-Violet radiation, Biased-H<sub>2</sub>O annealing

Student Number: 2008-20944

# Contents

| Abstracti                                                     |

|---------------------------------------------------------------|

| Contentsiv                                                    |

| List of Tablesvii                                             |

| List of Figuresix                                             |

| Chapter 1 Introduction1                                       |

| 1.1 Recent flat panel display technology2                     |

| 1.2 Device parameter extraction                               |

| 1.3 Dissertation organization14                               |

| Chapter 2 Review of solution-processed oxide TFTs16           |

| 2.1 Overview of oxide TFTs17                                  |

| 2.2 Advantages of solution-process                            |

| 2.3 Solution-processed oxide TFTs                             |

| Chapter 3 Optimization of the fabrication process of          |

| solution-processed oxide TFTs                                 |

| 3.1 Overview                                                  |

| 3.2 Structure of solution-processed oxide TFTs                |

| 3.3 Stirring time on solution-processed oxide TFTs            |

| 3.4 Active layer thickness on solution-processed oxide TFTs   |

| 3.5 Effects of passivation on solution-processed oxide TFTs60 |

| 3.6 Electrical characteristics of solution-processed oxide TFTs63       |

|-------------------------------------------------------------------------|

| 3.6.1 Transfer characteristics63                                        |

| 3.6.2 Reliability characteristics                                       |

| Chapter 4 Effects of Annealing Temperature on Solution-                 |

| processed oxide TFTs75                                                  |

| 4.1 Motivation                                                          |

| 4.2 Fabrication of solution-processed ZTO TFTs with various             |

| annealing temperature                                                   |

| 4.3 Electrical characteristics with the increase in annealing           |

| temperature                                                             |

| 4.4 Dechlorination on threshold voltage with the increase in            |

| annealing temperature                                                   |

| 4.5 Dechlorination and crystallization on saturation mobility with      |

| the increase in annealing temperature                                   |

| 4.6 Reliability characteristics with the increase in annealing          |

| temperature                                                             |

| 4.7 Chemical formation equations with the increase in annealing         |

| temperature                                                             |

| 4.8 Conclusion                                                          |

|                                                                         |

| Chapter 5 Improvement of low temperature solution-                      |

| processed oxide TFTs100                                                 |

| 5.1 Improvement of low temperature solution-processed oxide             |

| TFTs employing $O_2$ plasma treatment 101                               |

| 5.1.1 Motivation 101                                                    |

| 5.1.2 Fabrication of solution-processed ZTO TFTs employing $O_2$ plasma |

| treatment 104                                                              |

|----------------------------------------------------------------------------|

| 5.1.3 Electrical characteristics with $O_2$ plasma treatment               |

| 5.1.4 Preferential dissociation of Cl on threshold voltage by $O_2$ plasma |

| treatment 111                                                              |

| 5.1.5 Increase of electron concentration on saturation mobility by $O_2$   |

| plasma treatment 116                                                       |

| 5.1.6 Reliability characteristics with $O_2$ plasma treatment 119          |

| 5.1.7 Conclusion 122                                                       |

| 5.2 Improvement of low temperature solution-processed oxide                |

| TFTs employing Ultra-Violet radiation treatment                            |

| 5.2.1 Motivation 123                                                       |

| 5.2.2 Fabrication of solution-processed ZTO TFTs employing UV              |

| radiation treatment                                                        |

| 5.2.3 Electrical characteristics with UV radiation treatment               |

| 5.2.4 Effects of UV radiation treatment on oxide active layer              |

| semiconductors                                                             |

| 5.2.5 Generation of hydroxide(-OH) bonding by UV radiation treatment       |

| on oxide active layer semiconductors                                       |

| 5.2.6 Conclusion                                                           |

| 5.3 Improvement of low temperature solution-processed oxide                |

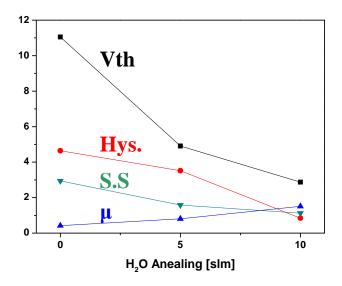

| TFTs employing biaed-H <sub>2</sub> O annealing                            |

| 5.3.1 Motivation                                                           |

| 5.3.2 Effects of various annealing condition                               |

| 5.3.3 Effects of $H_2O$ wet annealing according to the annealing           |

| temperature                                                                |

| 5.3.4 Proposed biased- $H_2O$ annealing to improve low temperature         |

| solution-processed oxide TFTs154                                           |

| 5.3.5 Conclusion 161                                                       |

| Chapter 6 Summary162                                                       |

| Bibliography171                                                            |

|                                                                            |

| 초 록191                                                                     |

## **List of Tables**

| Table 2-1. Comparison of TFTs with various active layers    22                                     |

|----------------------------------------------------------------------------------------------------|

| Table 2-2. Comparison of various solution-processed semiconductor TFTs       32                    |

| Table 2-3. The electrical characteristics of solution-processed ZTO TFTs with                      |

| various annealing temperature34                                                                    |

| Table 3-1. The property of solute as zinc chloride (ZnCl <sub>2</sub> ) and Tin (II) chloride      |

| (SnCl <sub>2</sub> ) powders and solvent as Acetonitrile (CH <sub>3</sub> CN) for the synthesis of |

| solution of ZTO                                                                                    |

| Table 3-2. Thickness of spin-coated ZTO active layer before and after RTA 500 °C                   |

| annealing according to the variation of rpm and time of spin-coating 58                            |

| Table 3-3. Materials including the thickness and processes for each layer of                       |

| solution-processed ZTO TFTs on Si-wafer substrate65                                                |

| Table 4-1. Electrical characteristics of solution-processed ZTO TFTs with the                      |

| annealing temperature of 300 - 500 °C with W / L = 100 / 10 $\mu m$ and $V_{\text{DS}}$ =          |

| 10 V                                                                                               |

| Table 5-1. Electrical characteristics of solution-processed ZTO TFTs with an                       |

| annealing temperature of 350 °C by employing $O_2$ plasma treatment of                             |

| 100 W and 300 W with W / L = 100 / 10 $\mu m$ and $V_{\text{DS}}$ = 10 V 110                       |

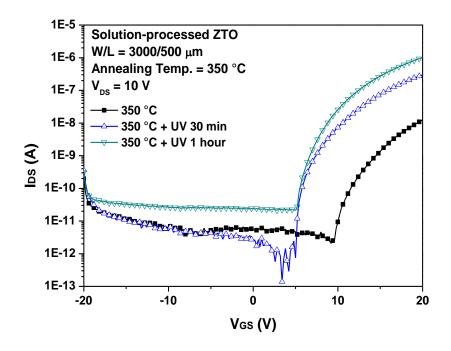

| Table 5-2. Electrical characteristics of solution-processed ZTO TFTs with an                       |

| annealing temperature of 350 $^{\circ}$ C employing UV radiation treatment for 30                  |

| min and 1 hour with W / L = 3000 / 500 $\mu m$ and $V_{\text{DS}}$ = 10 V                          |

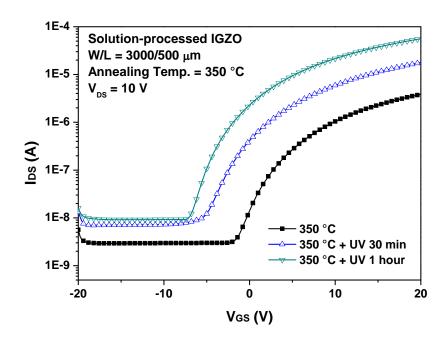

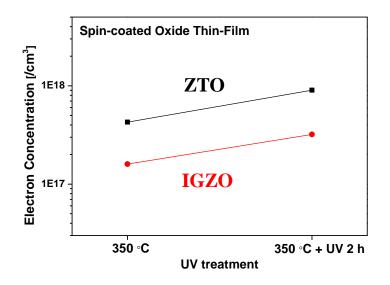

Table 5-3. Electrical characteristics of solution-processed IGZO TFTs with an annealing temperature of 350 °C employing UV radiation treatment for 30

min and 1 hour with W / L = 3000 / 500  $\mu$ m and V<sub>DS</sub> = 10 V ...... 132

- Table 6-1. Summary of improved electrical characteristics of solution-processedZTO TFTs with various annealing condition170

# List of Figures

| Figure 1-1. Desired development of display and active matrix TFT backplane                             |

|--------------------------------------------------------------------------------------------------------|

| technology9                                                                                            |

| Figure 1-2. Evolution of display technology10                                                          |

| Figure 1-3. Desired development of active matrix TFT backplanes to achieve high                        |

| performance of AMLCD and/or AMOLED11                                                                   |

| Figure 2-1. Schematic orbital structure of the conduction-band minimum in                              |

| crystalline and amorphous phase in (a) covalent bond as Si and (b) ionic                               |

| bond as oxide semiconductor                                                                            |

| Figure 2-2. Progress of oxide TFT technology (Ref. Displaybank)                                        |

| Figure 2-3. The advantages of oxide semiconductors compared with a-Si and                              |

| poly-Si                                                                                                |

| Figure 2-4. Transparent and flexible displays                                                          |

| Figure 2-5. The deposition types of solution-process as (a) spin-coating, (b) dip-                     |

| coating, and (c) ink-jet printing28                                                                    |

| Figure 2-6. The comparison of solution-processible semiconductor materials 29                          |

|                                                                                                        |

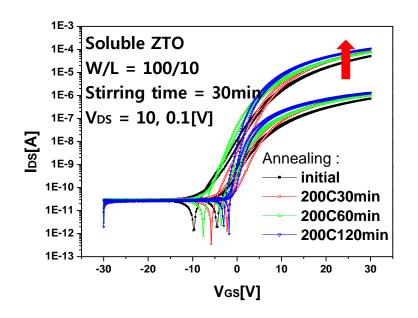

| Figure 2-7. Transfer characteristics of solution-processed ZTO TFTs with various                       |

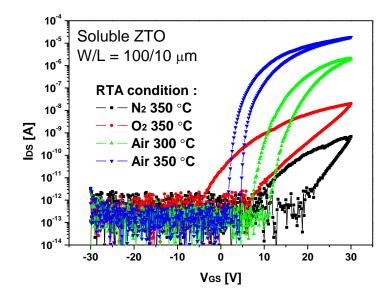

| Figure 2-7. Transfer characteristics of solution-processed ZTO TFTs with various annealing temperature |

|                                                                                                        |

| annealing temperature                                                                                  |

| annealing temperature                                                                                  |

| annealing temperature                                                                                  |

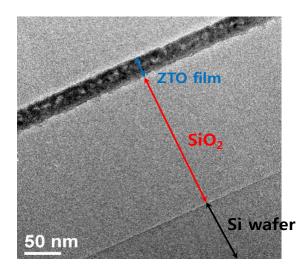

| Figure 3-3. Cross-sectional view of ZTO active layer, $SiO_2$ gate insulator, and Si       |

|--------------------------------------------------------------------------------------------|

| wafer substrate                                                                            |

| Figure 3-4. Plane view of the patterned solution-processed ZTO TFTs with ZTO               |

| active layer and IZO source/drain electrodes45                                             |

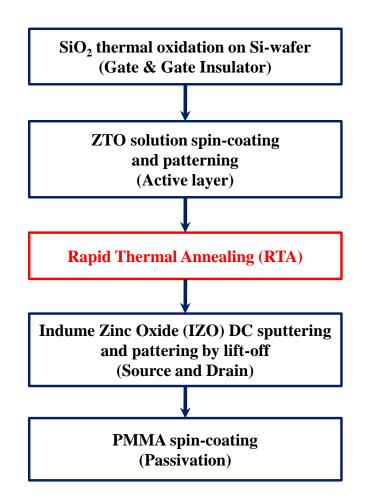

| Figure 3-5. Sequence of the fabrication process of solution-processed ZTO TFTs             |

| on Si-wafer substrate                                                                      |

| Figure 3-6. Transfer characteristics of solution-processed ZTO TFTs according to           |

| various stirring time of ZTO solution with an annealing temperature of                     |

| 500 °C with W / L = 100 / 10 $\mu m$ and $V_{DS}$ = 10 V                                   |

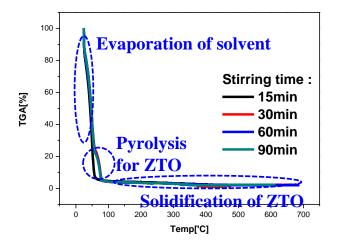

| Figure 3-7. Thermogavimetry analysis (TGA) and differential thermal analysis               |

| (DTA) results of ZTO solution with the increase in temperature according                   |

| to various stirring time of ZTO solution52                                                 |

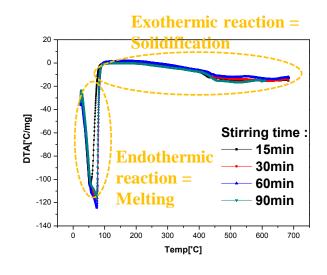

| Figure 3-8. Transmittance of ZTO active layer on bare glass with the increase in           |

| temperature according to various stirring time of ZTO solution53                           |

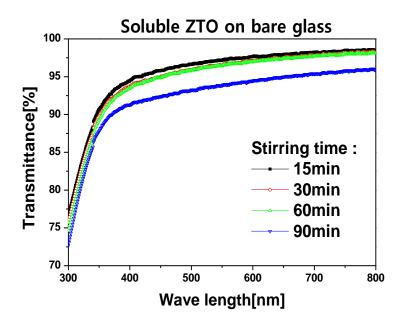

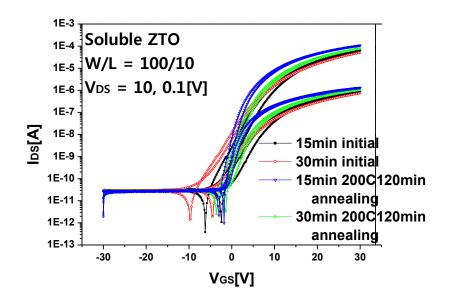

| Figure 3-9. Transfer characteristics of solution-processed ZTO TFTs with stirring          |

| time of 15 and 30 min, and their post-annealed results at 200 $^{\circ}\mathrm{C}$ for 120 |

| min                                                                                        |

| Figure 3-10. Transfer characteristics of solution-processed ZTO TFTs with                  |

| stirring time of 30 min according to various post-annealing time at 200 $^\circ\mathrm{C}$ |

|                                                                                            |

| Figure 3-11. Transfer characteristics of solution-processed ZTO TFTs according             |

| to multi-coating with an annealing temperature of 500 °C with W / L =                      |

| 100 / 10 $\mu m$ and $V_{DS}$ = 10 V                                                       |

| Figure 3-12. Stability for time of transfer characteristics of solution-processed          |

ZTO TFTs (a) without passivation and (b) with PMMA passivation with an

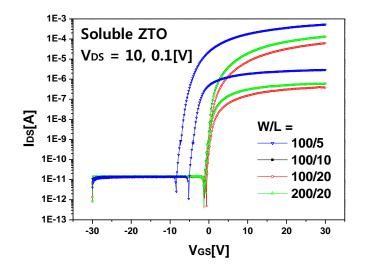

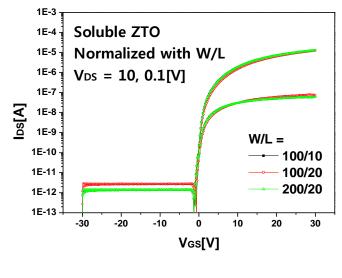

- Figure 3-13. Transfer characteristics of solution-processed ZTO TFTs with an annealing temperature of 500 °C with  $V_{DS}$  = 10 V (a) according to various channel width (W) and length (L) and (b) normalized curves with W/L.66

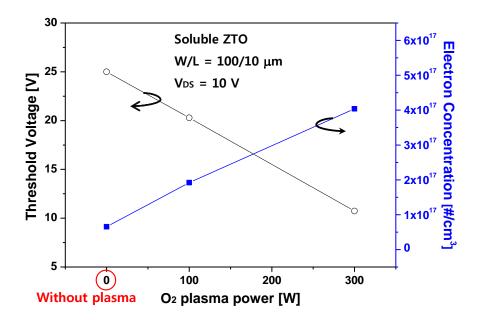

| Figure 4-3. Threshold voltage and electron concentration of solution-processed |

|--------------------------------------------------------------------------------|

| ZTO TFTs with the annealing temperature of 200 - 500 $^\circ$ C85              |

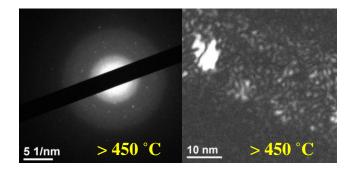

- Figure 4-8. (a) Diffraction patterns below 450 °C and (b) diffraction pattern and dark field images above 450 °C of ZTO active layer obtained by TEM ........92

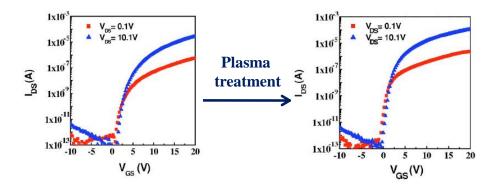

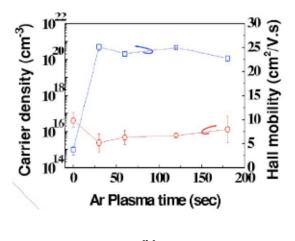

| Figure 5-1. Plasma treatment effects on (a) the transfer characteristics and (b)          |

|-------------------------------------------------------------------------------------------|

| carrier density and hall mobility of sputtered oxide TFTs in previous work                |

|                                                                                           |

|                                                                                           |

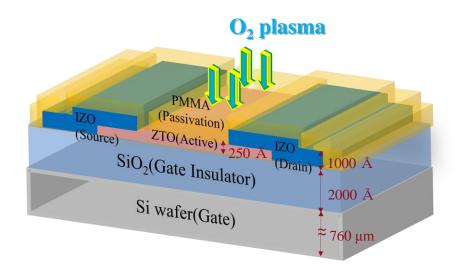

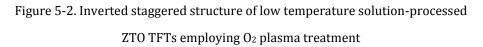

| Figure 5-2. Inverted staggered structure of low temperature solution-processed            |

| ZTO TFTs employing $O_2$ plasma treatment105                                              |

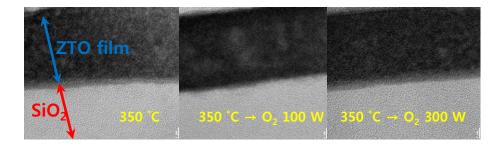

| Figure 5-3. Cross-sectional view of ZTO active film, $SiO_2$ gate insulator, and Si       |

| wafer substrate                                                                           |

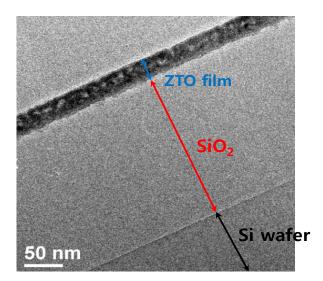

| Figure 5-4. Sequence of the fabrication process of low temperature solution-              |

| processed ZTO TFTs employing $O_2$ plasma treatment 107                                   |

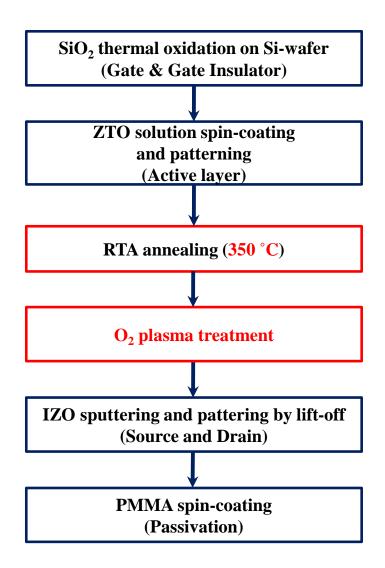

| Figure 5-5. Transfer characteristics of solution-processed ZTO TFTs with an               |

| annealing temperature of 350 °C by employing $O_2$ plasma treatment of                    |

| 100 W and 300 W with W / L = 100 / 10 $\mu m$ and V_DS = 10 V 109                         |

| Figure 5-6. Threshold voltage and electron concentration of solution-processed            |

| ZTO TFTs with an annealing temperature of 350 °C according to $O_2$ plasma                |

| power                                                                                     |

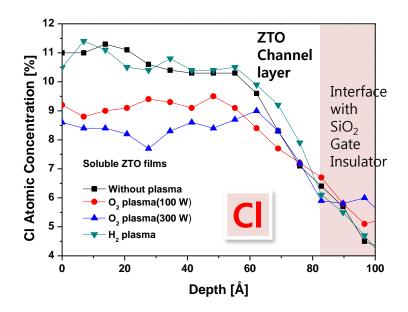

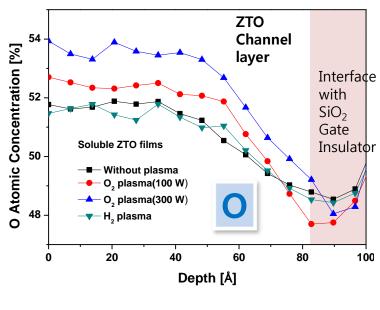

| Figure 5-7. Atomic concentration of ZTO films in AES annealed at 350 $^{\circ}\mathrm{C}$ |

| according to $O_2$ plasma power for (a) Cl atoms and (b) O atoms114                       |

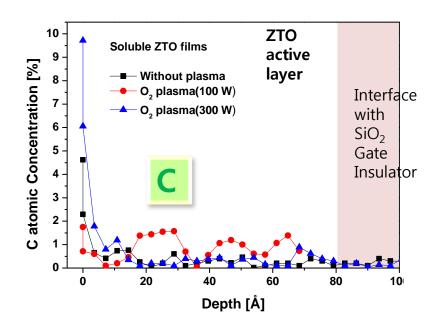

| Figure 5-8. Atomic concentration of ZTO films in AES annealed at 350 °C                   |

| according to $O_2$ plasma power for C atom 115                                            |

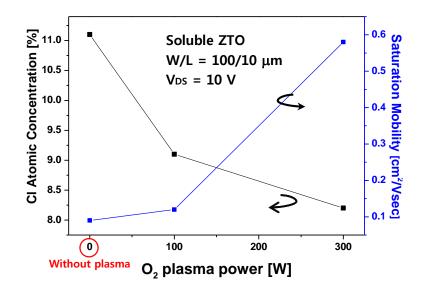

| Figure 5-9. Cl atomic concentration and saturation mobility of solution-                  |

| processed ZTO TFTs with an annealing temperature of 350 °C according                      |

| to $O_2$ plasma power                                                                     |

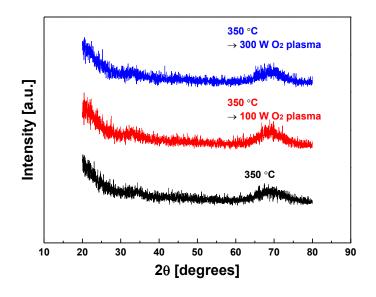

| Figure 5-10. ZTO active layer with amorphous phase regardless of $O_2$ plasma             |

|                                                                                           |

| power with (a) XRD results and (b) TEM images                                             |

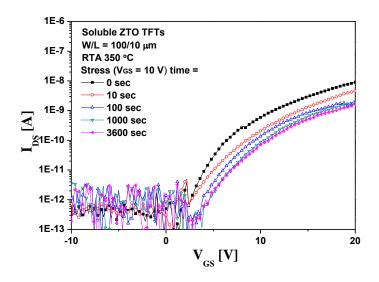

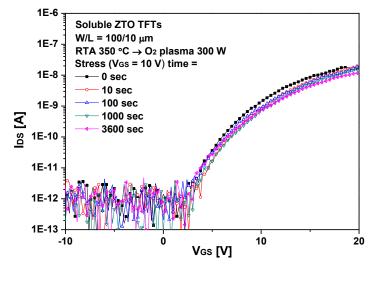

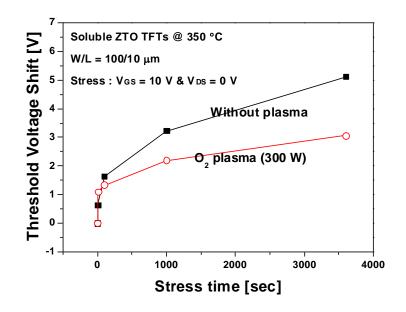

| Figure 5-11. Reliability characteristics of solution-processed ZTO TFTs with the   |

|------------------------------------------------------------------------------------|

| positive gate bias-stress of 10 V for 3600 sec as transfer curve (a) without       |

| $O_2$ plasma treatment, (b) employing $O_2$ plasma treatment of 300 W 120 $$       |

| Figure 5-12. Threshold voltage shift without $O_2$ plasma treatment and with $O_2$ |

| plasma treatment of 300 W 121                                                      |

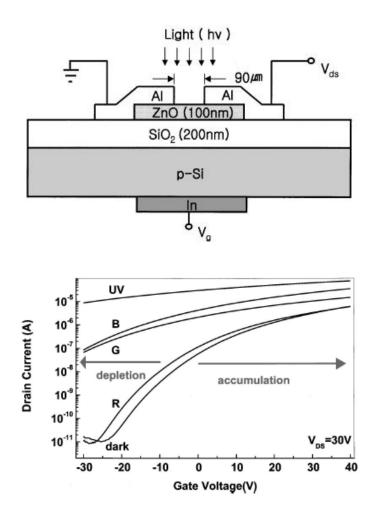

| Figure 5-13. UV exposure measurement on sputtered oxide TFTs in previous           |

| work                                                                               |

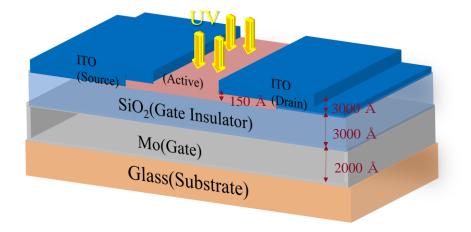

| Figure 5-14. Inverted staggered structure of low temperature solution-processed    |

| oxide TFTs employing UV radiation treatment128                                     |

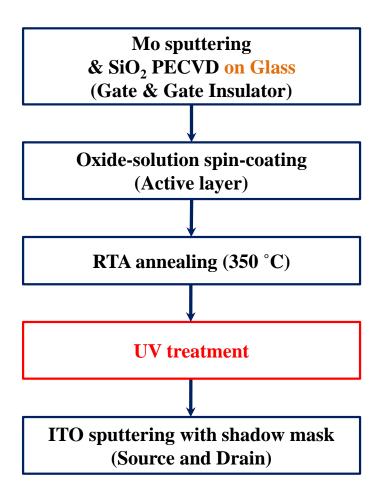

| Figure 5-15. Sequence of the fabrication process of low temperature solution-      |

| processed oxide TFTs employing UV radiation treatment                              |

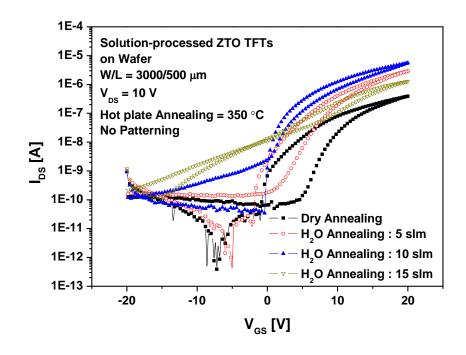

| Figure 5-16. Transfer characteristics of solution-processed ZTO TFTs with an       |

| annealing temperature of 350 °C employing UV radiation treatment for 30 $$         |

| min and 1 hour with W / L = 3000 / 500 $\mu m$ and $V_{\text{DS}}$ = 10 V          |

| Figure 5-17. Transfer characteristics of solution-processed IGZO TFTs with an      |

| annealing temperature of 350 °C employing UV radiation treatment for 30 $$         |

| min and 1 hour with W / L = 3000 / 500 $\mu m$ and $V_{\text{DS}}$ = 10 V 132      |

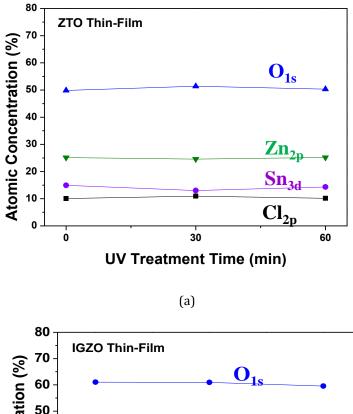

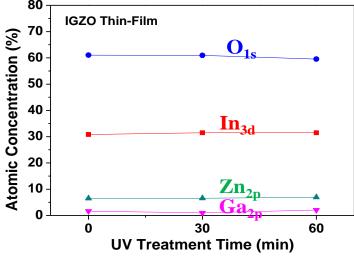

| Figure 5-18. Atomic concentration of solution-processed (a) ZTO and (b) IGZO       |

| active layers with UV radiation treatment by XPS 134                               |

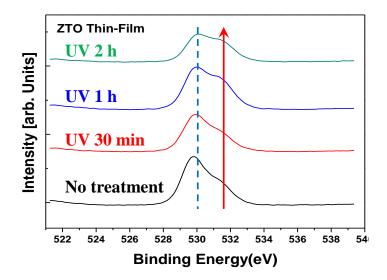

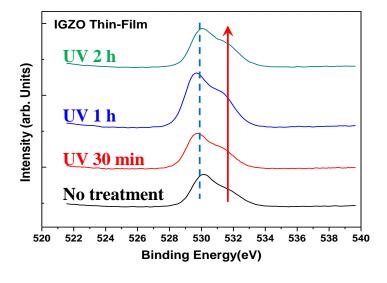

| Figure 5-19. XPS spectra of 0 1s core level of solution-processed 135              |

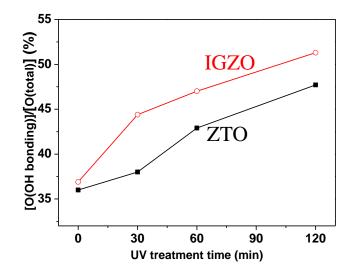

| Figure 5-20. [O(hydroxide)] / [O(total)] of (a) ZTO and (b) IGZO active layers     |

| with UV radiation treatment136                                                     |

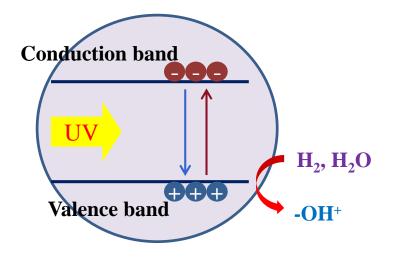

| Figure 5-21. Schematic diagram of generation of hydroxide (-OH) bonding by UV      |

| radiation treatment on oxide active layer semiconductors                           |

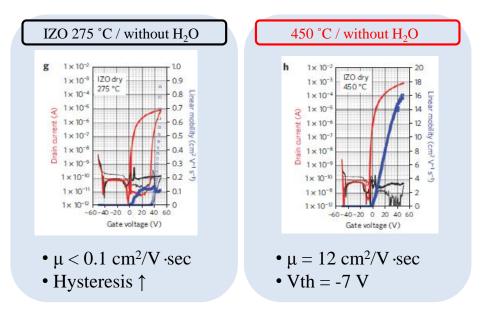

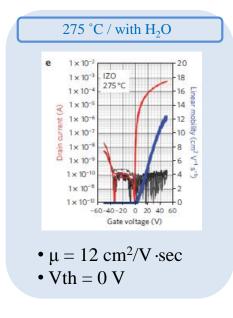

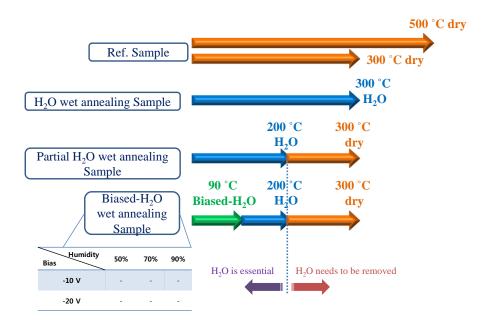

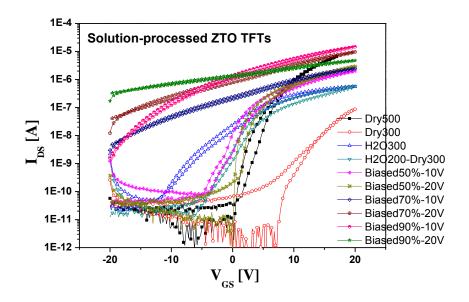

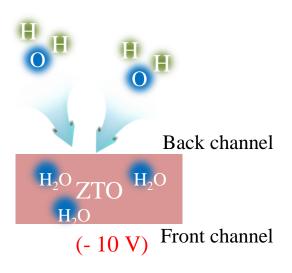

Figure 5-24. Transfer characteristics of solution-processed ZTO TFTs with various annealing condition with W / L = 100 / 10  $\mu$ m and V<sub>DS</sub> = 10 V.. 147

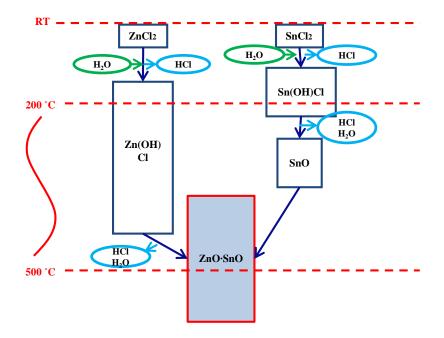

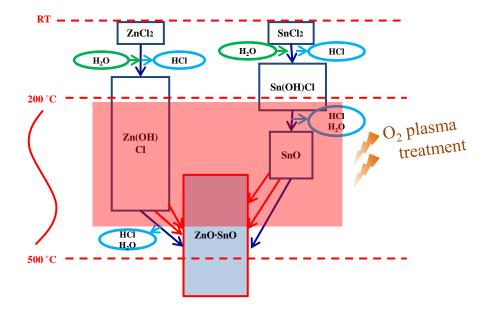

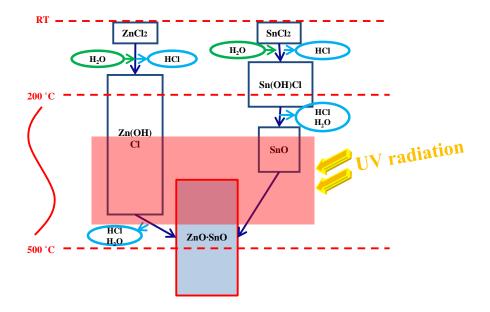

- Figure 6-2. Chemical diagram of metal-oxide formation from precursors with the increase in annealing temperature employing O<sub>2</sub> plasma treatment ..... 166

| Figure | 6-3. Chemical  | diagram    | of metal- | oxide form | nation fro | om precur | sors v | vith | the |

|--------|----------------|------------|-----------|------------|------------|-----------|--------|------|-----|

|        | increase in an | nealing te | emperatu  | re employ  | ing UV ra  | diation   |        | 1    | .67 |

Figure 6-4. Chemical diagram of metal-oxide formation from precursors with the increase in annealing temperature employing biased-H<sub>2</sub>O annealing .... 168

| Figure | 6-5.  | Diagram | of | improvement | of | low | temperature | solution-processed | ł |

|--------|-------|---------|----|-------------|----|-----|-------------|--------------------|---|

|        | oxide | e TFTs  |    |             |    |     |             |                    | ) |

### **Chapter 1 Introduction**

Recently, high performance, large size, low cost, transparent and flexible active matrix displays have attracted considerable attention in the emerging electronic device industry. Solution-processed oxide thin film transistors (TFTs) are promising candidates for next generation high performance, large size, low cost, transparent and flexible display backplane due to high mobility, good uniformity, high throughput and visible light transparency. The only issue of solution-processed oxide TFTs is the fabrication temperature, so that the efforts to achieve high device characteristics of solution-processed zinc-tin-oxide (ZTO) TFTs even at low annealing temperature on active layer are desired.

### 1.1 Recent flat panel display technology

Display technology has been desired to achieve high resolution, no motion blur, large size, cost reduction, transparency and flexibility. As a result, to keep pace with the development of display technology, the TFT backplane technology for active matrix display has been also developed as device minimizing, high mobility, good uniformity, non-vacuum process, large band-gap materials and low temperature process as demonstrated in Figure 1-1.

In development of display technology, flat panel displays (FPDs) have been remarkably encompassed a growing number of electronic visual display technologies with replacing the cathode ray tubes (CRTs) in display industries in the last decade as shown in Figure 1-2 [1]. FPDs are far lighter, thinner, usually less than 10 centimeters (3.9 in) thick, and more power efficient than traditional cathode ray tubes (CRTs) which was a dominant display for decades. They have many advantages such as the light and thin display, high-resolution images, and low-power consumption with low voltage driving so that they have been prevailed in many display applications such as monitor, television, and specifically modern portable devices as laptops, mobile phones, digital cameras, and camcorders.

FPDs could be divided by various types of materials and method to display into liquid crystal display (LCD), organic light emitting diode (OLED), plasma display panel (PDP), and field emission display (FED) [2-6].

Among various FPDs, LCDs have been used in most display technologies because they are thin, light-weight, bright and cost-effective due to the low-temperature process on glass substrates. LCDs are common in a wide range of applications including computer monitors, televisions, instrument panels, aircraft cockpit displays, signage, watches, calculators, and cellular phones. [7]. LCDs have been emerged by large size TVs and monitors over 40 inch so that they enlarge their portion over PDPs and projection TVs in home display applications [8]. Moreover, its low electrical power consumption enables it to be used in batterypowered electronic equipment so that they could be employed for diverse portable applications.

Although LCD display is the most widely commercialized FPD, it is relatively slow response time (~several msec), and narrow viewing angle. OLED technology could be another candidate for the alternative to LCD with regard to TFT backplane. In 1987, *C. W. Tang* and *S. A. VanSlyke* reported luminescence from an organic material [9-11]. Small molecules were deposited to form a layered structure in a vacuum and the layered structure is sandwiched between an anode and cathode. A high electric field at low voltage could be achieved by the thin (< 1  $\mu$ m) organic material. Therefore, a light from thin film organic materials could be produced at low voltage. OLED displays exhibit superb electro-optical properties such as a fast response (~ several µsec) to the image addressing and a wide viewing angle due to self-emissive characteristics. New organic materials and new configurations of devices to improve efficiency and stability of OLED displays have been investigated by many research groups [12-15]. Thus, OLED displays have the potential for new technology compared with the LCDs.

The development of both active matrix LCDs (AMLCDs) and active matrix OLED (AMOLED) for high resolution and full-color display has been fulfilled by the development of TFT backplanes [16]. The active matrix display employing the TFT as a pixel switch has enhanced the capability of high quality image processing, so that the importance of LCDs in commercial fields increases. The electro-optical performance of AMOLED is very sensitive to the characteristics of

TFT. A small variation of the OLED current in the each pixel may cause a critical problem because the OLED luminance is emitted by the current driving. Each TFT pixel in AMOLED panel requires a constant current source with a desired image data during the whole emission time. Therefore, TFT with high electrical capability as well as reliability is key issue for achieving high performance active matrix display.

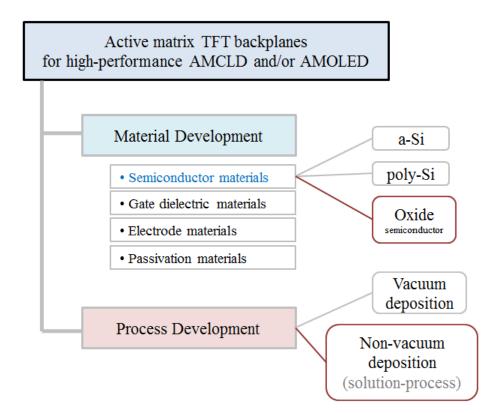

In terms of the active matrix backplane TFTs to achieve high performance of AMLCD and/or AMOLED, the TFTs need to have been developed as the aspect of material as well as fabrication process as demonstrated in Figure 1-3.

In material development of TFTs for the active matrix backplanes, TFTs have been investigated with the issues of semiconductor, gate dielectric, electrode, and passivation materials. Especially, semiconductor materials have been mostly investigated to achieve high performance TFTs of active matrix display.

Hydrogenated amorphous silicon thin film transistors (a-Si TFTs) have been widely used for AMLCDs due to their productivity on a large area glass substrates by low temperature process below 300 °C [17]. The a-Si TFT can represent the gray scale by switching the voltage data and charging the capacitors of each pixel element. However, the low field effect mobility (~ 0.5 cm<sup>2</sup>/V·sec) is the critical limitation for achievement of the high resolution display in AMLCD, results in the poor current driving characteristics of a-Si TFT [18]. Moreover, a-Si TFT should meet adequate requirements for current-driving device in AMOLED, which luminance emitting is closely related with electrical capability of TFT.

The a-Si technology is considered to be applied for large area AMOLED displays due to its low fabrication cost and excellent uniformity as widely used in AMLCDs. However, a long-term device degradation would be the fatal problem for adequate requirements of AMOLED, so that the degradation of the a-Si:H TFT should be compensated by the pixel circuit and the new driving scheme should be investigated to suppress the degradation of a-Si TFTs itself. This would require a rather complicated compensation circuit compared with the poly-Si TFT based pixel design. However, to fabricate the compensation circuit in every pixel is limited by the dimension of a-Si:H TFT components and other signal lines of the circuit.

Polycrystalline silicon (poly-Si) film as an active layer could be employed to solve the problem of low carrier mobility of a-Si TFTs [19, 20]. Poly-Si TFTs have attracted considerable attentions due to its high electron mobility ( $30 \sim 500$  cm<sup>2</sup>/V·sec) and current driving capability [21, 22]. Generally, Poly-Si film is fabricated by recrystallization of the a-Si:H film deposited at low temperature below 400 °C. The superior electrical characteristics of poly-Si TFT allows a fast switching required for high-resolution image with reduced device size compared with a-Si TFT. In addition, poly-Si TFTs enable the ability to implement the complementary metal-oxide-semiconductor (CMOS) process and to integrate the peripheral driver circuits and pixel switching devices simultaneously on a glass substrate for so-called 'System-on-Glass (SOG)' recently [23, 24].

Excimer laser annealing (ELA) technologies have been extensively investigated to fabricated high mobility poly-Si thin film on a large area glass substrate for a reliable current driving in AMOLED. The low temperature (< 400 °C) crystallization of a-Si film on a glass can be obtained by ELA without any thermal damage to the glass [25].

Although the low temperature poly-Si (LTPS) technology could achieve high electrical performances, the uniformity should be improved caused by grainboundaries induced by the fluctuation of ELA energy. In poly-Si film, the grain boundaries are inherently incorporated by a lot of disconnected or mismatched silicon bonds which make a high density of trap states [26]. The random distribution of grain boundaries would cause the non-uniformity of the field effect mobility and the threshold voltage of the poly-Si TFT. The anomalous large off-state leakage current is also attributed to the enhanced electron-hole pair generation in the grain boundary near the drain junction [27]. Additionally, the hot-carriers induced by the high drain field accelerate the kink current, resulting in the deterioration of reliability [28]. Therefore, the I<sub>OLED</sub> compensation pixel circuits, which can compensate the non-uniform characteristics of poly-Si TFTs, are required for the uniform luminance in the display panel [29, 30]. Furthermore, the LTPS technology requires high fabrication cost of poly-Si TFTs due to the additional process steps than a-Si TFT, reducing the process yield [31].

Therefore, the advanced technology are desired to achieve the high performance active matrix display, instead of conventional TFT devices, which poor reliability and low electrical capability of a-Si TFT and severe non-uniformity and complicated fabrication process of LTPS TFT.

nc-Si TFTs, which has small grains of crystalline silicon within the amorphous phase, may be promising devices to fabricate various flat displays, due to a superior performance and stability compared with a-Si and organic TFTs because of the uniformity of crystalline grains formed during the deposition and a rather simple process and good uniformity compared with a poly-Si TFT [32]. Although it currently cannot attain the mobility that poly-Si can, it has the advantage for both AMLCD and AMOLED applications over poly-Si that it is easier to fabricate, as it can be deposited using conventional low temperature a-Si deposition techniques, such as plasma enhanced chemical vapor deposition (PECVD), as opposed to laser annealing or high temperature CVD processes, in the case of poly-Si. Another candidate for advanced TFT would be amorphous oxide (a-oxide) semiconductor TFT for next generation display of AMLCD and/or AMOLED. a-oxide TFTs have attracted considerable attention with a high mobility of > 10 cm<sup>2</sup>/V·sec even in the amorphous phase for an good alternative to a-Si TFTs [33]. The high mobility in the a-oxide material is attributed to the electron transport by the conduction band, whose features are completely different from those of the covalent semiconductors [34]. In addition, oxide semiconductor materials have an amorphous phase, which shows uniform electrical properties even with a large-size display [35-37]. Therefore, high resolution, such as ultra-high definition (UD :  $3840 \times 2160$ ), a high frame rate (> 240 Hz), and large size display (more than 70 inches) could be achieved by the high electrical performance of a-oxide TFTs [38-40].

Transparency with the visible light of oxide semiconductors could be another advantage of the oxide TFTs over the silicon-based TFTs. Zinc oxide based semiconductor, such as indium-gallium-zinc-oxide, exhibits large optical band gap (> 2.8 eV) compared to silicon-based semiconductor [41, 42]. Due to large band gap characteristics, the oxide semiconductor exhibits low leakage current.

In fabrication process development of semiconductor materials of TFTs for the active matrix backplanes, the deposition method of semiconductor materials could be divided into vacuum process and non-vacuum process. Non-vacuum solution-processes such as spin-coating, dip-coating, and ink-jet printing could achieve low-cost fabrication because vacuum-deposition processes, such as rf magnetron sputtering and pulsed laser deposition, require a high manufacturing cost. Solution-processes are also suitable for large-area, high-throughput, and direct patterning [43, 44].

Therefore, the solution-processed oxide TFTs are employed in this study to

achieve low-cost fabrication as well as high mobility and high throughput for active matrix display.

For additional cost reduction and application extension to a flexible display, the solution-processed oxide TFTs need to be fabricated on inexpensive and flexible substrates such as glass and plastic. These substrates are easily damaged at high annealing temperatures, so low-temperature processes are essential for solution-processed oxide TFTs fabrication with flexible substrates. However, a high annealing temperature on an active layer exceeding 500 °C is required to obtain high device performance such as low threshold voltage and high mobility in solution-processed oxide TFTs from previous reports [45-49]. To improve the device characteristics of solution-processed oxide TFTs even at low annealing temperature on an active layer, a study of the effects of annealing temperature on the electrical characteristics of solution-processed oxide TFTs and the efforts to achieve high device characteristics of solution-processed oxide TFTs even at low annealing temperature on active layer are desired. There were some efforts to investigate the effects of annealing temperature on solution-processed oxide TFTs, but the electrical and chemical mechanisms of annealing temperature on solution-processed oxide TFTs have been scarcely studied [50, 51].

The purpose of this thesis is to fabricate oxide TFTs employing solution-process for an oxide semiconductor active layer with various annealing temperatures to investigate the effects of annealing temperature on the electrical characteristics of solution-processed oxide TFTs such as threshold voltage and mobility, and to improve the electrical characteristics of low temperature solution-processed oxide TFTs for active matrix display.

### **High Resolution**

|                  | Display    |             |                             | TFT<br>Backplane  |

|------------------|------------|-------------|-----------------------------|-------------------|

| High Resolution  | FHD        |             | UD $(4K \times 2K)$         | Device minimizing |

| Motion Blur Free | 120 Hz     |             | 240 Hz                      | High mobility     |

| Large Size       | 40 "       |             | 82 "                        | Good uniformity   |

| Cost Reduction   | High-thro  | oughput p   | Non-vacuum                  |                   |

| Transparency     | Visible li | ight transp | Large band-gap<br>materials |                   |

| Flexibility      | Flex       | ible subst  | Low temperature<br>process  |                   |

|                  |            |             |                             |                   |

Figure 1-1. Desired development of display and active matrix TFT backplane technology

Figure 1-2. Evolution of display technology

Figure 1-3. Desired development of active matrix TFT backplanes to achieve high performance of AMLCD and/or AMOLED

#### **1.2 Device parameter extraction**

In this section, the methods for preparing solution of oxide semiconductor precursors and device parameters extraction in this thesis are introduced.

The solution of oxide semiconductor is prepared with measuring by its weight. The solute, that is precursor, is measured by weight to confirm its molar ratio with a quantity of 3 ml as following equation.

$$FW [g/mol] \times 3 ml \times M [mol/L] = W [g]$$

(FW : Formula weight [g/mol], M : Molarity(Molar ratio) [mol/L], W : weight [g]) The solvent is also measured by weight to be matched with a quantity of 3 ml as following equation.

> d [g/ml] × 3 ml = W [g] (d : density [g/ml], W : weight [g])

Basically, the measurement was carried out in the dark state and at room temperature. The device parameter originated by from the conventional MOS field effect transistor (MOSFET) is adopted in TFT analysis.

I-V relationship of a TFT can be derived by Ohm' law,

$$I_{DS} = \frac{W}{L} \mu_{lin} C_{ox} \left( V_{GS} - V_{TH} - \frac{V_{DS}}{2} \right) V_{DS}$$

(1)

where  $\mu_{lin}$ ,  $\mu_{sat}$ ,  $C_{ox}$  and  $V_{TH}$  are the field effect mobility for the linear region and the saturation region, gate insulator capacitor per unit area and the threshold voltage, respectively. W and L are channel width and length of the TFT, respectively.

(1) is the standard linear regime equation. When  $V_D=V_G-V_{TH}$ , the channel becomes pinch-off, which means no longer potential difference between the gate

and the drain terminal, leading the drain region depletion of free carrier. By substituting ' $V_D=V_G-V_{TH}$ ' into (1) yields,

$$I_{DS} = \frac{W}{2L} \mu_{sat} C_{ox} (V_{GS} - V_{TH})^2$$

(2)

The saturation mobility  $(\mu_{sat})$  in the saturation region can be extracted from (2) with unit of cm<sup>2</sup>/V·sec.

The  $V_{TH}$  was defined by the gate voltage, which induced a drain current of 'L/W  $\times$  10 nA  $\times$  V\_{DS}'.

The subthreshold swing (S slope) describes how effectively the device switches between on and off state, with unit of V/dec or mV/dec.

$$S = \frac{dV_{GS}}{dlogI_{DS}}$$

(4)

#### 1.3 Dissertation organization

The purpose of this thesis is to fabricate oxide TFTs employing solution-process for an oxide semiconductor active layer with various annealing temperatures to investigate the effects of annealing temperature on the electrical characteristics of solution-processed oxide TFTs such as threshold voltage, saturation mobility, and reliability, and to improve the electrical characteristics of low temperature solution-processed oxide TFTs for inexpensive and flexible active matrix display.

Chapter 2 gives a brief introduction to the solution-processed oxide TFTs. The advantages of oxide TFTs and solution-process are reviewed, and accordingly the merits and the only issue, that is the fabrication temperature, of solution-processed oxide TFTs are also reviewed.

Chapter 3 indicates the optimization of the fabrication process of oxide TFTs employing solution-process for an oxide semiconductor active layer with various condition of the stirring time of oxide semiconductor solution, the active layer thickness, the effects of passivation to investigate the effects of fabrication process condition on the electrical characteristics of solution-processed oxide TFTs such as threshold voltage, saturation mobility, and reliability.

Chapter 4 focuses on the investigation of the effects of annealing temperature on the electrical characteristics of solution-processed oxide TFTs such as threshold voltage, saturation mobility, and reliability. The effects of annealing temperature on the bonding structure of ZTO active layer in solution-processed ZTO TFTs were investigated and the chemical formation equation of the ZTO active layer with regard to the annealing temperature was established.

Chapter 5 concentrates on the methods to improve the electrical characteristics of low temperature solution-processed oxide TFTs according to the investigation

of effects of annealing temperature. In regard of the chemical formation of ZTO active layer according to the annealing temperature, O<sub>2</sub> plasma treatment, UV radiation treatment, and the biased-H<sub>2</sub>O annealing were proposed to achieve high device characteristics of solution-processed oxide TFTs even at low annealing temperature. Moreover, the effects on electrical and chemical characteristics of solution-processed oxide TFTs with proposed methods were investigated in detail.

Finally, the investigation of the effects of annealing temperature on solutionprocessed oxide TFTs and the proposed methods to improve the electrical characteristics of low temperature solution-processed oxide TFTs for the low cost, stable, and flexible active matrix display backplane were summarized in chapter 6.

# Chapter 2 Review of solution-processed oxide TFTs

Solution-processed oxide TFTs are promising candidates for advanced high performance, large size, low cost, and flexible active matrix display backplane due to high mobility, visible light transparency, and good uniformity. Furthermore, solution-process could be a method for achieving low cost fabrication contrary to vacuum processes and suitable for large area and high throughput. The only issue of solution-processed oxide TFTs is the fabrication temperature, so that the efforts to improve electrical characteristics of solutionprocessed ZTO TFTs such as threshold voltage, saturation mobility, and reliability even at low annealing temperature on active layer are desired.

# 2.1 Overview of oxide TFTs

Oxide semiconductors with polycrystalline phase, such as ZnO, In<sub>2</sub>O<sub>3</sub>, SnO<sub>2</sub>, and ITO, have been introduced for the application of transparent conductive oxides (TCOs) for solar cells and conductive transparent electrodes because of high conductivity and wide-bandgap. Furthermore, oxide semiconductor TFTs (oxide TFTs) have been intensively studied as promising alternatives to conventional a-Si TFTs by a requirement for high-resolution, large size and high frame rate operation, from early 2000s.

Oxide TFT employing ZnO using radio frequency (RF) magnetron sputtering or pulsed laser deposition (PLD) was reported by various groups since early 2000s. Hoffman et al. fabricated ZnO TFT employing ion beam sputtering, and mobility of 2.5 cm<sup>2</sup>/V-s with a drain current on-to-off ratio >10<sup>5</sup> were obtained.[52] Elvira et al. developed fully transparent ZnO TFTs, with a room temperature process, exhibiting high mobility near 20 cm<sup>2</sup>/V·sec [53].

Higher electrical conductivity  $(10^{-2} \Omega^{-1} \text{ cm to } 10^3 \Omega^{-1} \text{ cm}^1)$  of oxide semiconductor is attributed to the existence of native defects, such as oxygen vacancies, cation interstitials, and substitutional/interstitial hydrogen, that act as shallow donors [54]. Because of these donors, the TCOs have a high carrier concentration of  $10^{18}$ cm<sup>-3</sup> to  $10^{21}$  cm<sup>-3</sup>.

However, polycrystalline oxide TFTs have its own drawback, which is the formation of grain boundary, causing non-uniform TFT performance at different locations. Another problem is the difficulty of fabrication, which originates from the low chemical durability of pure ZnO against acidic etchants. They also require relatively high gate voltages to turn-on as enhancement mode.

Oxide TFTs with amorphous phase were firstly reported in 2004, Nomura et al. with a new class of a-oxide semiconductors based on IGZO deposited at room temperature, and demonstrated high performance transistors ( $\mu \approx 8.3 \text{ cm}^2/\text{V} \cdot \text{sec}$ ) [55, 56]. Despite the amorphous state, the origin of the high mobility was attributed to the electronic orbital structure of the material.

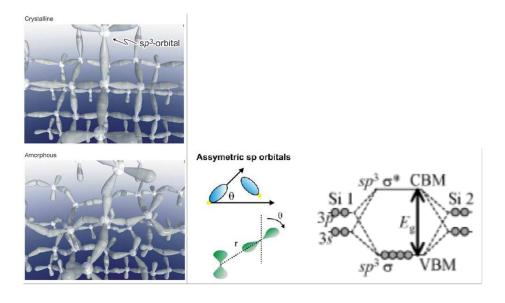

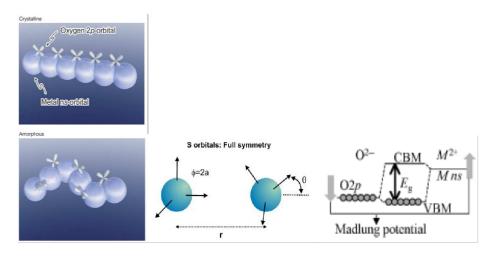

Figure 2-1 shows schematic orbital structure of the conduction-band minimum for the carrier transport paths in crystalline and amorphous phase in covalent bond as Si and also ionic bond as oxide semiconductor. Covalent semiconductors have carrier transport paths composed of strongly directive sp<sup>3</sup> orbitals, so structural randomness greatly degrades the magnitude of bond overlap and carrier mobility [57]. However, a-oxide semiconductors are composed of posttransition-metal cations which exhibit isotropic properties, where the overlap of the In 5s orbitals is mainly formed and the contribution of oxygen 2p orbitals is small. Direct overlap between neighboring metal s orbitals is rather large, and is not significantly affected even in a distorted amorphous structure [58]. Therefore, a-oxide semiconductor is insensitive to structural deformation, so that could exhibits high mobility even in an amorphous phase.

While Si material undergoes a significant reduction in mobility from 1000 (single crystal) to 1 (amorphous) cm<sup>2</sup>/V·sec, a-oxide semiconductor is not degraded in mobility even in amorphous phase so that a promising material for switching or driving elements in future high resolution and large size display.

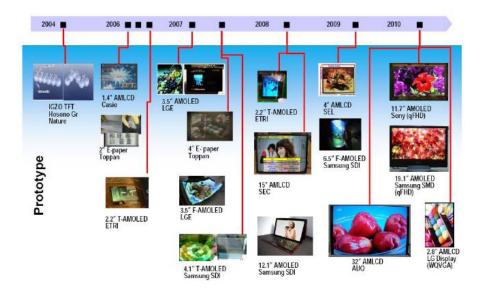

The development of oxide TFTs technology has been emerged drastically in the last decade by a number of advantages of oxide semiconductors as demonstrated in Figure 2-2 of the prototypes AMLCD or AMOLED employing oxide TFTs.

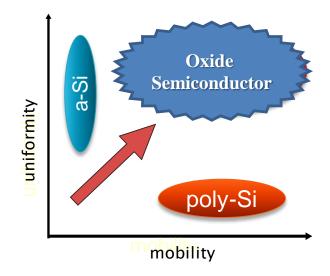

The progress of oxide TFTs could be achieved by their many advantages such as high mobility, good uniformity, low cost process, transparency, and flexibility, compared with conventional ones. Comparison of TFTs with various active layers was described in Table 2-1. Although currently widely used a-Si TFTs show a good uniformity, their low mobility is not suitable for high resolution and high speed driving devices. Poly-Si TFTs have high mobility and good reliability, but their bad uniformity would be the issue for large size display panel. nc-Si TFTs show no particular advantages compared with a-Si and poly-Si TFTs, so that they seems not to be good candidates for state-of-the-art display needs. However, oxide TFTs show better mobility and reliability than that of a-Si TFTs and better uniformity than that of poly-Si TFTs as demonstrated in Figure 2-3, so that oxide TFTs have attracted considerable attention for high resolution, high speed driving, and large size display. Moreover, a number of research groups such as Hosono have investigated the effective improvement of electrical characteristics of ZnO-based oxide semiconductors by adding indium, gallium, or tin, to be applied to advanced display technologies [59-61]. Especially, indiumgallium-zinc-oxide (IGZO), indium-zinc-oxide (IZO), and zinc-tin-oxide (ZTO) have been reported in the last decade and recently hafnium-indium-zinc-oxide (HIZO) and aluminum-zinc-oxide (AZO) have been investigated vigorously [62-67].

Furthermore, the oxide TFTs have merits of high transparency due to their widbandgap as well as flexibility due to their stability against bending stress. Therefore, oxide TFTs may be the promising candidate for the active matrix backplanes to the next generation transparent and flexible display as shown in Figure 2-4 [68, 69].

(a)

(b)

Figure 2-1. Schematic orbital structure of the conduction-band minimum in crystalline and amorphous phase in (a) covalent bond as Si and (b) ionic bond as oxide semiconductor

Figure 2-2. Progress of oxide TFT technology (Ref. Displaybank)

|                         | a-Si TFTs | Poly-Si TFTs | nc-Si TFTs | Oxide TFTs |

|-------------------------|-----------|--------------|------------|------------|

| Mobility<br>(cm²/V·sec) | 0.4~0.8   | 30~400       | 0.5~250    | 5~100      |

| Uniformity              | Good      | Medium       | Good       | Good       |

| Reliablility            | Bad       | Good         | Good       | Good       |

| Cost                    | Low       | High         | Medium     | Low        |

| Yield                   | High      | Low          | Medium     | High       |

Table 2-1. Comparison of TFTs with various active layers

Figure 2-3. The advantages of oxide semiconductors compared with a-Si and

poly-Si

Figure 2-4. Transparent and flexible displays

# 2.2 Advantages of solution-process

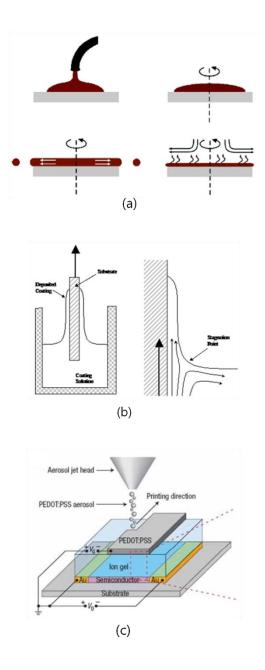

The deposition method of semiconductor materials for the active matrix backplane TFTs could be divided into vacuum process and non-vacuum process. Deposition methods based on non-vacuum solution-processes such as spincoating, dip-coating, and ink-jet printing require no pumping down time and are not limited by the size of the vacuum chamber. Therefore, they are compatible with low production cost for manufacturing devices and large-area thin film fabrication, while vacuum processes such as rf magnetron sputtering and pulsed laser deposition require a high manufacturing cost and have poor uniformity. Solution-processes are also suitable for high-throughput and direct patterning, so that they have attracted considerable attention for low cost, large size, and high-throughput display fabrication method [70, 71].

Solution-processes are the simple deposition method with the solution from the solute of precursors or nano-particle and the solvent on the substrate, afterward apply the annealing process to the solution for solid thin film.

There are two representative synthesis method of solution, employing the solute of precursors or nano-particle. The solution could be synthesized from precursors, a compound that participates in the chemical reaction that produces another compound, or nano-particle, semiconductor materials as themselves which approach to the nano-scale [72-75].

Lower fabrication temperature could be achieved employing nano-particle than precursors, but the thin film deposited by nano-particle has grain boundary, because nano-particle thin film is the bonding combination of semiconductor paricles, which causes mobility degradation [76]. On the other hand, the thin film deposited by precursors has fine amorphous film quality in spite of higher fabrication temperature.

Various deposition types of solution-processes are described in Figure 2-5. Spincoating is a procedure used to deposit uniform thin films to flat substrates and usually a small amount of coating material is applied on the center of the substrate, then rotate at high speed in order to spread the coating material uniformly by centrifugal force [77]. Dip-coating is a method of depositing thin films by immersing the substrate in the solution of the coating material at a constant speed. Ink-jet printing is a deposition type by propelling droplets of ink onto substrate in order to make the pattern formation [78-80].

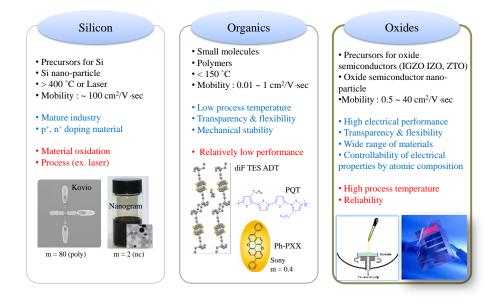

Si, organic semiconductors, and oxide semiconductors have been vigorously investigated in solution-processes among various semiconductor materials. Figure 2-6 shows the comparison of solution-processible semiconductor materials [81-85]. The solution types of all semiconductors, Si, organic, and oxide, could be precursors or nano-particle. Solution-processed Si has merits of the mature fabrication industry and the feasibility material for both p-type and ntype, but also has demerits of oxidation of Si and process complexity in case of laser application. Solution-processed organic semiconductors could be fabricated with low process temperature and have suitability for transparency, flexibility, and mechanical stability, but their relatively low electrical performance is issue. Solution-processed oxide semiconductors have advantages of high electrical performance, transparency, flexibility, wide range of materials, controllability of electrical properties by atomic composition, but also have disadvantages of high process temperature and improving reliability [86].

Among these various semiconductor materials, solution-processed oxide semiconductors have superior electrical and chemical characteristics, so that may be the promising candidate for the next generation active matrix backplane TFTs to high-resolution, high frame rate operation, large size, transparent, and flexible display [87].

Figure 2-5. The deposition types of solution-process as (a) spin-coating, (b) dipcoating, and (c) ink-jet printing

Figure 2-6. The comparison of solution-processible semiconductor materials

## 2.3 Solution-processed oxide TFTs

Solution-processed oxide TFTs with zinc-tin-oxide (ZTO) and indium-galliumzinc-oxide (IGZO) have attracted considerable attention for the driving elements of active matrix display, instead of Si-based TFTs and organic TFTs, because of high mobility, visible light transparency, flexibility, wide range of materials, and controllability of electrical properties by atomic composition [88-91]. Table 2-2 describes the comparison of various solution-processed semiconductor TFTs. Solution-processed oxide TFTs show superior performance for AMLCD and AMOLED display backplanes, compared with solution-processed Si and organic TFTs which have a number of issues. Furthermore, solution-processed oxide TFTs are compatible with large area due to good uniformity and high throughput, so that could be a method for achieving low cost fabrication contrary to vacuum processes.

Among various ZnO-based oxide semiconductors, ZTO TFTs employing tin (Sn) material maybe promising candidates for achieving low cost processes because Sn is a quite low cost material compared with widely used indium (In) [92-95]. Therefore, ZTO TFTs employing Sn maybe promising candidates for achieving low cost processes.

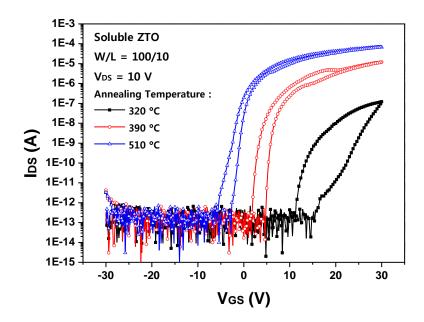

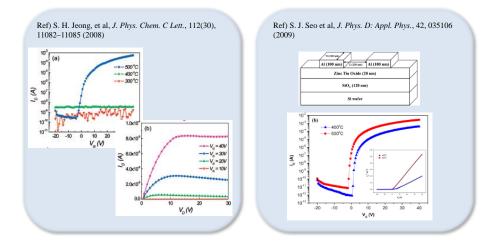

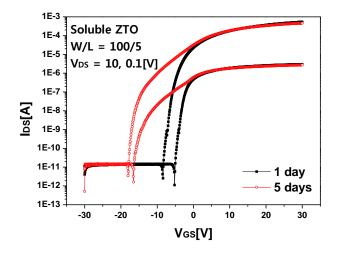

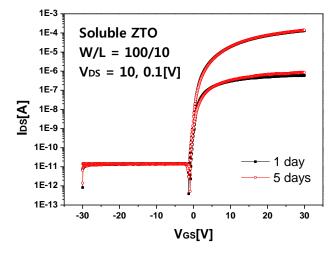

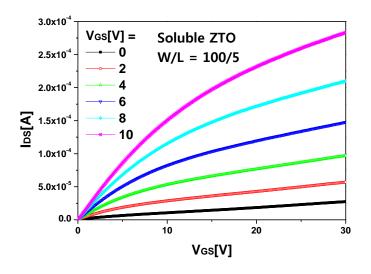

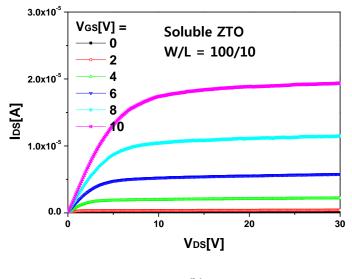

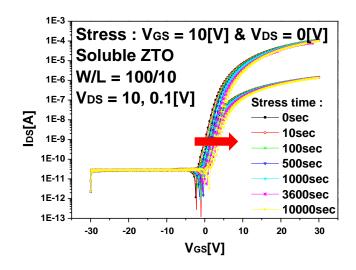

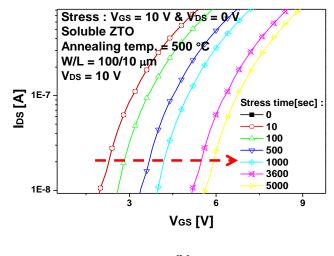

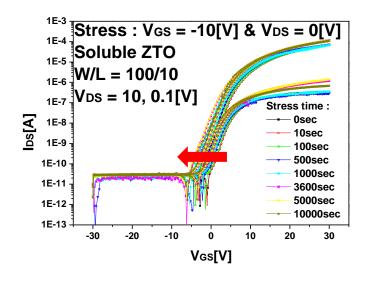

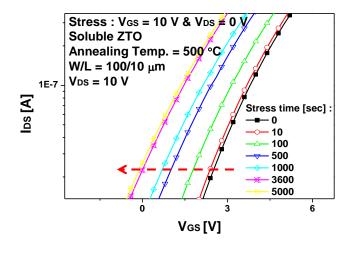

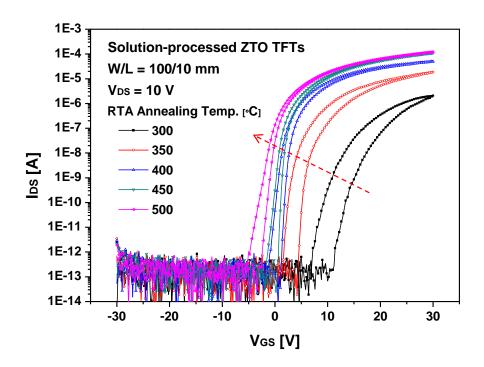

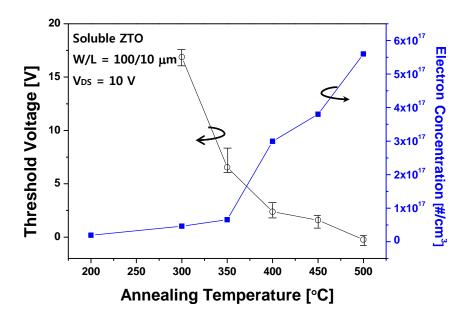

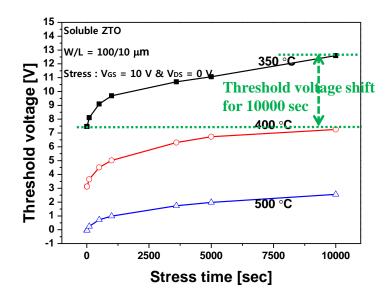

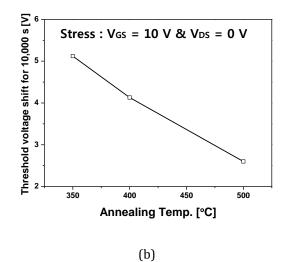

Solution-processed ZTO TFTs need to be fabricated on inexpensive and flexible substrates such as glass and plastic for additional cost reduction and application extension to a flexible display. For solution-processed ZTO TFTs fabrication with these flexible substrates, low temperature processes are necessary because these substrates are easily damaged at high annealing temperatures. At low annealing temperature, however, solution-processed ZTO TFTs have poor performance such as low on-current, high threshold voltage and low mobility, so a rather high annealing temperature exceeding 500 °C is required in solutionprocessed ZTO TFTs as investigated in the transfer characteristics of Figure 2-7 and the electrical characteristics of Table 2-3 of solution-processed ZTO TFTs with various annealing temperature [96, 97]. To improve the device characteristics of solution-processed oxide TFTs even at low annealing temperature on an active layer, a study of the effects of annealing temperature on the electrical characteristics of solution-processed oxide TFTs and the efforts to achieve high device characteristics of solution-processed oxide TFTs even at low annealing temperature on active layer are desired. There were some efforts to investigate the effects of annealing temperature on solution-processed oxide TFTs as shown in Figure 2-8, but the electrical and chemical mechanisms of annealing temperature on solution-processed oxide TFTs have been scarcely studied [98, 99].

The purpose of this thesis is to fabricate oxide TFTs employing solution-process for an oxide semiconductor active layer with various annealing temperatures to investigate the effects of annealing temperature on the electrical characteristics of solution-processed oxide TFTs such as threshold voltage, saturation mobility, and reliability, and to improve the electrical characteristics of low temperature solution-processed oxide TFTs for active matrix display.

31

| Solution-processed | Poly-Si TFTs                                                                        | Organic TFTs                   | Oxide TFTs                 |

|--------------------|-------------------------------------------------------------------------------------|--------------------------------|----------------------------|

| Туре               | Precursor<br>Nano-particle                                                          | Small Molecule<br>Polymer      | Precursor<br>Nano-particle |

| Process Temp.      | >400 °C<br>or Laser                                                                 | <150 °C                        | 400~600 °C<br>200~300 °C   |

| Mobility           | 108                                                                                 | 0.01 ~ 1                       | 0.5~44                     |

| Reliability        | 0                                                                                   | ×                              | Δ                          |

| Transparency       | ×                                                                                   | 0                              | 0                          |

| Display Mode       | LCD/OLED                                                                            | EPD, Flexible                  | LCD/OLED                   |

| Issue              | Air stability of ink<br>Toxic precursor<br>High temp. or Laser<br>Crystalline phase | Low mobility<br>Bias stability | High temp.                 |

# Table 2-2. Comparison of various solution-processed semiconductor TFTs

Figure 2-7. Transfer characteristics of solution-processed ZTO TFTs with various annealing temperature

| Annealing<br>temperature | Vth<br>(V) | I <sub>on</sub> /I <sub>off</sub><br>[10 <sup>x</sup> ] | µsat<br>(cm²/V·sec) | S.S<br>(V/decade) |

|--------------------------|------------|---------------------------------------------------------|---------------------|-------------------|

| <b>320</b> °C            | 28.43      | 5                                                       | 0.02                | 2.57              |

| <b>390</b> °C            | 6.68       | 7                                                       | 0.36                | 0.63              |

| <b>510</b> °C            | -0.48      | 8                                                       | 2.09                | 0.34              |

Table 2-3. The electrical characteristics of solution-processed ZTO TFTs with various annealing temperature

Figure 2-8. Previous report to investigate the effect of annealing temperature on solution-processed ZTO TFTs

# Chapter 3 Optimization of the fabrication process of solution-processed oxide TFTs

### 3.1 Overview

Solution-processed oxide TFTs with ZTO and IGZO have attracted considerable attention for the driving elements of active matrix display, instead of Si-based TFTs and organic TFTs, because of high mobility, visible light transparency, flexibility, wide range of materials, and controllability of electrical properties by atomic composition. Furthermore, solution-processed oxide TFTs are compatible with large area due to good uniformity and high throughput, so that could be a method for achieving low cost fabrication contrary to vacuum processes.

Among various ZnO-based oxide semiconductors, ZTO TFTs employing Sn material maybe promising candidates for achieving low cost processes because Sn is a quite low cost material compared with widely used In. Therefore, ZTO TFTs employing Sn maybe promising candidates for achieving low cost processes.

To optimize the fabrication process of solution-processed ZTO TFTs for high and stable electrical characteristics, a number of issues should be investigated in regards of the TFT structure, the stirring time of oxide semiconductor solution, the active layer thickness, the effects of passivation, and so on [100-104].

The purpose of this chapter is to optimize the fabrication process of ZTO TFTs employing solution-process for an oxide semiconductor active layer with various condition of the stirring time of oxide semiconductor solution, the active layer thickness, the effects of passivation to investigate the effects of fabrication process condition on the electrical characteristics of solution-processed ZTO TFTs such as threshold voltage, saturation mobility, and reliability.

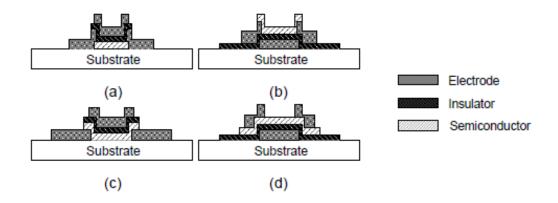

### 3.2 Structure of solution-processed oxide TFTs

There are four major typical classes of TFT devices: (a) staggered top gate, (b) staggered bottom gate (SBG), (c) coplanar top gate, and (d) coplanar bottom gate, as shown in Figure 3-1.

Staggered structure means that source / drain and gate are placed on the opposite sides if the channel layer, whereas they locates on the same side in coplanar structure. The inverted staggered structure is most widely used in the oxide TFTs, since it is the most commonly used among the commercial TFTs in the active matrix display [105]. Thus, for the achievement of conventional a-Si TFT compatible process, the inverted staggered structure is considered most appropriate one.

For the conventional TFTs, the inverted staggered bottom gated structure of a-Si TFT was most widely used in the industry since it maximizes the advantage of sequential deposition of gate insulator, channel layer and doped layer. However, for poly-Si TFT, which require additional ion doping and activation process, top gate coplanar structure has been preferentially selected [106-108].

The inverted staggered structure is most widely used in the oxide TFTs, since it is the most commonly used among the commercial TFTs in the active matrix display [109, 110]. Thus, for the achievement of conventional a-Si TFT compatible process, the inverted staggered structure is considered most appropriate one.

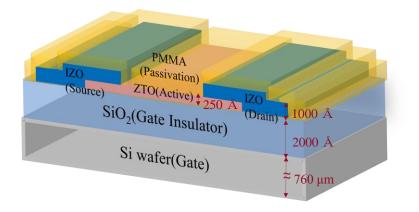

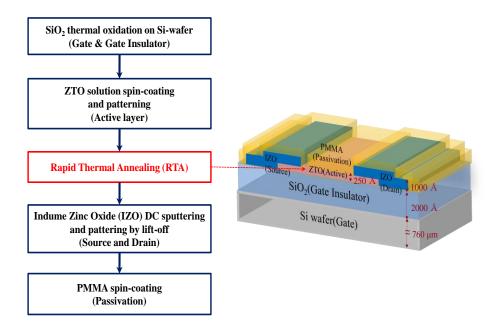

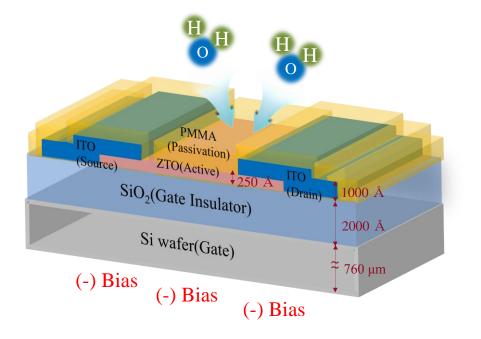

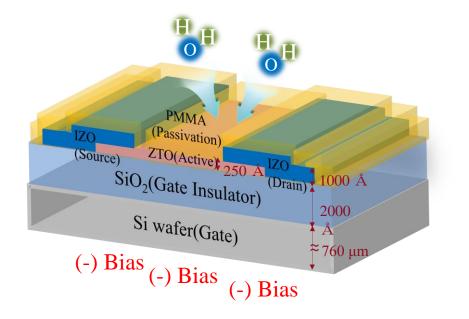

In this thesis, solution-processed ZTO TFTs were fabricated with inverted staggered structure on the silicon wafer substrates as shown in Figure 3-2. Heavily boron doped p-type silicon wafer substrate and thermal oxidized silicon dioxide (SiO<sub>2</sub>) were used as the gate and gate insulator, respectively [111].

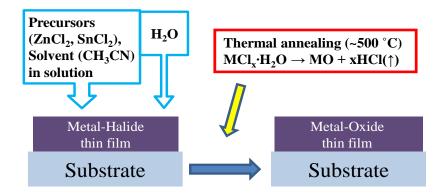

The precursor-based solution of ZTO for active layer was prepared with zinc chloride ( $ZnCl_2$ ) and Tin (II) chloride ( $SnCl_2$ ) powders in Acetonitrile ( $CH_3CN$ ) at equal molar ratios of 0.07 M. The formula weight of  $ZnCl_2$  is 136.3, so that the weight of  $ZnCl_2$  would be 0.029 g with a quantity of 3 ml of solvent by the follwing equation, explained in chapter 1.2 above.

$$FW[g/mol] \times 3 ml \times M [mol/L] = W [g]$$

(FW : Formula weight [g/mol], M : Molarity(Molar ratio) [mol/L], W : weight [g])

The formula weight of  $SnCl_2$  is 189.6, so that the weight of  $SnCl_2$  would be 0.04 g with a quantity of 3 ml of solvent by the same equation

The density of solvent CH<sub>3</sub>CN is 0.782, so that the weight was matched as 2.346 g with a quantity of 3 ml as following equation, explained in chapter 1.2 above. The property of solute as zinc chloride (ZnCl<sub>2</sub>) and Tin (II) chloride (SnCl<sub>2</sub>) powders and solvent as Acetonitrile (CH<sub>3</sub>CN) for the synthesis of solution of ZTO is demonstrated in Table 2-1.

d [g/ml] × 3 ml = W [g] (d : density [g/ml], W : weight [g])

The mixed precursor-based solution of ZTO was stirred at room temperature to promote the dissolving process and deposited by spin-coating with 500 rpm for 6 sec and sequentially 4000 rpm for 30 sec. The deposited ZTO active layer was soft-baked at 200 °C for 10 min with the slow increase and slow decrease in

temperature to solidify the ZTO active layer without pore. To avoid the fringing effect and a large leakage current, the soft-baked ZTO active layer was patterned by the photolithography employing wet-etching process with diluted HF. The photoresist (PR) GXR 601 for photolithography was spin-coated with 500rpm for 6sec and sequentially 3000rpm for 20sec, and soft-baked at 100 °C for 2 min. The exposure was performed employing MA-6 with the wavelength of 365 nm for 9 sec and developed in DPD200 for 40 sec. After hard-baking at 100 °C for 2 min, ZTO active layer was wet-etched in diluted HF as 500 : 1 with deionized water (DI water). The PR was stripped in acetone for 10 sec.

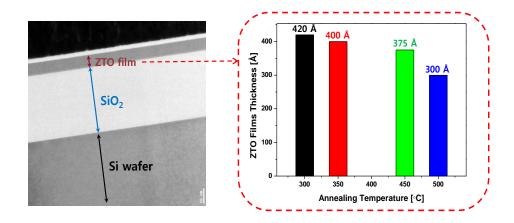

The pattened ZTO active layer were annealed at 500 °C for 10 min by rapid thermal annealing (RTA) process. The cross-sectional view of ZTO active layer,  $SiO_2$  gate insulator, and Si wafer substrate is shown as Figure 3-3 by transmission electron microscopy (TEM).

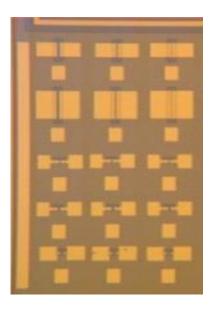

After the patterned ZTO active layer were formed on the SiO<sub>2</sub>, indium zinc oxide (IZO) film was deposited by dc sputtering with the thickness of 1000 Å and then defined by a lift-off process of PMMA (Poly(methyl methacrylate)) / PR double layer to yield source and drain electrodes. The plane view of the patterned solution-processed ZTO TFTs with ZTO active layer and IZO source/drain electrodes is demonstrated in Figure 3-4 by microscope.

Finally a PMMA layer was employed for passivation with the thickness of 2000 Å by spin-coating to protect the active layer from moisture in the air.

The sequence of the fabrication process of solution-processed ZTO TFTs on Siwafer substrate is summarized in Figure 3-5.

Figure 3-1. Typical structure of TFT : (a) top gate co-planar, (b)bottom gate coplanar, (c) top gate staggered, and (d) bottom gate staggered

Figure 3-2. Inverted staggered structure of solution-processed ZTO TFTs

Table 3-1. The property of solute as zinc chloride (ZnCl<sub>2</sub>) and Tin (II) chloride (SnCl<sub>2</sub>) powders and solvent as Acetonitrile (CH<sub>3</sub>CN) for the synthesis of solution of ZTO

| ZTO     | Zn                               | Sn                              |  |

|---------|----------------------------------|---------------------------------|--|

| Solute  | Zinc chloride, ZnCl <sub>2</sub> | Tin chloride, SnCl <sub>2</sub> |  |

| Solute  | (FW=136.3, d=2.907)              | (FW=189.6, d=3.95)              |  |

| Column  | ile, CH₃CN                       |                                 |  |

| Solvent | (d=0.782)                        |                                 |  |

Figure 3-3. Cross-sectional view of ZTO active layer, SiO $_{\rm 2}$  gate insulator, and Si wafer substrate

Figure 3-4. Plane view of the patterned solution-processed ZTO TFTs with ZTO active layer and IZO source/drain electrodes

Figure 3-5. Sequence of the fabrication process of solution-processed ZTO TFTs

on Si-wafer substrate

## 3.3 Stirring time on solution-processed oxide TFTs

To optimize the fabrication process of solution-processed ZTO TFTs for high and stable electrical characteristics, a number of issues should be investigated in regards of the TFT structure, the stirring time of oxide semiconductor solution, the active layer thickness, the effects of passivation, and so on.

In this section, the stirring time of ZTO semiconductor solution was varied to investigate to effect of stirring time on the electrical, optical, and chemical characteristics of solution-processed ZTO TFTs and to optimize the fabrication process of ZTO TFTs employing solution-process for an oxide semiconductor active layer for high and stable electrical characteristics [112].

The precursor-based solution of ZTO for active layer was prepared with zinc chloride (ZnCl<sub>2</sub>) and Tin (II) chloride (SnCl<sub>2</sub>) powders in Acetonitrile (CH<sub>3</sub>CN) at equal molar ratios and stirred at room temperature to promote the dissolving process with various stirring time of 15, 30, 60, and 90 min.

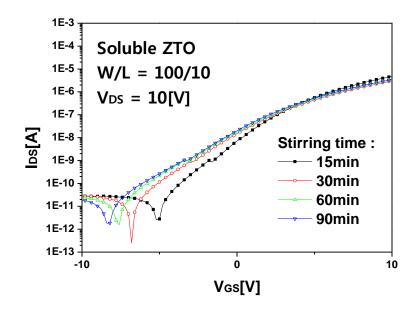

Figure 3-6 shows the transfer characteristics of solution-processed ZTO TFTs according to various stirring time of ZTO solution with an annealing temperature of 500 ° with W / L = 100 / 10  $\mu$ m and V<sub>DS</sub> = 10 V. When the stirring time of ZTO solution was decreased from 90 min to 15 min, the transfer characteristic of solution-processed ZTO TFTs was improved as the threshold voltage was increased to 0 V and the subthreshold swing (S.S) was decreased. The improvement of the transfer characteristics of solution-processed ZTO TFTs according to the decrease in stirring time was caused by the decrease in the halide residues such as Cl which was included in precursors. The decrease in the halide residues such as Cl could be investigated with thermogavimetry analysis (TGA), differential thermal analysis (DTA), and transmittance [113, 114].

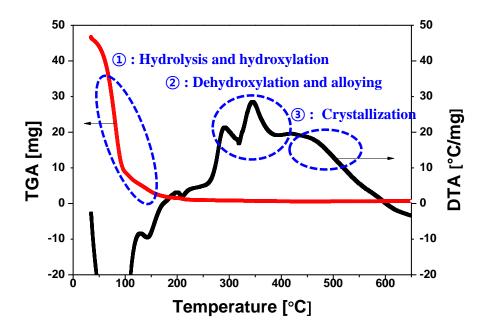

The thermogavimetry analysis (TGA) and differential thermal analysis (DTA) results of ZTO solution with the increase in temperature according to various stirring time of ZTO solution was demonstrated in Figure 3-7. TGA is a method of thermal analysis in which changes in physical and chemical properties of materials, such as weight loss, are measured as a function of increasing temperature (with constant heating rate). Differential thermal analysis (or DTA) is a thermoanalytic technique, in which the material under study and an inert reference are made to undergo identical thermal cycles, while recording any temperature difference between sample and reference [115]. In Figure 3-7 (a) of TGA results, the ZTO solution underwent the evaporation of solvent, the pyrolysis, and the solidification of ZTO active layer with the increase in temperature. The ZTO solution with the stirring time of 15 min was first pyrolyzed at lowest temperature [116]. In Figure 3-7 (b) of DTA results, the ZTO solution underwent endothermic reaction which means the melting of ZTO precursors and exothermic reaction which means the solidification of ZTO solution. The ZTO solution with the stirring time of 15 min was first stablized at lowest temperature. The TGA and DTA results of ZTO solution show that the increase of precipitate such as halide residues according to the increase of stirring time retards the decomposition of ZTO precursors.

The transmittance of spin-coated ZTO active layer on bare glass with the increase in temperature according to various stirring time of ZTO solution was demonstrated in Figure 3-8. When the stirring time of ZTO solution decreased from 90 min to 15 min, the transmittance of ZTO active layer was increased up to 97 % at the wavelength of 500 nm. The improvement of transmittance of ZTO active layer would be caused by the decrease of precipitate such as halide residues when the stirring time decreased [117].

Therefore, the threshold voltage and subthreshold swing of solution-processed

ZTO TFTs were improved with the decrease in stirring time of ZTO solution due to the decrease of precipitate, investigated in the TGA, DTA, and transmittance results.

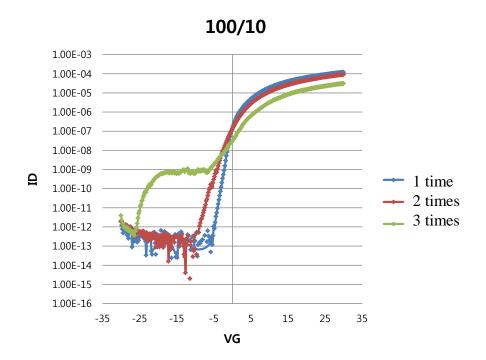

Figure 3-9 demonstrates the transfer characteristics of solution-processed ZTO TFTs with stirring time of 15 and 30 min, and their post-annealed results at 200 °C for 120 min. When compared the transfer characteristic with stirring time of 15 and that of 30 min and/or compared the post-annealed transfer characteristic with stirring time of 15 and that of 30 min, it is observed again that the threshold voltage, subthreshold swing, and on-current of solutionprocessed ZTO TFTs were improved with the decrease in stirring time of ZTO solution due to the decrease of precipitate, and the precipitate would not be removed by the post-annealing. The improvement of post-annealed transfer characteristics would be mainly due to the elimination of residues from PR and PMMA, and/or the moisture in the air, which are absorbed to the ZTO active layer during the fabrication process after the ZTO active layer was annealed, because the temperature of post-annealing is remarkably lower than that of ZTO active layer annealing temperature. However, when compared the transfer characteristic with stirring time of 15 and the post-annealed transfer characteristic with stirring time of 30 min, the precipitate during stirring of ZTO solution could be also eliminated during post-annealing because the latter has better electrical characteristics.

Figure 3-10 demonstrates the transfer characteristics of solution-processed ZTO TFTs with stirring time of 30 min according to various post-annealing time. The transfer characteristics of solution-processed ZTO TFTs were improved with the increase in post-annealing time because of the elimination of residues from PR and PMMA, the moisture in the air, and/or the precipitate during stirring of ZTO solution.

Therefore, the optimized stirring time of ZTO semiconductor solution for the least precipitate during stirring would be 15 min to achieve high and stable electrical characteristics of solution-processed ZTO TFTs, and the precipitate during stirring of ZTO solution could be eliminated by employing post-annealing treatment.

Figure 3-6. Transfer characteristics of solution-processed ZTO TFTs according to various stirring time of ZTO solution with an annealing temperature of 500 °C with W / L = 100 / 10  $\mu$ m and V<sub>DS</sub> = 10 V

(a)

(b)

Figure 3-7. Thermogavimetry analysis (TGA) and differential thermal analysis (DTA) results of ZTO solution with the increase in temperature according to various stirring time of ZTO solution

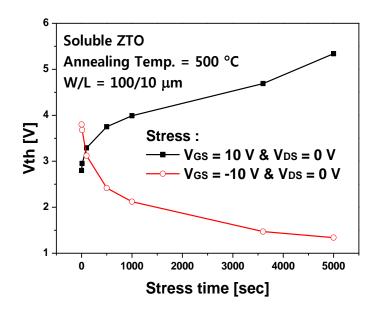

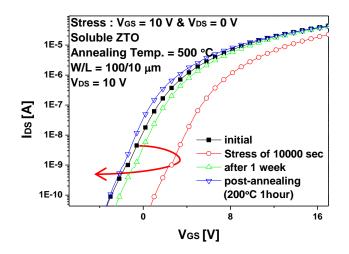

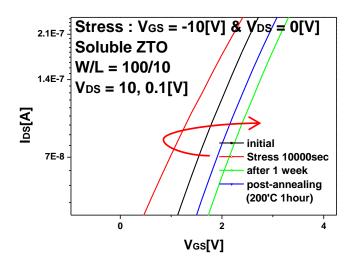

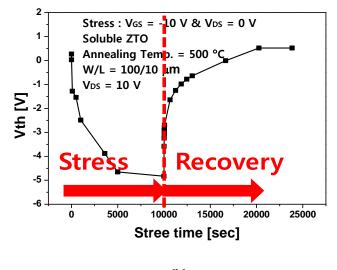

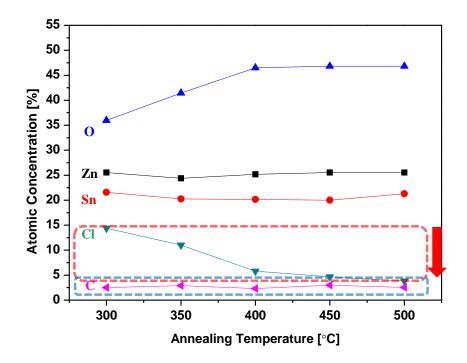

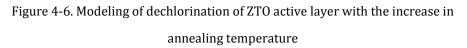

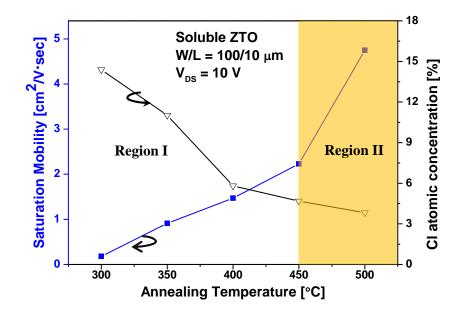

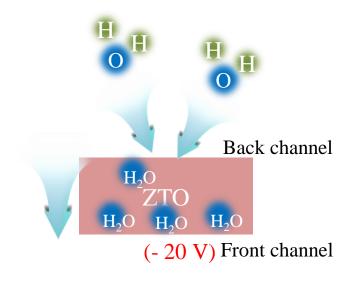

Figure 3-8. Transmittance of ZTO active layer on bare glass with the increase in temperature according to various stirring time of ZTO solution