#### 저작자표시-비영리-변경금지 2.0 대한민국

#### 이용자는 아래의 조건을 따르는 경우에 한하여 자유롭게

• 이 저작물을 복제, 배포, 전송, 전시, 공연 및 방송할 수 있습니다.

#### 다음과 같은 조건을 따라야 합니다:

저작자표시. 귀하는 원저작자를 표시하여야 합니다.

비영리. 귀하는 이 저작물을 영리 목적으로 이용할 수 없습니다.

변경금지. 귀하는 이 저작물을 개작, 변형 또는 가공할 수 없습니다.

- 귀하는, 이 저작물의 재이용이나 배포의 경우, 이 저작물에 적용된 이용허락조건 을 명확하게 나타내어야 합니다.

- 저작권자로부터 별도의 허가를 받으면 이러한 조건들은 적용되지 않습니다.

저작권법에 따른 이용자의 권리는 위의 내용에 의하여 영향을 받지 않습니다.

이것은 이용허락규약(Legal Code)을 이해하기 쉽게 요약한 것입니다.

#### 공학박사 학위논문

# Enhancement of Injection and Transport in Organic Field-Effect Transistors and Light-Emitting Transistors with Multilayers

다층 유기 전계 효과 트랜지스터 및 유기 발광 트랜지스터의 전하 주입 및 거동 능력의 향상

2017 년 8 월

서울대학교 대학원 공과대학 전기·컴퓨터공학부 이 규 정

# Enhancement of injection and transport in organic field-effect transistors and light-emitting transistors with multilayers

지도 교수 이 신 두

이 논문을 공학박사 학위논문으로 제출함 2017 년 8 월

> 서울대학교 대학원 공과대학 전기·컴퓨터공학부 이 규 정

이규정의 공학박사 학위논문을 인준함 2017 년 6 월

| 위 원 | l 장 | 이 창 희 | (인) |

|-----|-----|-------|-----|

| 부위- | 원장  | 이 신 두 | (인) |

| 위   | 원   | 홍 용 택 | (인) |

| 위   | 원   | 최종선   | (인) |

| 위   | 원   | 김 민 회 | (인) |

#### **Abstract**

## Enhancement of injection and transport in organic field-effect transistors and light-emitting transistors with multilayers

Gyujeong Lee

Department of electrical and Computer Engineering

The Graduate School

**Seoul National University**

The organic electronics have drawn great attention for their potential of application in advanced electronic device. The intrinsic advantages of organic materials, such as flexibility, light-weight, and low-cost and large-area processability, give organic electronics superior merit compared to the silicon-based materials. Moreover, the chemical versatility of organic materials opens new fields of light-emission, charge-transport, photovoltaicity, and sensing properties in organic electronics. In this regards, the detailed investigation to physical mechanism of organic electronics enables the successful introduction of organic semiconductors to various opto-electronic devices including organic light-emitting diodes (OLEDs), organic field-effect transistors (OFETs), and organic photovoltics (OPVs). Among the organic electronic devices, the OFETs have been considered as a main candidate for the various fields of flexible electronics, integrated circuits, organic-based

sensors, and radio frequency identification tags.

In recent years, the extensive researches in material level have led to the development of high performance organic materials having field-effect mobility (up to 10 cm²/Vs). For realization of OFETs as a practical application of advanced electronics, however, the enhancement of charge injection and transport in device level is strongly required. In order to fully utilize the capability of improved electric performance of organic material, the multi-layers structures of OFETs have been adopted to improve electrical characteristics. For example, the interlayer between the source/drain electrode and the organic semiconductor (OSC) was placed to improve the injection characteristics, and the ambipolar-type OFETs was introduced to balance the transport of holes and electrons in same device. Moreover, the light-emitting transistors was extensively studied for its light-emitting property together with the switching capability of transistor in single device.

The main purpose of this thesis is to demonstrate the enhancement of charge injection and transport of OFETs and OLETs with multi-layers by the optimization of device structures. At first, an ambipolar-type OFET with two-stacked OSCs in dual gate configuration was proposed. Two stacked OSCs, directly contacted with the source/drain electrodes, form the separated channels for holes and electrons, respectively. These individual channels can be effectively and independently controlled by corresponding gate bias voltage, so the ambipolar-type transport in a single device can be obtained. Next, the introduction of semiconducting organic buffer layer between the source/drain electrodes and the OSC layer is described. The semiconducting organic buffer layer greatly reduces the potential loss at the contact region (interface of source/OSC) so the injection properties of OFETs can be improved. And lastly, the vertical configuration of OLETs (VOLETs) having high on/off ratio is demonstrated by dielectric encapsulation of source electrode. The dielectric encapsulation of source electrode governs the effective charge pathway in

VOLETs by blocking excessive electric fields from the drain voltage. As a result, the

gate voltage can successfully control the accumulation and transport of charges,

which results in the high on/off ratio of VOLETs.

The novel device architectures of OFETs with multi-layers demonstrated in

this thesis would pave the way towards the enhancement of electrical characteristics

in OFETs, the precise control of effective charge flow in OFETs, the ambipolar-type

operation in single device, the integration of light-emitting capability in switching

OFETs, and further application of advanced, flexible and multi-functional organic

electronics.

Keyword: Organic field-effect transistors, Organic light-emitting transistors,

Device configuration, Numerical simulation, Charge injection and transport,

Dielectric encapsulation

**Student Number : 2011-20893**

iii

#### **Table of Contents**

| Abstract                                                               | i         |

|------------------------------------------------------------------------|-----------|

| Table of Contents                                                      | iv        |

| List of Figures                                                        | vi        |

| List of Tables                                                         | xii       |

| Chapter 1. Introduction                                                | 1         |

| 1.1. Overview of organic electronics                                   | 1         |

| 1.2. Organic field-effect transistors                                  | 3         |

| 1.3. Organic light-emitting transistors                                | 5         |

| 1.4. Outline of thesis                                                 | 7         |

| Chapter 2. Theoretical Background                                      | 9         |

| 2.1. Operation principle of organic field-effect transistors           | 9         |

| 2.2. Charge transport in ambipolar-type organic field-effect transisto | rs 16     |

| 2.3. Role of injection barrier in organic field-effect transistors     | 21        |

| 2.4. Organic light-emitting transistors                                | 24        |

| 2.4.1. General description of organic light-emitting transistors       | 24        |

| 2.4.2. Vertical organic light-emitting transistors                     | 28        |

| Chapter 3. Ambipolar-type Charge Transport of Organic Field            | ld-Effect |

| Transistors in Dual-Gate Configuration                                 | 30        |

| 3.1. Introduction                                                      | 30        |

| 3.2. Fabrication of ambipolar-type organic field-effect transistors    | 32        |

| 3.3. Experimental results and discussion                               | 34        |

| 3.3.1. Electrical characteristics in single gate configuration         | 34        |

| 3.3.2. Electrical characteristics in dual-gate configuration           | 36        |

| 3.4. Conclusions                                                       | 40        |

| Chapter 4. Enhancement of Charge Injection in Organic Field            | ld-Effect |

| Transistors by Semiconducting Organic Buffer Layer                     | 41        |

| 4.1. Introduction                                                      | 41        |

| 4.2. Numerical simulations                                             | 45        |

| 4.2.1. Simulation model and device parameters                          | 45        |

|        | 4   | 4.2.2.   | Potential distribution in channel                             | . 47      |

|--------|-----|----------|---------------------------------------------------------------|-----------|

|        | 2   | 4.2.3.   | Effect of semiconducting organic buffer layer on the e        | effective |

|        | 1   | nobility | /                                                             | . 51      |

| 4.3    | 3.  | Expe     | rimental results and discussions                              | . 54      |

|        | 2   | 4.3.1.   | Fabrication of organic field-effect transistors with semicor  | nducting  |

|        | (   | organic  | buffer layer                                                  | . 54      |

|        | 4   | 4.3.2.   | Electrical characteristics of organic field-effect transistor | ors with  |

|        | 5   | semicon  | ducting organic buffer layer                                  | . 55      |

| 4.4    | 4.  | Conc     | lustions                                                      | . 58      |

| Chapt  | ter | 5. Ve    | rtical Organic Light-Emitting Transistors with Di             | electric  |

| Encap  | วรเ | ılated   | source electrode                                              | .59       |

| 5.     | 1.  | Introd   | luction                                                       | . 59      |

| 5.2    | 2.  | Devic    | ce structure and fabrication                                  | . 63      |

| 5.3    | 3.  | Nume     | erical simulations in three-type of vertical organic light-   | emitting  |

| tra    | ans | istors   |                                                               | . 66      |

|        | 4   | 5.3.1.   | Simulation models and device parameters                       | . 66      |

|        | 4   | 5.3.2.   | Current density distributions                                 | . 70      |

|        | 4   | 5.3.3.   | Electrical characteristics                                    | . 75      |

|        | 4   | 5.3.4.   | Opto-electrical characteristics                               | . 78      |

| 5.4    | 4.  | Expe     | rimental results and discussions                              | . 80      |

|        | 4   | 5.4.1.   | Electrical characteristics                                    | . 80      |

|        | 4   | 5.4.2.   | Light emission properties                                     | . 83      |

| 5.3    | 5.  | Conc     | lusions                                                       | . 85      |

|        |     |          |                                                               |           |

| Chapt  | ter | 6. Co    | ncluding Remarks                                              | 86        |

| Biblio | gr  | aphy     |                                                               | 89        |

| Public | cat | tions    |                                                               | 96        |

| Abstr  | ac  | t (Kore  | ean)                                                          | 100       |

#### **List of Figures**

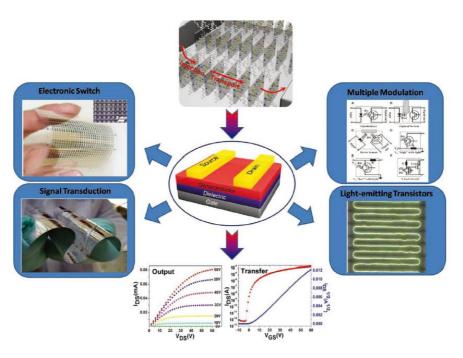

| Figure 1.1 | Illustration of device structure, electrical characteristics, and applications        |

|------------|---------------------------------------------------------------------------------------|

|            | of OFETs (Ref. [1])                                                                   |

| Figure 1.2 | Schematic representation of the device structures and the main                        |

|            | optoelectronic processes occurring in an OLET (Ref. [9]) 6                            |

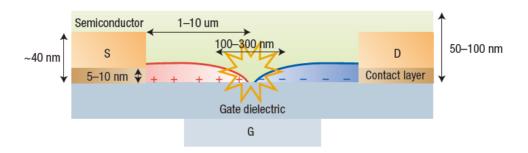

| Figure 2.1 | Structure of an OFET. $L$ represents channel length, $W$ the channel width,           |

|            | $V_{\rm d}$ the drain voltage, and $V_{\rm g}$ the gate voltage (Ref. [18])           |

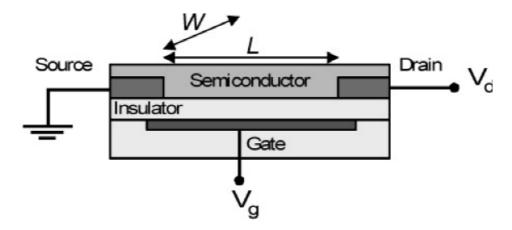

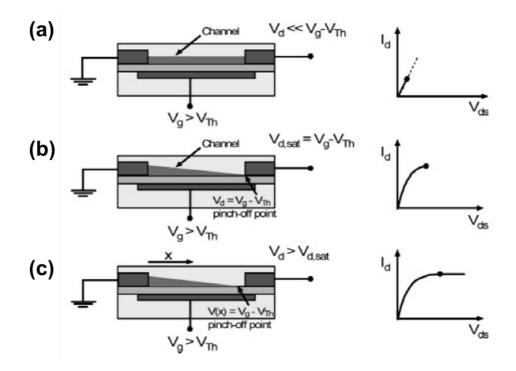

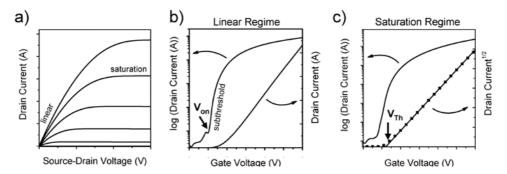

| Figure 2.2 | Illustrations of operating regimes of OFETs: (a) linear regime; (b) start             |

|            | of saturation regime at pinch-off, (c) saturation regime and                          |

|            | corresponding current-voltage characteristics. (Ref. [18])11                          |

| Figure 2.3 | Representative current-voltage characteristics of an n-type OFET. (a)                 |

|            | Output characteristics showing the linear and saturation regimes. (b)                 |

|            | Transfer characteristics in the linear regime and the onset voltage ( $V_{\rm on}$ ). |

|            | (c) Transfer characteristics in the saturation regime and the threshold               |

|            | · · ·                                                                                 |

|            | voltage V <sub>th</sub> (Ref. [18])                                                   |

| Figure 2.4 |                                                                                       |

| Figure 2.4 | voltage V <sub>th</sub> (Ref. [18])                                                   |

| Figure 2.4 | voltage $V_{\text{th}}$ (Ref. [18])                                                   |

| Figure 2.4 | voltage $V_{\rm th}$ (Ref. [18])                                                      |

| -          | voltage $V_{\rm th}$ (Ref. [18])                                                      |

| -          | voltage $V_{th}$ (Ref. [18])                                                          |

| -          | voltage $V_{\rm th}$ (Ref. [18])                                                      |

| -          | voltage $V_{\rm th}$ (Ref. [18])                                                      |

| -          | voltage $V_{th}$ (Ref. [18])                                                          |

| -          | voltage $V_{th}$ (Ref. [18])                                                          |

| Figure 2.5 | voltage $V_{\rm th}$ (Ref. [18])                                                      |

|            | electron affinity of semiconductor, $V_{bi}$ is the built-in potential, and $W$ is |

|------------|------------------------------------------------------------------------------------|

|            | the depletion width (Ref. [25])                                                    |

| Figure 2.7 | Schematic of the trilayer OLET with the chemical structure of each OSC,            |

|            | and the processes of charge transport and light-generation (Ref. [67])             |

|            |                                                                                    |

| Figure 2.8 | Cross-sectional view of a VOLET with a network source electrode having             |

|            | periodic apertures. The lateral charge transport $(q_{\rm L})$ and the vertical    |

|            | charge transport $(q_{\rm V})$ are depicted as solid and dashed arrows,            |

|            | respectively (Ref. [68])                                                           |

| Figure 3.1 | Device structures of various ambipolar OFETs with (a) single OSC, (b)              |

|            | blended OSC, and (c) bilayer OSCs                                                  |

| Figure 3.2 | Device structure of an ambipolar-type OFET with dual-gate, two-stacked             |

|            | OSCs, which has two OSC/metal interfaces for corresponding two                     |

|            | separate channels                                                                  |

| Figure 3.3 | Transfer curves of a p-type OFETs in the (a) top gate configuration and            |

|            | (b) bottom gate configuration with single gate electrode (Ref. [78])               |

|            | 35                                                                                 |

| Figure 3.4 | Transfer curves of an n-type OFETs in the (a) top gate configuration and           |

|            | (b) bottom gate configuration with single gate electrode (Ref. [78])               |

|            | 35                                                                                 |

| Figure 3.5 | Transfer curves of an ambipolar-type OFET with dual-gate: (a) p-type               |

|            | operation (sweeping bottom gate) with floated top gate, and (b) n-type             |

|            | operation (sweeping top gate) with floated bottom gate (Ref. [78]).                |

|            |                                                                                    |

| Figure 3.6 | Transfer curves of an ambipolar-type OFET with dual-gate: (a) p-type               |

|            | operation (sweeping bottom gate) with negatively biased top gate, and              |

|            | (b) n-type operation (sweeping top gate) with positively biased bottom                                                                                                         |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|            | gate (Ref. [78])                                                                                                                                                               |

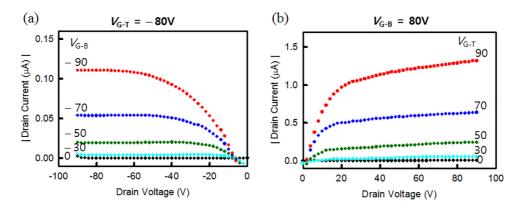

| Figure 3.7 | Output curves of ambipolar-type OFET with dual gate: (a) p-type                                                                                                                |

|            | operation at the $V_{\text{G-T}}$ = -80 V while $V_{\text{G-B}}$ was varied from 0 V to -90 V,                                                                                 |

|            | and (b) n-type operation at the $V_{\text{G-B}} = 80 \text{ V}$ while $V_{\text{G-T}}$ was varied from                                                                         |

|            | 0 V to 90 V (Ref. [78])                                                                                                                                                        |

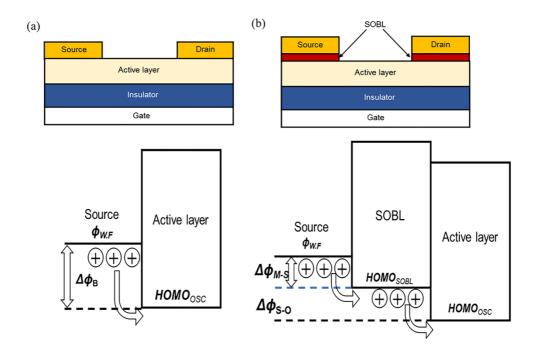

| Figure 4.1 | Device structures and corresponding energy diagram of (a) an OFET                                                                                                              |

|            | without semiconducting organic buffer layer (SOBL) and (b) an OFET                                                                                                             |

|            | with SOBL, respectively                                                                                                                                                        |

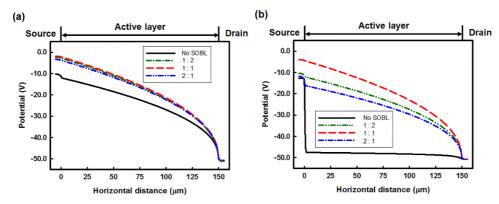

| Figure 4.2 | Spatial distribution of potential in the channel at various $\varDelta\phi_{\text{M-S}}:\varDelta\phi_{\text{S-O}}$                                                            |

|            | ratio having (a) $\Delta \phi_{\rm B} = 0.4$ eV and (b) $\Delta \phi_{\rm B} = 0.6$ eV. Black line represents                                                                  |

|            | the potential distribution in OFET without SOBL, the green dot-dashes                                                                                                          |

|            | represent that in OFET with $\Delta \phi_{\text{M-S}}$ : $\Delta \phi_{\text{S-O}} = 1:2$ , the red dashes represent                                                           |

|            | that in OFET with $\varDelta\phi_{\text{M-S}}:\varDelta\phi_{\text{S-O}}=1:1,$ and the blue dash-dot-dot                                                                       |

|            | patterns represent that in OFET with $\Delta \phi_{\text{M-S}}$ : $\Delta \phi_{\text{S-O}} = 2:149$                                                                           |

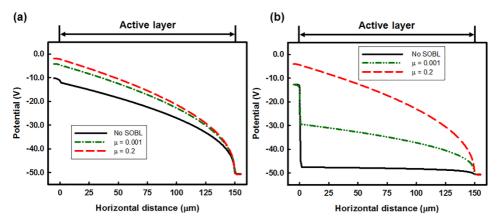

| Figure 4.3 | Spatial distribution of potential in the channel at different mobility of                                                                                                      |

|            | SOBL having (a) $\Delta\phi_{\rm B}=0.4$ eV and (b) $\Delta\phi_{\rm B}=0.6$ eV. Black line                                                                                    |

|            | represents the potential distribution in OFET without SOBL, the green                                                                                                          |

|            | dot-dashes represent that in OFET with the mobility of SOBL as $0.001$                                                                                                         |

|            | $\mbox{cm}^2/\mbox{Vs}$ and the red dashes represent that in OFET with with the mobility                                                                                       |

|            | of SOBL as 0.2 cm <sup>2</sup> /Vs                                                                                                                                             |

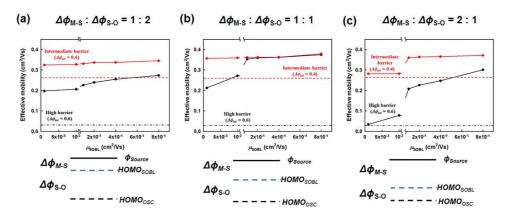

| Figure 4.4 | Simulation results of the effective mobility in conditions of (a) $\varDelta\phi_{\text{M-S}}$ :                                                                               |

|            | $\Delta \phi_{\text{S-O}} = 1:2$ , (b) $\Delta \phi_{\text{M-S}}: \Delta \phi_{\text{S-O}} = 1:1$ , and (c) $\Delta \phi_{\text{M-S}}: \Delta \phi_{\text{S-O}} = 2:1$ . Black |

|            | dots represent the mobility of an OFET with $\Delta\phi_{\rm B}$ = 0.6 eV and red black                                                                                        |

|            | dots represent that with $\Delta\phi_{\rm B}$ = 0.4 eV. The black dot-dashes show the                                                                                          |

|            | effective mobility of an OFET with $\Delta \phi_{\rm B} = 0.6$ eV and the red show that                                                                                        |

|            | with $\Delta \phi_{\rm B} = 0.4$ eV without SOBL, respectively                                                                                                                 |

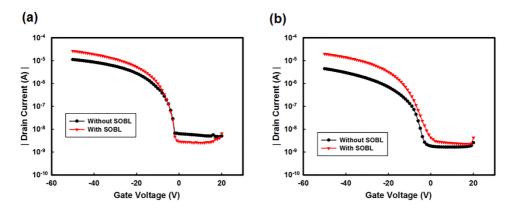

| <b>Figure 4.5</b> Transfer curves of the OFETs at $V_D = -50 \text{ V}$ having (a) $\Delta \phi_B = 0.4 \text{ eV}$ (Au |

|-------------------------------------------------------------------------------------------------------------------------|

| electrode) and (b) $\Delta \phi_{\rm B} = 0.6$ eV (Ag electrode), respectively. The black                               |

| circles represent the transfer curve of an OFET without SOBL and the                                                    |

| red triangles represent that of an OFET with SOBL 55                                                                    |

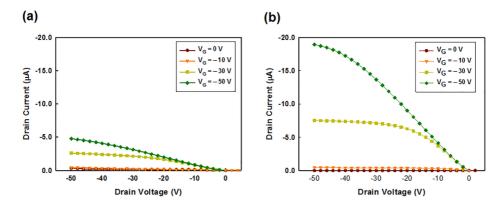

| <b>Figure 4.6</b> Output curves of OFETs having $\Delta \phi_{\rm B} = 0.4$ eV (a) without SOBL and (b)                 |

| with SOBL at various $V_{\rm G}$                                                                                        |

| <b>Figure 4.7</b> Output curves of OFETs having $\Delta \phi_{\rm B} = 0.6$ eV (a) without SOBL and (b)                 |

| with SOBL at various $V_G$                                                                                              |

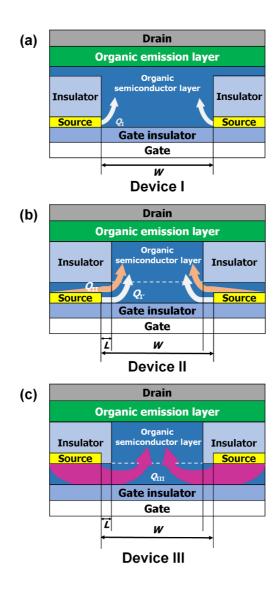

| Figure 5.1 Three different configurations of the VOLET; (a) Device I with no OSC                                        |

| above or below the source electrode, (b) Device II with the OSC between                                                 |

| the source insulator and the source electrode, and (c) Device III with the                                              |

| OSC between the source electrode and the gate insulator. $Q_{\rm I},Q_{\rm I},Q_{\rm II},$                              |

| and $Q_{\mathrm{III}}$ represent the flow of charges in the three VOLET structures,                                     |

| respectively. $W$ denotes the width of a single aperture region between                                                 |

| two adjacent stripes of the finger-like source electrode and $L$ represents                                             |

| an extended length of dielectric encapsulation of the source insulator                                                  |

| (Ref. [97])                                                                                                             |

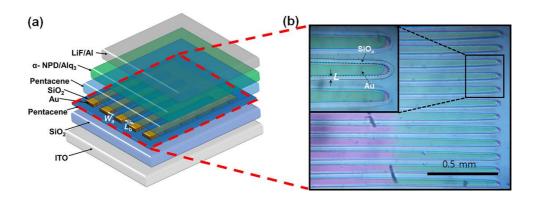

| Figure 5.2 (a) 3-D schematic of a VOLET with a dielectrically encapsulated source                                       |

| electrode. Dielectrically encapsulated source electrode is highlighted in                                               |

| red dashes. (b) Microscopic image of dielectrically encapsulated source                                                 |

| electrode with blocking length (L) of 10 $\mu$ m (Ref. [97]) 63                                                         |

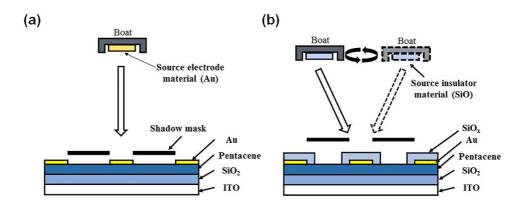

| Figure 5.3 Illustration describing fabrication method for deposition of dielectrically                                  |

| encapsulated source electrode by oblique deposition of source insulator.                                                |

| (a) The process of depositing source electrode and (b) the oblique                                                      |

| deposition of source insulator covering the top and side part of the                                                    |

| source electrode (Ref. [97])                                                                                            |

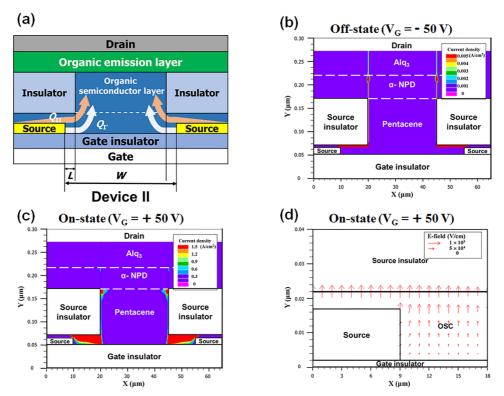

| Figure 5.4 | (a) The device schematic and charge flow of Device II. The current                                   |

|------------|------------------------------------------------------------------------------------------------------|

|            | density distributions of Device II (b) at off-state ( $V_G = -50 \text{ V}$ , $V_D = -10 \text{ J}$  |

|            | V), and (c) at on-state ( $V_G$ = - 50 V, $V_D$ = - 10 V). (d) Electric field lines                  |

|            | in the OSC layer near the source electrode of Device II at on-state. In a                            |

|            | color code from blue to red, the low density is shown in blue and the                                |

|            | high density in red except for zero density (in purple). (Ref. [97]).                                |

|            |                                                                                                      |

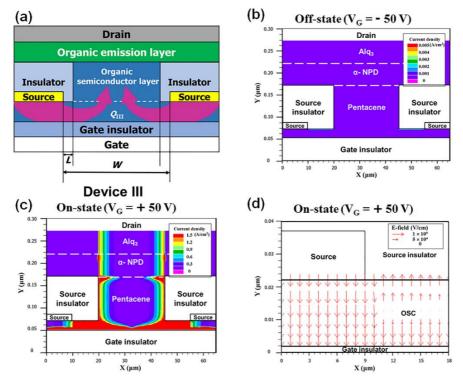

| Figure 5.5 | (a) The schematic and charge flow of Device III. The current density                                 |

|            | distributions of Device III (b) at off-state and (c) at on-state. (d) Electric                       |

|            | field lines in the OSC layer near source electrode of Device III at on-                              |

|            | state. In a color code from blue to red, the low density is shown in blue                            |

|            | and the high density in red except for zero density (in purple). (Ref. [97])                         |

|            |                                                                                                      |

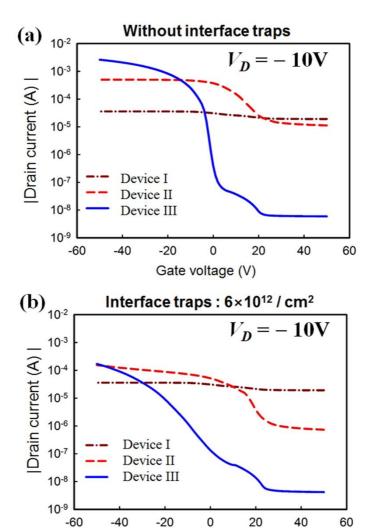

| Figure 5.6 | The simulated transfer curves of different VOLETs: (a) one with no                                   |

|            | interface traps and (b) the other with interface trap density of 6 $\times$                          |

|            | $10^{12} \mbox{cm}^2$ . The results for Device I, II and III are represented in a brown              |

|            | dash-dot line, a red dash line, and blue solid line, respectively. (Ref. [97])                       |

|            |                                                                                                      |

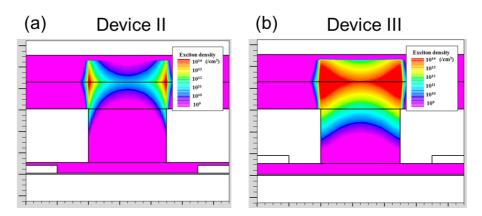

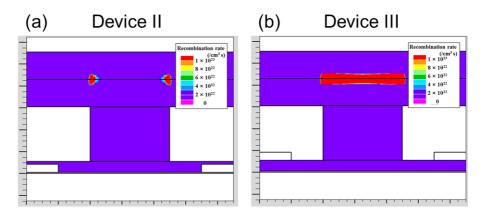

| Figure 5.7 | Spatial distribution of the exciton density in the on-state of Device II and                         |

|            | that of Device III obtained in numerical simulations                                                 |

| Figure 5.8 | Spatial distribution of the recombination rate in the on-state of Device II                          |

|            | and that of Device III obtained in numerical simulations 79                                          |

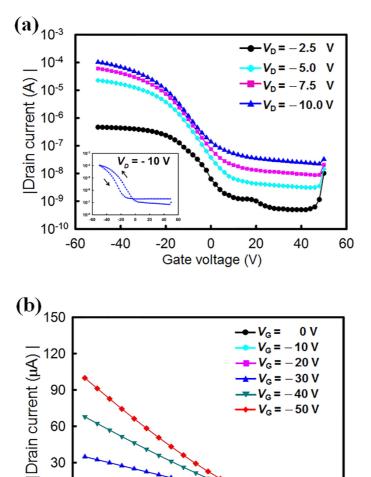

| Figure 5.9 | Experimental results of Device III. (a) The transfer curves as a function                            |

|            | of $V_{\rm G}$ at different values of $V_{\rm D}$ . (Inset: Hysteresis curve at $V_{\rm D} = -10$ V. |

|            | $V_{\rm G}$ was swept from $+$ 50 V to $-$ 50 V and then $-$ 50 V to $+$ 50 V.) (b) The              |

|            | output curves as a function of $V_{\rm D}$ at different values of $V_{\rm G}$ (Ref. [97])            |

|            | 81                                                                                                   |

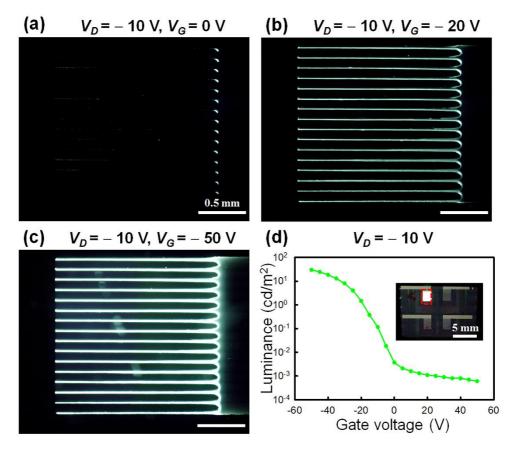

**Figure 5.10** Light emission properties of Device III. The microscopic images in area of device area (2.0 mm  $\times$  2.5 mm) under the bias conditions of (a)  $V_G = 0$  V, (b)  $V_G = -20$  V, and (c)  $V_G = -50$  V at fixed  $V_D = -10$  V. (d) The luminance transfer curve as a function of  $V_G$  at  $V_D = -10$  V. (Inset: the microscopic image showing the light emission covering the whole device area, indicated by a red dash rectangle) (Ref. [97]) ....... 84

#### **List of Tables**

| Table 4.1 The electrical parameters of materials used in simulation             | 46        |

|---------------------------------------------------------------------------------|-----------|

| Table 5.1 The electrical parameters of materials for organic layers used in sin | nulation  |

|                                                                                 | 69        |

| Table 5.2 The electrical parameters of materials for electrodes and insulators  | s used in |

| simulation                                                                      | 69        |

| Table 5.3 The opto-electrical parameters of material for emission layer         | used in   |

| simulation                                                                      | 79        |

#### **Chapter 1. Introduction**

#### 1.1. Overview of organic electronics

Organic electronics has been attracted a great attention due to its potentials for the application of novel class of electronic devices. For example, organic electronic devices have been widely investigated in the fields of integrated circuits, bendable/flexible electronic devices, chemical-/or bio- sensors, photovoltaic devices, and optoelectronic devices. [1] In addition, organic electronics have potential to be fabricated by low-cost, easy and high-throughput process and large-area production method. Among the various organic electronic devices, optoelectronic devices including organic field-effect transistors (OFETs), organic light-emitting diodes (OLEDs), and organic photovoltaic cells (OPVs) are in the center of interest. More excitingly, the optimization of organic semiconductor material design at the molecular level as well as structural innovation of organic devices allow organic electronic devices to exhibit excellent electrical characteristics with high mobility, low threshold voltage and stability and different functional properties simultaneously or under different operating conditions in a single device. Therefore, the multifunctional organic devices are considered as one of the hot topics in organic electronics.

In this regards, several ways to enhance the electrical performance of OFETs and organic light-emitting transistors (OLETs) by employing multi-layer organic semiconductors in a single device have been presented. The introduction of the multi-layer OSCs helps to accomplish the improvement of charge injection and charge transport in OFETs and OLETs. In this thesis, the structural optimization of the ambipolar-type OFETs in dual gate configuration and that of the vertical-type

OLETs via numerical simulation together with experimental data will be presented, which will provide the multi-functional integration in a single OFETs.

In this **Chapter 1**, two different organic electronic devices will be briefly introduced. One is the OFETs mainly used for the application of switching and driving transistors in integrated circuits and/or active matrix display component. The other is the OLETs for the integration of OFETs and OLEDs in a single device having both electrical switching performance and light-emitting characterisites, which can be controlled by applying the voltage for corresponding electrodes.

#### 1.2. Organic field-effect Transistors

OFETs have been considered as one of the attractive candidates for a broad range of low-cost, flexible electronic applications, including electronic papers, radio frequency identification (RFID) tags, and chemical-/bio-sensors [1-3]. Due to the extensive development of organic electronics, great progresses have been made towards the high performance organic devices with field-effect mobility well over 1 cm<sup>2</sup>/Vs [4, 5]. Moreover, the systemic investigation of the relationship between the molecular structure and device performances, the novel patterning technique of organic materials, and the innovative architectures such as vertical-type OFETs or dual-gate configuration of OFETs enable the construction of integrated circuits, and the exploration of novel applications with OFETs [6, 7]. Among these important progresses, the development of multi-functional OFETs, which combine two or more types of physical properties in a single device, has attracted particular attention. Recently, numerous studies on OFET based sensors, photodetectors, and organic light-emitting transistors (OLETs) have been demonstrated by various research groups [8-10], which clearly demonstrate the rapid developments of multi-functional OFETs. To achieve the multi-functional characteristics in a single OFETs, multilayer organic semiconductors (OSCs) are often used. In those OFETs with multilayer OSCs, it is essential to precisely control the charge injection and charge transport [11]. Especially, the advent of novel device configuration with multi-layer OSCs strongly requires the optimization of the charge injection and transport based on the systemically investigated physical mechanism.

**Figure 1.1.** Illustration of device structure, electrical characteristics, and applications of OFETs (Ref. [1]).

#### 1.3. Organic light-emitting transistors

Tremendous interest in organic optoelectronics has been drawn as the emergence of OLETs [8, 9]. An OLET has three electrodes with same role as those of an OFET, which determines degree of the injected charges, the accumulation of injected charges at the channel region, and the transport of accumulated charges. In addition, by governing the process of exciton recombination in the channel region, the feature of light-emission can be also accomplished in OLETs [8-11]. That is, OLETs offer the possibility to combine the electrical switching capability with the light-emission function in a single device, thereby less complex circuit design is required in realization of next-generation display circuit.

Moreover, OLETs are considered as excellent opto-electronic devices to investigate physical mechanism via observation of light-emission properties. For instance, the processes of charge-carrier injection, transport, recombination, and light-emission in organic semiconductors can be directly observed by the location of light-emission in terms of the applied voltage for each electrode. In this regard, the use of the high-resolution (up to nanometer scale) microscopic observation devices offers more detailed and easy access for physical mechanism.

The nature of the semiconductor and the chemical and dielectric properties of the insulator as well as the materials for each electrode, the device architecture and the processing conditions are fundamental in optimizing the optoelectronic parameters (charge carrier mobility, brightness, voltage threshold, quantum efficiency, etc.) of OLETs. Therefore, there have been various approaches toward the improvement of OLET such as (i) multi-layer OSCs for better charge transport and light-emission [12, 13]; (ii) modified electrodes for better charge injection [14-16]; (iii) increase of out-coupling efficiency by same techniques in OLEDs.

Still, more specific and detailed investigations on the physical mechanisms of

OLETs from the viewpoint of the injection, transport and recombination of charges as well as the light emission processes in organic light-emitting field-effect transistors are strongly required. Moreover, multi-layer OLETs should be optimized not just from the viewpoint of materials used, but also in the perspective of the device structure and geometrical level. Therefore, the novel device architecture of OLET is discussed in **Chapter 5**.

**Figure 1.2.** Schematic representation of the device structures and the main optoelectronic processes occurring in an OLET (Ref. [9]).

#### 1.4. Outline of thesis

This thesis is organized into the following Chapters of 1-6, including the Introduction and Concluding Remarks. In Chapter 1, the introduction of organic electronics, especially about the OFETs and OLETs with multi-layer structure for application of the advanced organic electronic circuits and/or the active matrix display component. In Chapter 2, I mainly discuss on the introduction and basic theoretical principals of OFETs. Moreover, advanced configurations such as multilayer OFETs, ambipolar-type OFETs, and OLETs with vertical configuration will be shown briefly. In Chapter 3, I present on the specific concept for enhancement of the charge transport mechanism via OFETs with multi-layers. The enhancement of transport characteristics of both charges (electrons and holes) in ambipolar-type OFETs will be demonstrated by introducing the dual-gate configuration with twostacked OSCs. The two-stacked OSCs in ambipolar-type OFETs form the separate channels for the electrons and the holes, respectively. The separate channels can be individually controlled by corresponding gate electrode while the counter gate electrode effectively suppresses the accumulation and transport of courter charge. The improvement of injection transport in terms of energy barrier height is discussed in the Chapter 4. With numerical simulations, the scientific investigation of physical mechanism in injection of OFETs was conducted in terms of the effect of the injection barrier height together with the mobility of buffer layer on the electrical characteristics of OFETs. Based on simulation results, the semiconducting organic buffer layer (SOBL) was inserted in typical bottom gate top contact OFET configuration. The SOBL enables the improvement of injection mechaism by tailoring injection barrier height as well as the increase of overall mobility by transporting the injected charges toward the channel region. In Chapter 5, vertical OLETs having high on/off ratio will be shown. The achievement of high on/off ratio

is accomplished by dielectric encapsulation of source electrode. The dielectrically encapsulating source insulator can successfully reduce the off-current current (leakage current between source-drain electrode) injected from the top and side of source electrode. Moreover, the injected charges can be accumulated at the interface of gate-inulsator/OSC, resulting increased gate-controllability. The degree of on/off ratio in terms of device configuration was investigated by 2-D numerical simulation tools. In addition, the effect of interfacial defect at the OSC/source-insulator on the on/off ratio was also studied. Finally, the concise summaries and some concluding remarks are presented in **Chapter 6**.

#### **Chapter 2. Theoretical Backgrounds**

#### 2.1. Operation principle of organic field-effect transistors

In this section, the basic structures, the current-voltage characteristics, and working principles of organic field-effect transistors will be introduced. In addition, this section will also briefly describe the basic component of OFETs, most common charge transport models, some important parameters, and the various device configuration of OFETs.

An organic field-effect transistor mainly consists of the parts of three electrodes, gate insulator, and an organic semiconductor (OSC). In detail, a gate insulator covers gate electrode. The source and drain electrodes with channel width W and the semiconducting layer with a channel length of L plays important role on carrier transport (shown in Figure 2.1). The OSC layer of an OFET is formed by vacuum deposition, drop-cast, or spin-cast method. The gate electrode can be a metal or a conducting polymer. As gate insulator, inorganic insulator or polymeric insulators are commonly used. The source electrode injects charges into the active layer and the drain electrode collects the transported charges. The metals and solution-processable conducting polymers have been used for the source and drain electrodes.

Figure 2.1. Structure of an OFET. L represents channel length, W the channel width,  $V_d$  the drain voltage, and Vg the gate voltage (Ref. [18]).

Figure 2.2 illustrates the basic operating regimes and associated current-voltage characteristics of a field-effect transistor. When  $V_G > 0$ , the electrons will be injected from the source electrode and then accumulated at the interface of insulator/semiconductor (the channel region). For negative  $V_G$ , the holes will be injected and accumulated at the channel region. The degree of accumulation at the interface is proportional to  $V_G$  and the capacitance  $C_i$  of the gate insulator. Those accumulated charges will be transported to the drain electrode by electric fields induced by the drain voltage, which contribute to the drain current.

Figure 2.2. Illustrations of operating regimes of OFETs: (a) linear regime; (b) start of saturation regime at pinch-off, (c) saturation regime and corresponding current-voltage characteristics (Ref. [18]).

However, due to the defects of OSC and gate insulator, not all injected charges can be transported to the drain electrode. At first, the deep traps in the OSC absorb the injected charges. That is, a gate voltage has to be applied that is higher than a threshold voltage  $V_{\rm th}$ , and thus the effective gate voltage is reduced to  $V_{\rm G}-V_{\rm th}$ . On the other hand, donor (for n-channel) or acceptor (for p-channel) states and interface dipoles can create an internal potential at the interface and thus cause accumulation of charges in the channel even when  $V_{\rm G}=0$  V. [19, 20]

When zero source-drain bias ( $V_{\rm DS}$ ) is applied, the carrier concentration in the transistor channel is uniform. A linear gradient of charge density from the carrier-injecting source to the extracting drain forms when a negligible small source-drain voltage is applied ( $V_{\rm DS} << V_{\rm G}$ , Figure 2.2(a). This regime is called as the linear regime, in which the degree of current flowing through channel is directly proportional to

$V_{\rm DS}$ . In the linear regime, the drain current  $(I_{\rm D})$  can be simplified to

$$I_D = (W/L)\mu_{lin}C_i(V_G - V_{th} - 0.5V_{Ds})V_{Ds}$$

(1)

The drain current is directly proportional to  $V_G$ , and the field-effect mobility in the linear regime ( $\mu_{lin}$ ) can thus be extracted from the gradient of  $I_D$  versus  $V_G$  at constant  $V_{DS}$  (applicable for gate voltage dependent mobility).

When  $V_{\rm DS}$  is further increased to a point of  $V_{\rm DS} = V_{\rm G} - V_{\rm th}$ , the channel becomes "pinched off" (Figure 2.2(b)). Here, a depletion region is formed next to the drain electrode because the difference between the local potential and the gate voltage is now below the threshold voltage. A space-charge-limited saturation current  $I_{\rm DS,sat}$  can flow across this narrow depletion zone as carriers are swept from the pinch-off point to the drain by the comparatively high electric field in the depletion region. Further increasing the source-drain voltage will not substantially increase the current but will lead to an expansion of the depletion region. Since the potential at the pinch-off point remains  $V_{\rm G} - V_{\rm th}$  and thus the potential drop between that point and the source electrode stays approximately the same, the current saturates at a level  $I_{\rm DS,sat}$  (Figure 2.2(c)). Here, the saturation current can be obtained by substituting  $V_{\rm DS}$  with  $V_{\rm G} - V_{\rm th}$ , yielding

$$I_D = (W/2L)\mu_{sat}C_i(V_G - V_{th})^2$$

(2)

Note that transistors with short channel lengths require thin gate dielectrics, typically  $L > 10d_{\rm dielectric}$  [21, 22], in order to ensure that the field created by the gate voltage determines the charge distribution within the channel (gradual channel approximation) and is not dominated by the lateral field due to the source-drain voltage. Otherwise, a space-charge-limited bulk current will prevent saturation and the gate voltage will not determine the "on" or "off" state of the transistor [23-27].

**Figure 2.3.** Representative current-voltage characteristics of an n-type OFET. (a) Output characteristics showing the linear and saturation regimes. (b) Transfer characteristics in the linear regime and the onset voltage  $(V_{on})$ . (c) Transfer characteristics in the saturation regime and the threshold voltage  $V_{th}$  (Ref. [18]).

Figure 2.3(a) shows typical output characteristics (the drain current versus source-drain voltage for various constant gate voltages) of an n-channel OFET with a channel length of 200  $\mu$ m. From the output characteristics, the linear regime at low  $V_{\rm DS}$  and the saturation regime at high  $V_{\rm DS}$  are evident.

Figure 2.3(b) shows the transfer characteristics (the drain current versus gate voltage at constant  $V_{\rm DS}$ ) of the same transistor in the linear regime by both as a semilog plot and as a linear plot. From the semi-log plot, the onset voltage ( $V_{\rm on}$ , the voltage at which the drain current abruptly increases above a defined low off-current level) can be easily extracted and the subthreshold swing ( $S = dV_{\rm G}/d(\log I_{\rm ds})$ ), which depend on the gate dielectric capacitance and the trap states at the interface, can be also calculated. The gradient of the current increase in the linear regime is directly proportional to the mobility if the mobility is gate voltage independent. Most semiconductors, however, show gate-voltage-dependent mobility, and thus, the curve shape may deviate from being linear.

Figure 2.3(c) shows a transfer curve in the saturation regime. Here the square root of the drain current should be linearly dependent on the gate voltage, and its gradient is proportional to the mobility. Extrapolating the linear fit to zero yields the threshold voltage  $V_{\text{th}}$ . Threshold voltage is originated from several effects and

strongly dependent on the OSC and dielectric used. Built-in dipoles, impurities, interface states, and, in particular, charge traps contribute to the threshold voltage [28]. Note that  $V_{th}$  can be reduced by increasing the gate capacitance and thus inducing more charges at lower applied voltages. The threshold voltage is not necessarily constant for a given device. When OFETs are operated for long time,  $V_{th}$  tends to increase. This bias stress behavior has a significant effect on the applicability of OFETs in circuits and is presently under intense investigation [29-34]. A shift of the threshold voltage on the time scale of current-voltage measurements causes current hysteresis (usually the forward scan shows higher currents than the reverse scan), stable threshold shifts, for example, induced by polarization of a ferroelectric gate dielectric, can be used in organic memory devices [35, 36].

Another important parameter of OFETs is the on/off ratio, which is the ratio of the drain current in the on-state at a particular gate voltage and the drain current in the off-state ( $I_{\rm on}/I_{\rm off}$ ). For excellent switching behavior, this value should be as large as possible. The on-current mainly depends on the mobility of the OSC and the capacitance of the gate dielectric. The magnitude of the off-current is determined by gate leakage and by the bulk conductivity of the semiconductor, which can increase due to unintentional doping, as for example often observed in P3HT transistors [37-39].

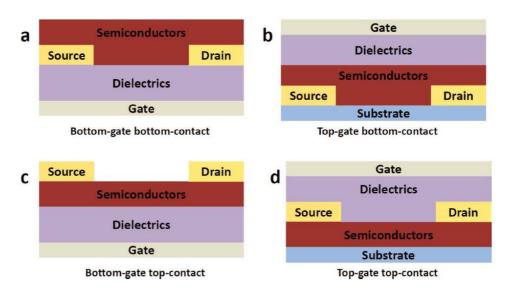

The difference of geometry has also great impact on the electrical characteristics even in case of OFETs with identical materials. The device configuration can be categorized in four-ways based on the position of gate electrode and contact between source/drain electrode and OSC. The four different device structures of the bottom-gate bottom-contact (BCBG, Figure 2.4(a)), top-gate bottom-contact (TGBC, Figure 2.4(b)), bottom-gate bottom-contact (BGBC, Figure 2.4(c)), and top-gate top-contact (TCTG) and top contact/bottom gate (TCBG, Figure 2.4(d)) structures are shown in Figure 2.4. One of the major differences

between these device geometries arises from the position of the injecting electrodes in relation to the gate. In the bottom contact/bottom gate structure, the charges are directly injected into the channel of accumulated charges at the semiconductor-dielectric interface. In the other structures, the source/drain electrodes and the channel are separated by the semiconducting layer. Thus, charges first have to travel through several tens of nanometers of undoped semiconductor before they reach the channel. Other differences among the transistor structures arise from the dielectric/semiconductor and electrode/semiconductor interfaces, such as different morphologies at the top and bottom surfaces of a semiconductor film (molecular orientation, roughness) [40] or introduction of trap states during metal evaporation on organic semiconductors for top contact transistors [41, 42].

**Figure 2.4** Device structures of typical OFETs: (a) bottom-gate bottom-contact (BGBC), (b) top-gate bottom-contact (TGBC), (c) bottom-gate topcontact configurations (BGTC), and (d) top-gate top-contact (TGTC) (Ref. [1]).

### 2.2. Charge transport in ambipolar-type organic field-effect transistors

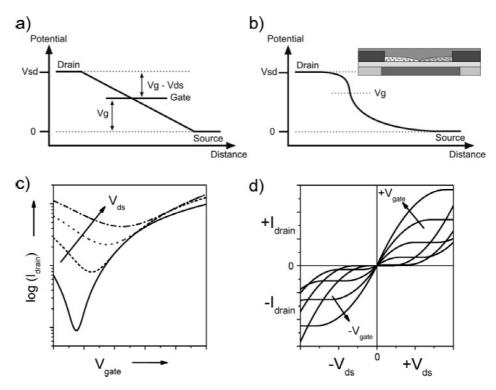

The performance of OFETs has improved immensely over the past decades, with OFET mobility in some cases exceeding those of amorphous silicon FETs [43-45]. Most of the OFETs have shown only unipolar behavior (either holes or electrons). However, the fabrication of devices exhibiting ambipolar-type behavior that can provide both n- and p-channel performance in single device is very important due to their application in large-area manufacturing of complementary integrated circuits without requiring micro-patterning of the individual p- and n-channel semiconductors [46]. Another advantage of ambipolar-type OFETs is that the light emission can be achieved in ambipolar-type OFETs by recombination of holes and electrons within the transistor channel. The ambipolar-type feature associated with light-emission will be discussed in **Section 2.5.** In this section, only electrical characteristics of ambipolar-type OFETs will be discussed.

For an ambipolar-type OFET, both electrons and holes are accumulated depending on the applied voltages. To understand ambipolar-type operation in OFET, let us assume an OFET at a given positive drain voltage  $V_{\rm D}$  (the source potential is held at ground,  $V_{\rm S}=0$  V) and start with a positive gate voltage of  $V_{\rm G}>V_{\rm D}$ . Like a typical n-type OFET, the gate electrode is more positive than the source electrode and thus electrons are injected from the source into the accumulation layer and drift toward the drain, given that  $V_{\rm g}>V_{\rm th,e}$  ( $V_{\rm th,e}$  is threshold for electron accumulation). Only one polarity of carriers is present, and we call this the unipolar regime. On the other hand, if  $V_{\rm G}$  is smaller than  $V_{\rm D}$ , the gate potential is more negative than that of the drain electrode by  $V_{\rm G}-V_{\rm D}$ . While, for  $V_{\rm G}< V_{\rm th,e}$ , the source will not inject electrons, the drain electrode in an ambipolar transistor will inject holes into the channel if  $V_{\rm G}-V_{\rm D}< V_{\rm th,h}$  ( $V_{\rm th,h}$  is threshold for hole accumulation). Thus, one should

actually now speak of the drain electrode as a hole source. A hole current will flow, and thus, the measured drain current will be high, not like in a unipolar, n-channel transistor, which would now be in an off-state. If the gate potential is somewhere between  $V_D$  and  $V_S$  so that it is bigger than  $V_{Th,e}$  but also  $V_G - V_D < V_{Th,h}$  (Figure 2.5(a)), both the source and drain electrode will inject the respective charge carriers and thus both electrons and holes are present in the channel. This regime is called the ambipolar regime, in contrast to the unipolar regime, where only one polarity of charges is present in the channel for any particular biasing condition.

In an ideal ambipolar transistor with just one semiconducting layer, the ambipolar regime is characterized by a hole and an electron accumulation layer next to the respective electrode that meet at some point within the transistor channel (inset of Figure 2.5(b)). There, oppositely charged carriers recombine. In electroluminescent materials, this leads to light emission from within the channel, which will be discussed in **Section 2.5**.

The length of each channel and thus the meeting point and position of the recombination zone depend on the applied gate and source-drain voltage and mobility ratio. The potential of the transistor channel in the ambipolar regime can roughly be imagined as that of a saturated hole and electron channel in series, resulting in an S-shaped transition region (Figure 2.5(b)), as shown in previous studies [47-49]. The transfer curves of ambipolar transistors exhibit a characteristic V-shape with one arm indicating electron transport and the other indicating hole transport (see Figure 2.5(c)). For positive (negative) applied voltages, the effective gate voltage for holes (electrons) depends on the applied source-drain voltage, which gives rise to the characteristic dependence of the transfer characteristics on the source-drain voltage. The output curves are characterized by a superposition of standard saturated behavior for one carrier at high  $V_G$  and a super-linear current increase at low  $V_G$  and high  $V_{DS}$  due to injection of the opposite carrier (Figure 2.5(d)).

**Figure 2.5** (a) Illustration of the electrode potentials in an OFET. (b) Channel potential in an OFET in the ambipolar-type with two separate channels of holes and electrons that meet in the channel where opposite charge carriers recombine (inset). (c) Transfer characteristics of an ambipolar transistor. (d) Output characteristics of various values of  $V_G$  and  $V_{DS}$ . (Ref. [18])

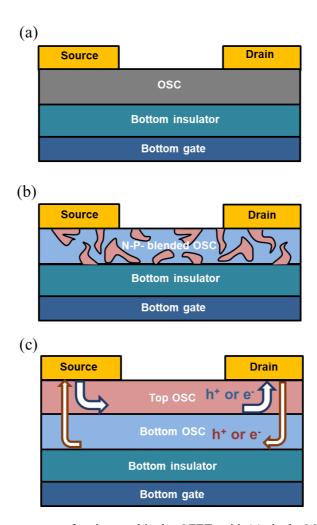

There are three major groups of ambipolar transport OFETs, which can be classified by the semiconducting layer: single ambipolar OSC, blended OSCs, and bilayer OSC(s) [43].

One of the challenges of fabricating ambipolar transistors with single OSC lies in the efficient injection of both charge carriers. Optimal charge injection takes place when the work function of the metal electrode lines up with the HOMO level of the semiconductor for hole injection and with the LUMO level for electron injection. Since most of the standard organic semiconductors have band gaps of 2-3 eV, the injection of at least one carrier must be contact limited for any given electrode

material. Another challenge is trapping of one or both carrier types. We have seen that especially electrons are likely to be trapped by impurities or certain chemical moieties at the dielectric/semiconductor interface. This can be prevented by using appropriate dielectrics, using pure materials, and processing in an inert atmosphere. The stability of hole and electron transport under ambient conditions, and thus exposure to moisture and oxygen, is another issue.

An alternative method of using blends of n- and p-channel materials is suggested to realize ambipolar-type transport in a single OSC layer. For the blend approach, both co-evaporated and solution-processed films are possible. Those results show good ambipolar characteristics but mobility of each carrier is smaller than that of the pure materials [50]. This can be understood in terms of interpenetrating networks of n-channel and p-channel materials, which predominantly conduct one or the other carrier due to their different electron affinities and ionization potentials, and thus, the effective mobilities of both electrons and holes in a percolating network are lower compared to that of a neat film. Some studies reveal that the ambipolar characteristics of these blend films depend strongly on the nature of the dielectric they are spun upon and the resulting film morphology [51]. Inverters fabricated with such blends show high gain [52] and thus could be suitable for integrated circuits. However, those OSC film formed by blends of two material have experienced poor surface properties such as non-uniform grains, high surface roughness, and high grain boundary resistance.

Another way to achieve the balanced ambipolar-type electrical characteristics is suggested as an OFET with bilayer configuration. A lot of bilayer structures such as pentacene/PTCDI-C<sub>13</sub>H<sub>27</sub>, pentacene/C<sub>60</sub>, and DH4T/PTCDI-C<sub>13</sub>H<sub>27</sub> have been found to exhibit ambipolar behavior [53, 54].

However, there are some major issues of bilayer structure. First, few case of ambipolar bilayer OFETs based on solution-processed semiconductors have been demonstrated up to now, due to the problem of degradation of bottom OSC from the solvent of top OSC. Second problem is that the one OSC is not directly contact with source/drain electrode, so injection is not balanced. Moreover, one OSC layer screens the electrical field from the gate electrode toward the other OSC layer, so the gate-controllability is greatly reduced for one-type of charges. As a result, the mobility of each charge carrier in bilayer is lower than that of OFET with single layer.

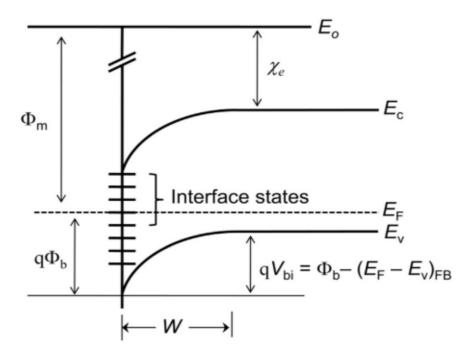

### 2.3. Role of injection barrier height in in organic field-effect transistors

In recent decades, the development of OSCs have demonstrated carrier mobility of over 10 cm<sup>2</sup>/Vs in organic field-effect transistors [1, 18, 43]. This value is comparable or even exceeding the mobility of amorphous/polycrystalline siliconbased FETs. In spite of this surprisingly high charge transport in OSCs, the need for improvement in contact injection properties in OFETs remains. That is, before a current flow through the transistor channel, the charges have to be injected from the source electrode into the semiconductor. For charges to be injected, electrons should be injected into the LUMO level in case of n-type OFET and holes should be injected into the HOMO level of the semiconductor in case of p-type OFETs, For injection of charges from electrode to OSC, injection barrier height plays critical role on determining the amount of injected charges at same bias condition. The injection barrier can be defined as difference between the work-function of electrode and the HOMO/LUMO level of OSC for holes/electrons. When the work function of the injecting metal is close to the HOMO or LUMO level of the semiconductor, an ohmic contact is expected [55]. In ohmic contact cases, the charges are easily injected from the electrode to OSC without potential loss. Otherwise, the charges have to overcome the injection barrier so the loss of potential at the contact exist. The amount of potential loss is expressed as an additional resistance (contact resistance) in the OFET. Contact resistance can be measured as the voltage drop at the electrodes by means of Kelvin probe, four-point probe measurements, or by transfer line method [18]. In a short-channel OFET with high OSC material, contact resistance can be significant or even larger than the channel resistance and effective mobility is greatly reduced than that of OSC material itself [56]. In particular, the linear regime of fieldeffect transistors is more affected by contact resistance because a large part of the

source-drain voltage already drops at the contacts and not across the channel. High non-ohmic contact resistance can be indirectly observed in the output curve as an initially suppressed and then super-linear current (S-shape) in the linear region. Adjusting the work function of the injecting metal with the HOMO/LUMO levels of an OSC is simple and good way to achieve the low contact resistance. However, the simple matching of the electrode work-function and the HOMO/LUMO of an OSC is sometimes insufficient to decrease the contact resistance. An additional dipole barrier at the interface tends to change the metal work function [57], and thereby the interface barrier height is increased. In this regard, the formation of dipoles at the metal/OSC interface through self-assembled monolayers have been proven to useful approach for enhancing the injection properties of OFETs [58].

**Figure 2.6.** The energy band diagram of Schottky barrier with interface states:  $\Phi_{\rm m}$  is the metal work function,  $\Phi_{\rm b}$  is the Schottky barrier height,  $\chi_{\rm e}$  is the electron affinity of semiconductor,  $V_{\rm bi}$  is the built-in potential, and W is the depletion width (Ref. [25]).

Additionally, the device structure has influence on the contact resistance. As mentioned in **Section 2.1.**, in a geometry of TGBC and BGTC, the charges are injected over a relatively larger area than in a BGBC configuration. This phenomena, called current crowding, reduces a contact resistance in given materials [59]. Furthermore, while bottom contacts can be modified to alter their work function, evaporated metals may introduce surface states in the semiconductor that help or hamper charge injection [41]. And during the OSC formation, OSC experience different surface energy in the regions of metal and gate-insulator. Those different surface condition leads to the poor morphology of OSC film, for example, non-uniform and smaller grain size. Therefore, non-uniformity of OSC film in bottom contact degrades the transport of charges in the OSC layer.

# 2.4. Organic light-emitting transistors

### 2.4.1. General description of organic light-emitting transistors

Recently, organic light-emitting transistors (OLETs) have been attracted a lot of attention for their potential of combining the electrical switching functionality of an OFET and the light generation capability of OLED in a single device [8-11]. OLETs represent a novel class of organic devices, and could pave the way towards nanoscale light sources and highly integrated organic optoelectronics. In addition, it is worth mentioning that OLETs offer an ideal structure for improving the lifetime and efficiency of organic light-emitting materials due to different driving conditions with respect to standard OLED architectures, and to optimized charge-carrier balances. Here, several recent advances in the use of field-effect transistor architectures to achieve light generation from a variety of organic materials are described. The advantages in terms of low fabrication costs and ease of integration on virtually any substrate are highlighted in the discussion of OLETs based on organic thin films. Some possible directions of development and opportunities that could be offered by this new class of devices are also discussed.

Organic light-emitting field-effect transistors were first demonstrated [60] using a device structure with interdigitated gold source and drain electrodes with a charge transport and emitting layer of a tetracene. The electrical device characteristics are typical of a unipolar p-type field-effect transistor, whereas observation of light emission from tetracene proves that electrons and holes are simultaneously injected into the active layer. After this study, many researches have been reported and some the enhancement in luminescence efficiency was demonstrated by scaling down the channel length in unipolar devices. However, the external quantum efficiency has been still very low and needs to be improved for

practical applications. For this purpose, it is necessary to use organic materials with both efficient electroluminescence and transistor characteristics. A promising approach to combine high emission efficiency and good transistor characteristics in OLETs has been reported [61]. In this work, it was shown that by doping active layer, the field-effect characteristics of the OLETs are maintained and the electroluminescence quantum efficiency of the OLET reached 0.8%. In addition, using metals for source and drain electrodes that have a work-function more suitable for holes and electrons injection showed [62, 63] a clear increase of the light-emission efficiency.

Ambipolar transport is a desirable feature for organic semiconductors as it enables the fabrication of complementary logic circuits such as CMOS transistors with in a single device with a single active layer [64]. Moreover, the ambipolar transport can maximize the exciton recombination through electron—hole balance. In ambipolar active layer, the position of the recombination region and resulting emission zone can be tuned by the gate voltage [65]. As a consequent, the exciton quenching is minimized and therefore it will lead to improved internal and external quantum efficiency of the OLETs. However, few materials possesses the high electroluminescence characteristics with high and balanced ambipolar mobility. As alternative approaches, therefore, the methods of the bilayer structure and the use of heterojunction have been suggested to achieve the high ambipolar transport in OLETs.

The bulk heterojunction approach, commonly applied to to LEDs, solar cells and FETs, was adopted for ambipolar OLETs by blending two materials of n-type and p-type. The most important requirement for the two materials used for heterojunction is that the relative positions of their highest occupied molecular orbitals (HOMO) and the LUMO must allow exciton formation and recombination in the material with the smaller energy gap.

The bilayer approach have exhibited the highest balanced mobility values in ambipolar OLET devices so far. Particularly, two groups have shown that in a polymer-based ambipolar light-emitting transistor the emission zone can be moved across the transistor channel on changing the gate bias [66]. In those cases with high opto-electrical performances, a low work-function metal for the electron injection electrode and of a high work-function metal for the hole-injection electrode is used. In addition, the dielectrics with less trap density were selected as the gate insulator to avoid the charge trapping at the interfaces. The observation of a spatially resolved recombination zone, whose location in the transistor channel is controlled by the gate voltage, suggests that the coexistence of electron and hole channels, and therefore the ambipolar transport of both charges actually occurs. The recombination zone is located at the center of the channel when the current of electrons and that of holes are balanced.

However, the spatial separation of the electron-transport layer and the hole-transport layer drastically reduces the probability of electrons and holes meeting to form excitons inside the device channel. In addition, the low mobility values and unbalanced mobility for holes/electrons is remains as the drawback of the ambipolar polymer-based light-emitting transistors.

Very recently, a tri-layer structure consisting of an emission layer sandwiched between an electron- and hole- transporting layer, similar to the conventional OFET configuration, is appeared (Figure 2.7) [67]. Trilayer OLET devices have demonstrated EQE values as large as 5%, outperforming the OLED with the same emission layer and optimized transport layers (2.2%). According to that research, the high value of EQE is achieved by the tri-layers of active layer structure, which enables the effective suppression of essential losses such as the the metal-exciton quenching, the charge-exiction quenching, and the charge-metal quenchings in the channels. Moreover, in the ambipolar operation mode ( $V_{\rm DS}$  = -100 V and  $V_{\rm GS}$  = -30

V) the light-emitting region is located far from the drain electrodes at a distance of 8 µm, thus preventing photon losses due to exciton-metal quenching. For the transported charges to be effectively transported into the central emission layer, the LUMO level of the n-type transport layer should be similar to the LUMO level of the emission layer and the HOMO level of the p-type transport layer should be aligned with the HOMO level of the emission layer. That is, it is essential for the trilayer structure to enable to transport the injected charges into the central emission layer. Moreover, in order to accomplish the high field-effect mobility in the transport layers together with the high recombination rate and internal quantum efficiency, the optimization of the interface morphology between the organic layers is strongly required. However, all of above mentioned OLETs constructed in planar geometry have experienced narrow light-emission zone.

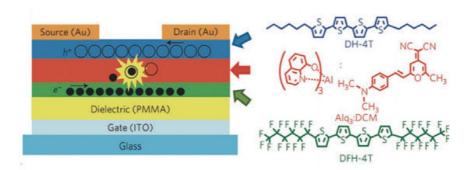

**Figure 2.7.** Schematic of the trilayer OLET with the chemical structure of each OSC, and the processes of charge transport and light-generation. (Ref. [67])

### 2.4.2. Vertical organic light-emitting transistors

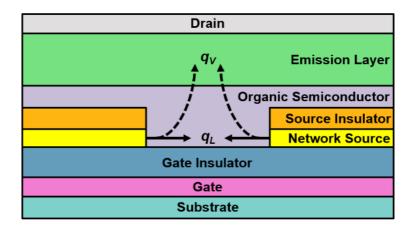

As discussed in previous section, the planar geometry of OLETs exhibits lineor band-type light-emission, which significantly reduces aperture ratio of OLETs. Therefore, from the viewpoint of expanding the area of light-emission in device with improved electrical characteristics, vertical OLETs have attracted great attention. In the vertical OLETs, the source electrode and the drain electrode is vertically located and the layers of OSCs are located between the two electrodes. Therefore, the short channel length can be easily achieved without additional patterning techniques, resulting in the high speed operation at low voltage. In a vertical architecture, typically a source electrode with periodic vacancies or perforated electrodes [68] and interdigitated electrodes [69] have been used. In those cases, the electric field should be precisely controlled through the vacancies of the source electrode by the gate electrode. As shown in Figure. 2.8, the flow of charge transport can be categorized in two flows: the first flow is lateral charge flow  $(q_L)$ , which the injected charges from the source electrode flow laterally along the channel area by the gate voltage. The second flow is the vertical charge flow  $(q_V)$ , which the injected charges moves into the emission layer by the drain voltage. Here, the degree of  $q_V$  is governed by the space-charge limited current [70] and is directly propositional to the degree of charge recombination in emission layer for light emission. Since the charge recombination and the resultant light emission are primarily governed by the pathway as well as the magnitude of  $q_L$  and  $q_V$  from each side of the aperture, the geometrical dimension of the aperture and the thickness of each layer play critical roles on the light emission characteristics including the emission zone and the spatial distribution around the aperture boundary.

**Figure 2.8.** Cross-sectional view of a VOLET with a network source electrode having periodic apertures. The lateral charge flow  $(q_L)$  and the vertical charge flow  $(q_V)$  are depicted as solid and dashed arrows, respectively. (Ref. [68])

# Chapter 3. Ambipolar-type Charge Transport of Organic Field-Effect Transistors in Dual-Gate Configuration

### 3.1. Introduction

Ambipolar-type organic field-effect transistors (OFETs) have been extensively studied for understanding the charge transport phenomena [18] and developing organic electronic devices such as light-emitting devices [71] and complementary integrated circuits [72]. An active, organic semiconductor (OSC) layer is one of the most critical ingredients in ambipolar-type OFETs, and generally consists of a single OSC (Figure 3.1 (a)) [71, 73] or a blend of two different OSCs (Figure 3.1. (b)) [74, 75]. The two cases often encounter with the unbalanced energy barrier and/or high channel resistance from the viewpoints of the charge injection and transport.

To simultaneously improve the injection and the transport of charges in the ambipolar OFETs by structural approach other than the OSC materials used, the device architectures using two stacked OSC layers in single gate configuration, as shown in Figure 3.1 (c), have been demonstrated to balance the carrier mobility and to improve the crystalline structure of each OSC layer [76, 77]. However, in a single gate configuration, the charge control scheme is still limited. For example, for the current flow from one of two OSCs either in the n-type or the p-type operation, the other OSC acts as an additional insulator or a channel of undesired charge carriers. This leads directly to a low on/off current ratio of an ambipolar-type OFET.

**Figure 3.1.** Device structures of various ambipolar OFETs with (a) single OSC (b) blended OSC, and (c) bilayer OSCs.

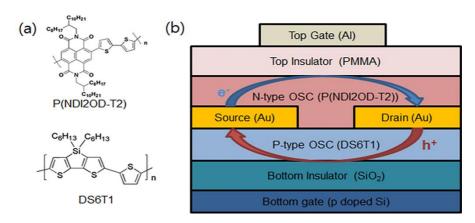

In this work, I present the ambipolar properties of a dual-gate OFET with two OSC-insulator interfaces stacked together [78]. Two active layers of an n-type and a p-type OSCs were stacked between two gate insulator-electrode pairs. In my ambipolar-type OFET structure, the bottom gate insulator-bottom OSC interface was involved in the channel for the p-type operation and the top gate insulator-top OSC interface in the channel for the n-type operation. A combination of two gate voltages from two separated, bottom and top electrodes enables to efficiently control the corresponding charge carriers for the enhancement of the mobility and the on/off current ratio in the ambipolar operation.

# 3.2. Fabrication of ambipolar-type organic field-effect transistors

A schematic diagram of my ambipolar dual-gate OFET is shown in Figure 3.2. A heavily doped p-type Si substrate was used as a bottom gate electrode and a 300 nm-thick SiO<sub>2</sub> layer was served as the bottom gate insulator. The Si/SiO<sub>2</sub> substrate was cleaned with acetone, isopropyl alcohol, methanol, and deionized water in series for 10 min each under ultra-sonication. The cleaned Si/SiO<sub>2</sub> substrate was subsequently exposed to UV-ozone for 10 min and then spin-coated with hexamethyldisilazane (HMDS) as a buffer layer at 3000 rpm for 30 sec and rinsed to obtain a monolayer. A p-type OSC, poly(4,4-di-n-hexyldithienosilole-alt-(bi)thiophene) (DS6T1 or P1200) dissolved in dichlorobenzene (DCB) in 1 wt.%, was spin-coated at 2000 rpm for 30 sec, followed by annealing at 70°C for the removal of the solvent and thickness was measured as 60 nm [79]. The source and drain electrode were prepared with 50-nm-thick Au which was thermally deposited. Using a shadow mask, the channel length and the channel width were defined to be 150 μm and 1 mm, respectively. An n-type OSC, poly{[N,N9-bis(2-octyldodecyl)naphthalene-1,4,5,8-bis(dicarboximide)-2,6-diyl]-alt-5,5-(2,29-bithiophene)} [P(NDI2OD-T2) or N2200] dissolved in p-xylene in 1 wt.%, was spin-coated at 2000 rpm for 30 sec and subsequently baked at 110°C for 6 hr in a vacuum dry oven, of which thickness was 60 nm. The top gate insulator was prepared using poly(methyl methacrylate) (PMMA), dissolved in ethyl acetate in 8 wt.%, by spin-coating at 3000 rpm for 30 sec and annealed at 100°C for 1 hr. The thickness of the PMMA film was about 1.8 µm. The top gate electrode was made of 50-nm-thick Al. All the electrical characteristics of my ambipolar OFET were measured using a semiconductor analyzer (HP 4155A) at room temperature under ambient condition.

**Figure 3.2.** Device structure of an ambipolar-type OFET with dual-gate, two-stacked OSCs, which has two OSC/metal interfaces for corresponding two separate channels.

# 3.3. Experimental results and discussions

### 3.3.1. Electrical characteristics in single gate configuration

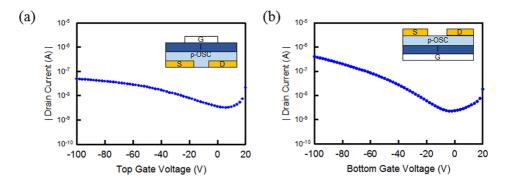

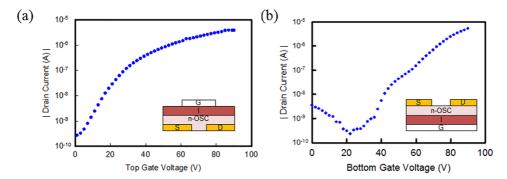

I first measure the unipolar characteristics of both the n-type and the p-type OSCs in conventional top- and bottom-gate OFETs with single OSC-insulator interfaces (SIs) to optimize the stacking sequence of two OSC-insulator pairs. Figure 3.3 show the transfer characteristics of the OFETs with P1200 and Figure 3.4 show those with N2200 in the top- and bottom-gate geometries, respectively.

The measured mobility of the SI-OFET with P1200 was about  $4.7 \times 10^{-4}$  cm<sup>2</sup>/Vs in the top-gate geometry from Figure 3.3(a) and  $1.3 \times 10^{-3}$  cm<sup>2</sup>/Vs in the bottom-gate geometry from Figure 3.3(b). The mobility for the N2200 case was  $6.4 \times 10^{-2}$  cm<sup>2</sup>/Vs in the top-gate geometry from Figure 3.4(a) and  $1.7 \times 10^{-2}$  cm<sup>2</sup>/Vs in the bottom-gate geometry from Figure 3.4(b). As a consequence, a bottom-gate geometry for the p-type operation (P1200) and a top-gate geometry for the n-type operation (N2200) are desirable in an ambipolar OFET. This is also hinted by the facts that for the p-type operation, less charge traps are produced at the P1200-SiO<sub>2</sub> interface than the P1200-PMMA interface and N2200 shows the high molecular regionegularity as well as the electronic structure suitable for the n-type operation [80, 81].

**Figure 3.3.** Transfer curves of SI-OFETs having OSC layer of P1200 in the (a) top gate configuration and (b) bottom gate configuration with single gate electrode. (Ref. [78])

**Figure 3.4.** Transfer curves of SI-OFETs having OSC layer of N2200 in the (a) top gate configuration and (b) bottom gate configuration with single gate electrode.

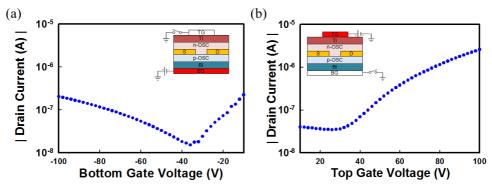

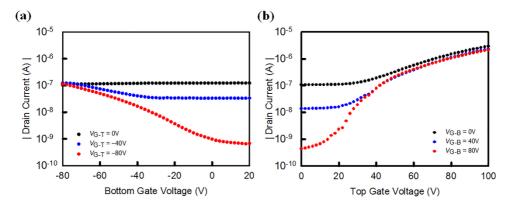

### 3.3.2. Electrical characteristics in dual-gate configuration