#### 저작자표시-비영리-변경금지 2.0 대한민국

#### 이용자는 아래의 조건을 따르는 경우에 한하여 자유롭게

• 이 저작물을 복제, 배포, 전송, 전시, 공연 및 방송할 수 있습니다.

#### 다음과 같은 조건을 따라야 합니다:

저작자표시. 귀하는 원저작자를 표시하여야 합니다.

비영리. 귀하는 이 저작물을 영리 목적으로 이용할 수 없습니다.

변경금지. 귀하는 이 저작물을 개작, 변형 또는 가공할 수 없습니다.

- 귀하는, 이 저작물의 재이용이나 배포의 경우, 이 저작물에 적용된 이용허락조건 을 명확하게 나타내어야 합니다.

- 저작권자로부터 별도의 허가를 받으면 이러한 조건들은 적용되지 않습니다.

저작권법에 따른 이용자의 권리는 위의 내용에 의하여 영향을 받지 않습니다.

이것은 이용허락규약(Legal Code)을 이해하기 쉽게 요약한 것입니다.

#### Ph.D. DISSERTATION

# Methodology for Solving Timing Closure Problem by Utilizing Adjustable Delay Clock Buffers

가변 지연 시간 클락 버퍼 활용을 통한 타이밍 일치 문제 해결 방법론

BY

JUYEON KIM

FEBRUARY 2018

DEPARTMENT OF ELECTRICAL ENGINEERING AND

COMPUTER SCIENCE

COLLEGE OF ENGINEERING

SEOUL NATIONAL UNIVERSITY

#### Ph.D. DISSERTATION

# Methodology for Solving Timing Closure Problem by Utilizing Adjustable Delay Clock Buffers

가변 지연 시간 클락 버퍼 활용을 통한 타이밍 일치 문제 해결 방법론

BY

JUYEON KIM

FEBRUARY 2018

DEPARTMENT OF ELECTRICAL ENGINEERING AND

COMPUTER SCIENCE

COLLEGE OF ENGINEERING

SEOUL NATIONAL UNIVERSITY

# Methodology for Solving Timing Closure Problem by Utilizing Adjustable Delay Clock Buffers

가변 지연 시간 클락 버퍼 활용을 통한 타이밍 일치 문제 해결 방법론

> 지도교수 김 태 환 이 논문을 공학박사 학위논문으로 제출함 2017년 11월

> > 서울대학교 대학원 전기 컴퓨터 공학부 김 주 연

김주연의 공학박사 학위 논문을 인준함 2017년 12월

| 위원정  | <b>:</b> |

|------|----------|

| 부위원정 | :        |

| 위 원  | :        |

| 위 원  | :        |

| 위 원  | :        |

**Abstract**

As clock timing is closely related to the performance of synchronous systems,

many synthesis techniques were suggested to optimize clock distribution networks.

Especially, meeting clock skew constraints is one of the most important objectives that

should be achieved for successful operation of the design. Meanwhile, multiple power

mode designs made the clock timing problem harder to tackle due to the dynamic delay

change caused by varying supply voltages. Inserting adjustable delay buffers (ADBs)

on the clock tree and controlling its delay can be a solution to the problem. However,

because ADBs require non-negligible area and control overhead, it should be carefully

inserted to minimize the number of ADBs. This work provides solutions to the ADB

minimization problem under the environment of multiple power modes in which the

clock path delay varies as power mode changes. Precisely, (1) an  $O(n \log n)$  time al-

gorithm that optimally solves the problem under clock skew bounds and (2) a graph

based algorithm which supports useful skew scheduling are proposed, along with (3)

their practical extensions, such as supporting discrete delay values and reducing more

ADBs by integrating buffer sizing scheme. The experimental results showed that pro-

posed ADB allocation algorithms under constant clock skew bound and useful skew

constraints allocated 13.5% and 23.3% less number of ADBs on average, respectively,

compared to the best known ADB allocation algorithm under the same constraints.

keywords: ADB, clock network design, multiple power mode, clock skew

**student number**: 2013-20776

i

# **Contents**

| Al | ostrac  | et e e e e e e e e e e e e e e e e e e      | i  |

|----|---------|---------------------------------------------|----|

| Co | onten   | ts                                          | ii |

| Li | st of ' | Tables                                      | iv |

| Li | st of ] | Figures                                     | v  |

| 1  | INT     | RODUCTION                                   | 1  |

|    | 1.1     | Introduction                                | 1  |

|    | 1.2     | Contributions of This Dissertation          | 2  |

| 2  | BAC     | CKGROUND                                    | 4  |

|    | 2.1     | Multiple Power Mode Design                  | 4  |

|    | 2.2     | Setup Time and Hold Time Constraints        | 5  |

|    | 2.3     | Clock Skew Optimization Objectives          | 8  |

|    | 2.4     | Adjustable Delay Buffers                    | 9  |

| 3  | TIM     | IING CLOSURE IN MULTIPLE POWER MODE DESIGNS | 11 |

|    | 3.1     | ADB Allocation for Timing Correction        | 11 |

|    | 3.2     | Problem Definitions                         | 12 |

| 4  | ADI     | B ALLOCATION UNDER CLOCK SKEW BOUND         | 15 |

|    | 4.1     | Related Works and Motivational Examples     | 15 |

| Al | ostrac | et (In Ko                                            | orean)                                                               | 99 |  |

|----|--------|------------------------------------------------------|----------------------------------------------------------------------|----|--|

| 6  | CO     | NCLUS                                                | ION                                                                  | 91 |  |

|    | 5.6    | Experi                                               | mental Results                                                       | 81 |  |

|    | 5.5    | Proper                                               | ty Proofs of the Proposed Algorithm                                  | 74 |  |

|    |        | 5.4.4                                                | Supporting Bounded ADB Delay                                         | 71 |  |

|    |        | 5.4.3                                                | Supporting Discrete ADB Delay                                        | 67 |  |

|    |        | 5.4.2                                                | Handling Scalability Problem                                         | 65 |  |

|    |        | 5.4.1                                                | Acceleration for Extracting Positive Cycles in $G \ \ldots \ \ldots$ | 60 |  |

|    | 5.4    | Extens                                               | ions                                                                 | 60 |  |

|    | 5.3    | ADB A                                                | Allocation Algorithm Utilizing Useful Skew                           | 54 |  |

|    | 5.2    | Observ                                               | vations                                                              | 48 |  |

|    | 5.1    | Relate                                               | d Works and Motivational Examples                                    | 44 |  |

| 5  | ADI    | 3 ALLC                                               | OCATION UNDER USEFUL SKEW                                            | 44 |  |

|    | 4.5    | Experi                                               | mental Results                                                       | 36 |  |

|    | 4.4    | Optima                                               | ality Proofs of the Proposed Algorithm                               | 27 |  |

|    |        | 4.3.2                                                | Integration of Buffer Sizing                                         | 25 |  |

|    |        | 4.3.1                                                | Supporting Discrete ADB Delay                                        | 23 |  |

|    | 4.3    | Extens                                               | ions                                                                 | 23 |  |

|    | 4.2    | ADB Allocation Algorithm Satisfying Clock Skew Bound |                                                                      |    |  |

# **List of Tables**

| 4.1 | Notations used in ADB-PULLUP                                       | 18 |

|-----|--------------------------------------------------------------------|----|

| 4.2 | Benchmark circuits used in the experiment                          | 36 |

| 4.3 | Comparison of results produced by ADB-ESYNC [1], ADB-PULLUP        |    |

|     | and ADB-PULLUP-B                                                   | 37 |

| 4.4 | Comparison of results produced by ADB-ESYNC-Q [1], ADB-PULLUP-     |    |

|     | Q and ADB-PULLUP-QB                                                | 38 |

| 5.1 | Benchmark circuits used in the experiment                          | 82 |

| 5.2 | Comparison of results produced by ADB-LP [2] that considers useful |    |

|     | skew scheduling, our ADB-UCP without allowing timing violations .  | 83 |

| 5.3 | Comparison of results produced by ADB-LP [2] that considers useful |    |

|     | skew scheduling, our ADB-UCP allowing timing violations            | 84 |

| 5.4 | The number of ADBs allocated by ADB-UCP on ISCAS'89 s38417,        |    |

|     | s 38584 and s 35932 with varying values of $limit$                 | 85 |

| 5.5 | Runtime and the number of iterations of ADB-UCP on ISCAS'89        |    |

|     | s 38417, s 38584 and s 35932 with varying values of $limit$        | 86 |

| 5.6 | The number of ADBs allocated by ADB-UCP-Q, under different set-    |    |

|     | tings of quantization resolution                                   | 87 |

| 5.7 | The number of ADBs allocated by ADB-UCP-LM, under different        |    |

|     | settings of delay upper limit                                      | 88 |

# **List of Figures**

| 2.1 | In multiple power mode design, applied voltage for each voltage island         |    |

|-----|--------------------------------------------------------------------------------|----|

|     | varies depending on the operating mode                                         | 5  |

| 2.2 | Timing waveforms showing three cases of flip-flop input timing, where          |    |

|     | timing constraints are satisfied, setup time constraint is violated, and       |    |

|     | hold time constraint is violated, respectively                                 | 6  |

| 2.3 | A datapath $Ckt_{i,j}$ from flip-flop $s_i$ to $s_j$ in a synchronous circuits | 7  |

| 2.4 | The implementation structure of a capacitor bank based ADB [3]                 | 10 |

| 3.1 | An example of clock tree ${\mathcal T}$ with the replacement of a clock buffer |    |

|     | with ADB under bounded clock skew constraint                                   | 13 |

| 4.1 | A motivational example for ADB allocation and delay assignment. (a)            |    |

|     | A clock tree with three ADBs allocated by the method of [1] to resolve         |    |

|     | clock skew violation. (b) An optimal allocation which uses one ADB.            | 17 |

| 4.2 | Example showing step-by-step procedure of ADB-PULLUP                           | 21 |

| 4.3 | The flow of ADB-PULLUP                                                         | 24 |

| 4.4 | An example of executing modified READJUST function to handle dis-              |    |

|     | crete ADB delays                                                               | 25 |

| 4.5 | An example of clock tree that belongs to ADB-unsolvable when clock             |    |

|     | skew bound $\kappa = 10. \dots \dots \dots \dots \dots \dots$                  | 29 |

| 4.6 | The overall sketch of our optimality proof                                     | 34 |

| 4.7  | Comparison of the numbers of ADBs allocated and runtime of ADB-                                  |    |

|------|--------------------------------------------------------------------------------------------------|----|

|      | PULLUP-Q, optimal exhaustive algorithm, and ADB-PULLUP-QB                                        | 40 |

| 4.8  | The changes of the average number of ADBs used by ADB-ESYNC                                      |    |

|      | and ADB-PULLUP by varying the number of power modes used                                         | 41 |

| 4.9  | Runtime of ADB-ESYNC [1], ADB-ESYNC-Q [1], ADB-PULLUP,                                           |    |

|      | ADB-PULLUP-Q, ADB-PULLUP-B, and ADB-PULLUP-QB                                                    | 42 |

| 5.1  | An example of clock tree $T$ with the replacement of clock buffers with                          |    |

|      | ADBs to meet the clock skew constraints. (a) A clock tree with two                               |    |

|      | ADBs allocated to satisfy the bounded clock skew constraint. (b) Use-                            |    |

|      | ful clock skew leads to allocate only one ADB while meeting the setup                            |    |

|      | time constraint.                                                                                 | 46 |

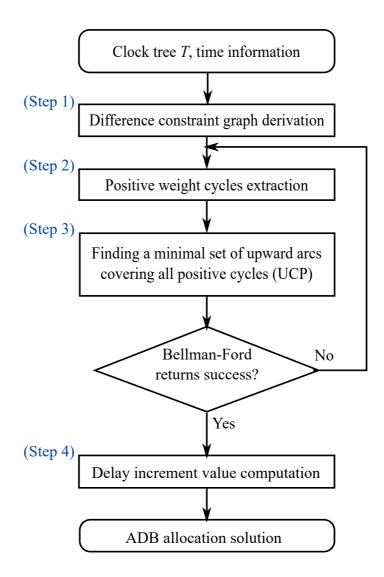

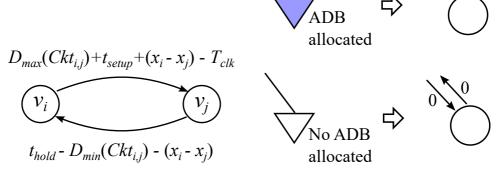

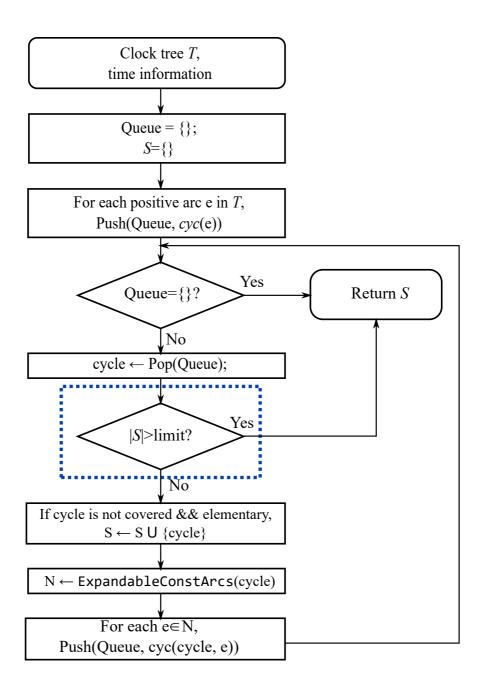

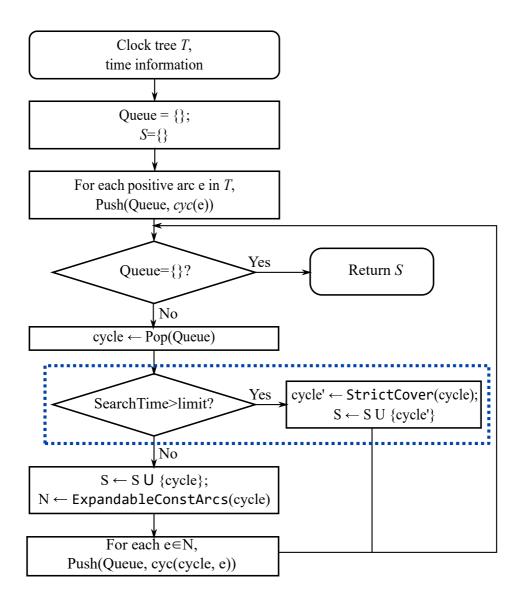

| 5.2  | A flow diagram showing the process of the proposed algorithm                                     | 49 |

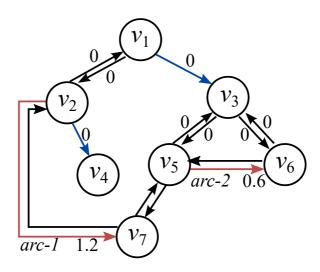

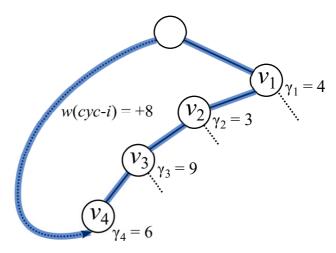

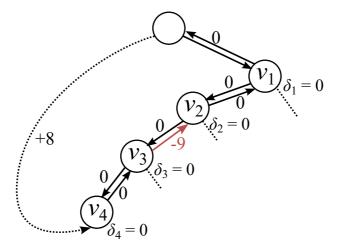

| 5.3  | Derivation of a time difference constraint graph from a clock tree $\ensuremath{\mathcal{T}}.$ . | 51 |

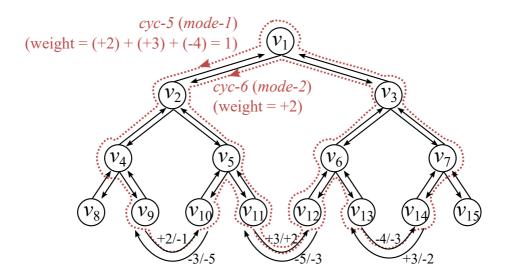

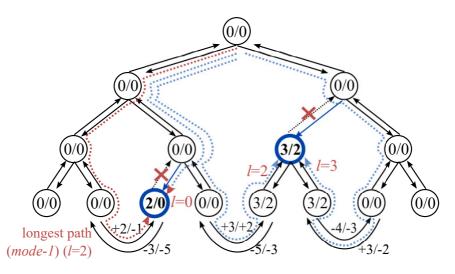

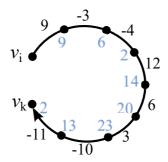

| 5.4  | An example illustrating the steps of ADB-UCP                                                     | 58 |

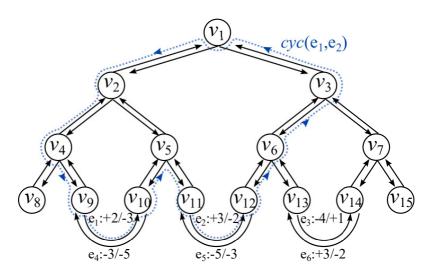

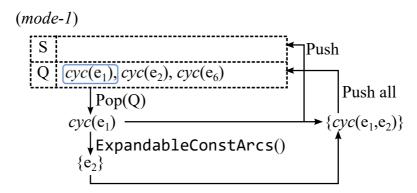

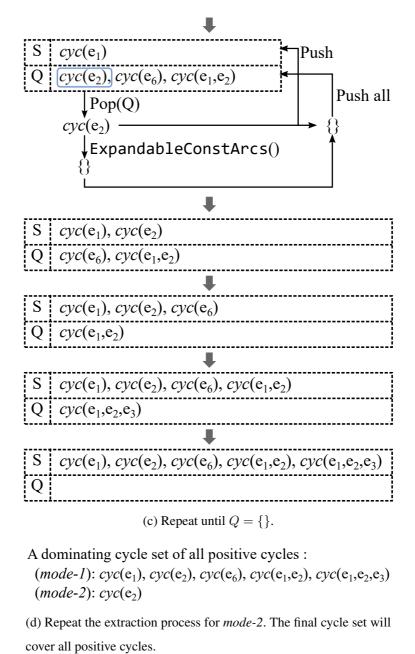

| 5.5  | Flow diagram of incrementally generating a dominating cycle set $\mathcal{S}_{\cdot}$ .          | 62 |

| 5.6  | An example of systematic extraction of a dominating cycle set                                    | 64 |

| 5.7  | Finding a set of upward arcs who covers all positive cycles that can be                          |    |

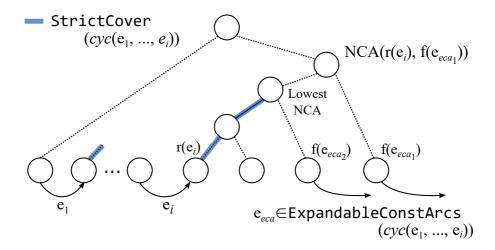

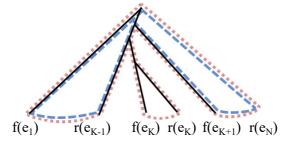

|      | found by expanding $cyc(e_1,\cdots,e_i)$                                                         | 66 |

| 5.8  | Flow diagram of incrementally generating a dominating cycle set with                             |    |

|      | the hard constraint on the number of iteration                                                   | 68 |

| 5.9  | An example of delay quantization procedure under arbitrarily given                               |    |

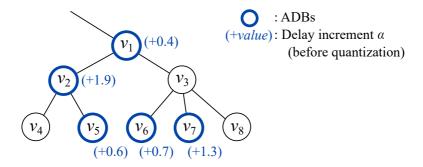

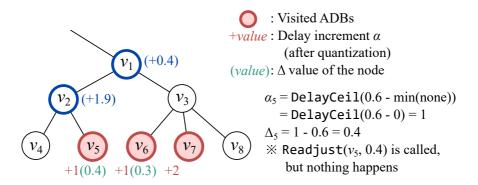

|      | delay increment values                                                                           | 70 |

| 5.10 | An example showing how ADBs with range $[0,\gamma]$ of delay increments                          |    |

|      | are supported by ADB-UCP                                                                         | 73 |

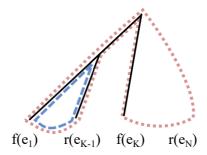

| 5.11 | A diagram showing the dominance relationship between cycles, when                                |    |

|      | $l(NCA(f(e_1), r(e_{K-1}))) \ge l(NCA(r(e_{K-1}), f(e_K)))$                                      | 78 |

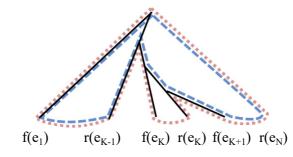

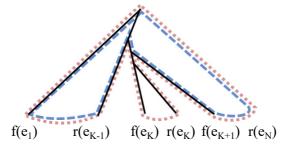

| 5.12 | Diagrams showing the dominance relationship between cycles, when |    |

|------|------------------------------------------------------------------|----|

|      | $l(NCA(f(e_1), r(e_{K-1}))) < l(NCA(r(e_{K-1}), f(e_K)))$ and    |    |

|      | $l(NCA(f(e_K), r(e_K))) \ge l(NCA(r(e_{K-1}), f(e_K)))$          | 79 |

| 5.13 | An example of strongly positive path                             | 80 |

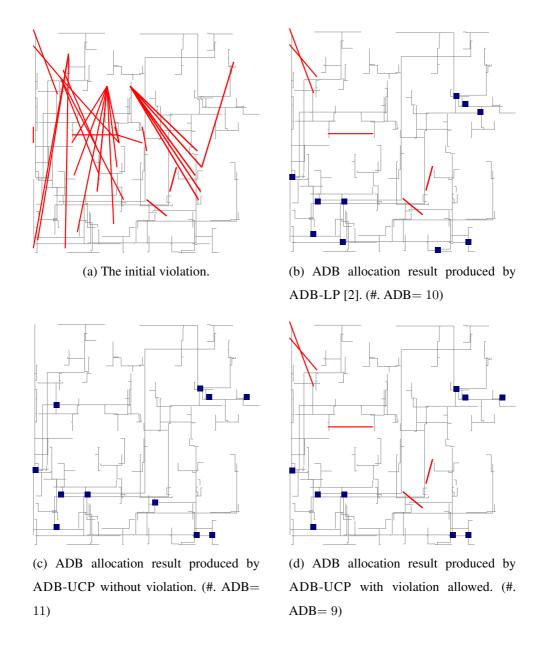

| 5.14 | ADB allocation result on ISCAS'89 \$15850 design                 | 90 |

# Chapter 1

#### INTRODUCTION

#### 1.1 Introduction

Clock is a periodic signal which triggers the state transition of synchronous systems. It is one of the most important signals of synchronous digital systems, as all the operation of synchronous components such as flip-flops and latches rely on it. To prevent the timing failure of the design, the clock signal should arrive at its sinks at the accurate time. However, the increasing demands on integrated circuit (IC) chip performance are reducing the timing margin and making the clock design problem more challenging.

Clock signal is distributed to the whole components in the chip through clock distribution networks (CDNs), such as clock trees, clock meshes and clock spines. Clock tree is a tree-structured CDN, whose root corresponds to clock source and has clock sinks as its leaf nodes. Because it requires less resource on implementation and timing analysis is relatively simple, the clock tree structure is widely used so that synthesizing and optimizing clock trees has been one of the most important issues in VLSI design. The research on clock tree synthesis and optimization can be roughly classified into two directions: generating clock tree structures or topologies (e.g., [4–9]) and optimizing them for better timing quality (e.g., [10–16]). One common assumption of these prior works is that the developed clock network should be applied to single power

mode designs, in which every design module operates in a single or global supply voltage.

However, as minimizing power consumption is one of the important design concerns, the design paradigm is shifting to multiple power mode designs, in which a design module can operate in different supply voltages on the different power modes. Multiple power mode design is very helpful for saving power consumption, but meeting the time constraints for every power mode by controlling the arrival times of clock signal becomes much more difficult because clock buffer delays vary depending on the power modes.

Meanwhile, inserting **Adjustable Delay Buffers** (ADBs) enables dynamic delay tuning by which the clock timing problem caused by the voltage change can be dealt with. The delay of an ADB is adjusted by its control inputs, thus the clock arrival times at each clock sink can be tuned during the operation. The idea of using ADBs in multiple power modes is to replace some of normal clock buffers with ADBs and control their delays by dynamically changing control inputs, so that the clock skew constraints on each power mode can be met [17].

The main drawback of inserting ADBs on clock tree is that it requires non-negligible area overhead. Thus, minimizing the number of ADBs to be inserted is the most essential problem to be solved for resolving timing violations of multiple power mode designs at a reasonable cost. This work provides a complete solution to the ADB minimization problem, which corrects timing violations in multiple power mode design with the minimum number of ADBs allocated.

#### 1.2 Contributions of This Dissertation

In this dissertation, the methods of ADB allocation and delay assignment are proposed to optimize the area utilization while resolving the clock skew variation problem in multiple power mode designs.

- In Chapter 4, an O(n log n) time algorithm that optimally solves the problem of minimizing the number of ADBs to be allocated under the given clock skew bound is proposed. It includes the extended version of the algorithm that supports the use of ADBs which have discrete delays, and replacing the ADBs with various sizes of buffers to reduce the area further.

- In Chapter 5, a graph based algorithm solving the problem with useful skew scheduling is proposed, along with the acceleration techniques to trade-off runtime and quality of the result, and supporting discrete or bounded delay values of ADBs.

The outcomes of this work will enable the use of ADBs with small overhead, and they can also be applied usefully to the diverse environments, such as non-uniform thermal effect, in which the clock skew varies dynamically during the operation.

# Chapter 2

#### **BACKGROUND**

### 2.1 Multiple Power Mode Design

One of the most efficient way of reducing power is to lessen the supply voltage for the design when high performance is not required [18,19]. Reducing the voltage levels depending on the tasks on operation, called dynamic voltage scaling, cannot only be applied in global chip level, but also for smaller units called voltage islands.

Multiple power mode design is a design strategy that exploits the advantage of dynamic voltage scaling in higher resolution. If some modules in a design have less tasks to do, applying low voltage to them will be more effective than applying high voltage for the whole circuit only for few modules that should have higher performance. In multiple power mode design, the circuit is divided into several voltage islands and different voltages are applied for each voltage island depending the operating mode. For instance, some tasks would require more computations in microprocessor unit, while the others would use digital signal processor more. Then, in each operating mode, the modules with heavy load use high voltage and the others use low one.

The drawback of this method is that the delay of clock buffers are also affected by the applied voltage. As two clock paths might cross different voltage domains, the relative clock arrival times on their sinks will vary depending on the operating modes.

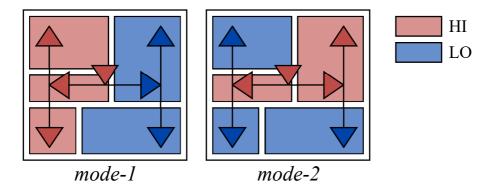

Figure 2.1: In multiple power mode design, applied voltage for each voltage island varies depending on the operating mode.

As a result, the circuit suffers from timing violations [20,21]. In Figure 2.1, the voltage level of each voltage island shifts from high to low, considering the operation speed required in the current mode. Then, the clock buffers operate under the voltage applied on voltage islands they locate, so that the clock arrival times on sinks cannot maintain their values as the power mode changes.

## 2.2 Setup Time and Hold Time Constraints

Time constraints describe the conditions which prevent the circuit from the timing failures. Especially, arrival time of clock events on synchronous components is one of the most important concerns to be considered for the timing closure. The input signal of a flip-flop in a synchronous circuit should be held steady before and after the clock event, to ensure the correct data being captured. The minimum duration of time that the input should be stable before and after the clock arrival is called setup time and hold time, respectively.

Thus, the timing failures in synchronous circuits can be classified into two situations, the valid input data not being able to arrive until the point capturing starts, and the data of the next cycle affecting the input before the capturing finishes. Figure 2.2

shows the timing waveforms at clock and data input pin of a flip-flop. The data input in Case 1 becomes stable at the latest setup time before the clock arrival, and retain stability until hold time after the clock. In this case, the flip-flop successfully stores the correct data. On the other hand, the input signals in Case 2 and Case 3 are not stable during the timing interval defined by setup time and hold time of the flip-flop, causing the timing violations. Each situation is called setup time violation and hold time violation.

Figure 2.2: Timing waveforms showing three cases of flip-flop input timing, where timing constraints are satisfied, setup time constraint is violated, and hold time constraint is violated, respectively.

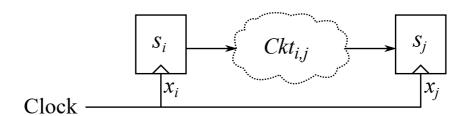

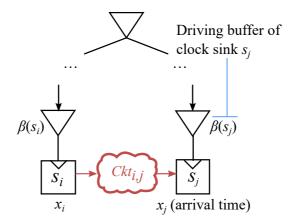

In circuit designs, the input data of flip-flops usually change depending on the output of the flip-flops connected through combinational logic cells. This implies that any pair of related flip-flops should be checked whether timing violations occur, to keep the circuit safe from the timing hazards. Figure 2.3 shows a pair of flip-flops,  $s_i$  and  $s_j$ , of a synchronous system. The maximum delay from the clock input of  $s_i$  to the data input of  $s_j$  is  $D_{i,j}^{max}$  and the minimum is  $D_{i,j}^{min}$ . (The notation  $D_{i,j}^{max}$  and  $D_{i,j}^{min}$  in this paper includes the clock-to-Q delay of  $s_i$ , which is the time interval from the clock arrival on the clock pin and to the data launch from the data output pin.) Then,

the interval in which data signal at the input pin of  $s_j$  is reliable begins at the time  $D_{i,j}^{max}$  elapsed from the data launch, and ends at the time  $D_{i,j}^{min}$  after the next clock arrival at  $s_i$ .

Figure 2.3: A datapath  $Ckt_{i,j}$  from flip-flop  $s_i$  to  $s_j$  in a synchronous circuits.

To ensure the data signal arrives at the time it is required, in other words, to prevent setup time violation,  $x_i$  and  $x_j$ , the clock arrival time of  $s_i$  and  $s_j$ , should satisfy the following inequality:

$$x_i + D_{i,j}^{max} \le x_j + T_{clk} - t_{setup,j} \tag{2.1}$$

where  $T_{clk}$  is the clock period and  $t_{setup,j}$  is the setup time of  $s_j$ . Likewise, to prevent hold time violation, the data of the next cycle should not affect the current data capture. Thus, the following inequality:

$$x_i + D_{i,j}^{min} \ge x_j + t_{hold,j} \tag{2.2}$$

is also needed to be met. The former constraint is called *setup time constraint*, and the latter is called *hold time constraint*. Each constraint can be transformed as:

$$x_j - x_i \ge D_{i,j}^{max} - T_{clk} + t_{setup,j}$$

$$\tag{2.3}$$

and

$$x_i - x_j \ge -D_{i,j}^{min} + t_{hold,j}. (2.4)$$

The latter form of time constraints (Equation (2.3) and Equation (2.4)) will be used in this paper since we will consider only the difference between clock arrival times in this paper.

# 2.3 Clock Skew Optimization Objectives

As the satisfaction of setup and hold time constraints depends on the clock arrival times, delivering the clock signal to clock sinks at the desired time has been one of the main concerns in synchronous digital system designs. The optimization of clock signal arrival times can be performed based on either one of the two objectives: (1) meeting or minimizing (global) clock skew bound and (2) maximizing the exploitation of useful clock skew [22].

Because clock skew of a pair of clock sinks is defined by a time difference between the clock arrival on each of them, *global clock skew* refers to the difference of the latest and earliest arrival times of a clock signal to flip-flops. In other words, global clock skew is the maximum clock skew among all pairs of clock sinks of the whole circuit. If no confusion occurs, the global clock skew is simply referred to as *clock skew* in this presentation. As circuits are usually designed assuming zero clock skew, the tighter the clock skew is, the more setup and hold time constraints are likely to be met. For this reason, achieving zero or bounded clock skew for clock distribution networks can be an effective solution of the timing optimization problem, especially when the design size is huge so that considering every relationship between clock sinks requires enormous design time and effort.

On the other hand, since the setup and hold time constraints are looser for some pairs of sinks than the others, it is beneficial to intelligently schedule the arrival times of clock signal to distribute timing margins in a way to satisfy all the timing constraints. For instance, given three flip-flops  $s_i$ ,  $s_j$  and  $s_k$  connected by combinational logics  $Ckt_{i,j}$  and  $Ckt_{j,k}$ , increasing the clock path delay on  $s_j$  adds more margin to the setup

constraint between  $s_i$  and  $s_j$ , and the hold constraint between  $s_j$  and  $s_k$ , and reduces the margin of the setup constraint between  $s_j$  and  $s_k$ , and the hold constraint between  $s_i$  and  $s_j$ . This method can be utilized to relax tight timing constraints in pipeline architecture by 'stealing' timing margin, called slack, from shorter datapaths and give them to longer ones. It is called *useful skew scheduling*. From the designers' point of view, the problem of optimizing clock networks under useful skew scheduling is more complicated than the one limiting clock skew bounded by constant values since the former is required to examine the satisfaction of all the setup and hold time constraints during the skew scheduling.

## 2.4 Adjustable Delay Buffers

Adjustable delay buffer (ADB) is a buffer whose delay can be adjusted depending on the control signal. ADBs have been suggested as a solution to process variation problem that can be adopted in post-silicon tuning stage [23–26]. However, rather than fixing the delay to a constant value, they can generate varying delays when dynamically changing control signal is assigned [17]. This strategy enables ADBs to solve the timing problem in multiple power mode design, by changing clock arrival times during the operation.

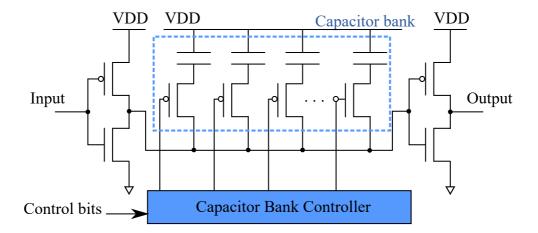

Figure 2.4 shows a structure of a capacitor bank based adjustable delay buffer implementation [3]. An ADB is composed of two inverters, one at the input port and the other at the output port, and an array of capacitors with switch transistors is connected between them. The switches are activated by a capacitor bank controller to change the number of active capacitors depending on the value of control bits. Activating more capacitors increases the total capacitance between the two inverters, which in turn increases the signal propagation delay between the input and output ports.

As the delay generation of an ADB relies on the MOS capacitors in the capacitor bank, the size of capacitor bank is directly proportional to the maximum delay of

Figure 2.4: The implementation structure of a capacitor bank based ADB [3]. The ADB delay is dynamically adjusted by turning on and off the individual capacitors in the bank.

ADB. Thus, the ADB cells necessarily occupy significantly larger area than those of the ordinary clock buffers, to generate a sufficient amount of delay to control the clock arrival times. It adds non-negligible area overhead to the circuit, so reducing the number of ADBs to be inserted is an essential topic to be dealt to efficiently tackle timing problems in multiple power mode designs.

# **Chapter 3**

# TIMING CLOSURE IN MULTIPLE POWER MODE DESIGNS

## 3.1 ADB Allocation for Timing Correction

While many optimization methods were effective, advanced low power design techniques introduced new challenges to the clock skew control problem. Specifically, for multiple power mode designs, where the supply voltage to the circuit components changes dynamically depending on modes, the clock arrival time also varies accordingly. Even though the previous works can consider the clock skew constraints on every power mode, it would be highly likely that the resulting clock tree uses a substantially long wirelength or there exists no clock tree that satisfies the clock skew constraint on every power mode.

Meanwhile, allocating ADBs on the clock tree and assigning control signals for each mode can intentionally increase the clock path delays passing them, in order to resolve the timing violations. The idea of using ADBs in multiple power modes is to replace some of normal clock buffers with ADBs so that the clock skew constraints on each power mode can be met; when the power mode changes during execution, for example from power mode *mode-1* to power mode *mode-2*, the delays of ADBs in

clock tree that have been adjusted under *mode-1* are readjusted to meet the clock skew constraints under *mode-2*.

The proposed clock timing correction flow is as follows. An initial clock tree is synthesized using ordinary clock buffers, which inevitably cause timing violations in multiple power mode. Based on the initial delays obtained by simulations under available power modes, the proposed algorithm finds the optimal set of clock buffers that should be replaced by ADBs. The algorithm also calculates the delay values that the ADBs should have in each mode, and converts them into the control signals. The calculation should take the change in applied voltage on ADBs in each power mode into account, to generate the intended delays in every case. The final ADB delay is implemented using a mode controller which stores and returns the calculated on/off signals to the capacitor bank of each ADB depending on the power mode.

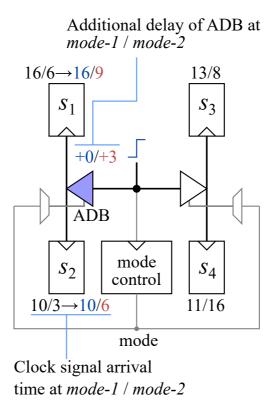

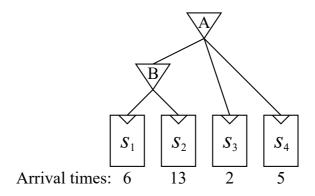

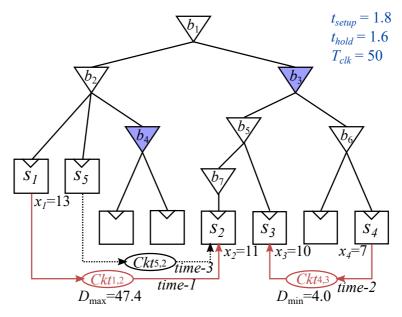

Figure 3.1 shows an example of clock tree  $\mathcal{T}$  that has four sinks  $s_1$ ,  $s_2$ ,  $s_3$ , and  $s_4$ . Assuming there are two power modes mode-1 and mode-2 in  $\mathcal{T}$ , the two numbers on each sink represent the clock signal arrival times to the sink on mode-1 and mode-2. With the clock skew bound of 10,  $\mathcal{T}$  has a clock skew violation between  $s_1$  and  $s_4$  in mode-2 if the ADB is not used. To solve this problem, an ADB replaces a buffer on left which drives  $s_1$  and  $s_2$ . The two numbers on ADB represent the values of delay increment in mode-1 and mode-2. Precisely, the ADB adds delay of 3 in mode-2, increasing the signal arrival time to  $s_2$  in mode-2 to 6. Then, all the clock skews are within bound of 10.

#### 3.2 Problem Definitions

Since ADBs add non-negligible area overhead to the circuit, minimizing the number of ADB cells to be allocated has been the most essential problem to solve for the effective use of ADBs. Meanwhile, as mentioned in Section 2.3, the clock timing optimization can have different kinds of objectives to eliminate the possibility of timing failure,

Figure 3.1: An example of clock tree  $\mathcal{T}$  with the replacement of a clock buffer with ADB under bounded clock skew (=10) constraint.

meeting the constant global clock skew bound and utilizing useful skew scheduling.

Thus, the ADB-based clock tree optimization problem can be described as:

**Problem 1** (ADB insertion problem under clock skew bound). Given a synthesized clock tree, arrival times of clock sinks in each power mode, and clock skew bounds  $\kappa_m$ , replace the least number of clock buffers with ADBs and assign delays to the ADBs to satisfy the bound  $\kappa_m$  in all power modes.

**Problem 2** (ADB insertion problem under useful skew). Given a synthesized clock tree, arrival times of clock sinks in each power mode, setup and hold time slacks, replace the least number of clock buffers with ADBs and assign delays to the ADBs to satisfy setup and hold time constraints in all power modes.

# **Chapter 4**

#### ADB ALLOCATION UNDER CLOCK SKEW BOUND

In this chapter, an optimal solution to Problem 1, the ADB insertion problem under constant clock skew bound is proposed.<sup>1</sup>

## 4.1 Related Works and Motivational Examples

Synchronous circuits are usually designed under the assumption of an ideal clock network, which drives the whole flip-flops to change their values at the same time. Thus, implementing clock trees to have zero or bounded clock skew is an efficient and safe solution to prevent timing violations. Several works have attempted to apply ADB insertion techniques for the timing closure in multiple power mode designs, while maintaining the area overhead reasonable. Su *et al.* [21] proposed a linear-time optimal algorithm for the delay assignment when the locations of ADBs are given. Then, they exploited the algorithm to find the appropriate points to allocate ADBs heuristically in a greedy manner. Lin *et al.* [29] proposed an efficient allocation algorithm of two-stage approach which performs a top-down ADB allocation followed by a bottom-up ADB elimination. Even though the approach reduced the runtime over that in [21], it still did not guarantee an optimality of ADB allocation. Lim and Kim [1] proposed a

<sup>&</sup>lt;sup>1</sup>The content of this chapter is an extended version of [27, 28].

linear-time algorithm for the ADB allocation problem where they solved the problem optimally for *each* power mode.

Two common features of the previous ADB allocation algorithms ([1,21,29]) are that (1) they resolve the clock skew violation by synchronizing *the earliest arrival times* of subtrees of interest where they set the delay value of ADB on a root of one of the subtrees to the difference of the earliest arrival times of the subtrees; (2) the methods are applied *mode by mode*, independently.

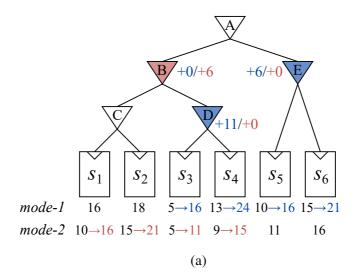

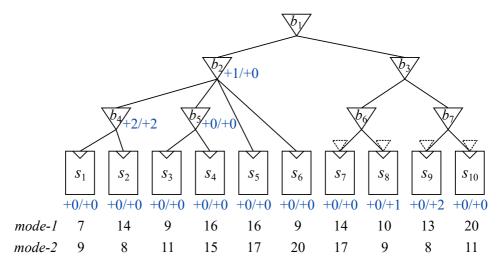

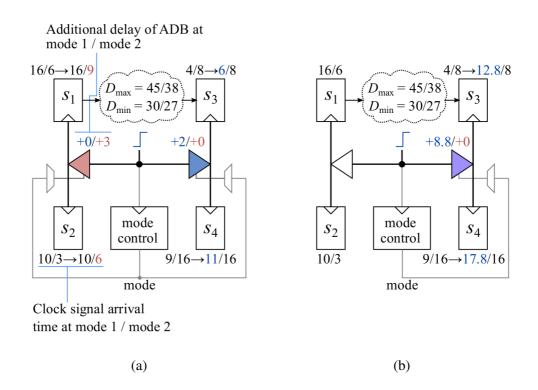

For example, consider the clock tree in Figure 4.1(a) with two operating modes mode-1 and mode-2. The initial clock signal arrival times at sinks are shown at the bottom in black numbers. Suppose the clock skew bounds for each power mode,  $\kappa_1$  and  $\kappa_2$  is 10. Clearly, there are clock skew violations in both mode-1 and mode-2; in mode-1 the clock skew is 13, which is defined by sinks  $s_2$  and  $s_3$ , and in mode-2, the clock skew is also 11, which is defined by  $s_3$  and  $s_6$ .

The results of ADB allocation produced by the previous algorithm [1] for the clock tree is shown in Figure 4.1(a) where buffers B, D, and E are replaced with ADBs and the adjusted arrival times are shown in pairs of numbers next to the initial delays. Their delay adjustment procedure is as follows. In mode-1, the earliest arrival time (= 5) of the subtrees rooted at D is synchronized to the earliest arrival time (= 16) of the subtree rooted at C by assigning delay increment of 11 to the ADB in node D. However, the delay adjustment at D increases the arrival time at sink  $s_4$  from 13 to 24, which causes another skew violation between the times in  $s_4$  and  $s_5$ . The violation is then resolved by assigning delay increment of 6 to the ADB in node E. Likewise, in mode-2 the clock skew violation due to the times at  $s_3$  and  $s_6$  is resolved by assigning delay increment of 6 to the ADB in node B.

From the ADB allocation and delay assignment, we observe that (1) synchronizing the subtree's earliest arrival times (e.g., time at  $s_3$  in mode-1) introduces delay increases at the other sinks (e.g.,  $s_4$ ), so that additional ADB allocation with delay adjustment shall be needed; (2) even though the skew violation in mode-2 requires

Figure 4.1: A motivational example for ADB allocation and delay assignment when the skew bound for each mode is given to 10 units of delay. (a) A clock tree with three ADBs allocated by the method of [1] to resolve clock skew violation. (b) An optimal allocation which uses one ADB.

one ADB to be allocated, node B is not the only position at which an ADB could be allocated. An alternative position is D, which coincides with the ADB allocation in *mode-1*.

An optimal ADB allocation is shown in Figure 4.1(b) in which only one ADB with delay increment of 3 in *mode-1* and 1 in *mode-2* is inserted to the tree. This example clearly shows that delay adjustment according to the synchronization of the earliest arrival times does not always yield optimal results. Furthermore, merely collecting the optimal results on individual power modes does not mean globally optimal for all power modes. In order to find optimal results, ADB allocation should consider all modes simultaneously.

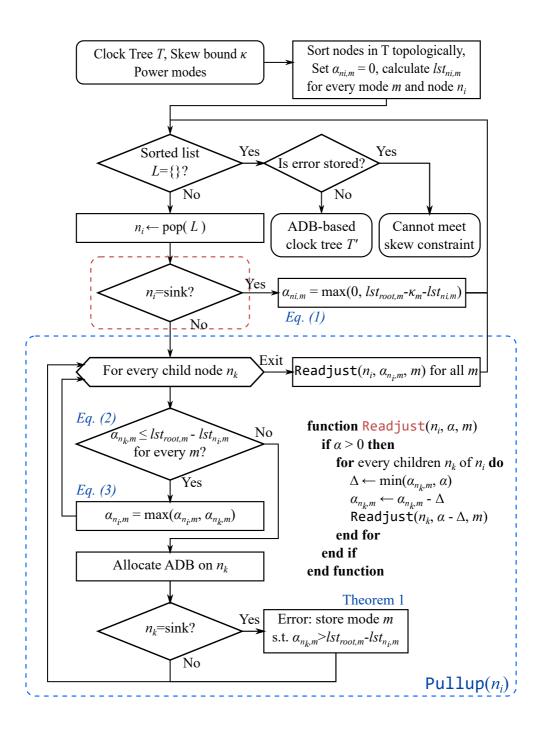

## 4.2 ADB Allocation Algorithm Satisfying Clock Skew Bound

This section describes our proposed ADB allocation algorithm, ADB-PULLUP, to ensure the clock skew bounded by a given margin. The notations commonly used in the presentation is summarized in Table 4.1.

Table 4.1: Notations used in ADB-PULLUP

| Symbol                                                                             | Description                                                              |  |

|------------------------------------------------------------------------------------|--------------------------------------------------------------------------|--|

| $n_i$                                                                              | A node in a clock tree, which is either a buffer or a sink;              |  |

| $T_{n_i}$                                                                          | The subtree rooted at node $n_i$ ;                                       |  |

| $arr_{n_i,m}$                                                                      | $arr_{n_i,m}$ Arrival time at sink node $n_i$ at $mode-m$ ;              |  |

| $lst_{n_i,m}$ The latest arrival time among the sinks on the subtree rooted at nod |                                                                          |  |

|                                                                                    | in mode-m;                                                               |  |

| $\kappa_m$                                                                         | The given clock skew bound to meet in <i>mode-m</i> ;                    |  |

| $\alpha_{n_i,m}$                                                                   | Delay value (i.e., increment) of ADB located at node $n_i$ in $mode-m$ ; |  |

| $H_{n_i}$                                                                          | Set of child nodes of $n_i$ not to be replaced by ADBs.                  |  |

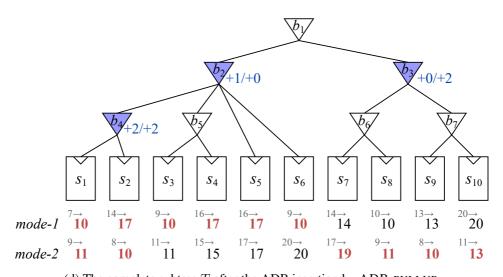

Firstly, we demonstrate the procedure of our algorithm for the allocation of ADBs under constant skew bound, called ADB-PULLUP, step-by-step using an example to see how the algorithm works. Then, we describe the flow of the algorithm and the properties of the algorithm.

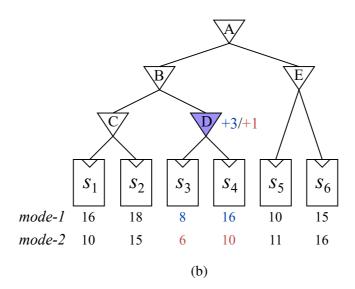

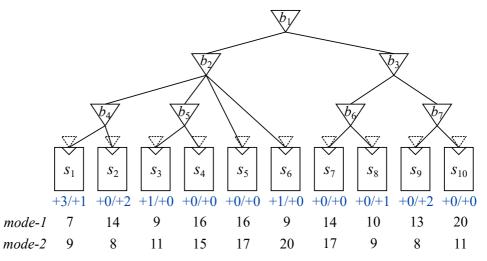

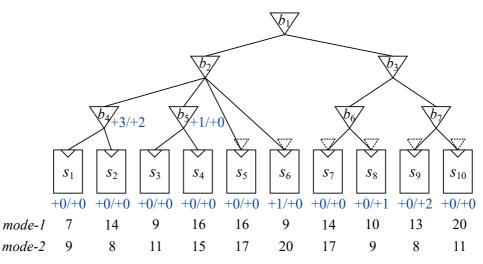

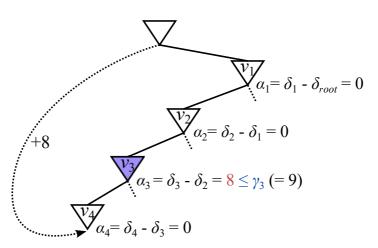

Let us consider the clock signal arrival times shown in the clock tree in Figure 4.2(a). Let  $\kappa_m = 10$  for all m. The numbers below the tree represent the clock delay from the clock source to the sinks in each mode. First, ADB-PULLUP initially assumes that each sink has a distinct fictitious ADB at the front of it. The numbers at the bottom of each sink  $s_i$  indicate the delay value increments of the ADB on  $s_i$ ,  $\alpha_{s_i,1}$  in mode-1 and  $\alpha_{s_i,2}$  in mode-2, for  $i=1,\cdots,10$ . We compute the delay value by

$$\alpha_{s_i,m} = \max\{0, lst_{root,m} - \kappa_m - arr_{s_i,m}\}$$

(4.1)

where root represents the clock source (root) node of the clock tree. Thus,  $lst_{root,m}$  is the latest clock arrival time among those of all clock sinks in power mode m. For example,  $\alpha_{s_1,1} = \max\{0,20-10-7\} = 3$  and  $\alpha_{s_1,2} = \max\{0,20-10-9\} = 1$ . Note that the value by Equation (4.1) for each sink  $s_i$  corresponds to the least increase of delay required on the fictitious ADB in  $s_i$  to meet the clock skew constraint. Then, ADB-PULLUP performs a bottom-up traversal on the clock tree to move up (i.e., pull up) the ADBs towards the root of the clock tree.

The decision of allocating an ADB at  $n_k$  which is a non-sink and whose  $\alpha$  value has been assigned is made according to the evaluation result of the inequality:

$$\alpha_{n_{k},m} > lst_{root,m} - lst_{n_{k},m}$$

(4.2)

where  $n_i$  is the parent node of  $n_k$ . If the inequality is true for at least one power mode, an ADB is allocated. For example, let us assume that  $\alpha_{b_4,-}$ ,  $\alpha_{b_5,-}$  have been calculated using the same method we are going to explain. The values are shown in Figure 4.2(b). Then, since  $\alpha_{b_4,2}(=2) > lst_{root,2} - lst_{b_2,2}(=20-20=0)$ , an ADB is inserted to  $b_4$ . However, since  $\alpha_{b_5,1}(=1) \leq lst_{root,1} - lst_{b_2,1}(=20-16=4)$  and  $\alpha_{b_5,2}(=0) \leq lst_{root,2} - lst_{b_2,2}(=20-20=0)$ , no ADB is inserted to  $b_5$ .

(a) A clock tree T before the ADB insertion by ADB-PULLUP with  $\kappa_1=\kappa_2=10$ ; allocating  $\alpha_{n_i,m}$  for each sink  $n_i$  and mode m.

(b) After the process of clock subtrees rooted at  $b_4$  and  $b_5$ . (All children  $n_k$  of each subtree rooted at  $n_i$  satisfy  $\alpha_{n_k,m} \leq lst_{root,m} - lst_{n_i,m}$  for all modes. Thus, ADBs are not inserted.)

(c) After the process of clock subtree rooted at  $b_2$ . ( $\alpha_{b_4,2} > lst_{root,2} - lst_{b_2,2}$ , thus, an ADB is inserted at  $b_4$ .)

(d) The complete subtree T after the ADB insertion by ADB-PULLUP.

Figure 4.2: Example showing step-by-step procedure of ADB-PULLUP.

Once the decision of allocating ADBs to all children of  $n_i$  is made, the  $\alpha$  value of  $n_i$  is updated by

$$\alpha_{n_i,m} = \max\{\alpha_{n_k,m} : n_k \in H_{n_i}\} \tag{4.3}$$

where  $H_{n_i}$  represents the set of  $n_i$ 's children on which ADBs are not allocated. If  $H_{n_i} = \phi$ , then  $\alpha_{n_i,m}$  is set to 0 for every mode m. For example, in Figure 4.2(c),  $b_4$  is not in  $H_{b_2}$  since  $\alpha_{b_4,2} > lst_{root,2} - lst_{b_2,2}$ , while  $\alpha$  of  $b_5$ ,  $s_5$ ,  $s_6$  is smaller than or equal to  $lst_{root} - lst_{b_2}$  for all modes. Thus,  $\alpha_{b_2,1} = \max\{\alpha_{b_5,1},\alpha_{s_5,1},\alpha_{s_6,1}\} = \max\{1,0,1\} = 1$  and  $\alpha_{b_2,2} = \max\{\alpha_{b_5,2},\alpha_{s_5,2},\alpha_{s_6,2}\} = \max\{0,0,0\} = 0$  since  $H_{b_2} = \{b_5,s_5,s_6\}$ .

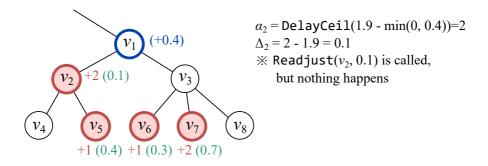

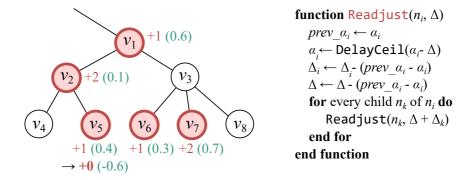

At this stage, from node  $n_i$  where its  $\alpha$  values are set, we recursively perform delay-resetting on every descendant,  $n_k$ , of  $n_i$  by calling function READJUST described in Figure 4.3. READJUST subtracts  $\alpha_{n_i,m}$  from the sum of delays on each path from a child of  $n_i$  to its descendent sinks, or set to 0 if  $\alpha_{n_i,m}$  is bigger than the original sum of delays. For example, Figure 4.2(c) shows the results of delay readjustment when the delay value of  $b_2$  is computed by Equation (4.3). For example,  $\alpha_{b_4,1}=3-\min\{1,3\}=2$  and  $\alpha_{b_4,2}=2-\min\{0,2\}=2$ . Subtree  $T_{b_3}$  is processed likewise. After all the nodes are processed, ADB-PULLUP reports the result of ADB insertion with the updated arrival times as shown in Figure 4.2(d).

The flow of ADB-PULLUP is depicted in Figure 4.3. In the initialization phase, the  $\alpha_{n_i,m}$  value of each sink  $n_i$  is assigned to the minimum value by which  $arr_{n_i,m}+\alpha_{n_i,m}$  is not shorter than  $lst_{root,m}-\kappa_m$ . This fixes the skew violations by assuming the allocation of a fictitious ADB to each sink. The next phase is "pulling up" these ADBs to non-sink locations of the clock tree, by performing PULLUP operation in a topological order. Consider a non-sink node  $n_i$  to be processed in the flow. Each child,  $n_k$ , of  $n_i$ , is checked to see if an ADB is needed according to the evaluation of  $\alpha_{n_k,m}>lst_{root,m}-lst_{n_i,m}$ . If the evaluation is true, an ADB is inserted to  $n_k$ , otherwise, the maximum  $\alpha$  value (initially 0) to be assigned to  $n_i$  is updated if needed. Once the process PULLUP at the bottom loop in Figure 4.3 is done, the  $\alpha$  values at the

descendants of  $n_i$  are recursively re-set according to function READJUST.

The time complexity of ADB-PULLUP is bounded by  $O(mn\log n)$  where m is the number of power modes and n is the number of nodes of the input clock tree. Since m is usually very small, the complexity is reduced to  $O(n\log n)$ . The detailed derivation of the time complexity of ADB-PULLUP is the following: O(n) time is taken to sort nodes in topological order and O(mn) time to compute the lst values of all nodes. Likewise, O(mn) time is taken to assign the  $\alpha$  values for all leaf nodes and O(mn) to the determination of ADB placement to nodes. Finally, total time of  $O(mn\log n)$  is taken for READJUST function, which is the most dominant in the steps of ADB-PULLUP. It is because each node is visited by READJUST at most the number of their ancestors. All properties and theorems of ADB-PULLUP are summarized in Section 4.4.

#### 4.3 Extensions

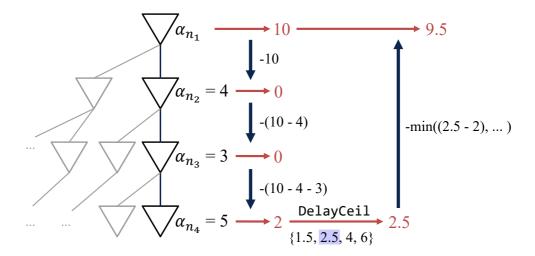

#### 4.3.1 Supporting Discrete ADB Delay

By slightly updating the computation of  $\alpha$  values in ADB-PULLUP, it is possible to support the ADB allocation with ADBs of discrete delay increments. (We call our updated ADB algorithm ADB-PULLUP-Q.)

At the stage of the decision made by Equation (4.2),  $\alpha_{n_k,m}$  is replaced by the closest ADB delay which is larger than or equal to the original value. The quantized delay is used as  $\alpha_{n_i,m}$  in Equation (4.3), and READJUST subtracts the new  $\alpha_{n_i,m}$  value from the  $\alpha$  of its descendent ADBs. The main difference of READJUST function in ADB-PULLUP and ADB-PULLUP-Q is that ADB-PULLUP-Q updates the  $\alpha$  to the quantized value with the minimum increase from the original value at the same time of the subtraction. At the final stage of READJUST, the minimum delay increment occurs from the quantization is subtracted from  $\alpha_{n_i,m}$ , to balance the total clock delays.

Figure 4.3: The flow of ADB-PULLUP.

Figure 4.4: An example of executing modified READJUST function to handle discrete ADB delays. After the execution of original READJUST, additional procedure, DELAYCEIL(), is executed to select the delay among the available values.

#### 4.3.2 Integration of Buffer Sizing

We can think of buffer sizing as an ADB allocation imposed by the restriction that the  $\alpha$  values in power modes are pre-defined. For example, when a buffer  $b_i$  in the input clock tree is going to be replaced by a buffer  $buf_j$  in the buffer library  $\mathcal{L}$  (rather than an ADB), the delay number in each power mode may be increased or decreased, but the number is fixed, which means uncontrollable, unlike ADB. Let  $\beta_{n_i,m}^j$  be the delay increase or delay decrease in power mode m caused by the replacement of buffer  $b_i$  in the input clock tree by  $buf_j \in \mathcal{L}$ . We can compute all  $\beta$  values from the input clock tree and  $\mathcal{L}$ . Now, we want to substitute the minimal ADBs determined by ADB-PULLUP (or ADB-PULLUP-Q) with as many buffers in  $\mathcal{L}$  as possible to further reduce the number of ADBs to be inserted in the clock tree while still meeting the clock skew constraint for every power mode. Since we have all the  $\beta$  and  $\alpha$  values in every node of the clock tree in all power modes, a naive solution is to generate all the combinations of buffer sizing as well as ADB insertion for all nodes, and choose the one that

uses the least number of ADBs while meeting the clock skew constraint. However, its computation time grows exponentially as the problem size increases. To be practically feasible, we propose a simple but effective iterative method:

For each node n<sub>i</sub> in the clock tree, in which ADB-PULLUP (or ADB-PULLUP-Q) has decided that an ADB should be inserted in the node, for each buffer buf<sub>i</sub> ∈ L, we compute

$$\delta_{n_i}^{buf_j} = \sum_{m=1}^{K} (\alpha_{n_i,m} - \beta_{n_i,m}^{buf_j})^2$$

(4.4)

where K is the number of modes. For example, if  $(\alpha_{n_1,1},\alpha_{n_1,2})=(+3,+1)$ ,  $(\beta_{n_1,1}^{buf_1},\beta_{n_1,2}^{buf_1})=(+3,+2)$ ,  $(\beta_{n_1,1}^{buf_2},\beta_{n_1,2}^{buf_2})=(+1,-1)$ , then,  $\delta_{n_1}^{buf_1}=(3-3)^2+(1-2)^2=1$  and  $\delta_{n_1}^{buf_2}=(3-1)^2+(1-(-1))^2=8$ .

- 2. Select the pair of node and buffer sizing such that the corresponding  $\delta$  value is minimal and it satisfies the clock skew and latency constraints. The buffer in the selected node is then resized accordingly. For the previous example, selecting  $buf_1$  is preferred to that of  $buf_2$  for resizing in node  $n_1$  since  $\delta_{n_1}^{buf_1} < \delta_{n_1}^{buf_2}$ .

- 3. Update the arrival times at clock sinks according to the buffer resizing performed in Step 2, and iterate the procedure. The iteration stops when there is no pair that satisfies the skew and latency constraints or the resizing causes the number of ADBs to increase.

The rationale behind the use of  $\delta$  is that as the smaller the value of  $\delta$  in a node is, the more the corresponding buffer sizing is likely to close to the ADB that has been inserted to the node, thus, the buffer sizing taking over the role of the ADB with a minimal impact on the overall timing of the clock tree. We call the ADB allocation algorithm combined with buffer sizing ADB-PULLUP-B for the continuous delay of ADB and ADB-PULLUP-QB for the discrete delay of ADB.

## 4.4 Optimality Proofs of the Proposed Algorithm

This section provides proofs of the useful properties of the algorithm that (1) it always gets the answer unless the answer does not exist, and (2) it allocates the minimum number of ADBs to satisfy the constraint.

**Property 1.** The arrival times at sinks produced by ADB-PULLUP never exceed  $lst_{root,m}$  for every mode m.

*Proof.* For simple notations, we drop the power mode symbol m in the presentation of the proofs if it is obvious.

For a power mode, let  $L^{n_l}_{n_k \to s_j}$  be the sum of the  $\alpha$  values of the nodes on the path from  $n_k$  (inclusive) to a sink  $s_j$  which is on the subtree rooted at  $n_k$  after READJUST is applied to  $n_l$  and  $\alpha^{pre}_{n_k}$  be the  $\alpha$  value of  $n_k$  before the application of READJUST to its parent. ( $L^{s_j}_{s_j \to s_j} = \alpha^{pre}_{s_j}$  since READJUST is not applicable to sinks.)

We claim that the following inequality is hold:

$$L_{n_i \to s_j}^{n_i} + arr_{s_j} \le lst_{root}. \tag{4.5}$$

We use induction in terms of the height, h, of the subtree rooted at  $n_i$ .

- i. h=1 corresponds to the case where  $n_i$  is a sink, which means  $s_j$  and  $n_i$  in Equation (4.5) are identical. Thus,  $L_{n_i \to s_j}^{n_i} + arr_{s_j} = \alpha_{s_j}^{pre} + arr_{s_j}$ . By Equation (4.1),  $\alpha_{s_j}^{pre} + arr_{s_j} \leq lst_{root}$ .

- ii. For the induction step, we assume that the hypothesis holds for all  $h \leq H$ , and consider a node  $n_i$  with height h = H + 1. Then, all heights of its children  $n_k$  is less than or equal to H. By the induction hypothesis, for every  $n_k$  of  $n_i$ , it is true that

$$L_{n_k \to s_i}^{n_k} + arr_{s_i} \le lst_{root} \tag{4.6}$$

where  $s_j$  is a sink in the subtree rooted at  $n_k$ .

Case 1.

$$L_{n_k \to s_i}^{n_k} \ge \alpha_{n_i}^{pre}$$

:

After the application of READJUST to  $n_i, L_{n_k \to s_j}^{n_i} = L_{n_k \to s_j}^{n_k} - \alpha_{n_i}^{pre}$ . Thus,  $L_{n_i \to s_j}^{n_i} + arr_{s_j} = L_{n_k \to s_j}^{n_i} + \alpha_{n_i}^{pre} + arr_{s_j} = L_{n_k \to s_j}^{n_k} - \alpha_{n_i}^{pre} + \alpha_{n_i}^{pre} + arr_{s_j}$  $= L_{n_k \to s_j}^{n_k} + arr_{s_j} \leq lst_{root} \text{ by Equation (4.6)}.$

Case 2.  $L_{n_k \to s_i}^{n_k} < \alpha_{n_i}^{pre}$ :

By Equation (4.2), after the application of READJUST to  $n_i$ ,

$$L_{n_i \to s_i}^{n_i} = \alpha_{n_i}^{pre}, \tag{4.7}$$

and according to Equation (4.1) and the definition of  $lst_{n_i}$ ,

$$\alpha_{n_i}^{pre} \le lst_{root} - lst_{n_i} \le lst_{root} - arr_{s_j}. \tag{4.8}$$

Therefore,

$$L_{n_i \to s_j}^{n_i} + arr_{s_j} = \alpha_{n_i}^{pre} + arr_{s_j} \le lst_{root}$$

.

From Cases 1 and 2, Equation (4.6) holds for  $n_i$  with h=H+1 if it holds for any node with  $h \leq H$ . Thus, from the induction, hypothesis  $L_{n_i \to s_j}^{n_i} + arr_{s_j} \leq lst_{root}$  holds for every node in the tree. Then, because Property 1 holds for root as well,  $L_{root \to s_j}^{root} + arr_{s_j}$ , the clock arrival times at sink  $s_i$  after the whole execution of ADB-PULLUP, do not exceed  $lst_{root}$ .

In some cases, clock trees do not have any solution of ADB allocation. For example, consider a simple clock tree shown in Figure 4.5 with clock skew bound  $\kappa = 10$ . The clock arrival times at sink  $s_2$  (= 13) and sink  $s_3$  (= 2) cause the clock skew violation. However, it is not possible to resolve the skew violation in the figure whatever ADB allocations are attempted to A, B or both. We formally classify the input clock trees into ADB-solvable or ADB-unsolvable as follows:

**Definition 1.** It is said that a clock tree T with  $\kappa$  is **ADB-unsolvable** if there is a node  $n_i \in T$  such that  $lst_{n_i} - arr_{S(n_i)}^{min} > \kappa$  in which  $S(n_i)$  is the set of sinks which are directly connected to  $n_i$ ,  $arr_{S(n_i)}^{min}$  is the minimum among the arrival times of sinks in  $S(n_i)$ . (It is  $\infty$  if  $S(n_i) = \phi$ .) For the clock trees in which do not have any node  $n_i \in T$  such that  $lst_{n_i} - arr_{S(n_i)}^{min} > \kappa$ , they are said to be **ADB-solvable**.

For example, the clock tree in Figure 4.5 is said to be ADB-unsolvable because  $S(A) = \{s_3, s_4\}$  and  $lst_A - arr_{S(A)}^{min} = 13 - 2 = 11 > \kappa (= 10)$ . It can be easily seen that even allocating ADBs on every inner nodes cannot solve the problem.

Figure 4.5: An example of clock tree that belongs to *ADB-unsolvable* when clock skew bound  $\kappa = 10$ .

**Theorem 1.** ADB-PULLUP allocates ADBs on sinks if and only if the input clock tree is ADB-unsolvable.

*Proof.* ( $\Rightarrow$ ) If an ADB is allocated at sink  $s_k$ , which is a child of  $n_i$ ,

$$\alpha_{s_k}^{pre} > lst_{root} - lst_{n_i} \tag{4.9}$$

for some mode m by Equation (4.2).

Since  $\alpha_{s_k}^{pre} > lst_{root} - lst_{n_i} \ge 0$ , Equation (4.1) implies

$$\alpha_{s_k}^{pre} = lst_{root} - arr_{s_k} - \kappa. \tag{4.10}$$

Clearly,

$$arr_{S(n_i)}^{min} \le arr_{s_k}. (4.11)$$

By Equation (4.11),  $lst_{n_i} - arr_{S(n_i)}^{min} \ge lst_{n_i} - arr_{s_k}$  and by Equation (4.10),  $lst_{n_i} - arr_{s_k} = lst_{n_i} + \alpha_{s_k}^{pre} - lst_{root} + \kappa$ , which is greater than  $\kappa$  by Equation (4.9). Thus,  $lst_{n_i} - arr_{S(n_i)}^{min} > \kappa$ .

( $\Leftarrow$ ) Since the clock tree is ADB-unsolvable, there is  $n_i$  such that  $lst_{n_i} - arr_{S(n_i)}^{min} > \kappa$ . Moreover, since  $arr_{S(n_i)}^{min} < \infty$ ,  $S(n_i) \neq \phi$ . Let  $s_k \in S(n_i)$  such that  $arr_{S(n_i)}^{min} = arr_{s_k}$ . Then,  $lst_{n_i} - arr_{s_k} = lst_{n_i} - arr_{S(n_i)}^{min} > \kappa$ .

Thus, by Equation (4.1),  $\alpha_{s_k}^{pre} \geq lst_{root} - arr_{s_k} - \kappa > lst_{root} - lst_{n_i}$ , which enables the allocation of ADB at  $s_k$  according to Equation (4.2).

Note that Property 1, which is a feature that enables to keep the total size of capacitor banks in ADBs within a certain limit, does not hold for the other ADB allocation algorithms proposed in previous works. In addition, Theorem 1 indicates that if there is at least one solution, ADB-PULLUP will always find an ADB allocation solution such that the  $\alpha$  values of all sinks are 0.

To facilitate the proof of the optimality of our proposed algorithm, we define terms ADB-free-path and est- $dir_{i,m}$ , and provide one lemma.

**Definition 2.** If the path from node n (exclusive) to a sink r in a clock tree does not contain ADBs, the path is called ADB-free-path and the sink is said to has ADB-free-path from n.

Although previous works ([1,21]) have used similar definitions, ours are stricter in that if an ADB is allocated because of some modes but  $\alpha_{\cdot,m}=0$  for the other modes, it is counted as ADB only in modes with  $\alpha_{\cdot,m}>0$ . A good example is the clock tree shown in Figure 3.1. In *mode-2*, the ADB has  $\alpha=0$  and this is not counted as ADB in less strict version of ADB-free-path.

**Definition 3.** est-dir<sub> $n_i$ ,m</sub> represents the earliest arrival time among those at the sinks which have ADB-free-path from  $n_i$  in power mode m. est-dir<sub> $n_i$ ,m</sub> =  $\infty$  if such sink does not exist.

**Lemma 1.** During the process of ADB-PULLUP, if  $\alpha_{n_i,m}^{pre} > 0$  for a power mode m, there is a sink in subtree  $T_{n_i}$  that the arrival time at the sink is exactly  $lst_{root,m} - \kappa_m - \alpha_{n_i,m}^{pre}$  and the sink has ADB-free-path from  $n_i$ .

Proof. Let h denote the height of  $T_{n_i}$ . If  $h=1, n_i$  only has sinks as its children, Thus, the lemma holds. Let us assume that the lemma is true for  $h \leq H$ . We now want to show that the lemma is true for h=H+1. By Equation (4.3), if  $\alpha_{n_i,m}^{pre}>0$  for any  $n_i$  with its height of H+1, there exists a child node  $n_{k_j}$  of  $H_{n_i}$  such that  $\alpha_{n_{k_j},m}^{pre}=\alpha_{n_i,m}^{pre}(>0)$ . Since  $T_{n_{k_j}}$  has a sink whose arrival time is  $lst_{root,m}-\kappa_m-\alpha_{n_{k_j},m}^{pre}$  on ADB-free-path from  $n_i$ ,  $T_{n_i}$  also has a sink on ADB-free-path passing through the child node  $n_{k_j}$  and its clock arrival time is  $lst_{root,m}-\kappa_m-\alpha_{n_i,m}^{pre}$ .

**Theorem 2.** After the application of ADB-PULLUP to  $n_i$  in clock tree T, the resulting subtree  $T_{n_i}$  has been allocated with a minimum number of ADBs while meeting the clock skew constraint for  $T_{n_i}$ .

*Proof.* The proof of the optimality of ADB-PULLUP involves "cut-and-paste" argument. Let  $N(T_{n_i})$  denote the number of ADBs in subtree  $T_{n_i}$  except the root  $n_i$ . Let  $X_{n_i} = 1$  if node  $n_i$  has an ADB, and  $X_{n_i} = 0$ , otherwise.

We want to show that  $N(T_{n_i})$  is the smallest number among those of all feasible ADB allocations on the subtree rooted at  $n_i$ , and it has the largest value of est- $dir_{n_i,m}$  for every power mode m among those of all feasible ADB allocations with the minimum number. For example, if  $(N(T_{n_i}), est$ - $dir_{n_i,m}) = (4, 10)$ , other feasible solutions could be (5, 12), (5, 8), (4, 11), and (4, 10), but will not be (3, 12) or (4, 9).

Let h be the height of  $T_{n_i}$ .

i. When h=1, all children of  $n_i$  are sinks. Thus,  $N(T_{n_i})=0$ , which is trivially solvable, and est- $dir_{n_i,m}=\infty$  for every power mode.

ii. Let us assume this theorem holds for  $h \leq H$ . If the theorem is not true for h = H + 1, there is a subtree  $T'_{n_i}$  produced by an ADB allocation such that

(1)

$$N(T'_{n_i}) < N(T_{n_i})$$

, or

(2)

$$N(T'_{n_i}) = N(T_{n_i})$$

and  $\operatorname{est-dir}'_{n_i,m} > \operatorname{est-dir}_{n_i,m}$  for some mode  $m$ .

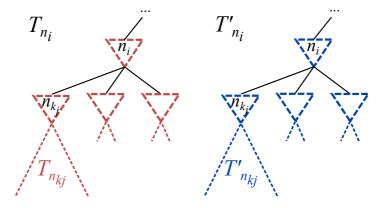

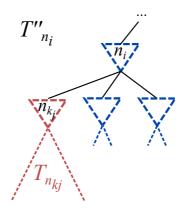

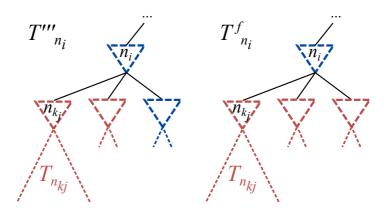

We want to prove that  $T'_{n_i}$ , which meets the above condition, does not exist, following the order illustrated in Figure 4.6. In Figure 4.6(a), the clock trees  $T_{n_i}$  and  $T'_{n_i}$  with ADBs are given. We will generate  $T''_{n_i}$  as shown in Figure 4.6(b) by replacing one child subtree  $T'_{n_{k_j}}$  of  $T'_{n_i}$  corresponding to subtree of  $T_{n_i}$ . Also, because  $T'_{n_i}$  is the better solution, we can select at least one subtree  $T'_{n_{k_j}}$  with less number of ADBs or larger est-dir. For all cases, we will show that (\*)  $N(T''_{n_i}) \leq N(T'_{n_i})$ , and est- $dir''_{n_i,m} \geq est$ - $dir'_{n_i,m}$  for every mode m if  $N(T''_{n_i}) = N(T'_{n_i})$ .

As shown in Figure 4.6(d), we can replace every child subtree  $T'_{n_{k_j}}$  with  $T_{n_{k_j}}$ , including the node  $n_{k_j}$ . Let  $T^f_{n_i}$  denote the ADB allocation tree produced by the process of replacement. Clearly,  $T^f_{n_i}$  satisfies  $N(T^f_{n_i}) \leq N(T'_{n_i})$ ,  $est\text{-}dir^f_{n_i,m} \geq est\text{-}dir'_{n_i,m}$  for every mode m with the same number of ADBs. However,  $T^f_{n_i}$  has the same values of N and est-dir as those of  $T_{n_i}$ , contradicting the assumption that  $N(T'_{n_i}) < N(T_{n_i})$ , or  $est\text{-}dir'_{n_i,m} > est\text{-}dir_{n_i,m}$  for some power mode m if  $N(T'_{n_i}) = N(T_{n_i})$ .

Now, we prove (\*). We use the fact that the theorem holds for  $h \leq H$ , (1)  $N(T_{n_{k_j}}) \leq N(T'_{n_{k_j}})$  and (2)  $\operatorname{est-dir}_{n_{k_j},m} \geq \operatorname{est-dir}'_{n_{k_j},m}$  for every power mode if  $N(T_{n_{k_j}}) = N(T'_{n_{k_j}})$ . In the proof,  $X_n$  denotes whether an ADB is allocated on node n.  $X_n = 1$  means the node n has an ADB, and  $X_n = 0$  means it does not.

Case 1.

$$N(T_{n_{k_j}}) < N(T'_{n_{k_j}})$$

:

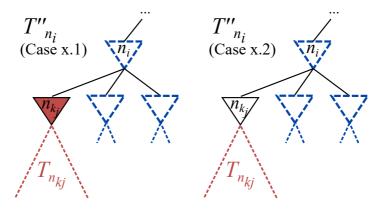

Case 1.1.  $n_{k_j} (= n''_{k_i})$  has an ADB:

(a) Assume that (1)  $N(T'_{n_i}) < N(T_{n_i})$ , or (2)  $N(T'_{n_i}) = N(T_{n_i})$  and est-dir'\_{n\_i,m} > est-dir\_{n\_i,m} for some mode m.

(b) Subtree  $T'_{n_{k_j}}$  in  $T'_{n_i}$  is replaced by  $T_{n_{k_j}}$  of  $T_{n_i}$ . The new tree is called  $T''_{n_i}$ .

(c) For Case 1 and 2, there are 2 subcases (Case x.1, Case x.2) in which  $n_{k_j}$  has an ADB or not. In all cases, (1)  $N(T''_{n_i}) < N(T'_{n_i})$  or (2)  $N(T''_{n_i}) = N(T'_{n_i})$  and  $\textit{est-dir}''_{n_i,m} \geq \textit{est-dir}'_{n_i,m}$  for every mode m.

(d) By replacing every subtree rooted on child node, we get  $T_{n_i}^f$ . Because  $N(T_{n_i}^f)$  and *est-dir*<sub> $n_i$ </sub> are the same with those of  $T_{n_i}$ , it contradicts the assumption in (a).

Figure 4.6: The overall sketch of our optimality proof.

$$\begin{split} N(T''_{n_i}) &= N(T'_{n_i}) - (N(T'_{n_{k_j}}) + X'_{n_{k_j}}) + (N(T_{n_{k_j}}) + X_{n_{k_j}}) = N(T'_{n_i}) - \\ &(N(T'_{n_{k_j}}) - N(T_{n_{k_j}}) - (X'_{n_{k_j}} - X_{n_{k_j}}) \leq N(T'_{n_i}) - 1 - (X'_{n_{k_j}} - X_{n_{k_j}}) \leq \\ &N(T'_{n_i}). \text{ Thus, } N(T''_{n_i}) \leq N(T'_{n_i}). \text{ Also, since all sinks with ADB-free-path in } T''_{n_i} \text{ are also in } T'_{n_i}, \textit{est-dir}''_{n_i,m} \geq \textit{est-dir}'_{n_i,m} \text{ for every } m. \end{split}$$

#### Case 1.2. $n_{k_i}$ does not have an ADB:

Since

$$X_{n_{k_j}} = 0$$

,  $N(T''_{n_i}) = N(T'_{n_i}) - 1 - (X'_{n_{k_j}} - X_{n_{k_j}}) < N(T'_{n_i})$ .

Case 2.  $N(T_{n_{k_j}})=N(T'_{n_{k_j}})$  and est- $dir_{n_{k_j},m}\geq est$ - $dir'_{n_{k_j},m}$  for every m:

Case 2.1.  $n_{k_j}$  has an ADB:

The ADB on  $n_{k_j}$  is allocated because  $\alpha_{n_{k_j},m}^{pre} > 0$  for some power mode m, by Lemma 1,  $lst_{n_i,m} - est\text{-}dir'_{n_{k_j},m} \geq lst_{n_i,m} - est\text{-}dir_{n_{k_j},m} = lst_{n_i,m} - (lst_{root,m} - \kappa_m - \alpha_{n_{k_j},m}^{pre}) > \kappa_m$ . Also, the est-dir of  $n'_{k_j}$  if less than or equal to the one of  $n_{k_j}$ , so that  $n'_{k_j}$  should have an additional ADB. In addition, since the sinks with ADB-free-path are the same for  $T'_{n_i}$  and  $T''_{n_i}$ ,  $N(T''_{n_i}) = N(T'_{n_i}) - (N(T'_{n_{k_j}}) + X'_{n_{k_j}}) + (N(T_{n_{k_j}}) + X_{n_{k_j}}) = N(T'_{n_i})$  and  $est\text{-}dir''_{n_i,m} = est\text{-}dir'_{n_i,m}$  for every m.

## Case 2.2. $n_{k_i}$ does not have an ADB:

As seen from Case 2.1,  $n'_{k_j}$  has an ADB on it.  $N(T''_{n_i}) = N(T'_{n_i}) - (N(T'_{n_{k_j}}) + X'_{n_{k_j}}) + (N(T_{n_{k_j}}) + X_{n_{k_j}}) = N(T'_{n_i}) - N(T'_{n_{k_j}}) + N(T_{n_{k_j}}) \le N(T'_{n_i})$ . Since  $T''_{n_i}$  and  $T'_{n_i}$  have the same sinks with ADB-free-path except the sinks in their subtrees rooted at  $n_{k_j}$ ,  $est\text{-}dir''_{n_{k_j},m} \ge est\text{-}dir'_{n_{k_j},m}$  for every m. If  $n'_{k_j}$  has an ADB,  $N(T''_{n_i}) < N(T''_{n_i})$ .

Theorem 2 claims that  $T_{root}$  produced by the application of ADB-PULLUP uses the minimal number of ADBs while meeting the clock skew constraint.

35

Table 4.2: Benchmark circuits used in the experiment

| Benchmark Circuit | #.FFs | #.Buffers | Original Skew (ps) | Latency (ps) |

|-------------------|-------|-----------|--------------------|--------------|

| s35932            | 1728  | 97        | 264.1              | 545.1        |

| s38417            | 1564  | 89        | 387.1              | 612.1        |

| s38584            | 1168  | 66        | 299.8              | 552.8        |

| B17               | 1312  | 89        | 287.7              | 654.7        |

| B18               | 2752  | 173       | 405.1              | 825.1        |

| B22               | 583   | 42        | 354.2              | 690.2        |

| F31               | 273   | 345       | 268.8              | 1268.5       |

| F34               | 157   | 218       | 211.2              | 1137.5       |

# 4.5 Experimental Results

The proposed algorithm ADB-PULLUP (continuous delay), ADB-PULLUP-Q (discrete delay), ADB-PULLUP-B (combining buffer sizing) and ADB-PULLUP-QB (combining buffer sizing with discrete delay) have been implemented in Python 3 language on a Linux machine with 8 cores of 3.50 GHz Intel i7 CPU and 16 GB memory. Table 4.2 shows the tested benchmark circuits used in the experiment. s35932, s38417 and s38584 are from ISCAS'89 benchmarks, B17, B18 and B17 are from ITC'99 benchmarks and F31 and F34 are from ISPD'09 benchmarks. ISCAS'95 and ITC'99 benchmarks were synthesized with *Synopsys IC Compiler* with 45 nm *Nangate Open Cell Library* [30]. ISPD'09 benchmarks were synthesized using the algorithm in [31]. Each benchmark was partitioned into 6 to 10 power domains which are able to operate in two different supply voltage levels, 0.95 V and 1.1 V. Each column represents the number of flip-flop, the number of clock buffers, the worst clock skew, and the worst clock latency in the four power modes of the input clock trees before the ADB allocation.

Table 4.3: Comparison of results produced by ADB-ESYNC [1], ADB-PULLUP and ADB-PULLUP-B

| Circuit | Skew       | ADB-ESYNC [1] |                   | ADB-PULLUP |        | ADB-PULLUP-B |        |  |

|---------|------------|---------------|-------------------|------------|--------|--------------|--------|--|

| Name    | Bound (ps) | #.ADBs        | Area <sup>a</sup> | #.ADBs     | Area   | #.ADBs       | Area   |  |

|         | 30         | 27            | 1180.2            | 25         | 1092.7 | 20           | 928.3  |  |

| s35932  |            |               | 1092.7            | 23         | 1005.3 | 19           | 871.2  |  |

|         | 50         | 25            | 1092.7            | 23         | 1005.3 | 19           | 871.2  |  |

|         | 30         | 31            | 1355.0            | 27         | 1180.2 | 22           | 1076.0 |  |

| s38417  | 40         | 28            | 1223.9            | 25         | 1092.7 | 20           | 985.3  |  |

|         | 50         | 26            | 1136.5            | 23         | 1005.3 | 18           | 960.9  |  |

|         | 30         | 22            | 961.6             | 20         | 874.2  | 13           | 686.9  |  |

| s38584  | 40         | 18            | 786.8             | 16         | 699.4  | 11           | 583.7  |  |

|         | 50         | 18            | 786.8             | 16         | 699.4  | 11           | 580.7  |  |

|         | 30         | 29            | 1267.6            | 25         | 1092.7 | 19           | 953.0  |  |

| B17     | 40         | 26            | 1136.5            | 22         | 961.6  | 15           | 799.7  |  |

|         | 50         | 26            | 1136.5            | 22         | 961.6  | 15           | 786.5  |  |

|         | 30         | 150           | 6556.5            | 120        | 5245.2 | 105          | 5040.6 |  |

| B18     | 40         | 147           | 6425.4            | 118        | 5157.8 | 99           | 4916.6 |  |

|         | 50         | 144           | 6294.2            | 118        | 5157.8 | 94           | 5012.9 |  |

|         | 30         | 32            | 1398.7            | 24         | 1049.0 | 21           | 986.8  |  |

| B22     | 40         | 32            | 1398.7            | 24         | 1049.0 | 21           | 976.6  |  |

|         | 50         | 31            | 1355.0            | 24         | 1049.0 | 21           | 971.5  |  |

|         | 30         | 13            | 568.2             | 13         | 568.2  | 11           | 487.4  |  |

| F31     | 40         | 13            | 568.2             | 13         | 568.2  | 7            | 325.8  |  |

|         | 50         | 7             | 306.0             | 7          | 306.0  | 7            | 306.0  |  |

|         | 30         | 30            | 1311.3            | 24         | 1049.0 | 21           | 965.4  |  |

| F34     | 40         | 30            | 1311.3            | 24         | 1049.0 | 21           | 965.4  |  |

|         | 50         | 30            | 1311.3            | 24         | 1049.0 | 18           | 844.2  |  |

| Ave     | erage (%)  | 100           | 100               | 86.16      | 86.16  | 67.73        | 75.29  |  |

<sup>&</sup>lt;sup>a</sup>The columns indicated by "Area" represent the sum of the areas of ADBs, fixed ADBs and resized buffers in  $\mu m^2$ .

Table 4.4: Comparison of results produced by ADB-ESYNC-Q [1], ADB-PULLUP-Q and ADB-PULLUP-QB

| Circuit | Skew       | ADB-ESYNC-Q [1] |        | ADB-PULLUP-Q |        | ADB-PULLUP-QB |        |

|---------|------------|-----------------|--------|--------------|--------|---------------|--------|

| Name    | Bound (ps) | #.ADBs          | Area   | #.ADBs       | Area   | #.ADBs        | Area   |

|         | 30         | 42              | 1835.8 | 29           | 1267.6 | 25            | 1143.6 |

| s35932  |            |                 | 1136.5 | 24           | 1049.0 | 19            | 879.5  |

|         | 50         | 25              | 1092.7 | 23           | 1005.3 | 19            | 871.2  |

|         | 30         | 36              | 1573.6 | 28           | 1223.9 | 23            | 1116.4 |

| s38417  | 40         | 31              | 1355.0 | 27           | 1180.2 | 20            | 991.9  |

|         | 50         | 29              | 1267.6 | 25           | 1092.7 | 18            | 967.5  |

|         | 30         | 22              | 961.6  | 21           | 917.9  | 17            | 810.2  |

| s38584  | 40         | 21              | 917.9  | 20           | 874.2  | 16            | 723.5  |

|         | 50         | 18              | 786.8  | 16           | 699.4  | 11            | 583.7  |

|         | 30         | 35              | 1529.8 | 29           | 1267.6 | 24            | 1155.0 |

| B17     | 40         | 30              | 1311.3 | 24           | 1049.0 | 16            | 828.5  |

|         | 50         | 26              | 1136.5 | 22           | 961.6  | 15            | 794.7  |

|         | 30         | 155             | 6775.0 | 122          | 5332.6 | 110           | 5125.0 |

| B18     | 40         | 153             | 6687.6 | 119          | 5201.5 | 101           | 4937.7 |

|         | 50         | 149             | 6512.8 | 118          | 5157.8 | 100           | 4942.8 |

|         | 30         | 33              | 1442.4 | 24           | 1049.0 | 19            | 985.2  |

| B22     | 40         | 32              | 1398.7 | 24           | 1049.0 | 21            | 981.7  |

|         | 50         | 32              | 1398.7 | 24           | 1049.0 | 21            | 976.6  |

|         | 30         | 13              | 568.2  | 13           | 568.2  | 12            | 527.8  |

| F31     | 40         | 13              | 568.2  | 13           | 568.2  | 11            | 487.4  |

|         | 50         | 7               | 306.0  | 7            | 306.0  | 7             | 306.0  |

|         | 30         | 30              | 1311.3 | 24           | 1049.0 | 18            | 854.4  |

| F34     | 40         | 30              | 1311.3 | 24           | 1049.0 | 21            | 965.4  |

|         | 50         | 30              | 1311.3 | 24           | 1049.0 | 19            | 898.9  |

| Ave     | erage (%)  | 106.4           | 106.4  | 89.53        | 89.53  | 72.63         | 79.57  |

Table 4.3 summarizes the results produced by applying the algorithms which assume the continous delay values of ADBs, ADB-ESYNC [1], ADB-PULLUP and ADB-PULLUP-B. The experiments were done under the clock skew bound of 30, 40 and 50 ps, respectively, for all power modes. Table 4.4 shows the results of applying the algorithms ADB-ESYNC-Q [1], ADB-PULLUP-Q and ADB-PULLUP-QB which allocates ADBs having uniformly quantized delays with granularity of 10 ps. Though the experiments used the same values for the easy comparison, clock skew bounds of each power mode does not need to be the same. Also, ADB delay candidates do not required to have uniform intervals, neither the same between different positions or power modes. In ADB-PULLUP-B and ADB-PULLUP-QB, some of the ADBs were replaced with buffers and fixed ADBs, which are ADBs that have a fixed delay because its control logic is removed. It is effectively a large buffer, covering large additional delay that standard buffers in the library can not support. The columns denoted as "Area" are the area occupied by ADBs, fixed ADBs and resized buffers. By having reduced number of ADBs, the area overhead of ADB control logic which is proportional to the number of ADBs have decreased, resulting in the reduction of the total area. The last rows of both tables show the relative values compared to ADB-ESYNC.

It is observed that ADB-PULLUP uses consistently less number of ADBs compared to the previous work, since ADB-PULLUP considers multiple power modes simultaneously during optimization. Also, the results shown in Table 4.4 indicates that ADB-PULLUP-Q uses considerably less ADBs than ADB-ESYNC-Q. This is because ADB-ESYNC-Q relies on re-iteration with tighter skew bound when clock skew violation occurs after delay quantization while ADB-PULLUP-Q can use quantized delay directly during its bottom-up phase.

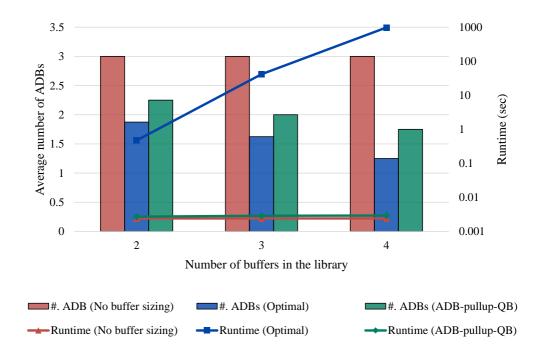

In addition, ADB-PULLUP-B and ADB-PULLUP-QB further reduce the number of ADBs over that of ADB-PULLUP and ADB-PULLUP-Q. We performed an experiment to check the effectiveness of the proposed algorithm combined with buffer sizing. Figure 4.7 shows the results on *ISCAS'89 s382* benchmark circuit, which was synthe-

Figure 4.7: Comparison of the numbers of ADBs allocated (bar) and runtime (line) of ADB-PULLUP-Q (red), optimal exhaustive algorithm (blue), and ADB-PULLUP-QB (green). The runtime is in log-scale.

sized to have 10 clock tree buffers. It is shown that the proposed algorithm clearly uses much fewer number of ADBs over the original result, but uses a little more ADBs than that of the optimal allocation with buffer sizing. However, our runtime is very small compared to that of the exhaustive algorithm.

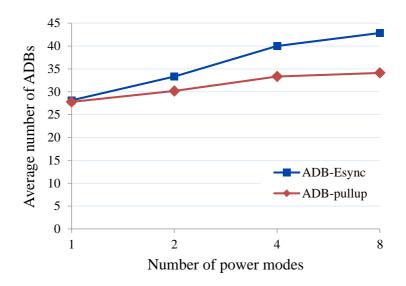

Figure 4.8: The changes of the average number of ADBs used by ADB-ESYNC and ADB-PULLUP by varying the number of power modes used.

Figure 4.8 shows the average numbers of ADBs allocated by ADB-ESYNC and our ADB-PULLUP when the number of modes varies. Clearly, ADB-PULLUP always uses less ADBs in all situations. The gap between the results increases as we increase the number of modes used since it is less likely that the ADB allocation in one mode coincides with the allocation in another mode.

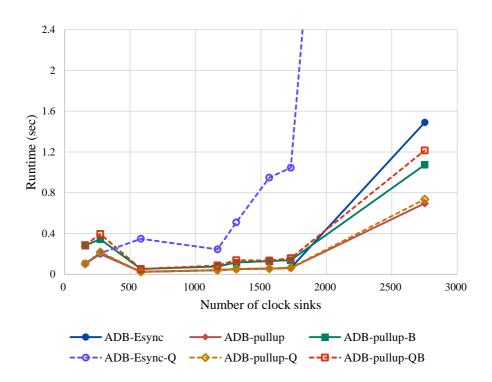

Figure 4.9 shows the runtime of ADB-ESYNC [1], ADB-ESYNC-Q [1], and proposed algorithms. ADB-PULLUP takes comparable runtime with that of ADB-ESYNC, and ADB-PULLUP-Q takes shorter compared to that of ADB-ESYNC-Q because it does not rely on iterations. The runtimes of ADB-PULLUP and ADB-PULLUP-Q are

Figure 4.9: Runtime of ADB-ESYNC [1], ADB-ESYNC-Q [1], ADB-PULLUP, ADB-PULLUP-Q, ADB-PULLUP-B, and ADB-PULLUP-QB. ADB-ESYNC-Q took about 16 sec. for a circuit with 2752 sinks.

theoretically  $O(n \log n)$ , but they are arbitrarily shorter than it in practice. This might be because READJUST function does not traverse all the children when an ADB is not allocated and  $\alpha$  becomes 0.

In summary, the comparison confirms that: (1) ADB-PULLUP finds the optimal solution with the minimum number of ADBs, reducing the average number of ADBs by 13.5% compared to ADB-ESYNC [1]; (2) ADB-PULLUP-Q allocates 15.8% less number of ADBs compared to ADB-ESYNC-Q [1] and its runtime is much shorter because it does not rely on iteration; (3) ADB-PULLUP-B and ADB-PULLUP-QB further reduces the area overhead.