# 저작자표시-비영리-변경금지 2.0 대한민국

# 이용자는 아래의 조건을 따르는 경우에 한하여 자유롭게

• 이 저작물을 복제, 배포, 전송, 전시, 공연 및 방송할 수 있습니다.

# 다음과 같은 조건을 따라야 합니다:

저작자표시. 귀하는 원저작자를 표시하여야 합니다.

비영리. 귀하는 이 저작물을 영리 목적으로 이용할 수 없습니다.

변경금지. 귀하는 이 저작물을 개작, 변형 또는 가공할 수 없습니다.

- 귀하는, 이 저작물의 재이용이나 배포의 경우, 이 저작물에 적용된 이용허락조건 을 명확하게 나타내어야 합니다.

- 저작권자로부터 별도의 허가를 받으면 이러한 조건들은 적용되지 않습니다.

저작권법에 따른 이용자의 권리는 위의 내용에 의하여 영향을 받지 않습니다.

이것은 이용허락규약(Legal Code)을 이해하기 쉽게 요약한 것입니다.

# Ph.D. DISSERTATION

# Exploration of machine learning techniques for anomaly detection in computer security

보안을 위한 이상징후 탐지를 위한 기계학습 기법의 탐색

BY

HAYOON YI

**AUGUST 2019**

DEPARTMENT OF ELECTRICAL ENGINEERING AND

COMPUTER SCIENCE

COLLEGE OF ENGINEERING

SEOUL NATIONAL UNIVERSITY

# Ph.D. DISSERTATION

# Exploration of machine learning techniques for anomaly detection in computer security

보안을 위한 이상징후 탐지를 위한 기계학습 기법의 탐색

BY

HAYOON YI

**AUGUST 2019**

DEPARTMENT OF ELECTRICAL ENGINEERING AND

COMPUTER SCIENCE

COLLEGE OF ENGINEERING

SEOUL NATIONAL UNIVERSITY

**Abstract**

Anomaly detection has long been studied in computer security for its capabil-

ity in detecting unknown new attacks. From these studies, various machine learning

models and feature engineering techniques have been proposed to enhance the ca-

pability of anomaly detection. Unfortunately, it is still considered premature for most

anomaly detection techniques to be fully deployed in real world systems. In this thesis,

I will explore various techniques to improve the deployability of anomaly detection in

real world systems. First, I will propose a new feature to be used for OS kernel data

anomaly detection to improve existing machine learning work. Then, I will explore and

propose applying LSTM language models to model program execution behavior while

mitigating a long known weakness to existing execution behavior modeling: mimicry

attacks. Furthermore, I will also propose a novel HW architecture to better support

and facilitate real-time anomaly detection with the proposed language model. Finally,

I will propose a network-device correlational model to better capture and model the

behavior of IoT devices. In this thesis, I will give details of the design and implemen-

tations of the aforementioned work and evaluate their effectiveness through various

experimental results.

주요어: Security, Machine learning, Anomaly detection

학 번: 2012-20844

i

# **Contents**

| Al | bstrac  | et            |                                                                | i  |

|----|---------|---------------|----------------------------------------------------------------|----|

| C  | onten   | ts            |                                                                | ii |

| Li | st of ' | <b>Fables</b> |                                                                | v  |

| Li | st of ] | Figures       |                                                                | vi |

| 1  | Intr    | oductio       | n                                                              | 1  |

| 2  | Prel    | iminari       | es                                                             | 4  |

|    | 2.1     | LSTM          | network                                                        | 5  |

|    | 2.2     | ROC c         | curve                                                          | 6  |

| 3  | DAI     | DE: A F       | ast Data Anomaly Detection Engine for Kernel Integrity Mon-    |    |

|    | itori   | ing           |                                                                | 8  |

|    | 3.1     | Backg         | round                                                          | 8  |

|    | 3.2     | Motiva        | ation                                                          | 12 |

|    |         | 3.2.1         | Overview of memory introspection system for kernel data anomal | ly |

|    |         |               | detection                                                      | 12 |

|    |         | 3.2.2         | Object identification & naming                                 | 14 |

|    | 3.3     | The D         | ADE Approach                                                   | 18 |

|   |      | 3.3.1                                                                   | Backtrace-Naming                                           | 19 |

|---|------|-------------------------------------------------------------------------|------------------------------------------------------------|----|

|   |      | 3.3.2                                                                   | Limitations of backtrace-naming                            | 21 |

|   | 3.4  | Design                                                                  | and Implementation                                         | 22 |

|   |      | 3.4.1                                                                   | Security assumptions and threat model                      | 23 |

|   |      | 3.4.2                                                                   | Overview                                                   | 23 |

|   |      | 3.4.3                                                                   | Generating integrity specifications                        | 24 |

|   |      | 3.4.4                                                                   | Extracting backtraces                                      | 25 |

|   |      | 3.4.5                                                                   | Verifying object integrity                                 | 28 |

|   |      | 3.4.6                                                                   | Deallocations                                              | 28 |

|   | 3.5  | Evalua                                                                  | ation                                                      | 31 |

|   |      | 3.5.1                                                                   | Performance                                                | 31 |

|   |      | 3.5.2                                                                   | Data anomaly detection                                     | 35 |

|   | 3.6  | Relate                                                                  | d Work                                                     | 40 |

|   | 3.7  | Summ                                                                    | ary                                                        | 42 |

| 4 | Mim  | siony De                                                                | ociliant Duagnam Pahavian Madaling with I STM based Propah |    |

| • | Mod  | nicry Resilient Program Behavior Modeling with LSTM based Branch dels 4 |                                                            |    |

|   |      |                                                                         |                                                            |    |

|   | 4.1  |                                                                         | round                                                      | 44 |

|   | 4.2  | Prototy                                                                 | ype Design                                                 | 46 |

|   |      | 4.2.1                                                                   | Components of DeePBM                                       | 46 |

|   |      | 4.2.2                                                                   | LSTM branch model                                          | 49 |

|   | 4.3  | Prelim                                                                  | inary findings                                             | 50 |

|   |      | 4.3.1                                                                   | Branch sequences and Mimicry attacks                       | 50 |

|   |      | 4.3.2                                                                   | Branch sequence model for anomaly detection                | 53 |

|   | 4.4  | Summ                                                                    | ary                                                        | 55 |

| 5 | Real | -Time                                                                   | Anomalous Branch Behavior Inference with a GPU-inspired    |    |

| - |      |                                                                         | Machine Learning Models                                    | 56 |

|   | Hno  |                                                                         |                                                            |    |

| Ac                                                                    | Abstract (In Korean) Acknowlegement |          |                                 |     |

|-----------------------------------------------------------------------|-------------------------------------|----------|---------------------------------|-----|

| Ab                                                                    |                                     |          |                                 |     |

| 7                                                                     | Cone                                | clusion  |                                 | 100 |

|                                                                       | 6.5                                 | Summ     | ary                             | 98  |

|                                                                       | 6.4                                 | Evalua   | tion                            | 92  |

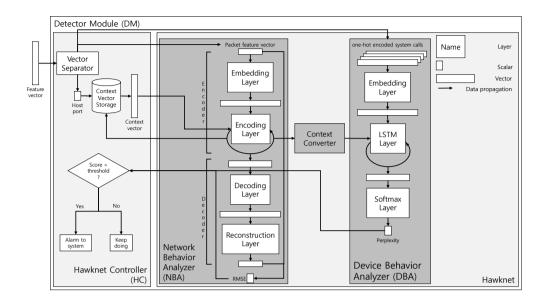

|                                                                       |                                     | 6.3.3    | Detector Module                 | 87  |

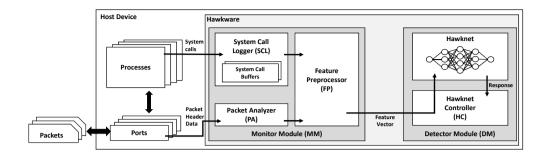

|                                                                       |                                     | 6.3.2    | Monitor Module                  | 83  |

|                                                                       |                                     | 6.3.1    | Threat models and assumptions   | 83  |

|                                                                       | 6.3                                 | Hawky    | ware Design                     | 82  |

|                                                                       | 6.2                                 | Relate   | d Work                          | 80  |

|                                                                       | 6.1                                 | Backg    | round                           | 76  |

|                                                                       | ANN                                 | Ns on an | ı IoT Device                    | 76  |

| 6 Hawkware: Network Intrusion Detection based on Behavior Analysis wi |                                     |          | h                               |     |

|                                                                       | 5.5                                 | Summ     | ary                             | 75  |

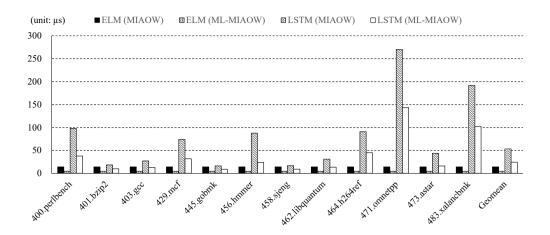

|                                                                       |                                     | 5.4.3    | Detection Speed of ML Models    | 73  |

|                                                                       |                                     | 5.4.2    | Performance Analysis            | 71  |

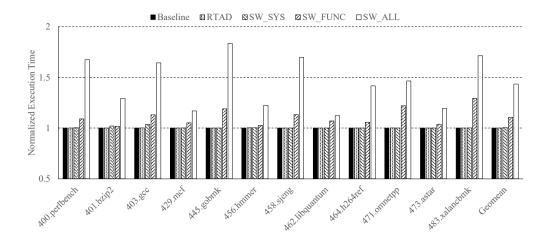

|                                                                       |                                     | 5.4.1    | Synthesis Results               | 69  |

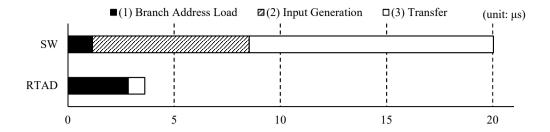

|                                                                       | 5.4                                 | Evalua   | ition                           | 68  |

|                                                                       |                                     | 5.3.3    | Anomaly Detection with RTAD SoC | 67  |

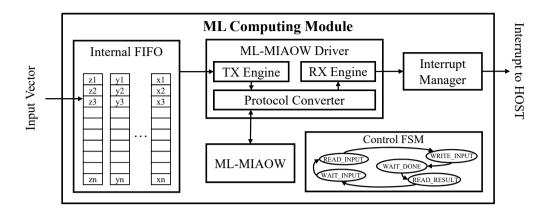

|                                                                       |                                     | 5.3.2    | ML Computing Module             | 64  |

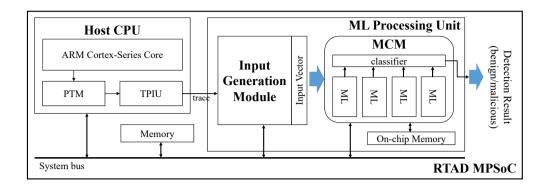

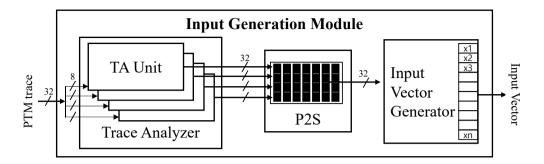

|                                                                       |                                     | 5.3.1    | Input Generation Module         | 63  |

|                                                                       | 5.3                                 | RTAD     | Architecture                    | 62  |

|                                                                       | 5.2                                 | Relate   | d Work                          | 60  |

|                                                                       | 5.1 Background                      |          |                                 | 56  |

# **List of Tables**

| 3.1 | Overhead for object identification and naming during kernel boot in          |    |

|-----|------------------------------------------------------------------------------|----|

|     | DADE                                                                         | 33 |

| 3.2 | Attacks, which were successfully detected by DADE, reported along-           |    |

|     | side their required detection method in Gibraltar's original design (at-     |    |

|     | tacks detectable with persistent specifications or transient specifications) | 36 |

|     |                                                                              |    |

| 5.1 | Synthesized results of RTAD                                                  | 70 |

| 5.2 | Trimming Result of ML-MIAOW                                                  | 70 |

|     |                                                                              |    |

| 6.1 | Feature vector of Hawkware                                                   | 86 |

| 6.2 | Average performance of each component of Hawknet (in cycles per              |    |

|     | input)                                                                       | 98 |

# **List of Figures**

| 2.1  | Standard LSTM architecture                                             | 5  |

|------|------------------------------------------------------------------------|----|

| 2.2  | Example ROC curve                                                      | 7  |

| 3.1  | Workflow of a memory introspection system for kernel data anomaly      |    |

|      | detection.                                                             | 13 |

| 3.2  | An example backtrace-name with its corrsponding function call trace.   | 18 |

| 3.3  | Granularity of backtrace-naming                                        | 20 |

| 3.4  | Overview of DADE.                                                      | 23 |

| 3.5  | The process of trapping an allocation event in DADE                    | 26 |

| 3.6  | Number of invariant properties for unique object names                 | 34 |

| 3.7  | Partial code of a VFS attack                                           | 37 |

| 3.8  | Path-name based integrity specification for <i>i_fop</i>               | 37 |

| 3.9  | Backtrace-name of inode object                                         | 38 |

| 3.10 | Backtrace-name based integrity specification for <i>i_fop</i>          | 38 |

| 3.11 | Backtrace-name for kobject (a) allocation event (b) legitimate deallo- |    |

|      | cation event (c) abnormal deallocation event                           | 39 |

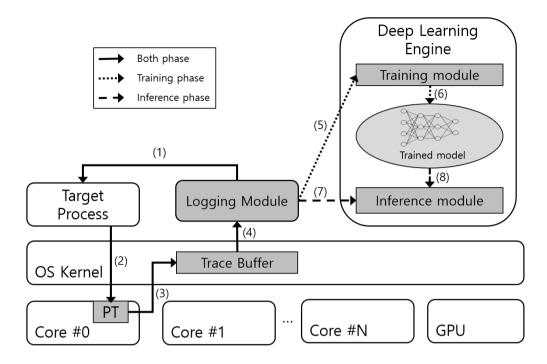

| 4.1  | Architectural overview of the DeePBM framework                         | 47 |

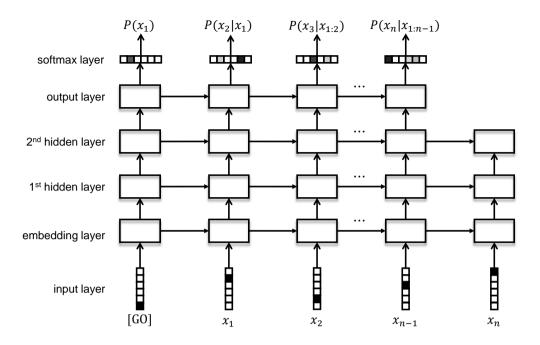

| 4.2  | Branch model                                                           | 48 |

| 4.3  | Initial branch sequence of system call open()                          | 51 |

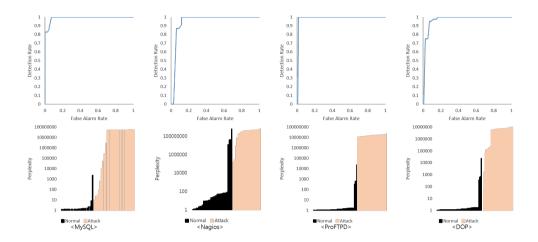

| 4.4 | The ROC curves and perplexity of each Program. Prof IPD and DOP       |    |

|-----|-----------------------------------------------------------------------|----|

|     | share the same normal sequence in this figure                         | 52 |

| 4.5 | The average perplexity values for a system call sequence model and    |    |

|     | branch sequence model                                                 | 54 |

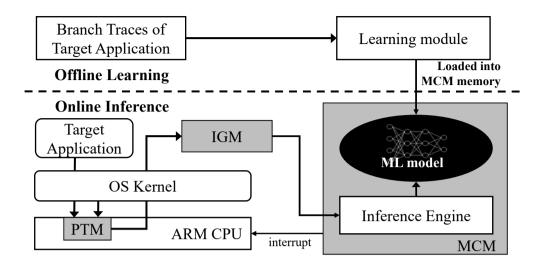

| 5.1 | RTAD architectural overview                                           | 63 |

| 5.2 | Block diagram of IGM                                                  | 64 |

| 5.3 | Block diagram of MCM                                                  | 65 |

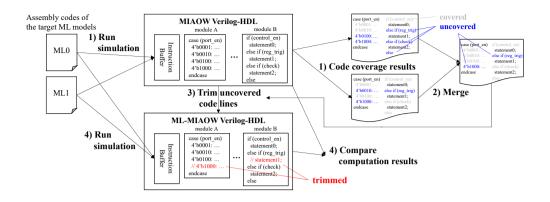

| 5.4 | Trimming MIAOW into ML-MIAOW                                          | 66 |

| 5.5 | RTAD anomaly detection procedure                                      | 69 |

| 5.6 | Performance overhead of RTAD                                          | 71 |

| 5.7 | Data transfer latency of RTAD                                         | 72 |

| 5.8 | Latencies of anomaly detection                                        | 74 |

| 6.1 | Architectural overview of Hawkware                                    | 82 |

| 6.2 | Design of Hawkware's detector module (DM)                             | 87 |

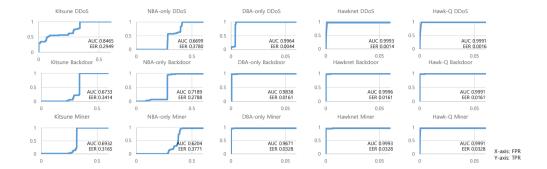

| 6.3 | Detection accuracy of Hawknet, Kitsune and variations of Hawknet      |    |

|     | given as the the receiver operating characteristic (ROC) curve along- |    |

|     | side the area under curve (AUC) and equal error rate (EER)            | 92 |

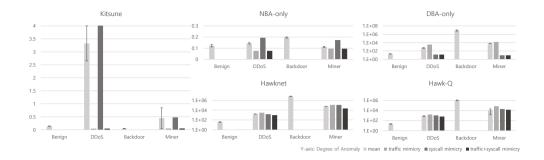

| 6.4 | Degrees of anomaly (RMSE for Kitsune and NBA-only, perplexity for     |    |

|     | the rest) of Kitsune. Hawknet and its variations.                     | 95 |

# Chapter 1

# Introduction

Inspired by biological immune systems, *anomaly detection* techniques in security strive to define a sense of self (normal behavior) in order to detect any non-self (abnormal behavior) within its target environment [1]. The rationale behind anomaly detection is that there is a distinguishable difference in benign behavior and malicious behavior. Therefore, unlike its counterpart, *misuse detection* which defines malware or attack behavior and finds adversarial activity with the defined behavior, anomaly detection focuses on defining benign normal behavior so that it may detect any abnormalities deviating from the defined normal behavior. This lends anomaly detection the capability of detecting even new and unknown attacks as anything that deviates from the norm will be detected as anomalous behavior.

With recent reports showing that millions of new malware and attacks are found in the wild every month [2], this capability of anomaly detection should make it highly favorable over misuse detection because it is well known that traditional security solutions based on misuse detection are hard-pressed to keep their malicious behavior definitions up-to-date. This is due to the fact that as the analysis of newly found malicious behavior takes time, a vast amount of effort must be given to keep the analysis from falling behind the discovery of new malicious behavior. Furthermore, as misuse detection relies on given definitions of malicious behavior, the time needed for analysis delays the update of the security solution. Unfortunately, during this delay, misuse detection is left blind to new malicious behavior which could cause severe harm to systems employing only such solutions. On the other hand, as anomaly detection defines benign behavior and detects any deviation from that defined behavior, new malicious behavior can be detected without any need of update as long as the benign behavior has not changed.

Until recently, most commodity security solutions employing anomaly detection realized the definition of normal behavior as a white-list rule set. In other words, only the behavior following the given rule set is considered normal and any behavior that violates the rules is considered anomalous. These rules are typically handcrafted by security and system experts who analyze their intended defense target, be it a network or a system, to formulate a set of rules defining its normal behavior. Evidently, this demands effort from highly skilled experts which, unfortunately, is well known to be in shortage across the globe.

To mitigate this issue, alongside the recent developments in machine learning, there has been focus on incorporating machine learning into security solutions. In machine learning based anomaly detection, instead of manually formulating rule-sets, a machine learning algorithm would formulate a set of rules or build a model from a given set of benign data. As long as a set of normal behavioral data is available, this would minimize the effort needed from a human expert and expedite the development of an anomaly detection solution for new networks or systems.

However, even though recent trends favor machine learning based anomaly detection for security, there are still many issues to consider in order to deploy the two decades of published work in real world environments. In this thesis, I perform a series of research that each explores a different issues in enhancing the deployability of machine learning based anomaly detection. Though each research addresses an issue

in deploying anomaly detection in a specific security domain, the approaches could be generalized to be of use in other domains as well.

In Chapter 3, an issue on feature collection an representation in kernel data anomaly detection will be discussed. The way prior work collected and represented kernel data feature was found to be impractical when trying to detect newer attacks and therefore a new collection and representation method that enables realistic deployment of kernel data anomaly detection will be proposed.

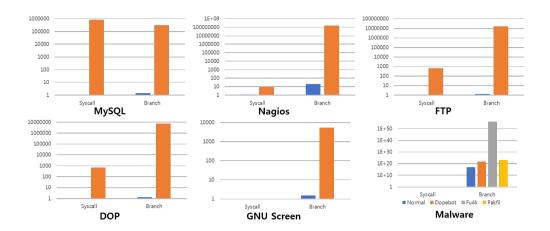

In Chapter 4, preliminary findings in research to mitigate a long known weakness of system call based program behavior anomaly detection will be shared. As my findings show branch sequences to provide better information in detecting anomalies in program behavior, a prototype deep learning model is also employed to learn the more complex branch behavior.

In Chapter 5, issues on performing real-time anomaly detection will be discussed. To facilitate real-time inference of branch based program behavior anomaly detection, a MPSoC will be proposed. The MPSoC accelerates the collection of branch behavior data, the preprocessing of features, delivery of features to a anomaly detection model and the execution of the model itself.

In Chapter 6, issues on deploying anomaly detection in IoT systems will be discussed. As most existing work assume high-end machines to perform anomaly detection, they are too heavy to deploy in inexpensive IoT devices. Therefore, features and a model fit for IoT behavior anomaly detection will be proposed.

In Chapter 2, some basic preliminaries to help understanding the following research will be given. From Chapter 3 to Chapter 6, the various issues will be discussed and explored while providing clear motivation and relation to other work. The details of the design and implementation of the proposed solutions will be explained and their effectiveness will be evaluated through various experimental results. After exploring the various issues, this thesis will be concluded in Chapter 7.

# Chapter 2

# **Preliminaries**

Below I will provide brief explanations on some important terms used throughout the thesis.

**Learning/Training:** The terms learning and training are used throughout Chapter 4 to Chapter 6. As these chapters discuss mainly deep learning models, learning and training indicate the act of adjusting the neural network parameters in accordance to the given training data.

**Inference:** The use of the term inference slightly differ between Chapter 3 and the other Chapters. In Chapter 3, inference means the act of inferring specifications from a given set of benign kernel memory snapshots, which would be closer to the term learning/training in the other Chapters. This is due to the fact that the machine learning algorithm used in Chapter 3, Daikon [21], defines the act of generating specifications as inference. In the other Chapters, inference indicates the act of performing classification with a trained neural network model.

**False positive/negative:** As we are discussing anomaly detection for security in this thesis, a positive classification on a data sample indicates that the classifier believes that the sample in anomalous. Therefore a false positive would be a benign sample being reported as anomalous and a false negative would be an anomalous sample being

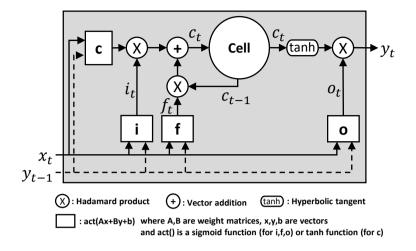

Figure 2.1: Standard LSTM architecture

reported as benign.

# 2.1 LSTM network

Though other machine learning algorithms are also mentioned, the newly proposed models in this thesis are all based on Long Short Term Memory (LSTM) [3] Recursive Neural Network (RNN). Therefore I will focus on explaining the basics of LSTM RNNs here.

RNNs are artificial neural networks that are designed to operate in a recurrent manner so that its operation on input  $x_t$  is affected by prior inputs  $x_1$  through  $x_{t-1}$ . This is typically accomplished by recurrently using the prior iteration's output  $y_{t-1}$  (from processing the prior input  $x_{t-1}$ ) when calculating the current iteration's output  $y_t$  from input  $x_t$ . LSTM is a type of RNN which uses, in addition to the prior output  $y_{t-1}$ , a special memory block to perform such recurrent operations. Through the use of this memory block, LSTM networks can maintain information over long distances (relative to typical RNNs) between inputs which gives it the capability to correlate inputs over large gaps. As shown in Figure 2.1, the LSTM memory block contains

a memory cell storing  $c_t$ , a context vector representing information of prior inputs, as well as three gates regulating the data flow into and out of the memory cell. The input gate i controls how much the current input  $x_t$  and prior output  $y_{t-1}$  would affect the calculation for  $c_t$ . The forget gate f decides how much of the prior information represented in  $c_{t-1}$  should be kept for the current iteration. From the outputs of these two gates,  $c_t$  is calculated. The output gate o controls how the new values stored in  $c_t$  should be represented in the current iteration's output  $y_t$ . And from the output of o and the values in  $c_t$ , the current output  $y_n$  is calculated. The explicit operations of each gate, which can be found in [3], is omitted here for the sake of brevity.

In order for an LSTM network to compute output  $(y_1, ..., y_n)$  from input  $(x_1, ..., x_n)$ , the following operations are performed iteratively from t = 1 to t = n.

1.

$$i_t = \sigma(W_{ix}x_t + W_{iy}y_{t-1} + b_i)$$

2.

$$f_t = \sigma(W_{fx}x_t + W_{fy}y_{t-1} + b_f)$$

3.

$$c_t = f_t \cdot c_{t-1} + i_t \cdot tanh(W_{cx}x_t + W_{cy}y_{t-1} + b_c)$$

4.

$$o_t = \sigma(W_{ox}x_t + W_{oy}y_{t-1} + b_o)$$

5.

$$y_t = o_t \cdot tanh(c_t)$$

Here, the operator  $\bullet$  denotes the Hadamard product (element-wise product), the W terms denote weight matrices (e.g.  $W_{ix}$  indicates the weight matrix for the input within the input gate's calculations.) and the b terms denote bias vectors.

# 2.2 ROC curve

In order to evaluate a proposed machine learning model, we must be able to measure its performance. Though the performance of a classification model can be expressed by simple metrics such as false positive rate (FPR) or true positive rate (TPR), the

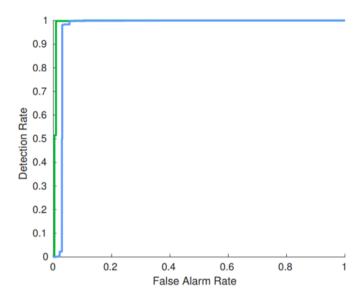

Figure 2.2: Example ROC curve

value of these can change depending on the selected threshold of the classifier. Therefore, in most classifier evaluations, receiver operating characteristics (ROC) curves are used to visualize the performance of the classifier over various thresholds. As can be seen in Figure 2.2, an ROC curve plots the TPR against the FPR on various threshold values. Typically, the larger the area under the curve (AUC), the better a classifier can distinguish data classes [4]. For example, in Figure 2.1, the classifier represented by the green curve has better performance than that of the blue curve. ROC curves are used to evaluate the proposed classifiers in Chapter 4 and Chapter 6.

# Chapter 3

# DADE: A Fast Data Anomaly Detection Engine for Kernel Integrity Monitoring

# 3.1 Background

In computer systems, the kernel is at the heart of most critical operations because it manages the information stored in the system (both code and data) as well as hardware resources such as CPU, memory, and peripheral devices. Thus, ensuring the integrity of the kernel assumes considerable importance as attacks against the kernel could allow an adversary to obtain the highest privilege within a compromised system. However, with said privilege, adversaries would be able to bypass most protection methods inside a system, therefore most methods of monitoring kernel integrity require an isolated environment which is safe from the potential influence of a compromised kernel.

This isolation is typically achieved by keeping the monitor on the outside of the operating system it wishes to verify. From this external position, the monitor would perform *memory introspection*, which is the act of looking into and making sense of the raw memory of a different system, in order to acquire the values of current kernel data. Then, it would verify kernel integrity by checking whether certain *integrity specifications*, which describes the behavior expected from an uncompromised ker-

nel, hold over the acquired data or not. These specifications would represent *invariant properties*, properties that would hold true throughout the execution of an uncompromised kernel, and any violation of these specifications would be acknowledged as a *data anomaly* and be considered as an attack against the kernel. For example, pointers in the system call table are supposed to strore addresses of legitimate system calls and therefore any pointer indicating an unknown address can be considered as the result of an attack that tries to insert a malicious hook inside the system call table.

For most cases in the past, the integrity specifications and their corresponding invariant properties were identified and specified by hand, as this task typically requires intimate knowledge of the workings of a kernel to understand and describe the expected behavior of its data. However, as it requires such expert knowledge, hand-tailoring these specifications can be rather time-consuming. For example, in order to write the specification that verifies the existence of permission tampering attacks against the Access Vector Cache (AVC) in the SELinux, shown in [35], the writer must recognize that the attack creates a discrepancy between AVC node values and the access permissions in access vector tables and therefore can be verified by cross-checking the two. This rule was written in 709 lines of C code. Considering this rule alone, the code size may not seem much big, but let me remind that the code was only for a certain type of attack against a single data structure. Therefore, describing such specifications for the entire kernel would be highly impractical as there are thousands of objects within a kernel and thousands of new kernel attacks surface every month [9].

In order to lessen tremendous efforts and overheads for monitoring every object in the kernel, much of research in practice has taken a more realistic approach where they confine their interest only on a more limited class of objects, called *kernel control data*, which are used to manage the flow of operations within a kernel, such as the system call table or the interrupt descriptor table. From the perspective of security, kernel

control data are of great importance in that they are involved in the kernel's runtime execution behavior. Thus, by examining their values, we may basically determine the existence of a rootkit that is altering normal control flows of the kernel at its disposal. Fortunately, their types and numbers are relatively small when compared to the entire kernel data and moreover, each control data structure generally holds just a limited number of possible, legitimate values under normal circumstances. Capitalizing on this interesting property, previous studies have successfully verified the integrity of various critical kernel structures by examining only a handful of integrity specifications for control data.

However, in their efforts to seek sophisticated techniques to compromise OSes, adversaries have turned their eyes to attacking a system without altering control data (or equivalently, changing normal execution flows) but only by tampering with noncontrol kernel data. For example, an attack could alter the non-control data representing the maximum number of threads that could run concurrently and cause a denial of service (DoS) attack or tamper with the data managing reserved pages and cause a resource wastage attack [12]. Unfortunately, unlike control data that, in most cases, can be verified with similar types of specifications defining the legitimate addresses of kernel code for certain services, non-control data usually have little in common. This is due to the fact that, as each non-control data dictates a specific functionality within the system and therefore would represent a different aspect of the kernel state, the context of most non-control data would be vastly different from one another. Furthermore, non-control kernel data heavily outnumber kernel control data, making it virtually impossible, as stated above, to provide hand-crafted specifications for all non-control data in the kernel to verify the kernel integrity.

Acknowledging this, Baliga et al. [12] suggested a framework named Gibraltar that leverages machine learning to find *invariants* of kernel data, which are properties expected to hold true during the runtime of a kernel. This is made possible by defining

templates of possible invariant properties of data, such as value bounds  $(Value_A \leq Value_B)$  or memberships  $(Value_A \in Set_X)$ , that could express most cases of data behavior in a simple and straightforward way. These templates are used alongside with memory snapshots of a healthy kernel to infer the actual invariants of kernel data structures. This allows the generation of specifications for both control and non-control data across the entire kernel with little human involvement, minimizing human error as well as human labor in the process.

Unfortunately, despite the advantages of Gibraltar, there is a major problem in its original design in regards to its practicality for deployment in real-world systems. As mentioned above, Gibraltar and most frameworks enforce their specifications by employing external monitors that are isolated, physically or virtually, from the potential influence of contaminated kernels. However, this isolation introduces a complication to these frameworks widely known as the semantic gap, i.e., the external monitors not having any contextual information of the raw kernel memory that they are monitoring. As this is the case, each framework has its own way of overcoming the gap and examining the data objects within raw kernel memory. In the original design of Gibraltar, data objects are found by their relative position to public symbols, whose addresses are predetermined at compile time. These relative positions, however, are subject to change after a system reboot, and thus any specification related to an object with an alternate position must incorporate its new position in order to correctly examine its current value. Consequently, Gibraltar must track down data objects and infer their invariant properties at the start of each and every reboot of the system, which takes up from 20 to 50 minutes even on an up-to-date machine.

In this chapter, I propose a new design that accelerates the overall introspection process by virtually eliminating the long booting delay needed in Gibraltar. The key idea of my design is to leverage information available at object allocation events, namely, backtraces of kernel function calls, to identify objects persistently over re-

boots, substantially cutting out the time needed at every reboot as well as the time needed to verify specifications at runtime. To evaluate the effectiveness of my design, I have implemented a prototype data anomaly detection engine (DADE) which relies on a virtualization to provide an isolated externel monitor environment. The experiment reveals that DADE only induces a delay of 68.49ms with each reboot and a delay of 900ms for an initial scan and an average of 160ms for subsequent scans. The main contributions of this chapter is introducing this new design and providing evaluation of a working prototype based on this design, which enables the automatic generation and use of integrity specifications of kernel data objects while incurring low overhead.

The remainder of this chapter is organized as follows. I first give a more thorough description of memory introspection and my motivation in Section 3.2 and then explain the main concepts of my approach in Section 3.3. I then show the design and implementation of the prototype DADE in Section 3.4 and its evaluation in Section 3.5. Finally, I relate my work to others in Section 3.6 and conclude in Section 3.7.

### 3.2 Motivation

In this section, I give a brief overview of the general flow of kernel data anomaly detection and introduce the techniques adopted in such systems and then explain the motivation behind my approach.

# 3.2.1 Overview of memory introspection system for kernel data anomaly detection

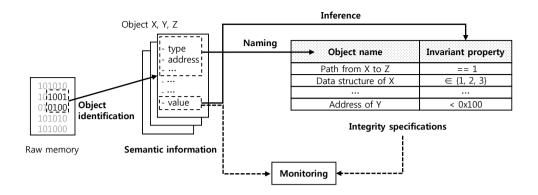

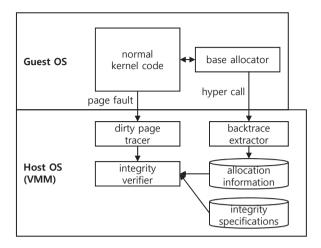

Figure 3.1 is a diagram of the basic workflow of a memory introspection system for data anomaly detection.

In order to perform memory introspection, kernel data objects must first be identified within raw memory. However, as stated in Section 3.1, the monitor performing introspection initially has little information of the actual kernel data residing in memory.

Figure 3.1: Workflow of a memory introspection system for kernel data anomaly detection.

In order to overcome this, the monitor typically leverages known semantic information of data objects, such as their data structure definitions, and maps out the data objects within raw kernel memory. During this process each object is given a *name* that represents one of its semantic information, such as its physical address or object type, in order to distinguish them from one another.

For the generation of integrity specifications in this system, the invariant properties of the mapped data objects are inferred from their found data values, be it by hand or machine learning, and associated with their corresponding data objects. The association of object name and invariant property would be reflected in integrity specifications as seen in Figure 3.1, being in the form of tuples of object names and their corresponding invariant properties.

Then, during runtime, these specifications are utilized for data anomaly detection. When the system monitors for data anomaly, the monitor first goes through the raw memory mapping data objects and naming them. Next, it looks up the object names in integrity specifications to find their corresponding invariant properties. Finally, it examines the current values of the objects and verifies whether or not a data anomaly has occurred.

**Transient integrity specifications** In such a system, especially when integrity specifications are generated automatically, there exists a complication, namely, *transient integrity specifications*, which are specifications that hold true during the runtime they were inferred but may not hold true across system reboots. There are mainly two reasons for these specifications: the object naming used for specifications being transient or the inferred invariant property being transient. Though both cases have interesting properties, in this chapter, I focus on those caused by transient object names and leave the other case to future work. Below I give a more in depth view of object naming and why some techniques may end up with transient specifications.

# 3.2.2 Object identification & naming

In a memory introspection system, its overall operation is greatly affected by the technique selected for object identification and naming. For instance, assume a system opted to naïvely name every identified object with the same name. In this scenario, all objects would be subject to the same set of invariant properties because all properties would be associated with one single name. Thus, it would be impossible to perform a meaningful data anomaly detection. On the other hand, if a system adopted an elaborate technique that could name each object uniquely, it could perform a thorough data anomaly detection as each object would be verified by their own set of invariant properties. I give below an overview of the two most prominent object identification schemes and their associated naming schemes along with their impact on the operation of data anomaly detection systems.

# **Memory traversal**

*Memory traversal* [16, 17] is one of the most widely used techniques for object identification. For a system to utilize memory traversal, it must first gather two sets of information on the OS it wishes to monitor: One is the set of addresses where static

objects, whose addresses are fixed at compile time, can be located and the other is the set of data structure definitions for all data objects. Having this information, the system can identify all objects in memory by recursively following objects pointed by a member pointer field of an object that was identified earlier, starting with static objects. This technique allows the system to gather valuable semantic information, namely, the pointer traversal paths leading up to each object. These *paths* of objects are highly suitable for object naming since they can uniquely distinguish each individual object and express essential information on the connectivity between objects in a form that is easy to interpret. For these reasons, Gibraltar adopted memory traversal for object identification along with naming objects with their path information.

However, despite the advantage of naming objects with their path information, there is a problem with verifying integrity specifications generated with such object names. As mentioned before, in order to verify the integrity of an object, a detection system names an object and then checks invariant properties associated with the object name in its integrity specifications. The problem is that there is no guarantee that the path-name of an object would persist over system reboots, and thus making it difficult to reuse integrity specifications across reboots as there is no way of knowing if the path-name in a specification points to the same object after a reboot. This is because one or more objects on a pointer traversal path may be of a container type of data structure, say a linked-list, and in this case, the path is subject to change after every system reboot, as the contents of the linked list cannot be decided until runtime. For instance, task\_struct objects, which hold task information, are known to be connected in a linked-list that starts from the static object *init\_task*. Therefore, the path-name for the nth  $task\_struct$  object would be  $init\_task \rightarrow next \rightarrow task\_struct\_1 \rightarrow next \rightarrow ... \rightarrow$  $next \rightarrow task\_struct\_n$ . However, after a reboot, unless the kernel being monitored has the exact same task environment as that of when its invariant properties were inferred before the reboot, the path-name leading to the nth task\_struct object might be pointing to a different *task\_struct* object.

In consideration of this, Gibraltar categorized integrity specifications into two distinct groups; persistent and transient. Persistent specifications are ones that would hold across reboots, in other words, the object names of persistent specifications will always stay the same regardless of reboot as well as their associated invariant properties. All other specifications, which was briefly mentioned above, are considered to be transient ones. The authors of Gibraltar argued that persistent specifications alone are sufficient enough to detect all of the attacks from their test suite. However, I discovered that there are attacks that cannot be covered by their set of persistent specifications. For example, VFS (Virtual File System) [15] rootkits are a well-known class of rootkits hijacking control flows during file management. They attempt to manipulate member function pointers of file objects which designate the functions to be called when file operations such as read and write are carried out. In order to detect this class of rootkits, the value of the f<sub>-</sub>op variable inside file objects must match a value in a list of legitimate  $f_{-}op$  values. The path-name for file objects, however, are subject to change over reboots, therefore only with transient specifications can a VFS rootkit be detected. Consequently, Gibraltar must employ both groups of specifications in order to provide adequate security, which, unfortunately, hampers performance. In order to employ transient integrity specifications, Gibraltar must discard previous integrity specifications and generate new specifications after every reboot. This encompasses cross-examining an overwhelming number of object values for the inference of new invariant properties, which alone was reported to take at least 20 minutes in Gibraltar's experimental results.

### Linear scan

The drawbacks of memory traversal, mentioned above, could be alleviated if objects are identified with a different scheme: *linear scanning*. *Linear scanning* [36, 25] iden-

tifies objects with each object's allocation information which could be obtained by memory management structures, such as slab [14] allocators in Linux [25], or by observing object allocation events [36]. The major difference between this technique and memory traversal is that an object can be identified without reference to any other object. This frees linear scanning from the drawbacks of pointer chasing that occurs in memory traversal and renders it possible to overcome the limitations of Gibraltar. The root cause of Gibraltar's problems, as you may recall, lies in the fact that it names objects with their paths, semantic information of object relations that cannot be guaranteed to persist over reboots; bringing the possibility of transient integrity specifications. Considering this, it is safe to assume that if the semantic information used for naming objects remains persistent across reboots, no transient specification would be generated from invalidated object names. Which would partially eliminate the need of generating specifications with every reboot, as such specifications would be reusable across reboots due to the persistency of their object names. Fortuitously, typical semantic information obtainable in linear scanning are not subject to change over reboots. For instance, the type of an object obtained through the kernel memory allocator should never be altered in normal circumstances and would stay the same regardless of reboots. Therefore, employing linear scanning in Gibraltar would alleviate its inherent problem, as it would allow the reuse of specifications over reboots; in other words, Gibraltar only needs to generate its specifications once due to the fact that they would persist across reboots.

However, these approaches come with their own drawbacks. As [36] was mainly designed for systems such as honeypots, it did not concern itself in having practical performance in commodity systems. On the other hand, [25] shows practical performance. However, it determines information of objects with their types or their connectivity to different objects, the former lacking a bit in granularity to distinguish objects of different contexts and the latter having the same problem as path-naming.

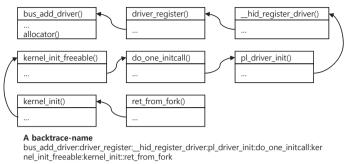

Figure 3.2: An example backtrace-name with its corrsponding function call trace.

In summary, despite their advantages, there are limitations to prior techniques in object identification. Memory traversal with path-naming, though it is straightforward and fine-grained, is accompanied by transient specifications caused by transient object names, whereas linear scanning techniques lack precision in distinguishing individual objects, even though they are free from those transient specifications. In this chapter, I aim to provide a new object identification scheme that would overcome the aforementioned limitations. I employ linear scanning in DADE to eliminate transient specifications caused by pointer chasing and introduce a new semantic information for naming objects that provides a narrow enough granularity. I give a detailed explanation on my approach in the following section.

# 3.3 The DADE Approach

As stated in Section 3.2, I introduce a new semantic information obtainable through linear scanning: *backtraces*, which, in my data anomaly detection engine DADE, is utilized to name objects.

# 3.3.1 Backtrace-Naming

A backtrace (also called call trace or traceback) is a backward list of active function calls that starts with the last function call. As a function is a unit of performing a specific task, the backtrace can be helpful in discerning the context of the current thread because it shows the tasks performed up until the last function call. In DADE I use backtrace-naming, which is naming objects with their allocation backtrace. In other words, whenever an object allocation occurs in a function, the object is named with the backtrace of that function, which would represent the context of the object's creation. For instance, Figure 3.2 depicts a backtrace of the kernel functions calling function bus\_add\_driver and the corresponding backtrace-name for the object allocated by the allocator function. This name would hold true for the object under any circumstance, barring a change in kernel code. Consequently, backtrace-names would persist over reboots, allowing DADE to reuse integrity specifications generated during a one-time offline inference.

The basis for the use of backtrace-naming in DADE for kernel integrity monitoring is the following two observations made on examining Linux kernels:

**O1.** Most Kernel objects are allocated through only a couple of fundamental object allocators.

**O2.** The kernel context when a kernel object is created reflects the object's characteristic during runtime.

**Identifying Kernel Objects** DADE applies linear scanning to identify kernel objects. In order to accomplish this, whenever an object allocation event occurs, DADE must gather relevant information through the virtual machine manager (VMM). Although there are various types of object allocators in the kernel, according to my examination, most are nothing but wrapper functions that ultimately call a couple of fundamental object allocators, as in **O1**. For example, the *alloc\_task\_struct\_node func-*

Figure 3.3: Granularity of backtrace-naming.

tion, which allocates task\_struct objects, internally calls the kmem\_cache\_alloc\_node function; in other words, it wraps the other function. Likewise, kmalloc is a wrapper function of the kmem\_cache\_alloc function. Therefore, DADE can gather most object allocation information of kernel objects by only tracking a couple of fundamental allocators.

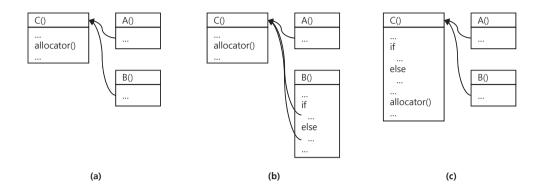

**Object naming** As mentioned before, DADE names objects with the backtrace at the moment of their allocation. This allows DADE to more elaborately distinguish objects than prior naming schemes in linear scanning, such as allocation-sites or data structures. For instance, lets assume the case of Figure 3.3.(a), where an object is allocated in function C. Under allocation-site naming, all objects would share the same name of *allocated-in-C*, whereas with backtrace-naming, objects would have two distinct names reflecting the function that called C. The name  $C \leftarrow A$  for objects allocated when C was called by A and  $C \leftarrow B$  for the case of C being called by B. Furthermore, as backtrace naming can distinguish function calls from different branches, as in the case of Figure 3.3.(b), it can give a higher resolution of objects in terms of granularity. Therefore, backtrace-naming is able to better reflect the subtle differences in kernel context than other existing naming schemes in linear scanning.

Generating Integrity Specifications Still, even with a higher resolution than prior linear scanning naming schemes, as backtrace naming cannot give every individual object their own unique name, a few objects are bound to share the same name, and thus the same integrity specifications. Observation O2, however, gives insight that objects created in a similar kernel context would have similar characteristics at runtime, and thus their sharing of a name is not necessarily a bad thing in this case. For instance, *inodes* are kernel objects used in various kernel functionalities, such as file systems, sockets or device drivers. They are allocated by the function *alloc\_inode* which is a wrapper function for *kmem\_cache\_alloc*, which I have found that could be called through 259 distinct backtraces. The reason for this is that, instead of generating and distributing inodes from a central component, each kernel component generates their own inode in accordance to their distinct kernel context. As a result, inodes sharing the same backtrace-name show similar characteristics, and thus the integrity specifications shared among them reflect the invariant properties based on these similarities.

# 3.3.2 Limitations of backtrace-naming

**Static objects** Kernel objects can be categorized into static objects and dynamic objects. Among these, only dynamic objects are created through allocators, and thus backtrace-naming can only be applied to these objects. However, as the memory location of static objects are fixed at compile time, their identification in memory is trivial. DADE incorporates these static objects via locating them at their predetermined addresses and names these objects with their addresses.

**Coverage for dynamic objects** During a more thorough investigation I found that even though most dynamic kernel objects are created by fundamental allocators, which are explicit as observed in **O1**, some data objects are allocated in an implicit way. For example, the kernel manages page objects, which contains memory properties of a continuous block of virtual memory called a page, in such a way that it first allocates

one large memory block, divides the block into page objects and indices them sequentially. Furthermore, objects created through arbitrary allocations or non-standard means of allocations would not go through the fundamental allocators. As these allocations are beyond the reach of DADE's current backtrace-naming scheme, it cannot incorporate the objects created in such a way. DADE may be able to encompass these implicit allocators by treating them explicitly but it is out of the scope of this chapter.

Representing kernel context Though backtrace-naming reflects the kernel context when an object is created, it does not necessarily reveal all relevant contexts; it cannot distinguish different contexts that reflect data values or express context not included in the function call trace at creation. For example, in Figure 3.3.(c) function C has an if-else statement before the allocator, and the condition is true when function C is called from function A and false when it is called from function B. The allocator, however, is on the outside of the if-else statement, so the backtrace name of any object allocated by the allocator does not reflect the different execution flow caused by this if-else statement because DADE extracts a backtrace at the moment the allocator is called. To resolve this limitation, DADE must be able obtain the runtime callstack, and I leave its inclusion as future work.

# 3.4 Design and Implementation

In this section, I describe my design and implementation of a prototype DADE. The prototype is implemented on an Arndale board [5], with an ARM Cortex-A15 citearm-cortexa 1.7 GHz dual-core processor and 2 GB RAM, which supports hardware virtualization extension. The prototype was integrated to a KVM [8] with Linux version 3.8.0, running VMs with Linux version 2.4.20 and 3.8.0.

Figure 3.4: Overview of DADE.

# 3.4.1 Security assumptions and threat model

DADE is designed to work from the VMM of a virtualization environment, monitoring the kernels of systems running within virtual machines (VM). It is assumed that the VMM is not contaminated by attacks and protected from malicious modification so that DADE would work as intended. DADE aims to detect attacks that alter any kind of kernel data, therefore attacks that do not alter any kernel data, such as altering kernel code, is considered out of scope. In addition, as will be described in the following sections, DADE selects to perform periodic scans to monitor the kernel data. This gives DADE only a probabilistic chance of detecting transient attacks [30]. This probability relies on the interval or randomness of periodic scans which in itself is a separate topic of research. Therefore transient attacks are considered to be out of scope for this chapter as well.

### 3.4.2 Overview

Figure 3.4 depicts the components of DADE and their interactions. While the kernel of the guest OS runs, the backtrace extractor obtains the backtrace-name whenever an

object is allocated and then stores the name along with the object's allocation address. At the same time, the dirty page tracer marks all memory pages where write operations occur. Then, the integrity verifier periodically scans objects residing in the marked pages, which is easily done by extracting object values from the addresses provided by the backtrace extractor. Then, it periodically verifies the integrity of the extracted objects by confirming whether or not they follow pre-inferred integrity specifications, which are generated with the help of Daikon [21], a machine learning tool that infers invariant properties of programs.

DADE assumes that the kernel code is not altered during runtime, that its source code is available a priori and that there is a way to securely bootup a clean kernel for each launch of the system. These assumptions are typically acheivable to some point in virtualization environments, which, fortunately, DADE is built on.

# 3.4.3 Generating integrity specifications

Unlike Gibraltar, DADE only needs a one-time offline inference phase to generate integrity specifications due to the fact that the backtrace-names adopted in DADE are persistent across reboots. The one-time inference phase itself is similar to that of Gibraltar. First of all, DADE finds all dynamically allocated objects in the memory of a benign kernel with the help from fundamental allocators and the backtrace extractor. This provides DADE with the allocation address and backtrace-name of each allocated object. The next step is to identify the data structures of the identified objects and then associate objects with their corresponding data structures in order to properly interpret the contents of the object. DADE achieves this by gathering the address and type information of objects found in a memory traversal and then matching these object addresses with the addresses of objects found through the backtrace extractor. As matching these objects enables DADE to associate type information with backtrace-named objects, it only needs to be done once during the one-time inference. After this

is done, by utilizing the type information of objects, DADE records the values of its identified objects in various work cases, such as right after finishing a reboot or during the execution of a strenuous benchmark. These records provide DADE with the list of observed values of data objects in various kernel contexts that are commonly encountered during runtime. Then, DADE groups objects on the basis of their assigned backtrace-names. Each group with the same backtrace-name is treated in Daikon as an individual input instance and as a result, Daikon produces integrity specifications in regards to backtrace-names. These generated specifications are then enforced at run-time (supported by **O2** in Section 3.3.1).

# 3.4.4 Extracting backtraces

Based on **O1** in Section 3.3.1, DADE can extract most object allocation information by trapping a couple of fundamental allocators such as *kmem\_cache\_alloc*, *\_\_kmalloc*, or *\_\_vmalloc\_node\_range*.

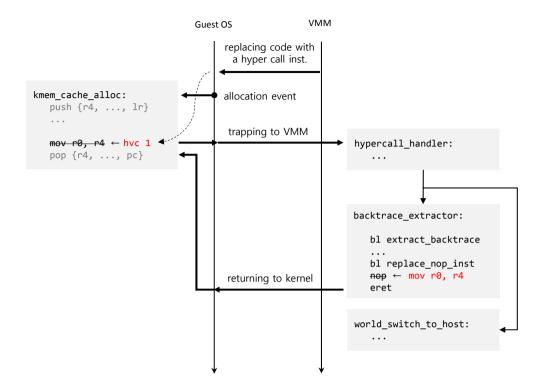

Early in the kernel bootup sequence, DADE replaces an instruction in the exit code block of these fundamental allocators with a hypercall instruction, which traps to the VMM, as seen in Figure 3.5. Then, when a fundamental allocator is called, the inserted hypercall transfers control over to the hypercall handler in the VMM, which calls the backtrace extractor. The backtrace extractor ascends the stack and retrieves the current backtrace along with the allocation address of the allocated object and stores them as a tuple.

In order to retrieve a backtrace, the extractor must go through the stack and retrieve the return addresses from the stack frames of each funtion call. The most convenient way to accomplish this is to utilize frame pointers due to the fact that they can provide the backtrace extractor with the exact size of each stack frame. Unfortunately, optimizations that are commonly found in modern compilers usually omit frame pointers and related instructions in order to reduce performance overhead. Thus, the target ker-

Figure 3.5: The process of trapping an allocation event in DADE.

nel needs to be re-compiled with an option similar to *-fno-omit-frame-pointer* in GCC, which would force the compiler to keep frame pointers. If one wishes to apply the optimizations that omit frame pointers, they can achieve the same effect of DADE by analyzing, in accordance to the processor's calling convention, the binary of the kernel alongside the program stack for the retrieval of backtraces. In DADE, I compiled the kernel so that it would keep frame pointers.

When the backtrace extractor finishes, DADE must properly execute the original kernel instruction that was replaced with the hypercall instruction at bootup before the hypercall handler returns control back to the kernel. This is done by keeping a *nop* instruction in the exit code block of the backtrace extractor and executing the original kernel instruction instead of the *nop* instruction at runtime. This is depicted in Figure 3.5. However, this workaround is not always possible. For instance, instructions

dealing with memory or banked registers would produce different results because the instructions would operate on the memory and register contents of the VMM rather than those of the kernel. To avoid such problems, the instruction to be replaced with a hyper call must be chosen carefully.

## **Optimizing backtrace extraction**

As mentioned before, in DADE, whenever an object allocation event transpires, control transfer between the kernel and the VMM must occur because DADE traps every kernel object allocation event to keep track of live kernel objects. Normally when a trap happens, the hypercall handler performs a world switch so that the data in registers and memory would reflect the state of the VMM, and thus handing control over to the VMM. World switches are, however, expensive operations due to the fact that a considerable amount of state needs to be saved and restored. As DADE needs to trap every allocation event in the kernel, this overhead for world changes could potentially cripple the guest VM's performance, which, in turn, would render DADE unsuitable for practical use. In order to minimize this overhead, DADE deploys a conditional branch in the hypercall handler, as seen in Figure 3.5, so that when the current hypercall is just called for recording an object allocation event, the handler directly calls and executes the backtrace extractor without performing a world switch. This optimization reduces the time needed for handling a hypercall for object identification to 321 CPU cycles, as shown in table 3.1, whereas without this optimization, 2,270 cycles would be needed just for a single round-trip to the VMM [18].

Another optimization in DADE for backtrace extraction is related to memory pressure. DADE has to manage over ten thousand allocation data at runtime with only a limited amount of memory space. Thus, in my implementation, DADE stores backtracenames as hash values. For example, in Figure 3.2, we can compute the hash value of the backtrace-name by running a hash function using each address of the subroutine

as its inputs. The resulting hash value would be 0xb95260f4. This hashing scheme is also adopted when generating an integrity specification in inference phase. Though collision within a hash could possibly lead to objects having different properties to share the same object name, which could lead to false positives during detection, considering the false positive rate from the evaluation in Section 3.5.1, the effect could be considered negligible.

## 3.4.5 Verifying object integrity

For efficiency, DADE enforces integrity specifications only on objects whose contents might have changed since the last enforcement. In other words, it only verifies the integrity of objects residing on *dirty* pages. In order to do so, DADE initially marks every kernel memory page as not dirty. Then, when any content of a page is modified, it flags the page as dirty. This is implemented by leveraging extended page tables supported by hardware virtualization extensions. DADE sets the whole kernel memory as read only, then any write towards a kernel memory page would be prohibited and generate a page fault, which is handled by the VMM. When such an event occurs, DADE flags the page as dirty and enables writes on the page to prevent any further page faults on an already dirty page. Once DADE performs a scan for data anomaly detection, it marks all pages as not dirty and starts this process all over again.

To fully capitalize on this dirty page optimization, DADE keeps track of not only the backtrace-names of objects but also their allocation addresses, which makes it possible to extract the object values in dirty pages with a single linear scan and check their corresponding integrity specifications.

## 3.4.6 Deallocations

Any object that is allocated might be deallocated at some point at runtime, and therefore DADE must be able to handle deallocation events to properly locate and verify objects. DADE accomplishes this by instrumenting hypercall instructions into fundamental deallocator functions just as it has done with allocators. With this, DADE generates a list of the backtraces of deallocation events along with the addresses of the deallocated objects. Then, at the start of the each data anomaly detection, it cross examines newly deallocated addresses with the addresses of identified objects and deletes information it gathered on objects that have a matching address. To handle reallocation events, which are allocations following deallocations, DADE deletes only the oldest object information that has a matching address per deallocation event.

#### Inference from deallocation information

DADE, as it has done with allocation information, could leverage deallocation information, such as the backtrace of a deallocation event or the address of a deallocated object, so that it could infer invariant properties related to object deallocations. Furthermore, by utilizing allocation and deallocation information together, DADE could infer invariant properties related to an object's life cycle, which is a hidden yet fundamental property of an object. For instance, such an invariant property might dictate where, in kernel code, an object must be deallocated and an integrity specification reflecting this property could potentially detect attacks that involve an abnormal removal of a kernel object, such as those used in loadable kernel module (LKM) hiding attacks.

## **Example integrity specification with deallocation information**

As an example of such invariant properties, I introduce a new simple invariant property I1, which is universally applicable to kernel objects that only have a single legitimate deallocation event.

**I1.** objects allocated by an allocator with  $Backtrace_A$  are only deallocated by a deal-locator with  $Backtrace_B$ .

In practice, when DADE performs its off-line inference, in addition to backtrace-

names and values of objects, it also retrieves the addresses of objects coupled with their allocation backtraces and deallocation backtraces. This information is packaged and given to Daikon as a custom input format so that Daikon may acknowledge it is handling additional allocation and deallocation information. When Daikon is handling such inputs Daikon sees if it can infer I1 from the given inputs. This inference is done by first building sets of allocation addresses that share the same backtrace-names; that is to say, Daikon groups the addresses of objects allocated by the same allocator that was called in the same kernel context. Data objects from different bootups of the kernel are grouped seperately as they probably would not share the same object addresses. This grouping is done similarly for deallocation addresses and deallocation event backtraces as well and are matched with the allocation backtrace group from the same kernel execution. After the sets are all built and matched, Daikon examines them to ascertain if a set of deallocation addresses with the same  $Backtrace_B$ , is the unique subset for a set of allocation addresses with the same Backtrace<sub>A</sub>; in other words, it determines if there is no other subset but the one. This relation between these sets imply that all objects allocated by  $Backtrace_A$  are observed to only be deallocated by  $Backtrace_B$ , and therefore when such a relationship between sets are found, Daikon produces the invariant property I1 and its corresponding integrity specification.

## Enforcing deallocation related integrity specifications at runtime

In order for these integrity specifications reflecting I1 to be enforced at runtime, it must be done when DADE handles deallocation events. When DADE is about to resolve a recorded deallocation event and delete the corresponding object information it had stored, it links deallocation event backtraces with their corresponding allocation event backtraces by finding a match between the addresses of the objects related to the events. For instance, an object that was allocated at  $Address_X$  with  $Backtrace_A$  would be linked to an deallocation event that deallocated  $Address_X$  with

$Backtrace_B$ , as both events are related to the object allocated at the same address. After the link is made, DADE verifies one last integrity specification I1, if it exists for the allocation backtrace. In the case of the specification being present, DADE compares the backtraces of the linked object's allocation and deallocation events against those in the specification. Any discrepancy between them would indicate that the object was deallocated in an abnormal way.

## 3.5 Evaluation

In this section, I evaluate DADE in terms of its practical performance and its ability to detect data anomalies.

#### 3.5.1 Performance

The performance of DADE is evaluated in four aspects, the generation time of integrity specifications, false positive rate, the induced delay at boot-up and the detection performance. As discussed in the limitations of backtrace-naming in Section 3.3, though DADE can trivially encompass the static region of the kernel memory, my approach holds little advantage over previous approaches handling the static region of kernel memory because its main idea is built around improving the locating of dynamically allocated kernel objects. Therefore, for clarity on the effects of DADE, evaluations in this section report only on these dynamic objects. The performance evaluations were made on Linux 3.8.0.

## **Generation time of integrity specifications**

In order to generate integrity specifications, as detailed in Section 3.4, DADE extracts data object values from an uncontaminated kernel and associates object names with the values so that it can utilize Daikon to infer the invariant properties of the objects.

For this process, I extract kernel data in various kernel states, such as when the boot-up sequence just finished, when the kernel is in an idle state and when a benchmark (such as Imbench [29], SPEC2006 [11]) is running. I have collected 2 to 3 sets of object values from various situations, cumulating in 15 sets of object values per inference. With these records of object value changes, I run the invariant property inference module of Daikon to infer invariant properties and generate integrity specifications, which took an average of 54 minutes. Note that this whole process is done offline, so the runtime performance of DADE is not affected in any way.

### **False positives**

As DADE automatically generates integrity specifications from kernel data acquired in various situations, its specifications are confined by the information embedded in the sets of data used for their generation. In other words, DADE might report legitimate kernel data values found in rare kernel events as a data anomaly if the event was not captured for its generation of specifications. These false positives in data anomaly reports are artifacts of generating specifications from incomplete sets of kernel data values and shows a side of DADE that may be improved with better sets of kernel data values. To measure the amount of false anomaly reports, I ran a benign workload, which includes running the aforementioned benchmarks [29, 11] in different configurations or running benign programs (ProFTPD [10], gcc [7], bzip2 [6]), and recorded any data anomaly report made from DADE over 30 minutes. During this experiment, 0.15% of the specifications were related in false reports. Unfortunately, as I have no way of exactly replicating the benign workload of Gibraltar which reported a 0.65% false positive rate, I cannot fairly claim better accuracy over it. However, note that DADE achieves its goal in improving aspects of Gibraltar while still having a comparably low false positive rate.

Table 3.1: Overhead for object identification and naming during kernel boot in DADE

| The number of allocations               | 186,132     |

|-----------------------------------------|-------------|

| The number of deallocations             | 156,367     |

| The number of live objects              | 29,765      |

| Avr. CPU cycles per trap                | 321         |

| Avr. CPU cycles per backtrace-naming    | 140         |

| Total spent CPU cycles of traps         | 116,440,503 |

| Total spent time(ms) of traps at 1.7GHz | 68.49       |

## Induced delay at boot-up

As a means to evaluate the impact DADE's object identification and naming scheme has on system performance, I measured the delay caused by the backtrace extraction and object naming that is handled during the boot-up of a guest VM. This was measured through the performance monitor equipped on ARM processors and Table 3.1 shows the results. During the guest VM boot-up, there were 342,499 traps caused by the hyper call instrumented in fundamental (de)allocators, ultimately delaying the boot-up sequence by 68.49ms. This is 1.5% of the average boot-up time 4.5s. Note that, as mentioned in Section 3.2, without the backtrace naming scheme DADE introduces, Gibraltar would need to generate integrity specifications at every system boot-up, inducing a delay of 56 minutes (reported in their paper [12]) or 54 minutes (from my experimental results in Section 3.5.1).

## **Detection performance**

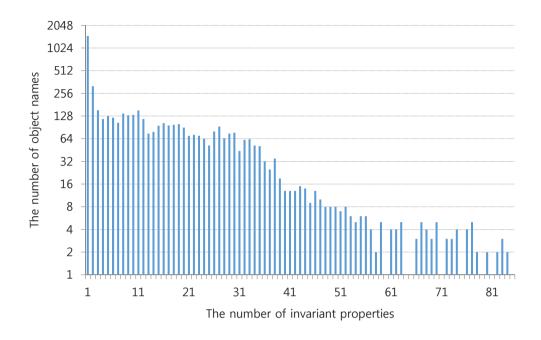

As DADE runs data anomaly detection periodically, the interval between scans is directly related to the performance and security of the whole system. The time it takes DADE to perform a single scan is proportional to the number of objects that need to be verified and the amount of invariant properties related to each object. Figure 3.6

Figure 3.6: Number of invariant properties for unique object names.

depicts the number of object names (Y-axis) that have certain numbers of properties (X-axis) in my prototype. A total of 68,854 invariant properties were inferred for a total of 5,177 unique object backtrace names, so each object name had an average of 13.3 invariant properties. Therefore, when DADE needs to verify N objects, it would perform an average of 13.3N comparisons to detect data anomaly.

During a scan in DADE, the number of objects that need to be checked depends on the number of objects that were created or changed. DADE narrows down, as described in Section 3.4, the objects it performs data anomaly detection by only scanning the objects within a memory page that was marked dirty. As seen in table 3.1, right after kernel boot-up, DADE identified and verified 29,865 objects, which resided on 9,854 dirty pages. This initial scan took 900ms. After this, DADE performed another scan after an execution of a benchmark and found that 17604 objects were located on 1,232 dirty pages. This additional scan only took 159ms. This result is due to the dirty page optimization of DADE. Initially, DADE must go through every object because the

pages they reside on will all be marked dirty during boot-up. However, after the initial scan, the number of objects needing verification decreases as only the pages containing object changes will be scanned.

## 3.5.2 Data anomaly detection

Even though DADE might show practical runtime performance, if it is unable to detect data anomalies, its performance would be for nothing. In order to evaluate the security aspect of my approach, I show DADE's performance against various kernel attacks. For more precise detection, specifications for objects in the static region of the kernel are included in the evaluations of this section.