#### Ph.D. DISSERTATION

#### **Study on Binary Resistance Switch Array**

### for Neuromorphic Hardware

by

Guhyun Kim

February 2020

DEPARTMENT OF MATERIALS SCIENCE AND ENGINEERING

**COLLEGE OF ENGINEERING**

SEOUL NATIONAL UNIVERSITY

# Study on Binary Resistance Switch Array for Neuromorphic Hardware

Advisor : Prof. Cheol Seong Hwang

by

Guhyun Kim

A thesis submitted to the Graduate Faculty

of Seoul National University in partial fulfillment of the requirements

for the Degree of Doctor of Philosophy

Department of Materials Science and Engineering

December 2019

#### Approved

by

Chairman of Advisory Committee :Sang Bum KimVice-chairman of Advisory Committee :Cheol Seong HwangAdvisory Committee :Dongsuk JeonAdvisory Committee :Doo Seok JeongAdvisory Committee :Byung Joon Choi

#### Abstract

Resistance switch array is a strong contender for next-generation memory. A resistance switch has low resistance state or high resistance state. Switching between states are stimulated by electric signal such as application of voltage or current. With crossbar array configuration, resistance switch array reaches to high integration density of  $4F^2$  where F means minimum feature size. Analog resistance switches are also have been proposed, but most of them need very precise control of conductance. Additionally, at least one of their potentiation or depression is non-linear to pulse number (or pulse length).

Resistance switch array is also able to realize matrix-vector multiplication, or parallel operation. In other words, the current response to an applied input voltage vector naturally captures the conductance matrix-voltage vector multiplication.

Simulating resistance switch array is an efficient method to analyze its property. The most popular simulation uses Newton-Raphson methods for resistance array simulation, but this method consumes large calculation costs. As an alternative, an artificial neural network was applied for the resistance switch simulation. An artificial neural network was utilized in the behavior inference of a random crossbar array ( $10 \times 9$  or  $28 \times 27$  in size) of nonvolatile binary resistance-switches (in a high resistance state (HRS) or low resistance state (LRS)) in response to a randomly applied voltage array. The employed artificial neural network was a multilayer perceptron (MLP) with leaky rectified linear units. This MLP was trained with 500,000 or 1,000,000 examples. For

each example, an input vector consisted of the distribution of resistance states (HRS or LRS) over a crossbar array plus an applied voltage array. That is, for a  $M \times N$  array where voltages are applied to its M rows, the input vector was  $M \times (N+1)$  long. The calculated (correct) current array for each random crossbar array was used as data labels for supervised learning. This attempt was successful such that the correlation coefficient between inferred and correct currents reached 0.9995 for the larger crossbar array. This result highlights MLP that leverages its versatility to capture the quantitative linkage between input and output across the highly nonlinear crossbar array. Additionally, MLP accelerates simulation 8 times faster compared to Newton-Raphson method.

With its availability of parallel operation, resistance switch array is used in various parts of neuromorphic hardware, which aims to synthesize hardware mimicking neural networks. The typical application of resistance switch array is an artificial synapse array. Because matrix-vector multiplication in resistance switch array is similar to that in neural network, neuromorphic hardware can be accelerated by implementation of a resistance switch array as an artificial synapse array.

In this paper, a learning algorithm suitable for binary resistance switch array is proposed. This algorithm is referred to as the Markov chain Hebbian learning algorithm. The algorithm pursues efficient use in memory during training in that: 1) the weight matrix has ternary elements (-1, 0, 1) and 2) each update follows a Markov chain—the upcoming update does not need past weight values. Additionally, the ternary synaptic units are easily realized by a pair of resistance switches, so that the Markov chain Hebbian learning algorithm is appropriate for training binary resistance switch array used as synapse array. The algorithm was verified by two proof-of-concept tasks: image (MNIST and CIFAR-10 datasets) recognition and multiplication table memorization. Particularly, the latter bases multiplication arithmetic on memory, which may be analogous to humans' mental arithmetic. The memory-based multiplication arithmetic feasibly offers the basis of factorization, supporting novel insight into memory-based arithmetic.

Another application is using a resistance switch array as a contentaddressable memory (CAM) as lookup table (LUT) in topology block. The LUT stores the entire connectivity among neurons. When a spike occurs from a neuron, the topology block searches the LUT and finds the destination neurons and synapses to update. Resistance switch-based CAM (RCAM) satisfies fast search ability, high integration density and low static energy consumption, and thus it is appropriate for LUT.

RCAM, however, has a low data density due to the use of a pair of resistance switches for a single bit of contents (0.5 bit/switch) in comparison with resistive random access memory (1 bit/switch). In this paper, we propose a new type of RCAM referred to as combination-encoding CAM (CECAM). In *N*-CECAM, a single unit consists of *N* high and *N* low resistance state switches whose combination collectively represents binary contents, yielding a data density of approximately 0.85 bit/switch when N = 10, for instance. The key to CECAM is the encoding of an *n*-bit search key as a 2*N*-digit key and its decoding. To this end, we propose a simple algorithm for encoding and decoding and its implementation in digital circuitry. Keywords: Neuromorphic engineering, resistance switch array, multilayer perceptron, Markov chain, content-addressable memory

Student Number: 2015-20801

Guhyun Kim

# **Table of Contents**

| Abstra   | ct                                             | i                |

|----------|------------------------------------------------|------------------|

| Table of | of Contents                                    | V                |

| List of  | Tables                                         | ix               |

| List of  | Figures                                        | X                |

| List of  | Abbreviations                                  | xviii            |

| 1. In    | troduction                                     | 1                |

| 1.1.     | Resistance switch array                        | 1                |

| 1.2.     | Resistance switch array application in         | neuromorphic     |

| hardy    | vare                                           | 4                |

| 1.3.     | Bibliography                                   | 7                |

| 2. Ar    | tificial neural network for response inference | of a nonvolatile |

| resista  | nce-switch array                               |                  |

| 2.1.     | Introduction                                   |                  |

| 2.2.     | Description of model system                    | 12               |

| 2.3.     | Description of artificial neural network       | 14               |

| 2.4.     | Training and test datasets                     | 15               |

| 2.5.     | Training results                               | 16               |

| 2.6.     | Conclusions                                    |                  |

| 2.7.  | Bibliography2                                               | 2 |

|-------|-------------------------------------------------------------|---|

| 3. Ma | arkov chain hebbian learning algorithm with ternary synapti | c |

| units |                                                             | 5 |

| 3.1.  | Introduction                                                | 5 |

| 3.2.  | Model description                                           | 8 |

| 3.2   | 2.1. Network structure and energy                           | 8 |

| 3.2   | 2.2. Field application and update probability               | 3 |

| 3.3.  | Implementation of the MCHL algorithm on hardware            | 6 |

| 3.3   | 3.1. Field-programmable gate array                          | 6 |

| 3.3   | 8.2. Resistance-based random access memory                  | 6 |

| 3.4.  | Applications4                                               | 0 |

| 3.4   | 1.1. Image recognition                                      | 0 |

| 3     | 3.4.1.1. Implementation on a general-purpose computer       | 0 |

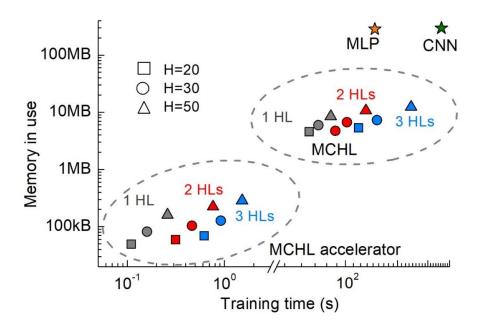

| 3     | 3.4.1.2. MCHL accelerator                                   | 9 |

| 3.4   | .2. Multiplication table memorization and prime             |   |

| fac   | torization                                                  | 0 |

| 3.5.  | Discussion                                                  | 0 |

| 3.6.  | Appendix 6                                                  | 4 |

| 3.6   | 5.1. Derivation of stochastic activity of a neuron          | 4 |

| 3.6   | 5.2. Calculation of update probability                      | 5 |

| 3.6   | 5.3. Properties of Markov chain in MCHL                     | 6 |

3.6.4. Effect of update probability and temperature parameter on training 70

| 3.0   | 6.5.  | Handwritten digit recognition                              | 72 |

|-------|-------|------------------------------------------------------------|----|

| 3.0   | 6.6.  | MCHL accelerator in detail                                 | 75 |

| 3.0   | 6.7.  | Multiplication table memorization                          | 80 |

| 3.0   | 6.8.  | Prime factorization                                        | 83 |

| 3.0   | 6.9.  | Direct search factorization                                | 84 |

| 3.7.  | Bił   | bliography                                                 | 84 |

| 4. C  | ombi  | nation-encoding content addressable memory                 | 89 |

| 4.1.  | Int   | roduction                                                  | 89 |

| 4.2.  | Co    | mbination-encoding content addressable memory              | 91 |

| 4.2   | 2.1.  | Algorithm for combination encoding                         | 97 |

| 4.2   | 2.2.  | Implementation of encoding circuit10                       | 00 |

| 4.3.  | Par   | callel search of <i>N</i> -CECAM domains10                 | 03 |

| 4.4.  | Alg   | gorithm for content decoding and circuit implementation 10 | 06 |

| 4.5.  | Dis   | scussion10                                                 | 09 |

| 4.6.  | Co    | nclusion1                                                  | 14 |

| 4.7.  | Ap    | pendix 1                                                   | 14 |

| 4.8.  | Bił   | pliography1                                                | 16 |

| 5. C  | onclu | 1sion12                                                    | 20 |

| Curri | culur | n Vitae12                                                  | 22 |

| List of publications   |     |

|------------------------|-----|

| -                      |     |

| Abstract (in Korean)   | 126 |

| Abstract (III Koreall) |     |

## **List of Tables**

| Table 2.1. Parameters of model switch                                           | 13     |

|---------------------------------------------------------------------------------|--------|

| Table 3.1. Symbols                                                              | 32     |

| Table 3.2. MCHL algorithm for handwritten digit classification                  | 74     |

| Table 3.3. MCHL algorithm for multiplication table memorization                 | 82     |

| Table 4.1. Truth table of encodings of 4-bit integers as resistor configuration | ations |

| ( <i>N</i> = 3)                                                                 | 99     |

| Table 4.2. Comparison to previous work                                          | 113    |

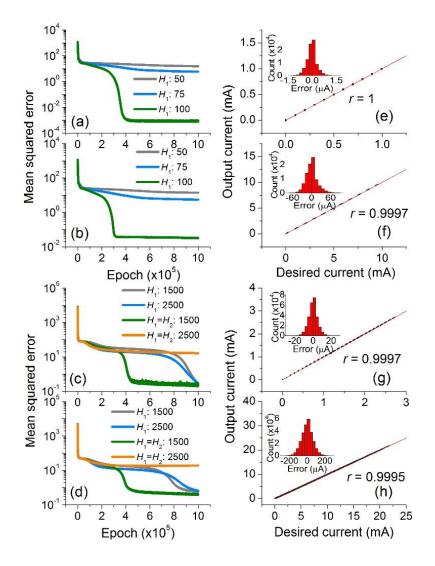

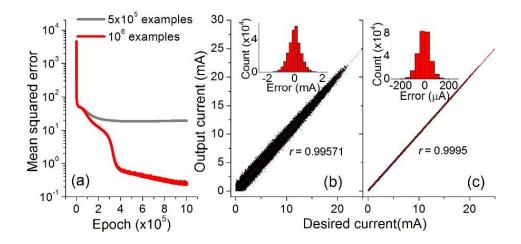

- Figure 2.2. Inference-error reduction while training a network with the dataset of a 10 × 9 crossbar array of (a) Type A and (b) Type B switches.

Their output results (inferred currents) for the entire 10,000 test datasets after successful training (green lines) are plotted against the desired currents in (e) and (f), respectively. The histogram of

|             | the error (the difference between inferred and desired currents) for       |

|-------------|----------------------------------------------------------------------------|

|             | each case is shown in the inset. The red solid lines denote the            |

|             | perfect match of inference with the desired (correct) results. The         |

|             | results are shown for a 28 $\times$ 27 crossbar array of (c) Type A and    |

|             | (d) Type B switches, and their statistics in (g) and (h),                  |

|             | respectively                                                               |

| Figure 2.3. | (a) Training the network (2,500 units in each of two hidden layers)        |

|             | with 500,000 and 1,000,000 examples for Type B switch. The                 |

|             | capability of response inference is shown for the network trained          |

|             | with (b) 500,000 and (c) 1,000,000 examples. The insets address            |

|             | the distribution of inference-error                                        |

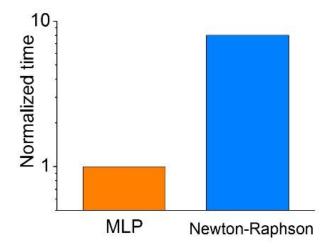

| Figure 2.4. | Comparison of run time for the proposed method and Newton-                 |

|             | Raphson method                                                             |

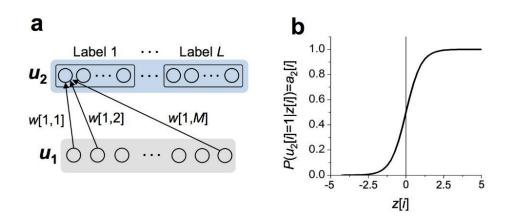

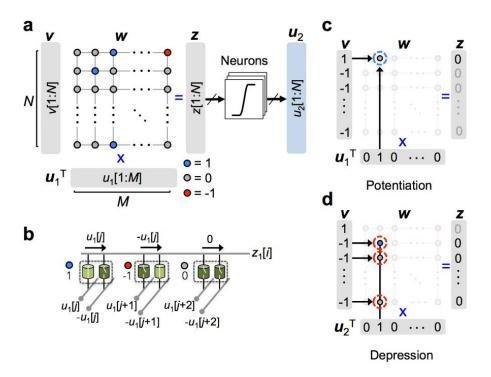

| Figure 3.1. | MCHL algorithm working principle. (a) Basic network of $M$ input           |

|             | and N output binary stochastic neurons ( $u_1$ and $u_2$ : their activity  |

|             | vectors). (b) Behavior of $P(u_2[i] = 1)$ with $z[i]$ when $b[i]=0$ . This |

|             | probability is identical to the deterministic activity $a_2[i]$ of the     |

|             | neuron                                                                     |

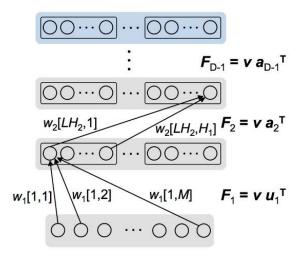

| Figure 3.2. | Network with hidden layers. $F_2$ and $F_{D-1}$ denote a field matrix for  |

|             | <i>w</i> <sub>2</sub> and <i>w</i> <sub>D-1</sub>                          |

| Figure 3.3. | Memory-centric illustration of a neural network. (a) Graphical             |

|             | description of the weight matrix $w$ that determines the correlation       |

|             | between the input activity $u_1$ and output activity $u_2$ . The grey      |

|             | vertical and horizontal lines denote word and bit lines,                   |

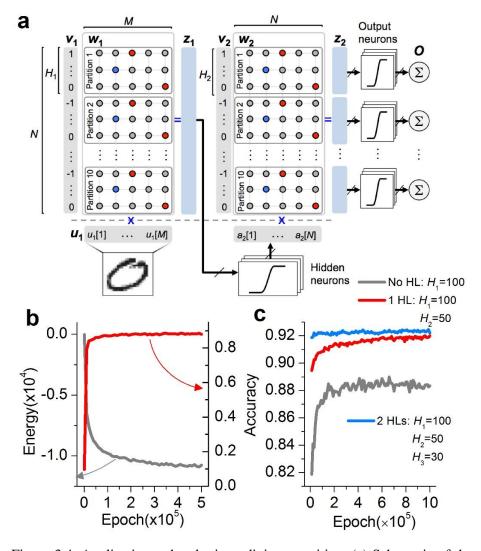

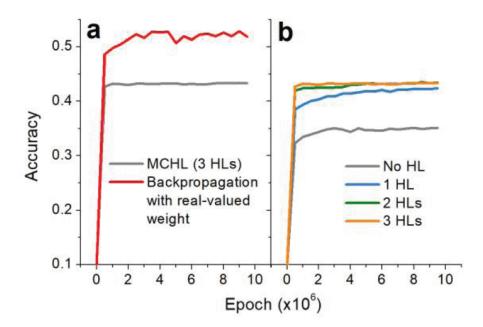

Figure 3.4. Application to handwritten digit recognition. (a) Schematic of the network architecture for handwritten digit recognition. A single HL is included. The matrix  $w_1$  first maps the input vector  $u_1$  to the hidden neurons. The array  $a_2$  is taken as an input vector to  $w_2$  that maps the input vector to the output neurons. The write vector  $v_1$  has 10 (the number of labels) buckets, each of which has  $H_1$  elements, i.e.  $N = 10H_1$ . Each thick arrow indicates an input vector to a group of neurons (each neuron takes each element in the input vector). (b) The increase of recognition accuracy (red curve) and corresponding decrease of energy (grey curve) with training epoch. The trained network is a single-layer network (H=100). (c) Classification accuracy change in due course of training with

xii

| network depth ( $H_1$ = | $100, H_2 = 50,$ | $H_3=30$ ) | 44 |

|-------------------------|------------------|------------|----|

|-------------------------|------------------|------------|----|

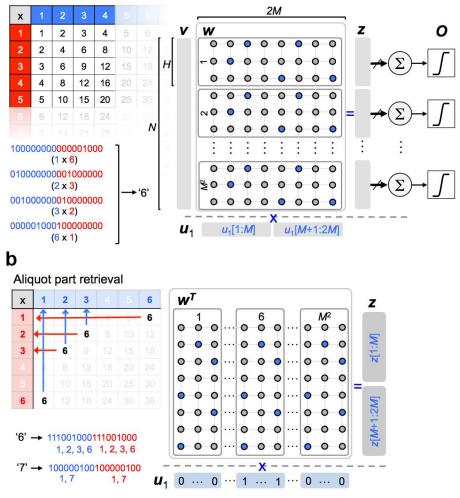

- Figure 3.8.Multiplication table memorization and aliquot part retrieval. (a) Network architecture for multiplication table memorization. The

numbers in the range 1 - M are described by one-hot vectors. Any two of total  $M^2$  numbers are combined to form an input vector  $u_1$  $(u1 \in \mathbb{Z}2M; u1i \in 0, 1)$ ; for instance, when  $M = 9, u_1$  for one and six is [10000000000000000], where the first and last 9 bits indicate one and six, respectively, as shown in the figure. The correct answer serves as the label of chosen numbers; there are  $M^2$ labels in total. Each label (bucket) has H elements so that the write vector v is a  $M^2H$  long vector that is adjusted given the correct label. Given entire pairs of numbers in the table and their multiplication results, the matrix  $w (w \in \mathbb{Z}M2H \times 2M)$  is adjusted. P + 0, P - 0, b[i], and  $\tau$  were set to 1, 0, 3, and 0.001, respectively (b) Network architecture of aliquot part retrieval given the matrix w. The transpose of  $w(w^{T})$  finds the entire aliquot parts of a given number in a parallel manner in place. For instance, for number '6', an input vector  $u_1$  ( $M^2H$  long vector) has a single nonzero bucket (6th bucket) that is filled with ones. The output vector z is [111001000] [111001000], indicating the sum of four one-hot vectors  $(1^{2} + 2^{2} + 3^{2} + 6^{2})$ —each of them is an aliquot part of 6. For prime numbers, the output vector includes only two 1's (1 and its own number) so that prime numbers can readily be found; for instance, 7 results in [100000100]100000100] as shown in the figure......55

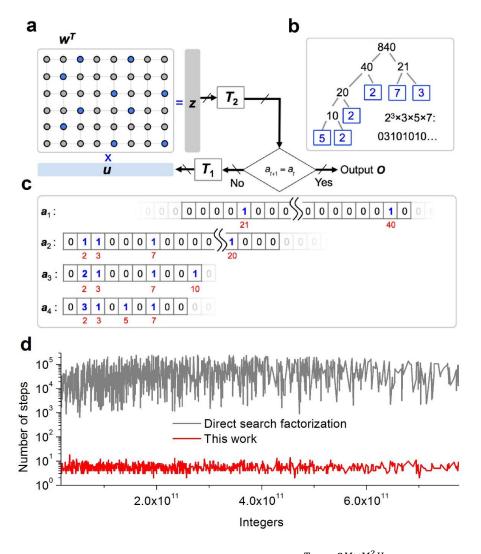

Figure 3.9.Prime factorization. (a) Memory ( $wT \in \mathbb{Z}2M \times M2H$ ) based iterative and parallel search for prime factors. Given an input

vector *u* standing for a certain number *n*, the matrix multiplication  $w^{T}u$  outputs vector z ( $z \in \mathbb{Z}2M$ ;  $zi \in 0, 1$ ) that reveals one pair of its factors—except 1 and itself—z[1:M] and z[M+1:2M] whose product yields *n*. Operator  $T_2$  adds these two one-hot vectors, resulting  $a_t$  ( $at \in \mathbb{Z}M$ ). The iteration terminates upon no further change in a other than a[1]. Otherwise, operator  $T_1$  transforms  $a_t$ to u, and the next cycle continues. (b) Prime factorization of 840 = $2^3 \times 3 \times 5 \times 7$  with a matrix  $w^T$  (M = 100, H = 30). The first iterative step outputs  $a_1$  in (c); the address of each element indicates a factor, e.g. the 21st element, a[21], means a factor of 21, and the element value its exponent. Only  $a_1[21]$  and  $a_1[40]$  in  $a_1$  except  $a_1$ [1] are nonzero, indicating 21×40. The second iteration outputs  $a_2$  whose nonzero elements are  $a_2[2], a_2[3], a_2[7], and <math>a_2[20] (= 1, -1)$ 1, 1, and 1, respectively), implying  $2^2 \times 10 \times 21$ . The third iteration respectively sets  $a_3[2]$ ,  $a_3[3]$ ,  $a_3[7]$ , and  $a_3[10]$  to 2, 1, 1, and 1, i.e.  $2^{2} \times 3 \times 7 \times 10$ . The forth iteration sets  $a_{3}[2], a_{3}[3], a_{3}[5]$ , and  $a_{3}[7]$  to 3, 1, 1, and 1, i.e.  $2^3 \times 3 \times 5 \times 7$  and an additional iteration does not alter other elements than *a*[1] such that the prime factorization is completed. (d) The number of factorization steps until prime factors for the integers  $(1.62884 \times 10^{10} - 7.75541294 \times 10^{11})$ . The

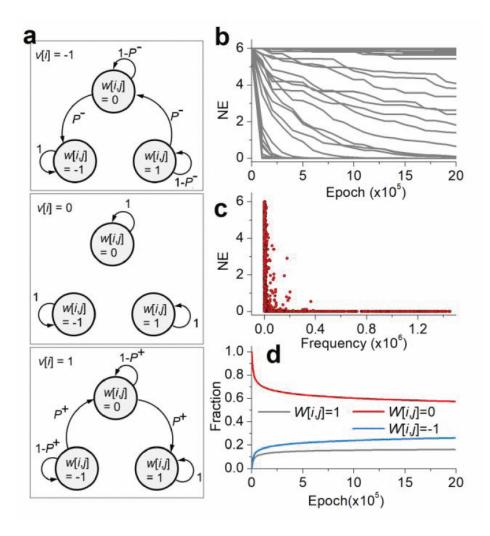

- Figure 3.12. (a) State transition diagram for a weight element given three different v[i] values. (b) NE change (for 100 weight elements randomly sampled) monitored when training a network with the MNIST dataset. (c) The 100 final NE values plotted with respect to the frequency of non-zero input during the training phase. (d) Probability distribution over w[i, j] = 1, 0, 1 with training epoch.69

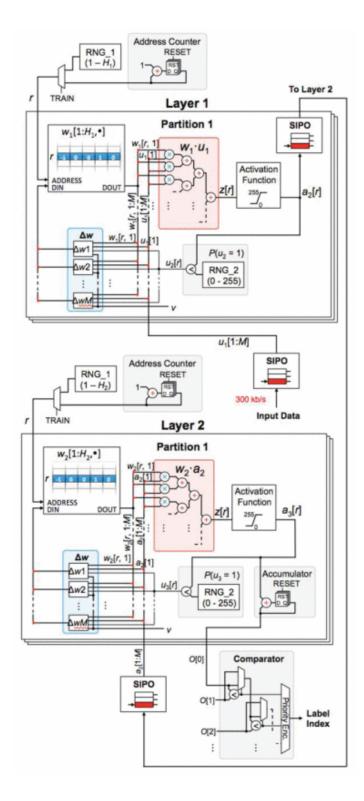

- Figure 3.14. Block diagram of the MCHL accelerator......79

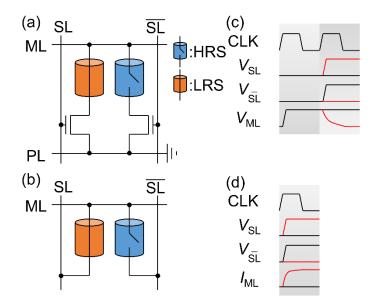

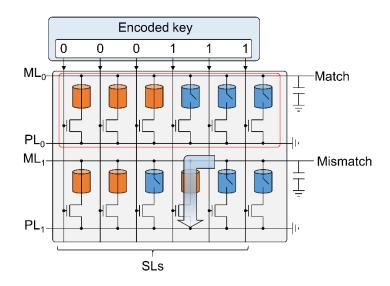

Figure 4.2. (a) Schematic of 3-CECAM (N = 3). A single unit consists of N

|            | HRS and N LRS switches. SA and PE mean a sense amplifier and               |

|------------|----------------------------------------------------------------------------|

|            | priority encoder, respectively. (b) Current responses to a given           |

|            | encoded key upon a match and mismatches. Matching allows the               |

|            | minimal current response (first row)96                                     |

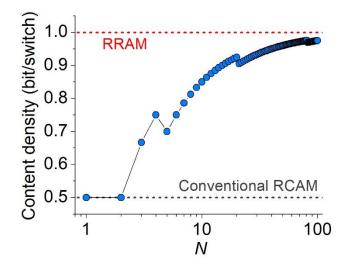

| Figure 4.3 | . Content density of $N$ -CECAM with $N$ in comparison with the            |

|            | conventional RCAM and RRAM. The kinks arise from the floor                 |

|            | function in (1)96                                                          |

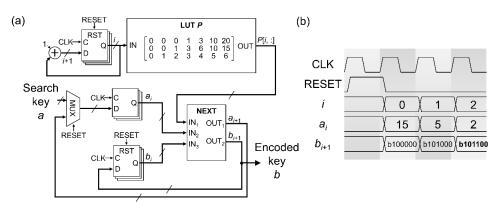

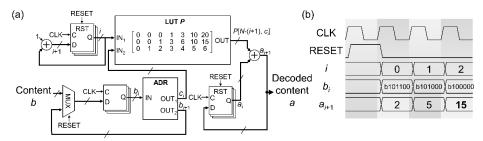

| Figure 4.4 | . (a) Block diagram of an encoding circuit for 3-CECAM. (b)                |

|            | Timing diagram for encoding a search key of 15 as a 6-digit key of         |

|            | 101100                                                                     |

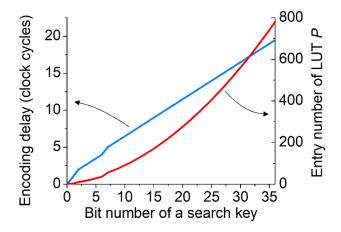

| Figure 4.5 | . Encoding delay and number of entries in the LUT P with the bit           |

|            | number of a search key ( <i>n</i> )102                                     |

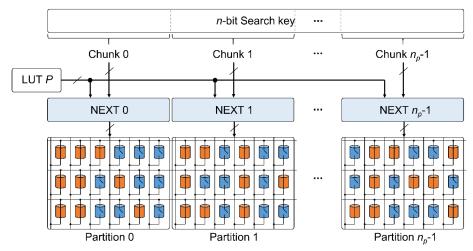

| Figure 4.6 | . Schematic of parallel searches of $N_{\rm p}$ -CECAM partitions. NEXT in |

|            | the figure means NEXT block in the encoding circuit. The <i>n</i> -bit     |

|            | search key is divided into $n_p$ chunks, and each chunk applies to the     |

|            | NEXT block of each partition. All partitions share a single LUT            |

|            | <i>P</i> 105                                                               |

| Figure 4.7 | . (a) Block diagram of a decoding circuit for 3-CECAM. (b) Timing          |

|            | diagram for decoding an encoded search key of 101100 as its                |

|            | original search key (15)108                                                |

| Figure 4.8 | . Schematic of CECAM with a voltage-reading scheme. The blue               |

|            | arrow in the second row illustrates activated pull-down path112            |

# List of Abbreviations

| LRS   | Low resistance state                            |

|-------|-------------------------------------------------|

| HRS   | High resistance state                           |

| RAM   | Random access memory                            |

| SNN   | Spiking neural network                          |

| IC    | Integrated circuit                              |

| CMOS  | Complementary metal oxide semiconductor         |

| LUT   | Lookup table                                    |

| CAM   | Content-addressable memory                      |

| MLP   | Multilayer perceptron                           |

| CNN   | Convolutional neural network                    |

| MAC   | Multiply-accumulation                           |

| GPU   | Graphics processing unit                        |

| MCMC  | Markov chain Monte Carlo                        |

| MCHL  | Markov chain Hebbian learning                   |

| CBA   | Crossbar array                                  |

| HL    | Hidden layer                                    |

| FPGA  | Feld programmable gate array                    |

| 2T2R  | 2 transistor-2 resistance switch                |

| CECAM | Combination-econding content-addressable memory |

|       |                                                 |

#### 1. Introduction

#### 1.1. Resistance switch array

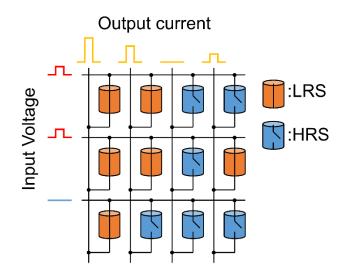

Resistance switch is regarded as a promising candidates for next-generation memory [1]. Resistance switch has two states called low resistance state (LRS) and high resistance state (HRS). The states of resistance switch are non-volatile so that it allows lower energy consumption compared to the conventional memories such as dynamic random access memory (DRAM), which needs refreshment. The switching between LRS and HRS is triggered by electrical stimulation such as applying voltage or current to resistance switch. In the resistance switch array, each resistance switch is placed at the crossing point between each horizontal and vertical metal electrode lines (Fig. 1.1). Note that these horizontal and vertical electrodes have roles of word and bit line. Therefore, resistance switch array is regarded as a two-terminal memory. This simple structure without transistor allows high integration density, the minimum cell size of  $4F^2$ , where F means the minimum feature size [2].

Recently, several analog resistance switches have been proposed [3], [4]. These analog resistance switches enable high data density because a single resistance switch express multi-bit data. Yet, analog resistance switches have bottlenecks such as high non-linear write-pulse number dependency [4], and they also need extremely dedicate control to reach desired resistance [5].

An important feature of resistance switch array is that it realizes matrixvector multiplication [6]-[8]. From the Kirchhoff's law, the output current response is derived as the multiplication between conductance matrix and input voltage vector (Fig. 1.1). This parallel operation enables resistance switch array to be applied to various field, such as analog computer, artificial synapse array, content-addressable memory (CAM). Additionally, this parallel operation enables exclusion of sneak current, which causes degradation of sensing margin, because all electrodes are connected to ground or  $V_{dd}$ . Therefore, sneak currents problem is merely considered in the parallel operation of resistance-switch array [6]-[8].

Figure 1.1. Schematic of resistance switch array. Each resistance switch is placed at each crossing points between electrodes. The output current from resistance switch array is same as multiplication between conductance matrix and input voltage vector.

# **1.2. Resistance switch array application in neuromorphic hardware**

Neuromorphic engineering aims for implementing biologically plausible spiking neural network (SNN) into hardware [9]. With SNN, neuromorphic hardware is expected to be energy-efficient similar to human brain [10]. Also it is suitable for temporal learning, including temporal difference learning [11] and temporal sequence learning [12], and thus expected to be appropriate to solve time-dependent problem.

A neuromorphic hardware consists of neurons that are interconnected through synapses. Implementing neurons and synapses commonly uses analog and/or digital integrated circuits (IC) based on standard complementary metal oxide semiconductor (CMOS) technologies [13], [14]. Recently, emerging devices such as phase change memory [15], [16], magnetic tunnel junctions [17], [18], threshold switches [19], and floating-gate transistors [20] are proposed to build artificial neurons and synapses.

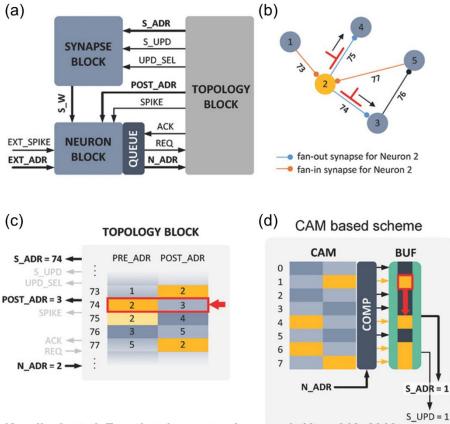

Resistance switch array is also a strong candidate for artificial synapses [3], [4]. In neural network, the activation of pre-synaptic neurons causes spikes and these spikes are transmitted to post-synaptic neurons. Here, post-synaptic neurons receive weighted sum of spikes from pre-synaptic neurons, not spikes. The weighted sum of spikes is expressed as  $W \times x$ , where W and x indicate a synaptic weight matrix and activation of pre-synaptic neurons, respectively. It is similar to matrix-vector multiplication in resistance switch array, mentioned section 1.1 so that resistance switch array is usable as artificial synapse array. Another application of resistance switch array in a neuromorphic hardware is as a look-up table (LUT) in a topology block [21] (Fig. 1. 2). The entire connections between neurons through synapses are tabulated in the LUT. When a spike occurs from a neuron, the topology block searches all elements of the LUT and find the post-synaptic neurons and synapses to update. Therefore, fastsearch ability is the most important factor of LUT. RAM is not a proper solution for LUT because RAM search every address sequentially and it causes significant delays. Unlike RAM, content-addressable memory (CAM) has parallel search ability and thus it is proper to be used as LUT [22]. The conventional CAMs, however, have SRAM-based structure which needs tremendous amount of transistors and have low-integration density.

Compared to SRAM-based CAM, resistance switch-based CAM (RCAM) has much higher content density because they use much less transistors [23], [24]. Also, RCAM has very low static energy consumption because of non-volatility. Consequently, RCAM is appropriate for the LUT in topology block of neuromorphic hardware.

From this features, this paper consists of three parts. At first, artificial neural network is applied to accelerate simulation of resistance-switch array. In the second part, a new learning algorithm called Markov Chain Hebbian Learning is proposed as the appropriate learning algorithm for resistance switch array. Lastly, a new type of RCAM, called combination-encoding CAM, is proposed to improve content density.

Kornijcuk et al, Frontiers in neuroscience, vol. 10, p. 212, 2016.

Figure 1.2. (a) Scheme of neuromorphic hardware. It consists of neuron block, synapse block which realize artificial neurons and synapses, respectively, and topology block. (b), (c) Topology block stores neuronal connectivity. When a spike occurs, it searches LUT and find the destination neurons and synapses to be updated. (d) Scheme for CAM as LUT. CAM enables fast-searching for topology block.

#### **1.3. Bibliography**

- [1] A. Beck, J. Bednorz, C. Gerber, C. Rossel, and D. Widmer, *Applied Physics Letters*, vol. 77, no. 1, pp. 139-141, 2000.

- J. Y. Seok, S. J. Song, J. H. Yoon, K. J. Yoon, T. H. Park, D. E. Kwon,

H. Lim, G. H. Kim, D. S. Jeong, and C. S. Hwang, *Advanced Functional Materials*, vol. 24, no. 34, pp. 5316-5339, 2014.

- M. Prezioso, F. Merrikh-Bayat, B. D. Hoskins, G. C. Adam, K. K. Likharev, and D. B. Strukov, *Nature*, vol. 521, no. 7550, pp. 61-64, 2015.

- [4] G. W. Burr, R. M. Shelby, S. Sidler, C. Di Nolfo, J. Jang, I. Boybat, R.

S. Shenoy, P. Narayanan, K. Virwani, and E. U. Giacometti, *IEEE Transactions on Electron Devices*, vol. 62, no. 11, pp. 3498-3507, 2015.

- [5] M. Hu, C. E. Graves, C. Li, Y. Li, N. Ge, E. Montgomery, N. Davila,

H. Jiang, R. S. Williams, and J. J. Yang, *Advanced Materials*, vol. 30, no. 9, p. 1705914, 2018.

- [6] D. S. Jeong, K. M. Kim, S. Kim, B. J. Choi, and C. S. Hwang, Advanced Electronic Materials, vol. 2, no. 9, p. 1600090, 2016, Art no. 1600090.

- [7] M. Hu, J. P. Strachan, Z. Li, E. M. Grafals, N. Davila, C. Graves, S. Lam, N. Ge, J. J. Yang, and R. S. Williams, in *Proceedings of the 53rd annual design automation conference*, 2016: ACM, p. 19.

- [8] L. Gao, P. Y. Chen, and S. Yu, *IEEE Electron Device Letters*, vol. 37, no. 7, pp. 870-873, 2016.

- [9] C. Mead, *Proceedings of the IEEE*, vol. 78, no. 10, pp. 1629-1636, 1990.

- [10] G. Cauwenberghs, *Proceedings of the national academy of sciences*, vol. 110, no. 39, pp. 15512-15513, 2013.

- [11] R. P. Rao and T. J. Sejnowski, *Neural computation*, vol. 13, no. 10, pp. 2221-2237, 2001.

- [12] F. Wörgötter and B. Porr, *Neural computation*, vol. 17, no. 2, pp. 245-319, 2005.

- [13] G. Indiveri, B. Linares-Barranco, T. J. Hamilton, A. Van Schaik, R.

Etienne-Cummings, T. Delbruck, S.-C. Liu, P. Dudek, P. Häfliger, and

S. Renaud, *Frontiers in neuroscience*, vol. 5, p. 73, 2011.

- [14] M. R. Azghadi, N. Iannella, S. F. Al-Sarawi, G. Indiveri, and D. Abbott, *Proceedings of the IEEE*, vol. 102, no. 5, pp. 717-737, 2014.

- [15] T. Tuma, A. Pantazi, M. Le Gallo, A. Sebastian, and E. Eleftheriou, *Nature nanotechnology*, vol. 11, no. 8, p. 693, 2016.

- [16] S. Ambrogio, P. Narayanan, H. Tsai, R. M. Shelby, I. Boybat, C. di Nolfo, S. Sidler, M. Giordano, M. Bodini, and N. C. Farinha, *Nature*, vol. 558, no. 7708, p. 60, 2018.

- [17] A. Sengupta, P. Panda, P. Wijesinghe, Y. Kim, and K. Roy, *Scientific reports*, vol. 6, p. 30039, 2016.

- [18] A. Mizrahi, T. Hirtzlin, A. Fukushima, H. Kubota, S. Yuasa, J. Grollier, and D. Querlioz, *Nature communications*, vol. 9, no. 1, p. 1533, 2018.

- [19] H. Lim, H.-W. Ahn, V. Kornijcuk, G. Kim, J. Y. Seok, I. Kim, C. S. Hwang, and D. S. Jeong, *Nanoscale*, vol. 8, no. 18, pp. 9629-9640, 2016.

- [20] V. Kornijcuk, H. Lim, J. Y. Seok, G. Kim, S. K. Kim, I. Kim, B. J. Choi, and D. S. Jeong, *Frontiers in neuroscience*, vol. 10, p. 212, 2016.

- [21] V. Kornijcuk, J. Park, G. Kim, D. Kim, I. Kim, J. Kim, J. Y. Kwak, and

D. S. Jeong, *Advanced Materials Technologies*, vol. 4, no. 1, p. 1800345, 2019.

- [22] K. Pagiamtzis and A. Sheikholeslami, *IEEE Journal of Solid-State Circuits*, vol. 41, no. 3, pp. 712-727, 2006.

- [23] A. Grossi, E. Vianello, C. Zambelli, P. Royer, J.-P. Noel, B. Giraud, L.

Perniola, P. Olivo, and E. Nowak, *IEEE Transactions on Very Large Scale Integration Systems*, no. 99, pp. 1-9, 2018.

- [24] R. Han, W. Shen, P. Huang, Z. Zhou, L. Liu, X. Liu, and J. Kang, Japanese Journal of Applied Physics, vol. 57, no. 4S, p. 04FE02, 2018.

# 2. Artificial neural network for response inference of a nonvolatile resistance-switch array

#### 2.1. Introduction

An artificial neural network (ANN) is a layered graph of nodes (activation units) and edges (nonzero connection weights), offering an immensely versatile hypothesis for various types of data description and different training methods [1]. Among feed-forward neural networks, multilayer perceptrons (MLP) and convolutional neural networks (CNN) are the most frequently applied types of neural network [2]. MLP is a prototypical feed-forward architecture in which every unit in a layer is fully wired to all units in the adjacent layers. In contrast, CNN has interlayer connections that are sparse and localized in the network topology [3,4]. A weight matrix in the CNN filters an input matrix fed into the next layer, and this filter (also known as convolution kernel) skims over the input layer. This is mathematically identical to convolving around the input layer, thus this architecture is termed CNN. In fact, the CNN has been successfully applied to a wide range of tasks including image recognition [1], [3]-[5] and natural language processing [6].

The scope of tasks (other than conventional tasks mentioned above) within the capability of ANN has been markedly expanding, including quantum mechanical problems such as estimation of quantum mechanical ground state given a two-dimensional potential distribution [7] and modelling a mechanical

system in presence of noise [8]. These examples highlight the neural network as a versatile hypothesis and the capability of backpropagation for supervised learning as a widely applicable training method.

Meanwhile, a crossbar array of nonvolatile resistance-switches, i.e., passive resistive random access memory (RRAM), ideally meets the 4F2 design rule (F is the minimum feature size), offering a solution to high-density nonvolatile memory [9]-[11]. Additionally, its current response to an applied voltage array naturally captures the multiply-accumulate (MAC) operation so that crossbar arrays have often been used for physical implementation of the matrix–vector product [12]-[14]. The benefit of this approach is obvious in comparison to the digital MAC operation: high speed due to the fully parallel operation and energy-efficiency due to no need for data transference during the operation. Given that the MAC operation is at the heart of MLP for both training and inference, the passive RRAM can substantially improve efficiency in MLP, which is an important field of neuromorphic engineering [12], [14]-[19].

Considering the beneficial relationship between passive RRAM and MLP (particularly, the aforementioned passive RRAM for MLP), it is of interest to seek the reverse approach (MLP for passive RRAM). To this end, this work exemplifies the feasible application of MLP to the response inference of passive RRAM in which, once trained, the inference merely costs a few steps of matrixvector product (depending on the depth of the network). Our new method may offer a new feasible means of crossbar circuit simulations as an alternative to conventional circuit simulation methods.

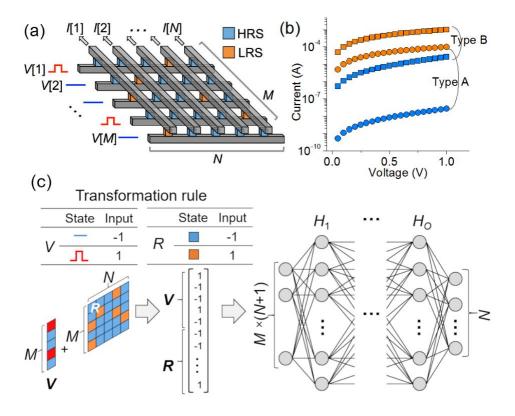

#### 2.2. Description of model system

Passive RRAM as a model system is a  $M \times N$  matrix R loaded with  $R_{\text{HRS}}$  and  $R_{\text{LRS}}$  that denote resistance in a high resistance state (HRS) and low resistance state (LRS), respectively, i.e.,  $R \in \{R_{\text{HRS}}, R_{\text{LRS}}\}^{M \times N}$ . This model system outputs an N-long real-valued current vector ( $\in \mathbb{R}^N$ ) in response to an M-long real-valued input voltage vector V ( $\in \{0,1\}^M$ ). The model system is illustrated in Fig. 2.1(a).

The model is a nonlinear system because the HRS features a highly nonlinear current-voltage (*I-V*) relationship in contrast to the linear (or almost) *I-V* of the LRS. In this regard, the HRS was provided with a nonlinear *I-V* characteristic as follows:  $I = I_0e^{aV}$ , where  $I_0$  and a denote a pre-exponential factor and voltage coefficient, respectively. The larger *a*, the higher nonlinearity is given to the *I-V* behavior. Such nonlinearity in the HRS has been observed in an enormous number of resistance-switches given the usual thermal activation of current transport in the HRS [10, 20, 21]. In contrast, the LRS was given a linear *I-V* characteristic, keeping fidelity to experimental systems that generally represent linear or very weakly nonlinear *I-V* characteristics.

Two types of resistance-switch were addressed in this study: Type A and B, whose detail is tabulated in Table 2.1. The *I-V* behavior for each switch is plotted in Fig. 2.1(b). They differ in the  $R_{\text{HRS}}/R_{\text{LRS}}$  ratio (evaluated at 1 V); the ratio for Type A is 100 times larger than Type B. For each type, two different array sizes (10×9 and 28×27; M = 10 and N = 9, and M = 28 and N = 27, respectively) were considered.

Figure 2.1. (a) Schematic of an  $M \times N$  crossbar array. (b) Assumed *I-V* characteristics of the model resistance-switches (Types A and B). (c) Schematic of the MLP with  $M \times (N + 1)$  input and N output units, and O hidden layers. The rule for mapping resistance-switches and input voltage arrays to an input vector is tabulated in the inset.

Table 2.1. Parameters of model switch.

| Heading                        | Type A                       | Туре В               |

|--------------------------------|------------------------------|----------------------|

| $R_{ m HRS}\left(\Omega ight)$ | $10^8 	imes \mathrm{e}^{-V}$ | $10^5 \times e^{-V}$ |

| $R_{ m LRS}\left(\Omega ight)$ | 10k                          | 1k                   |

| $R_{ m HRS}/R_{ m LRS}$ at 1 V | 3679                         | 36.79                |

#### 2.3. Description of artificial neural network

The passive RRAM outputs a current vector I that is determined by the configuration of switches over the whole array instead of their local configuration. A fully connected feed-forward network is, therefore, suitable for the model system instead of a CNN capturing patterns over local areas. Additionally, given the aforementioned nonlinearity of the model system, a hidden layer(s) needs to be incorporated in the network, rendering an MLP most suitable. Thus, an MLP was chosen as an appropriate network for the crossbar array. Fig. 2.1(c) illustrates the employed MLP with  $M \times (N+1)$  input units, N output activation units, and O hidden layers, each of which is filled with Hi activation units where  $i \in \{1, 2, \dots, 0\}$ . The input into the MLP is the resistance-state (+1 and -1 for the LRS and HRS, respectively) distribution over the  $M \times N$  array (R) plus an M-long vector for input voltage (+1 and -1 for V[i] = 1 and V[i] = 0, respectively) as sketched in Fig. 2.1(c). This matrix is then vectorized to feed into the MLP. The output is the estimated output current of the crossbar array at a given voltage. Note that successful training is crucial to rescale the original physical input (resistance and voltage) and output (current) in a heuristic manner such that the rescaled (scale-free) values stay in an "acceptable" range. To this end, symbolic (+1 and-1), rather than physical, values were given to the input components. Likewise, the desired (correct) output values (currents) were rescaled such that  $L[i] = 10 \times I[i] \times R_{LRS}$ .

The leaky rectified linear unit (ReLU) was deployed as an activation unit: f(x)= max(x, 0.1x). The leakage when x < 0 is required for the negative input components. Otherwise, the negative input components are merely ignored as for the simple ReLU, f(x) = max(x, 0). The ReLU is a workaround for the notorious vanishing gradient problem, which is significant when the network is deep.

#### 2.4. Training and test datasets

The output *I* in response to an input *V* for a given *R* was evaluated by applying the Kirchhoff's circuit law to each switch. The obtained nonlinear equations were solved using the Newton-Raphson method, which resulted in the output I. The calculation was elaborated in [22]. A training dataset was produced by randomly sampling resistance state distribution over the array and input V. First,  $p_1$  ( $0 \le p_1 \le 1$ ) was randomly sampled from a uniform probability distribution function (PDF) and used as the probability that V[i] = 1. That is, if  $p_1$  is 0.4, 40% of all input lines are pulled high (1 V), and the rest lines (60%) are pulled down (0 V). Another number  $p_2$  ( $0 \le p_2 \le 1$ ) was subsequently sampled for each input line from a uniform PDF to randomly distribute 1 V signals over all input lines at a probability of  $p_1$  such that, when  $p_2 \leq p_1$ , V[i] = 1, and 0 otherwise. This process was repeated with different  $p_2$ 's over M rows, resulting in an input V for this training example. A third number  $p_3$  ( $0 \le p_3 \le 1$ ) was picked from a uniform PDF and taken as the percentage of LRS switches in the entire array. For each switch in the array,  $p_3$  was compared with another random number,  $p_4$  $(0 \le p_4 \le 1)$  was sampled for each switch, and  $R[i, j] = R_{LRS}$  when  $p_4 \le p_3$ , and  $R[i,j] = R_{\text{HRS}}$  otherwise. The label of this training example was the current response for I given R and V. The complete dataset was acquired by repeating this process. The test dataset was separately made for the fair evaluation of

inference accuracy. Two different crossbar array sizes (10×9 and 28×27) for each type of switch were considered so that four different training and test datasets were produced. Each training dataset included 500,000 training examples (V, R, and I) unless otherwise specified. The network was examined for every training epoch using 10,000 test examples. Backpropagation using the mean-squared error loss function was employed with Adam optimizer that leverages learning rate adaptation for each parameter to accelerate training [23]. The MLP was batch-trained with a batch size of 100 (100 examples were randomly chosen for each training epoch). Both training and inference were performed using TensorFlow [24]. Note that for successful training, the network should vary on its hyper-parameters such as the number of ReLU units in each hidden layer ( $H_i$ ) and the network depth (O) depending on the input array length.

# 2.5. Training results

Fig. 2.2 shows a reduction in the discrepancy between the output (inferred) current lout and desired (correct) current  $I_{cor}$  in due course, revealing successful training for all four cases conditional on the network structure. For the small crossbar array (10×9), a network including a single hidden layer (O = 1) loaded with 100 ReLU units could successfully be trained with the 500,000 training examples (Fig. 2.2(a), (b)). However, the use of fewer units (50 and 75) falls short of the capability of learning the dataset so that a high error level is maintained for both types of switch. This is a result of underfitting referring to the use of an unsuitable network for capturing the input pattern. Here, the network is too simple (insufficient number of units) to describe the complexity

of input data. The successfully trained network infers the output current of a random  $10 \times 9$  crossbar array **R** at a random V. The inferred currents for 10,000 test examples are plotted against the desired (correct) currents in Fig. 2.2(e), (f), each of which includes 90,000 data points (10,000 test examples, each of which produces 9 current values). The error histogram for each case is plotted in the inset, indicating a root mean squared error (RMSE) of 0.313  $\mu$ A and 17.8  $\mu$ A, respectively. The larger error for Type 2 switch arises from the higher current in both HRS and LRS due to the lower RHRS and RLRS. The results for the larger crossbar array ( $28 \times 27$ ) of Types A and B switches are shown in Fig. 2.2(c), (d), respectively. Given the larger input dimension  $(28 \times 28 = 784)$ , a network needs more units in each hidden layer and/or more hidden layers for success in training. The employed network varies on the number of units (1500 and 2500) in a hidden layer and the network depth (1 and 2). The three networks among four are given the capability to estimate the response of a random  $28 \times$ 27 crossbar array **R** at a random V. As such, the network fully trained along the green curve for Types A and B switches represents low inference-error (a RMSE of 4.85  $\mu$ A and 62.7  $\mu$ A, respectively) as elucidated in Fig. 2.2(g), (h), and their insets.

The correlation coefficient r for each case was also evaluated as another measure of success of training, which is given by  $r = cov(I_{out} - I_{cor})/\sqrt{var(I_{out}) \cdot var(I_{cor})}$ , where cov and var denote a covariance and variance, respectively. The correlation coefficient is asymptotic to 1 when the inference error tends to zero, and thereby r = 1 implies zero error (perfect match). The calculated r for each case is written in Fig. 2.2. The failure of training for the network with 2,500 units in each of the two hidden layers is due to overfitting (see orange curves in Fig. 2.2(c), (d)). Although the network is given sufficient complexity (a large number of units and hidden layers) to learn the complex input pattern, insufficient training examples lead to faulty training as shown in the orange curves (Fig. 2.2(c), (d)). Overfitting could be avoided by training with a larger training dataset (here 1,000,000 examples for Type B switch) as shown in Fig. 2.3(a). The inference-error for the overfitting case is detailed in Fig. 2.3(b) which represents a substantial discrepancy between the inferred and desired outputs, the extent to which the RMSE reaches 438.2  $\mu$ A (r = 0.99571). The error statistics are plotted in the inset. In contrast, a remarkable reduction in inference-error is identified for the non-overfitting case (Fig. 2.3(c)) whose RMSE is lowered down to 49.2  $\mu$ A (r = 0.9995).

Finally, we compared the time-efficiency of the proposed method with the conventional Newton-Raphson method [22]. The run time of a 10×9 resistance array calculation was measured for both methods using the same computer. The result shown in Fig. 2.4 ensures an acceleration in calculation by approximately 8 times, identifying a feasible benefit of fast calculation from the proposed method.

Figure 2.2. Inference-error reduction while training a network with the dataset of a  $10 \times 9$  crossbar array of (a) Type A and (b) Type B switches. Their output results (inferred currents) for the entire 10,000 test datasets after successful training (green lines) are plotted against the desired currents in (e) and (f), respectively. The histogram of the error (the difference between inferred and desired currents) for each case is shown in the inset. The red solid lines denote the perfect match of inference with the desired (correct) results. The results are

shown for a  $28 \times 27$  crossbar array of (c) Type A and (d) Type B switches, and their statistics in (g) and (h), respectively.

Figure 2.3. (a) Training the network (2,500 units in each of two hidden layers) with 500,000 and 1,000,000 examples for Type B switch. The capability of response inference is shown for the network trained with (b) 500,000 and (c) 1,000,000 examples. The insets address the distribution of inference-error.

Figure 2.4. Comparison of run time for the proposed method and Newton-Raphson method.

# **2.6.** Conclusions

A fully connected feed-forward network with different structures (depth and the number of activation units) was successfully trained to infer the current response of a random crossbar array to a randomly applied voltage array. This work first verifies the capability of ANN to capture the highly nonlinear input-output relationship of a crossbar array model system. Secondly, MLP for supervised learning provides a means of real-valued array inference beyond the classification of input patterns. Thirdly, this work offers a distinct view of crossbar array evaluation — a numerical solution of a number of simultaneous equations can be avoided at the expense of a few steps of matrix-vector product for inference. However, training the network and preparing datasets can be expensive, depending on the network hyper-parameters and model crossbar array size. Thus, we leave this efficiency issue open for the moment.

# 2.7. Bibliography

- Y. LeCun, Y. Bengio, and G. Hinton, *Nature*, Insight vol. 521, no. 7553, pp. 436-444, 2015.

- [2] N. P. Jouppi, C. Young, N. Patil, D. Patterson, G. Agrawal, R. Bajwa,

S. Bates, S. Bhatia, N. Boden, and A. Borchers, in 2017 ACM/IEEE

44th Annual International Symposium on Computer Architecture (ISCA), 2017: IEEE, pp. 1-12.

- [3] Y. Lecun, L. Bottou, Y. Bengio, and P. Haffner, *Proceeding of IEEE*, vol. 86, no. 11, pp. 2278-2324, 1998.

- Y. LeCun, K. Kavukcuoglu, and C. Farabet, in 2010 IEEE International Symposium on Circuits and Systems (ISCAS), 2010, pp. 253-256.

- [5] A. Krizhevsky, I. Sutskever, and G. E. Hinton, in *Advances in Neural Information Processing Systems*, 2012, pp. 1097-1105.

- [6] R. Collobert, J. Weston, L. o. Bottou, M. Karlen, K. Kavukcuoglu, and

P. Kuksa, *Journal of Machine Learning Research*, vol. 12, pp. 2493-2537, 2011.

- [7] K. Mills, M. Spanner, and I. Tamblyn, *arXiv:1702.01361*, 2017.

- [8] M. Nentwig and P. Mercorelli, in 2008 7th IEEE International Conference on Cybernetic Intelligent Systems, 2008: IEEE, pp. 1-6.

- [9] R. Waser, R. Dittmann, G. Staikov, and K. Szot, *Advanced Materials*, vol. 21, pp. 2632-2663, 2009.

- [10] D. S. Jeong, R. Thomas, R. Katiyar, J. Scott, H. Kohlstedt, A. Petraru, and C. S. Hwang, *Reports on Progress in Physics*, vol. 75, no. 7, p. 076502, 2012.

- J. Y. Seok, S. J. Song, J. H. Yoon, K. J. Yoon, T. H. Park, D. E. Kwon,

H. Lim, G. H. Kim, D. S. Jeong, and C. S. Hwang, *Advanced Functional Materials*, vol. 24, no. 34, pp. 5316-5339, 2014.

- [12] D. S. Jeong, K. M. Kim, S. Kim, B. J. Choi, and C. S. Hwang, Advanced Electronic Materials, vol. 2, no. 9, p. 1600090, 2016.

- [13] M. Hu, J. P. Strachan, Z. Li, E. M. Grafals, N. Davila, C. Graves, S. Lam, N. Ge, J. J. Yang, and R. S. Williams, *Proceedings of the 53nd Annual Design Automation Conference*, 2016, pp. 1-6.

- [14] L. Gao, P. Y. Chen, and S. Yu, *IEEE Electron Device Letters*, vol. 37, no. 7, pp. 870-873, 2016.

- [15] D. S. Jeong, I. Kim, M. Ziegler, and H. Kohlstedt, *RSC Advances*, vol. 3, no. 10, pp. 3169-3183, 2013.

- [16] J. J. Yang, D. B. Strukov, and D. R. Stewart, *Nature Nanotechnology*, vol. 8, no. 1, pp. 13-24, 2013.

- [17] P. Y. Chen, L. Gao, and S. Yu, *IEEE Transactions on Multi-Scale Computing Systems*, vol. 2, no. 4, pp. 257-264, 2016.

- [18] P. M. Sheridan, F. Cai, C. Du, W. Ma, Z. Zhang, and W. D. Lu, *Nature Nanotechnology*, Article vol. advance online publication, 2017.

- [19] S. Choi, J. H. Shin, J. Lee, P. Sheridan, and W. D. Lu, *Nano Letters*, vol. 17, no. 5, pp. 3113-3118, 2017.

- [20] D. S. Jeong, H. Schroeder, and R. Waser, *Electrochemical Solid-State Letters*, vol. 10, p. G51, 2007.

- [21] D. S. Jeong, H. Schroeder, and R. Waser, *Physical review B*, vol. 79, p. 195317, 2009.

- [22] D. S. Jeong, H.-W. Ahn, S.-D. Kim, M. An, S. Lee, and B.-k. Cheong, *Electronic Materials Letters*, vol. 8, no. 2, pp. 169-174, 2012.

- [23] D. P. Kingma and J. Ba, *arXiv:1412.6980*, 2014.

- [24] M. Abadi, A. Agarwal, P. Barham, E. Brevdo, Z. Chen, C. Citro, G. S. Corrado, A. Davis, J. Dean, and M. Devin, *arXiv:1603.04467*, 2016.

# 3. Markov chain hebbian learning algorithm with ternary synaptic units

# **3.1. Introduction**

Recent progress in machine learning (particularly, deep learning) endows machines with high precision recognition and problem-solving capabilities beyond the human level [1]-[3]. Computers on the von Neumann architecture are the platform for the breakthroughs albeit frequently powered by hardware accelerators, e.g., graphics processing unit (GPU) [4]. The main memory stores intertwined fragmentary information, e.g., weight matrix, representation of hidden neurons, input datasets, and so forth. However, essential to efficient memory retrieval is memory organization such that the whole weight matrix can readily be recalled when necessary. In this regard, a high-density crossbar array (CBA) of two-terminal memory elements, e.g., oxide-based resistive memory and phase change memory, is perhaps a promising solution to machine learning acceleration [5]-[9].The connection weight between a pair of neurons is stored in each memory element in the CBA as conductance, and the weight is read out in place by monitoring current in response to a voltage [5]-[9].

Albeit promising, this approach should address the following challenges; each weight should be calculated beforehand using a conventional errorcorrecting technique, and the pre-calculated value needs to be programmed in a single memory element. The former particularly hinders online learning. In this study, an easy-to-implement algorithm based on a stochastic neural network—termed the Markov chain Hebbian learning (MCHL) algorithm—is proposed. The most notable difference between the MCHL and restricted Boltzmann machine (RBM) [10]-[15] is that the MCHL is a discriminative learning algorithm with the aid of "external field" that realizes supervised learning. Also, each update uses only local (spatial and temporal) data rather than global data such as energy of the entire network. The MCHL algorithm also features as follows: (a) Each weight w[i, j] is a ternary number:  $w[i, j] \in$  $\{-1, 0, 1\}$

(b) Given (a), each update of weight follows a finite-state Markov chain, and the update probability is in line with the Hebbian learning.

(c) A group of output neurons in a bucket (rather than a single neuron) simultaneously represent a data class (label), which is comparable to concept cells [16]-[18].

(d) When the network is deep, the network is trained in a greedy layer-wise manner, and each layer is trained in a greedy edge-wise manner.

Provided with these features, the MCHL algorithm enables an ad hoc update of the weight matrix (online learning) in a memory-saving fashion, so that it is suitable for machine learning powered by CBA-based memory. No need for an auxiliary function for error correction, e.g., backpropagation, particularly alleviates computational complexity. Each synapse is given a ternary number during the entire learning period—distinguishable from binarizing real-valued weight at each update step [19] as well as the use of auxiliary real-valued variables [20]. A Markov chain, specifically, in Markov chain Monte Carlo(MCMC), is a common means of sampling from a complex distribution of data to extract information in stochastic machine learning [21]. Especially, a Markov decision process offers a solution to an optimal policy that maps a current state of an agent to a certain action resulting in the maximum reward in reinforcement learning [22], [23] Additionally, MCMC yields a posterior probability distribution that is the key to Bayesian inference and learning [21] Examples also include recent attempts to apply Markov chains to multi-instance multi-label learning [24] that addresses objects embodying multiple instances (features). In this case, Markov chains are used as probabilistic classifiers mapping multiple instances to multiple labels [25].

Stochastic Hebbian learning algorithms are methods to probabilistically train a binary synapse conditional on the pre and postsynaptic activities in line with the MCHL algorithm [26], [27]. Interestingly, such algorithms can train networks to a comparable degree with its deterministic counterpart [26], [27]. Yet, these algorithms barely support supervised learning for classification tasks. Senn and Fusi proposed a single-layer perceptron with a stochastic learning algorithm for supervised learning [28]. The algorithm requires global inhibition that is applied to all output neurons so that the actual synaptic input in total (input from binary excitatory synapses plus global inhibition) is not all or nothing. Additionally, no explicit method to apply the algorithm to multilayer perceptrons (MLPs) is proposed.

Note that, regarding the feature (d), the network depth indicates repeated linear classifiers through the layers so that it differs from that of a multilayer feed-forward network that features a nonlinear classifier. Nevertheless, we term the additional layers between input and output layers as hidden layers(HLs) given that they are literally hidden irrespective of their role in non-linear classification. Additionally, a network with such HLs is referred to as a deep network.

The MCHL algorithm was applied to two proof-of concept examples: image recognition using the MNIST and CIFAR-10 datasets and multiplication table memorization. The latter example relates the arithmetic to memory-based perception in an analogous way to humans' mental arithmetic. The weight matrix trained with the multiplication table was then applied to more complicated arithmetic such as aliquot part evaluation and prime factorization.

# **3.2. Model description**

## **3.2.1.** Network structure and energy

Analogous to the RBM, two layers of neurons without recurrent connection form the basis for the MCHL algorithm. However, it differs from the RBM such that the HL in the RBM is replaced by an output layer that does not feed input into the input layer. Fig. 3.1(a) depicts a stochastic neural network of M input features and N output neurons.  $u_1$  and  $u_2$  denote the input vector and activity vector of the output layer, defined as

$$\begin{cases} \boldsymbol{u}_1 \in \mathbb{R}^M, & 0 \le u_1[i] \le 1 \\ \boldsymbol{u}_2 \in \mathbb{Z}^N, & u_2[i] \in \{0,1\} \end{cases}$$

respectively. In the output layer, *H* neurons associatively represent each of total *L* labels so that the output layer includes *LH* neurons (*N*=*LH*). A group of such *H* neurons is referred to as a bucket. When the *L* labels are indexed from 1 to *L*,  $u_2[(n - 1)H+1:nH]$  is a block of output activities for the *n*th label. Note that x[a:b] denotes a block ranging from the *a*th to *b*th elements of vector *x*. A matrix

$w \in \mathbb{Z}^{LH \times M}$  defines the weight of feed-forward connection from the input to output layer such that the input z[i] into the *i*th output neuron is given by

$$z[i] = \sum_{j=1}^{M} w[i, j] u_1[j]$$

(1)

Each element of *w* is given one of the ternary values (-1, 0, 1). According to the bucket configuration of the vector  $u_2$ , the matrix w can be partitioned such that  $w[(n-1)H+1:nH, \cdot]$  is for the connection from the input vector to the output neurons of the *n*th label.  $\cdot \cdot$  means all *j*=1, ..., *M*. Likewise,  $z(=wu_1)$ can also be partitioned into *L* buckets.

The energy of this network is defined as

$$E(\boldsymbol{u}_1, \boldsymbol{u}_2) = -(2\boldsymbol{u}_2 - \vec{\mathbf{1}})^{\mathrm{T}} \cdot \boldsymbol{w} \cdot \boldsymbol{u}_1 + \boldsymbol{b}^{\mathrm{T}} \cdot \boldsymbol{u}_2, \qquad (2)$$

where w is a weight matrix,  $\vec{1}$  is a *N*-long vector filled with ones. b denotes a bias vector for the output layer.  $(2u_2 - \vec{1})$  in (2) transforms  $u_2$  such that a quiet neuron  $(u_2[i] = 0)$  is given an output of -1 rather than zero. This counts the cost of a positive connection (w[i, j]=1) between a nonzero input  $(u_1[j]\neq 0)$  and output neuron in an undesired label  $(u_2[i]=0)$ . This undesired connection raises the energy by  $u_1[j]$ .

The following conditional probability that  $u_2[i]=1$  given z[i] holds:

$$P(u_2[i] = 1|z[i]) = \left[1 + e^{-(2z[i] - b[i])/\tau}\right]^{-1},$$

(3)

where  $\tau$  denotes a temperature parameter. (3) is plotted in Fig. 3.1(b). The derivation of (3) is elaborated in Appendix A. We also define the deterministic activity of neuron *i* in the *j*th layer as

$$a_{j}[i] = \left[1 + e^{-(2z[i] - b[i])/\tau}\right]^{-1}.$$

(4)

For instance, for the network in Fig. 3.1(a),  $a_2[i]$  denotes the activity of neuron

*i* in the second (output) layer. This deterministic activity is used for inference as follows. The output from each label n (O[n]) is the sum of deterministic activity over all output neurons in the label. The maximum component of Odesignates the estimated label for a given input. (4) is also used when training a deep network (Sec. IVA).

Note that, unless otherwise stated, the bias is set to zero, simplifying (2), (3), and (4) to

$$E(\boldsymbol{u}_1, \boldsymbol{u}_2) = -(2\boldsymbol{u}_2 - \vec{\mathbf{1}})^{\mathrm{T}} \cdot \boldsymbol{w} \cdot \boldsymbol{u}_1,$$

(5)

$$P(u_2[i] = 1|z[i]) = \left[1 + e^{-2z[i]/\tau}\right]^{-1},$$

(6)

and

$$a_j[i] = \left[1 + e^{-2z[i]/\tau}\right]^{-1},\tag{7}$$

respectively. The description of each mathematical symbol is addressed in Table 3.1.

Figure 3.1. MCHL algorithm working principle. (a) Basic network of *M* input and *N* output binary stochastic neurons ( $u_1$  and  $u_2$ : their activity vectors). (b) Behavior of  $P(u_2[i] = 1)$  with z[i] when b[i]=0. This probability is identical to the deterministic activity  $a_2[i]$  of the neuron.

Table 3.1. Symbols.

| Symbol             | Description                                                            |

|--------------------|------------------------------------------------------------------------|

| $x[i] (i \ge 1)$   | <i>i</i> th element in array $x$                                       |

| $x[i:j] (i \ge j)$ | Block ranging from the <i>i</i> th to <i>j</i> th element in array $x$ |

| <b>u</b> 1         | Activity vector of the M input neurons                                 |

|                    | $oldsymbol{u}_1\in\mathbb{R}^M;$                                       |

|                    | $0 \le u_1[i] \le 1$                                                   |

|                    | Activity vector of the N output neurons                                |

| <b>U</b> 2         | $oldsymbol{u}_2\in\mathbb{Z}^N$ ;                                      |

|                    | $u_2[i] \in \{0,1\}$                                                   |

|                    | Weight matrix                                                          |

| w                  | $oldsymbol{w} \in \mathbb{Z}^{N 	imes M}$ ;                            |

|                    | $w[i, j] \in \{-1, 0, 1\}$                                             |

| b                  | Bias vector for the output neurons                                     |

|                    | Array of inputs into the output neurons                                |

| z                  | M                                                                      |

|                    | $z[i] = \sum_{i=1}^{N} w[i, j] u_1[j]$                                 |

|                    | j=1                                                                    |

|                    | Deterministic activity of the $N$ output neurons                       |

| $a_2$              | $oldsymbol{a}_2\in\mathbb{R}^N$ ;                                      |

|                    | $0 \le a_2[i] \le 1$                                                   |

| L                  | Number of total labels in a dataset                                    |

| $H_i$              | Number of neurons in a bucket in the <i>i</i> th layer                 |

|                    | Write vector                                                           |

| V                  | $oldsymbol{ u}\in\mathbb{Z}^{LH}$ ;                                    |

| V                  | $v[i] \in \{-1,1\}$ if $H = 1$                                         |

|                    | $v[i] \in \{-1,0,1\}$ otherwise                                        |

| τ                  | Temperature parameter                                                  |

|                    |                                                                        |

| Е                  | Energy of the model                                                    |

| $P_+$              | Probability of potentiation                                            |

| <u> </u>           | Probability of depression                                              |

| $P^{0}_{+}$        | Maximum probability of potentiation                                    |

| $P_{-}^{0}$        | Maximum probability depression                                         |

## 3.2.2. Field application and update probability

In the MCHL algorithm, write vector v designates the correct label of a given input  $u_1$ . Akin to  $u_2$ , v is an *LH*-long vector in which v[(n-1)H+1:nH] is assigned to the *n*th label. The correct label (indexed *N*) is indicated by v such that

$$v[i] = \begin{cases} 1 & \text{if } i = (N-1)H + h \\ -1 & \text{if } i = (n-1)H + h \text{ for all } n \ (\neq N) \\ 0 & \text{otherwise} \end{cases}$$

(8)

where  $1 \le h \le H$ , and *h* is chosen at random. That is, one of the elements for label *N* is endowed with 1 while one of the elements for each undesired label is given -1. Thus, only one element in *v* has 1, *L*-1 elements -1, and the others 0. In conjunction with the corresponding input vector *u*<sub>1</sub>, a field matrix *F* is defined as  $F = v \cdot u_1^T$  and  $F[i, j] = v[i]u_1[j]$  element-wise. F[i, j] determines the sign and probability of weight change of w[i, j] for a given input and its correct label. F[i, j] (>0) causes potentiation ( $\Delta w[i, j] = 1$ ) at probability  $P_+$  only if  $u_2[i] = 0$  (condition (a)) and  $w[i, j] \neq 1$  (condition (b)). In contrast, F[i, j] (<0) causes depression ( $\Delta w[i, j] = -1$ ) at probability  $P_-$  only if  $u_2[i] = 1$  (condition (a)) and  $w[i, j] \neq -1$  (condition (b)).  $P_+$  and  $P_-$  are

$$\begin{cases} P_{+} = P_{+}^{0}F[i,j] = P_{+}^{0}v[i]u_{1}[j] \\ P_{-} = -P_{-}^{0}F[i,j] = -P_{-}^{0}v[i]u_{1}[j] \end{cases},$$

(9)

where  $P^0_+$  and  $P^0_-$  denote the maximum probability of potentiation and depression, respectively. Stochastic update on weight given probability is detailed in Appendix B.

This update rule is reminiscent of the Hebbian learning such that the larger the input  $u_1[j]$ , the more likely the update is successful since  $P_+$  and  $P_-$  scale with  $u_1[j]$  as shown in (9). Condition (a) indicates that a quiet output neuron  $(u_2[i] = 0)$  supports potentiation, whereas an active one  $(u_2[i] = 1)$  supports depression. Condition (b) keeps  $w[i, j] \in \{-1, 0, 1\}$  so that the update falls into a finite state Markov chain. v is renewed for the subsequent update with another input data and its label. h in (8) is also randomly renewed.

Specifically, the MCHL algorithm exploits inhomogeneous Markov chains that alter the transition matrices every training epoch given the update probability conditional on input and write vector according to (9). Several basic properties of the inhomogeneous Markov chains in the MCHL algorithm are addressed in Appendix C. Generally, a learning rate is of significant concern for successful learning. A learning rate in the MCHL algorithm is dictated by  $P_{+}^{0}$ and  $P_{-}^{0}$  in place of an explicit rate term. For extreme cases such as  $P_{+}^{0} = 1$ and  $P_{-}^{0} = 1$ , the matrix barely converges, but constantly fluctuates.

When including HLs (Fig. 3.2), the network is trained in a greedy layer-wise manner as for deep belief networks [29]. That is, the matrix  $w_1$  was first fully trained with a field matrix  $F_1$  of each input vector  $u_1$  and the corresponding write vector v. The matrix  $w_2$  is subsequently trained with a field matrix  $F_2$  for a given  $u_1$  and v, which reads  $F_2 = v \cdot u_2^T$ . Such layer-wise training continues up to the topmost weight matrix  $w_{D-1}$  that is trained with  $F_{D-1}$  shown in Fig. 3.2.

Figure 3.2. Network with hidden layers.  $F_2$  and  $F_{D-1}$  denote a field matrix for  $w_2$  and  $w_{D-1}$ .

# 3.3. Implementation of the MCHL algorithm on

## hardware

## **3.3.1.** Field-programmable gate array

Implementing the MCHL algorithm on hardware boosts the advantage of the algorithm with regard to its efficient use of memory and computational simplicity in weight update. To identify the acceleration of training and inference, a field programmable gate array (FPGA) is an easy-to-implement test bed where weight matrices can be densely organized in static random access memory (SRAM) arrays that are readily accessed when necessary. We will highlight the significant acceleration of the MCHL algorithm by implementing the MCHL algorithm on an FPGA board later in Sec. IVA.

## 3.3.2. Resistance-based random access memory

A CBA of resistance-based memories offers extremely time efficient multiplyaccumulate (MAC) operation and random accessibility to each bit [30], making the MCHL come into its own. Fig. 3.3(a) illustrates a feed-forward connection between u1 and u2 for the topology in Fig. 3.1(a), where the weight matrix w is mapped onto a RAM. Each ternary unit is placed at the cross point between a word line (vertical grey line) and bit line (horizontal grey line). The input vector u1 is physically represented by a voltage array in that  $u_1[j]$  is applied to the *j*th word line. w[i, j] is implemented by the conductance of the unit at the cross point between the *j*th word and *i*th bit lines. High conductance and low conductance correspond to1 and 0, respectively. Likewise, a w[i, j] of -1corresponds to negatively high conductance. This counterintuitive concept is realized as illustrated in Fig. 3.3(b). Each unit consists of 2 bits (two resistors), and each word line for  $u_1[j]$  is paired with an additional line for negative  $u_1[j]$  (Fig. 3.3(b)). Therefore, the total current through the parallel resistors I is

$$I = (G[i,j] - \overline{G}[i,j])u_1[j]$$

where G and  $\overline{G}$  are the conductance of the left and right resistors in each unit, respectively. The three combinations of G and  $\overline{G}$  in Fig. 3.3(b) realize the ternary weight. Note that  $(G, \overline{G}) = (1,1)$  is not favorable because of high power consumption, it can represent 0 though. Therefore, in this strategy, zcorresponds to an array of output currents; z[i] is the current through the *i*th bit line, equivalent to (1). The random accessibility to each unit supports the parallel programming (training) of the units with a programming voltage applied to each bit line. An array of programming voltages corresponds to write vector v (Figs. 3.3(a) and (c)). The sign of  $v[i]u_1[j]$  dictates the weight change of the unit placed between the *i*th bit line and *j*th word line. When positive, the unit is given the non-zero probability that  $\Delta w[i, j] = 1$  (potentiation) while negative  $v[i]u_1[j]$  gives the unit nonzero probability that  $\Delta w[i, j] = -1$ (depression) as sketched in Figs. 3.3(c) and (d), respectively.

Figure 3.3. Memory-centric illustration of a neural network. (a) Graphical description of the weight matrix *w* that determines the correlation between the input activity  $u_1$  and output activity  $u_2$ . The grey vertical and horizontal lines denote word and bit lines, respectively. This weight matrix *w* evolves in accordance to given pairs of an input  $u_1$  and write vector *v*, ascertaining the statistical correlation between  $u_1$  and *v*. (b) A pair of memory resistors in each synaptic unit. Three combinations of the two conductance values represent the ternary weight (1, -1, 0). (c) Potentiation: a weight component at the current step  $t(w_t[i, j])$  has a nonzero probability to gain +1 (i.e.  $\Delta w_t[i, j] = 1$ ) only if  $u_1[j] \neq 0$ , v[i] = 1, and  $w_t[i, j] \neq 1$ ; for instance, given  $u_1 = (0, 1, 0, ..., 0)$  and v = (1, -1, -1, ..., -1),  $w_t[1, 2]$  has a probability of positive update. (d) Depression:

all components  $w_i[i, 2]$   $(i \neq 1)$  are probabilistically subject to negative update (gain -1) insofar as  $u_1[2] \neq 1$ , v[i] = -1, and  $w_i[i, 2] \neq -1$ .

# 3.4. Applications

## **3.4.1. Image recognition**

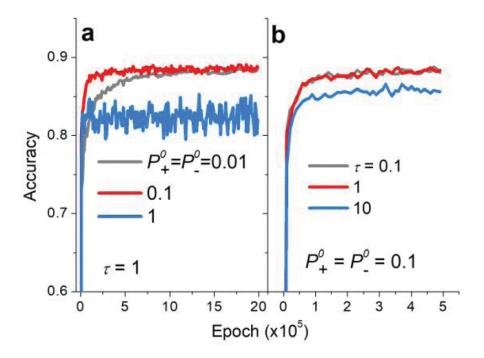

The MCHL algorithm was applied to image recognition tasks with the MNIST database ( $M = 28 \times 28$  and L = 10) and CIFAR-10 database ( $M = 32 \times 32 \times 3$  and L =10). Fig. 3.4(a) shows a memory-centric schematic of the network for the training, which includes one HL. The implementation was two-fold. First, the MCHL algorithm was implemented on a general-purpose computer (CPU: Intel i5-4690 3.5GHz) without using a GPU. The code was written in Python. Second, the algorithm was implemented on an FPGA board (Virtex-7 XC7VX485T) to identify the acceleration of the algorithm. Hereafter, the FPGA board on which the MCHL algorithm is implemented is referred to as an MCHL accelerator. Regarding a tradeoff between recognition accuracy and training speed, parameters  $P^0_+$  (=  $P^0_-$ ) and  $\tau$  were set to 0.1 and 1, respectively, during training with the MNIST dataset. The effect of the parameters on training behavior is elaborated in Appendix D. Note that parameters  $P^0_+$  (=  $P^0_-$ ) and  $\tau$  were set to 0.01 and 1, respectively, during training with the CIFAR-10 dataset, with regard to the tradeoff.

## 3.4.1.1. Implementation on a general-purpose computer

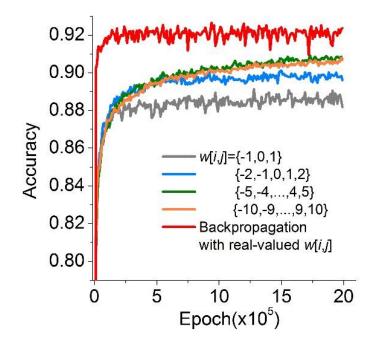

When training the network with the MNIST dataset, the repeated *ad hoc* updates increase the recognition accuracy and decrease the network energy in (5) as plotted in Fig. 3.4(b). The network depth substantially alters the recognition accuracy as plotted in Fig. 3.4(c). Without HL the accuracy merely reaches approximately 88% at  $H_1 = 100$  while deploying one HL improves the

accuracy up to approximately 92% at  $H_1 = 100$  and  $H_2 = 50$ . Note that  $H_1$  and  $H_2$ denote bucket size in the HL and output layer, respectively. Improvement on accuracy continues onwards with more HLs (e.g., two HLs; blue curve in Fig. 3.4(c)), although its effect becomes smaller compared with the drastic improvement by the first HL. The training and test in detail are addressed in Appendix E. The weight matrix becomes larger with bucket size, so is the memory allocated for the matrix. Nevertheless, the benefit of deploying buckets at the expense of memory is two-fold. First, many input features (pixels) are shared among labels such that several individual features do not exclusively belong to a single particular label. The use of buckets allows such common features to be connected with elements over different labels given the sparse update on the weight matrix. For instance, without such buckets, every attempt to direct the feature at (1,1) — belonging to both labels 1 and 2 — to label 1 probabilistically weakens its connection with label 2. Second, when shared, the statistical correlation between the feature and each of the sharing labels is captured by bucket, enabling comparison among the labels. As depicted in Fig. 3.4(a), the 10 sub-matrices in the matrix  $w_2$  define 10 ensembles of  $H_2$  output neurons; the final output from each label O[n] is the sum of deterministic activity  $a_2[i]$  over the neurons in the same label, i.e., the output range scales with  $H_2$  in the range  $0 - H_2$ .

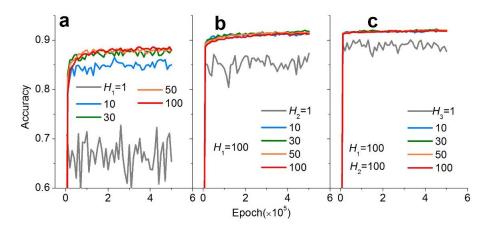

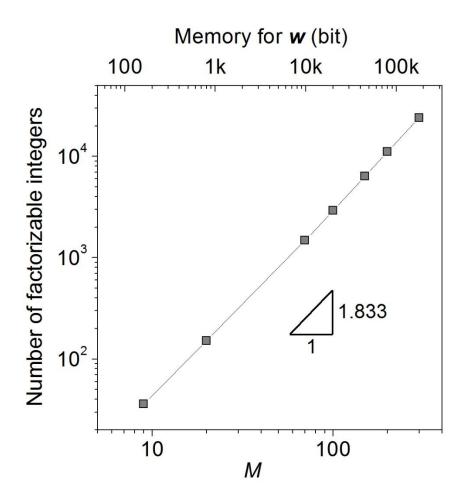

A single training is hardly able to capture a statistical correlation between input and write vectors. However, the larger the training numbers, the less likely the statistical error (noise) is incorporated into the data, which is similar to the error reduction in Monte Carlo simulation with an enormous number of random numbers (RNs) [31]. The use of buckets enables the parallel acquisition of effectively multiple w matrices as opposed to repeated training trials to acquire a w matrix on average. Therefore, it is conceivable that a larger bucket size tends to improve the recognition accuracy. In fact, the bucket size and consequent memory allocation for matrix w significantly determine the recognition accuracy (see Fig. 3.5). However, in Monte Carlo simulations, the error reduction with sample number tends to be negligible when the number is sufficiently large. The same holds for the MCHL algorithm as shown in Fig. 3.5. Additionally, the memory cost perhaps outweighs the negligible improvement in the accuracy. Therefore, it is practically important to reconcile the performance with the memory cost.