공학박사 학위논문

# DNN Accelerator and Load Balancing Techniques Tailored for Accelerating Memory–Intensive Operations

메모리 집약적 연산 가속화를 위해 맞춤화된 DNN 가속기 및 로드 밸런싱 기술

2022년 8월

서울대학교 융합과학기술대학원 융합과학부 지능형융합시스템전공 이 선 정

# DNN Accelerator and Load Balancing Techniques Tailored for Accelerating Memory-Intensive Operations

#### 지도교수 안 정 호

이 논문을 공학박사 학위논문으로 제출함

#### 2022년 7월

서울대학교 융합과학기술대학원

융합과학부 지능형융합시스템전공

## 이선정

이선정의 공학박사 학위 논문을 인준함 2022년 7월

유 승 주 안 정 호 위 원 장: (인) 부 위원장: (인) 김 장 우 (인) 위 원: (인) 원: 김 지 훈 위 원: 정 대 진 (인) 위

# Abstract

# DNN Accelerator and Load Balancing Techniques Tailored for Accelerating Memory–Intensive Operations

Sunjung Lee Intelligence Systems Department of Transdisciplinary Studies The Graduate School Seoul National University

Deep neural networks (DNNs) are used in various fields, such as in image classification, natural language processing, and speech recognition based on high recognition accuracy that approximates that of humans. Due to the continuous development of DNNs, a large body of accelerators have been introduced to process convolution (CONV) and general matrix multiplication (GEMM) operations, which account for the greatest level of computational demand. However, in the line of accelerator research focused on accelerating compute-intensive operations, the execution time of memory-intensive operations has increased more than it did in the past.

In convolutional neural network (CNN) inference, recent CNN models adopt depth-wise CONV (DW-CONV) and Squeeze-and-Excitation (SE) to reduce

the computational costs of CONV. However, existing area-efficient CNN accelerators are sub-optimal for these latest CNN models because they were mainly optimized for compute-intensive standard CONV layers with abundant data reuse that can be pipelined with activation and normalization operations. In contrast, DW-CONV and SE are memory-intensive with limited data reuse. The latter also strongly depends on the nearby CONV layers, making an effective pipelining a daunting task. Therefore, DW-CONV and SE only occupy 10% of entire operations but become memory bandwidth bound, spending more than 60% of the processing time in systolic-array-based accelerators.

During the transformer training process, the execution times of memory– intensive operations such as softmax, layer normalization, GeLU, context, and attention layer increased because conventional accelerators improved their com– putational performance capabilities dramatically. In addition, with the latest trend toward increasing the sequence length, the softmax, context, and atten– tion layers have much more of an influence as their data sizes have increased quadratically. Thus, these layers take up to 80% of the execution time.

In this thesis, we propose a CNN acceleration architecture called MVP, which efficiently processes both compute- and memory-intensive operations with a small area overhead on top of the baseline systolic-array-based ar-chitecture. We suggest a specialized vector unit tailored for processing DW-CONV, including multipliers, adder trees, and multi-banked buffers to meet the high memory bandwidth requirement. We augment the unified buffer with tiny processing elements to smoothly pipeline SE with the subsequent CONV, enabling concurrent processing of DW-CONV with standard CONV, thereby

achieving the maximum utilization of arithmetic units. Our evaluation shows that MVP improves performance by 2.6× and reduces energy consumption by 47% on average for EfficientNet-B0/B4/B7, MnasNet, and MobileNet-V1/V2 with only a 9% area overhead compared to the baseline.

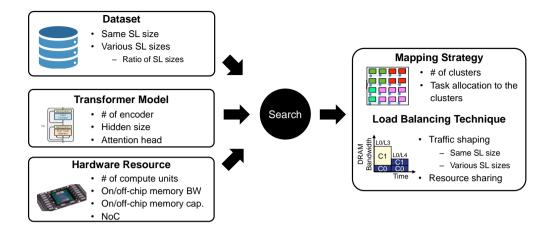

Then, we propose load balancing techniques that partition multiple processing element tiles inside a DNN accelerator for transformer training acceleration. Traffic shaping alleviates temporal fluctuations in the DRAM bandwidth by handling multiple processing element tiles within a cluster in a synchronous manner but running different clusters asynchronously. Resource sharing reduces the execution time of compute-intensive operations by simultaneously executing the matrix units and vector units of all clusters. Our evaluation shows that traffic shaping and resource sharing improve the performance by up to 1.27× for BERT-Large training.

keywords: DNN accelerator, tailored vector unit, CNN, load balancing, partitioning processing units, transformer, traffic shaping, resource sharing student number: 2018–38972

# Contents

| Ał | ostrac            | t        |                                                | i    |  |

|----|-------------------|----------|------------------------------------------------|------|--|

| Со | onten             | ts       |                                                | iv   |  |

| Li | List of Tables vi |          |                                                |      |  |

| Li | st of I           | Figures  |                                                | viii |  |

| 1  | Intro             | oduction | n                                              | 1    |  |

|    | 1.1               | Accele   | rating Depth-wise Convolution on Edge Device   | 3    |  |

|    | 1.2               | Accele   | rating Transformer Models in Training          | 6    |  |

|    | 1.3               | Resear   | ch Contributions                               | 10   |  |

|    | 1.4               | Outlin   | e                                              | 11   |  |

| 2  | Back              | kground  | l and Motivation                               | 12   |  |

|    | 2.1               | CNN      | background and trends                          | 12   |  |

|    |                   | 2.1.1    | Various types of convolution (CONV) operations | 12   |  |

|    |                   | 2.1.2    | Trends in CNN model architecture               | 14   |  |

|    |                   | 2.1.3    | EfficientNet: A state-of-the-art CNN model     | 17   |  |

|    | 2.2               | Transf   | ormer background and trends                    | 20   |  |

|   |     | 2.2.1   | Bidirectional encoder representations from transformers                         |    |

|---|-----|---------|---------------------------------------------------------------------------------|----|

|   |     |         | (BERT)                                                                          | 20 |

|   |     | 2.2.2   | Trends in training transformer models                                           | 21 |

|   | 2.3 | Baseli  | ne DNN acceleration architecture                                                | 23 |

|   | 2.4 | Motiv   | ation                                                                           | 25 |

|   |     | 2.4.1   | Challenges of computing memory-intensive CNN layers .                           | 25 |

|   |     | 2.4.2   | Opportunity for load balancing in BERT training                                 | 28 |

| 3 | DN  | N accel | erator tailored for accelerating memory-intensive operations                    | 32 |

| 4 | MV  | P: A C  | NN accelerator with <u>Matrix</u> , <u>Vector</u> , and <u>Processing-near-</u> |    |

|   | men | nory un | its                                                                             | 35 |

|   | 4.1 | Contr   | ibution                                                                         | 35 |

|   |     | 4.1.1   | MVP organization                                                                | 35 |

|   |     | 4.1.2   | How depth-wise processing element (DWPE) operates                               | 38 |

|   |     | 4.1.3   | How processing-near-memory unit (PNMU) operates                                 | 41 |

|   |     | 4.1.4   | Overlapping the operation of DW-CONV with PW-CONV                               | 42 |

|   |     | 4.1.5   | Considerations for designing DWIB                                               | 44 |

|   | 4.2 | Evalua  | ation                                                                           | 45 |

|   |     | 4.2.1   | Experimental setup                                                              | 46 |

|   |     | 4.2.2   | Performance and energy evaluation                                               | 47 |

|   |     | 4.2.3   | Comparing MVP with NVDLA                                                        | 52 |

|   |     | 4.2.4   | Exploring the design space of MVP architecture                                  | 54 |

|   |     | 4.2.5   | Evaluating MVP with various SysAr configurations                                | 57 |

|   | 4.3 | Relate  | d Work                                                                          | 57 |

| 5  | Load | d Balan | cing Techniques for BERT Training | 61 |

|----|------|---------|-----------------------------------|----|

|    | 5.1  | Contri  | bution                            | 61 |

|    |      | 5.1.1   | Tiled architecture                | 61 |

|    |      | 5.1.2   | DRAM traffic shaping              | 64 |

|    |      | 5.1.3   | Resource sharing                  | 66 |

|    | 5.2  | Evalua  | ation                             | 68 |

|    |      | 5.2.1   | Experimental setup                | 68 |

|    |      | 5.2.2   | Performance evaluation            | 69 |

| 6  | Disc | ussion  |                                   | 73 |

| 7  | Con  | clusion |                                   | 78 |

| RI | EFER | ences   |                                   | 79 |

| 국  | 문초록  |         |                                   | 98 |

# List of Tables

| 2.1 | Categorization of operation types used in various CNN models. |    |  |  |  |

|-----|---------------------------------------------------------------|----|--|--|--|

|     | (* means that it is only used at the initial layer.)          | 16 |  |  |  |

| 4.1 | SysAr, VU-DW, PNMU, and DRAM specifications                   | 45 |  |  |  |

# List of Figures

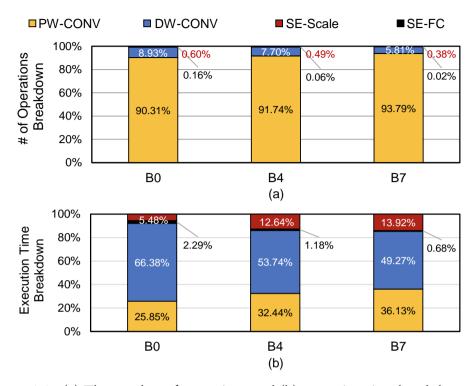

| 1.1 | (a) The number of operations and (b) execution time break-             |    |

|-----|------------------------------------------------------------------------|----|

|     | down of EfficientNet-B0/B4/B7 of the evaluated systolic-array-         |    |

|     | based accelerator (configurations are specified in Section 4.2.1).     |    |

|     | NORM, ACT, and POOL operations are not included as their               |    |

|     | execution time is hidden through pipelining                            | 5  |

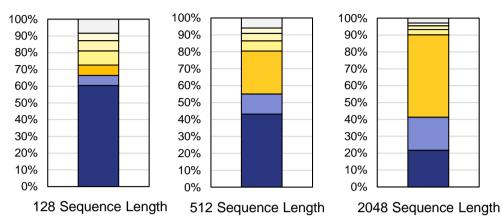

| 1.2 | Execution time breakdown of BERT-Large training using A100.            |    |

|     | Here, 128, 512, and 2048 sequence lengths are used by BERT-            |    |

|     | Large, and Megatron-LM [64]. We obtain the results using the           |    |

|     | latest NVIDIA code [67]                                                | 7  |

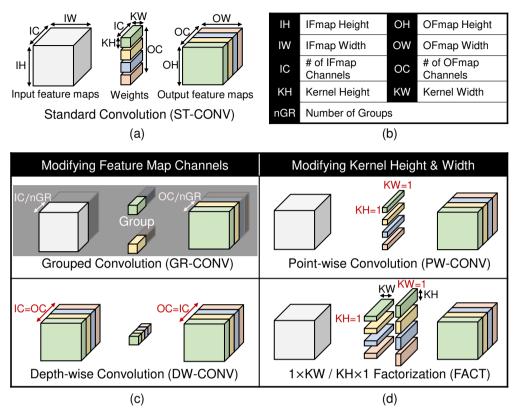

| 2.1 | (a) ST-CONV (in general, ST-CONV includes PW-CONV, but                 |    |

|     | we distinguish the two terms to emphasize whether the kernel           |    |

|     | size is $1 \times 1$ or not), (b) abbreviations for IFmaps, OFmaps and |    |

|     | weights, (c) CONVs with different ways to refer channels, and          |    |

|     | (d) CONVs with different kernel configurations                         | 13 |

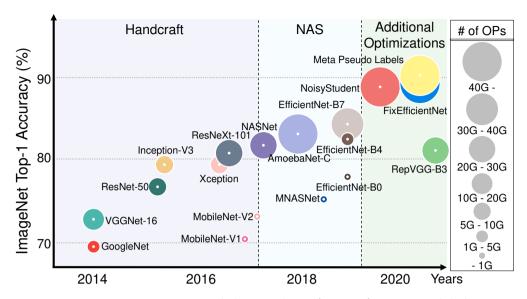

| 2.2 | Top-1 accuracy and the number of OPs of CNN models by year.      |    |

|-----|------------------------------------------------------------------|----|

|     | Handcraft refers to the CNN models in which various configu-     |    |

|     | rations are manually tuned by researchers until mid-2017. The    |    |

|     | radius of a circle is proportional to the number of MAC opera-   |    |

|     | tions required by the models.                                    | 15 |

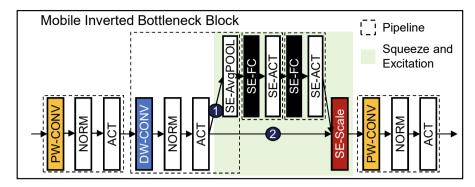

| 2.3 | Mobile inverted bottleneck block (MBConv) of EfficientNet        | 18 |

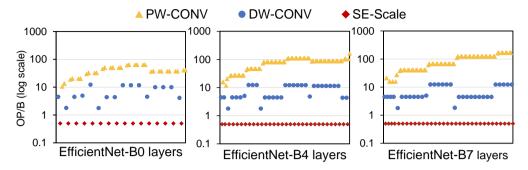

| 2.4 | Operations per byte (OP/B) of EfficientNet-B0/B4/B7 layers.      |    |

|     | The leftmost column represents the layer processing an input im- |    |

|     | age. We only show PW-CONV, DW-CONV, and SE-Scale be-             |    |

|     | cause they occupy most operations of the models. It is assumed   |    |

|     | that all three operations use 8-bit data type                    | 19 |

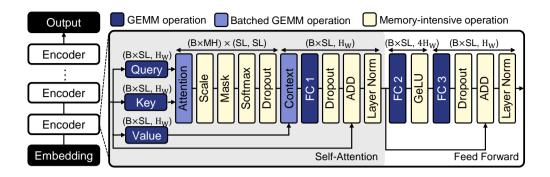

| 2.5 | BERT model structure. Self-attention and feed forward represent  |    |

|     | gray and white ranges within an encoder. B, SL, H, and MH refer  |    |

|     | to batch, sequence length, hidden, and multi-head, respectively. |    |

|     | Equations such as (B×SL, $H_W$ ), (B×MH)×(SL, SL) indicate the   |    |

|     | output size                                                      | 20 |

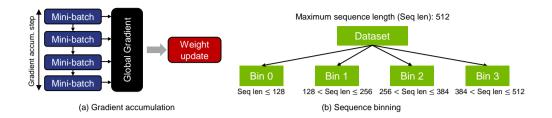

| 2.6 | (a) Gradient accumulation. (b) Sequence binning                  | 21 |

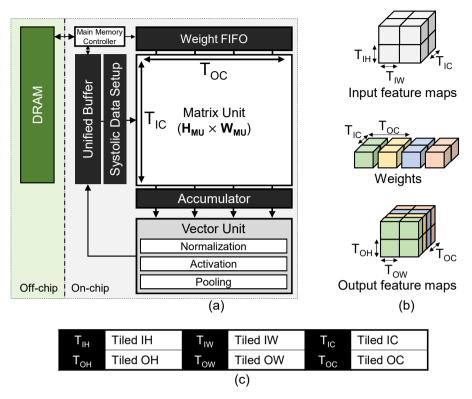

| 2.7 | (a) Baseline systolic-array architecture (SysAr). When SysAr     |    |

|     | computes a CONV layer, IC and OC are mapped to each row          |    |

|     | and column of MU [75,76] without using im2col [16]. (b) Tiling   |    |

|     | features of ST/PW-CONV in SysAr. Tiling notations are listed     |    |

|     | in (c)                                                           | 23 |

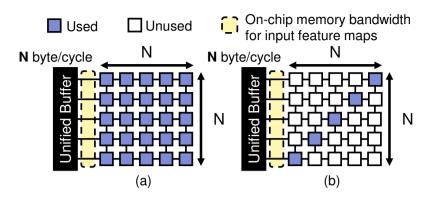

| 2.8  | MAC and on-chip memory bandwidth used inside of MU when               |    |

|------|-----------------------------------------------------------------------|----|

|      | $N{\times}N$ SysAr computes CONV (assuming that IC and OC are         |    |

|      | bigger than N): the cases of (a) executing ST-CONV or PW-             |    |

|      | CONV and (b) executing DW-CONV.                                       | 26 |

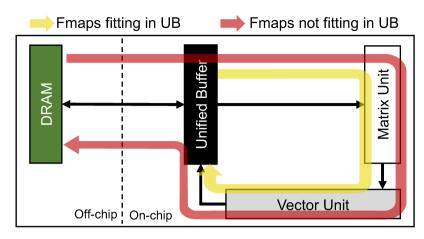

| 2.9  | Data movement patterns inside SysAr when performing SE-Scale.         |    |

|      | Fmaps can be read from either UB or DRAM, depending on their          |    |

|      | size. We focus on only Fmaps because they are much larger than        |    |

|      | the scale factors.                                                    | 27 |

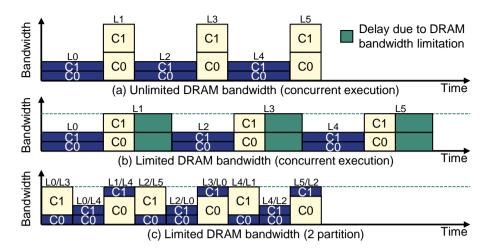

| 2.10 | Example of a memory traffic distribution over time [51]: (a)          |    |

|      | concurrent execution with an unlimited DRAM bandwidth, (b)            |    |

|      | concurrent execution with a limited DRAM bandwidth and (c)            |    |

|      | partitioning of PE tiles into two clusters (C0 and C1). The blue      |    |

|      | layers (L0, L2, L4) are GEMM operations, and the yellow layers        |    |

|      | (L1, L3, L5) are memory-intensive operations                          | 29 |

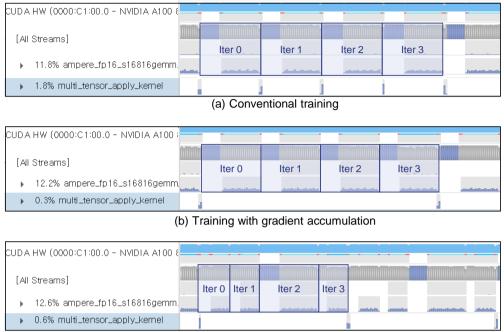

| 2.11 | Execution time of various training methods using the NVIDIA           |    |

|      | Nsight system profiler [66]: (a) conventional training, (b) train-    |    |

|      | ing with gradient accumulation, and (c) training with gradi-          |    |

|      | ent accumulation and sequence binning. We set the maximum             |    |

|      | SL size to 128 and used four gradient accumulation steps. The         |    |

|      | Nsight system uses <i>multi_tensor_apply_kernel</i> as the weight up- |    |

|      | date kernel                                                           | 30 |

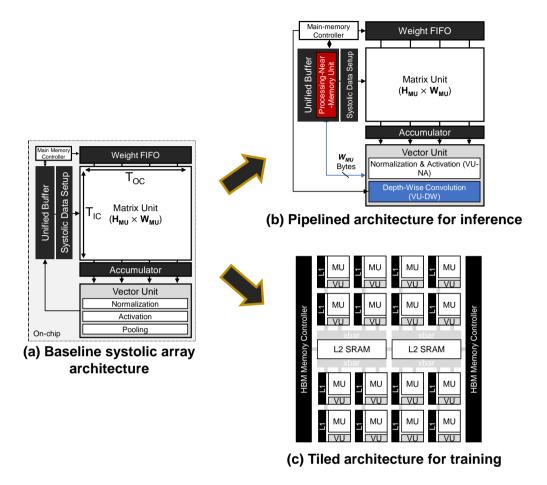

| 3.1  | (a) Baseline systolic array architecture. (b) A pipelined architec-   |    |

|      | ture tailored for accelerating inference. (c) A tiled architecture    |    |

|      | tailored for accelerating training.                                   | 33 |

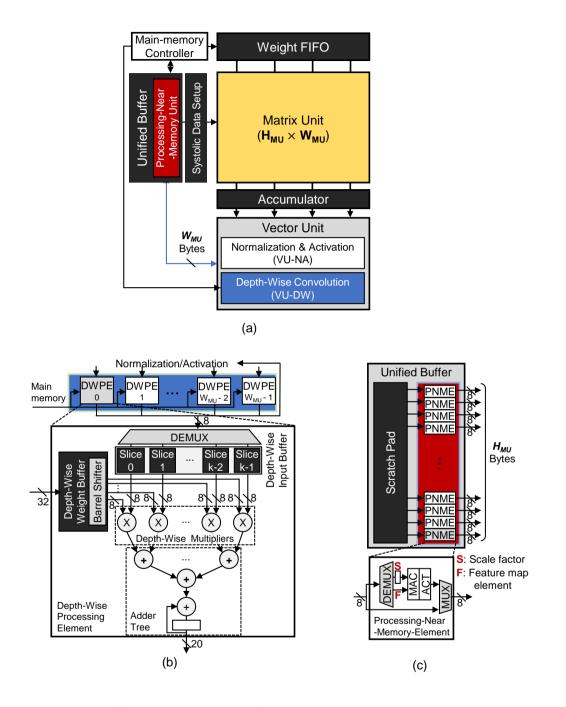

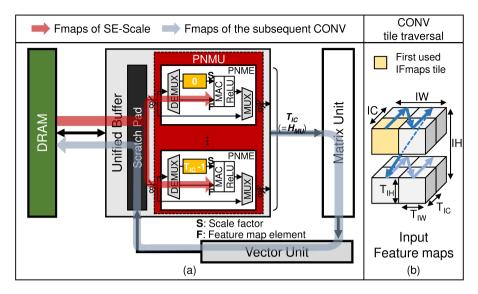

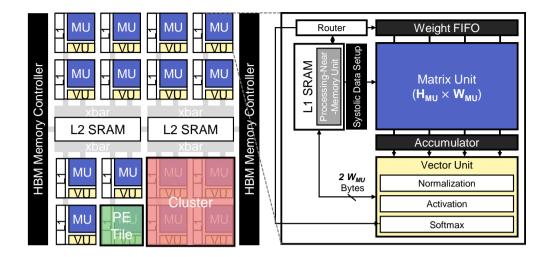

- 4.1 (a) MVP architecture (the red and blue parts represent the units added to the baseline SysAr), (b) VU–DW, and (c) PNMU. . . . 36

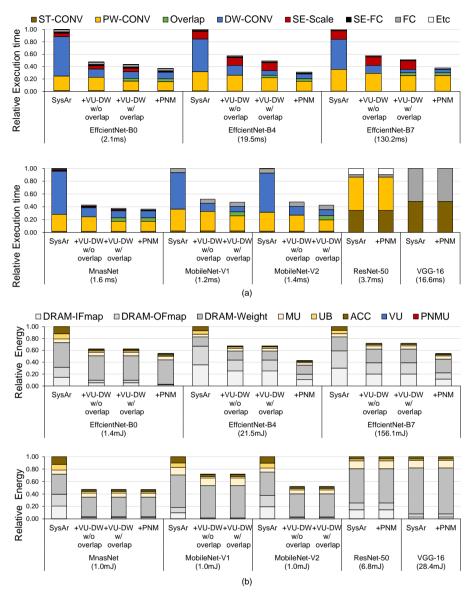

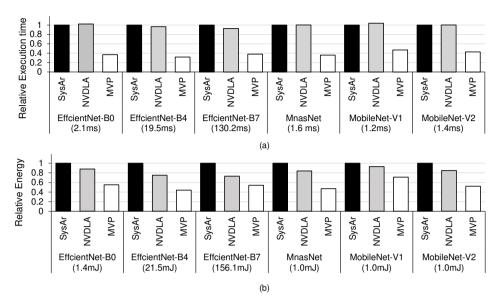

| 4.6 | (a) Relative execution time and (b) relative energy consump-      |

|-----|-------------------------------------------------------------------|

|     | tion of MVP over SysAr by incrementally applying VU-DW,           |

|     | the overlapped execution between PW-CONV and DW-CONV              |

|     | (shown as overlap), and PNMU. The absolute execution time         |

|     | and energy comsumption of the baseline SysAr is shown below       |

|     | the name of each CNN model. The execution time of MobileNet-      |

|     | V2 with SysAr is in a similar ball park to the reported execution |

|     | time of EdgeTPU [30] (2.6ms), which has the same peak FLOPS       |

|     | as the evaluated SysAr.                                           |

48

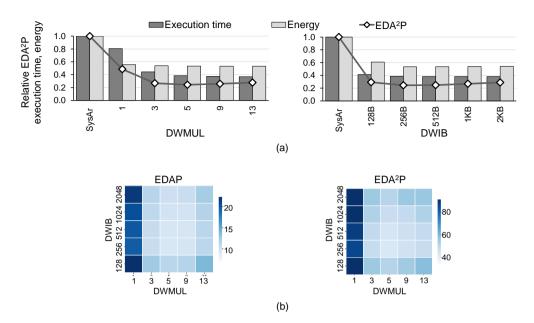

4.9 (a) Execution time, Energy, and EDA<sup>2</sup>P when the number of DWMULs is varied for a 256B DWIB size (Left side) when the DWIB size is varied for 5 DWMULs (Right side). (b) EDAP and EDA<sup>2</sup>P heatmap by the number of DWMULs and the DWIB size (the lower, the better [61]).

54

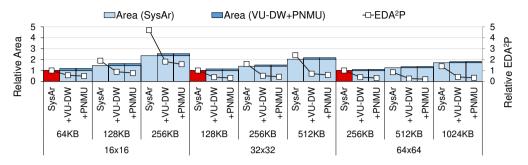

- 4.10 Area and EDA<sup>2</sup>P of MVP while varying MU, UB, and ACC parameters. The outermost category on the x-axis represents the MU size and the inner category represents the UB size. We select a candidate configuration that fits UB and ACC capacity in proportion to the change in MU size and set ACC as one fourth of the UB size. We obtain the design parameters of MVP for each SysAr configuration by using the design space exploration conducted in Section 4.2.4.  $EDA^2P$  values are calculated as the geometric mean for the target CNN models. Both  $EDA^2P$  and area are expressed as relative values based on each SysAr configuration, which has the smallest UB in each MU size (colored red). 56 5.1 Baseline tiled architecture. 62

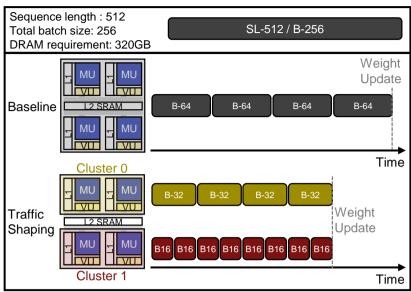

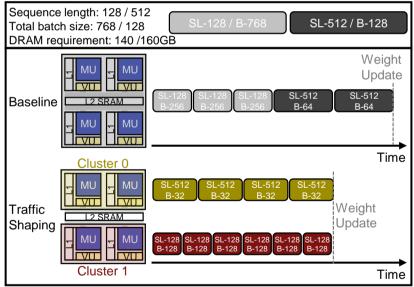

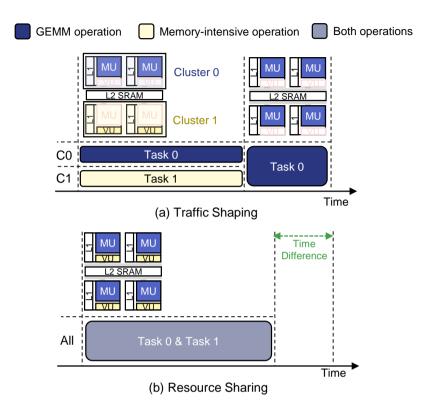

- 5.3 Figure 8. Mapping description and timing diagram of (a) traffic shaping and (b) resource sharing. Red indicates that the computation unit does not operate. C0 and C1 denote clusters 0 and 1, respectively.

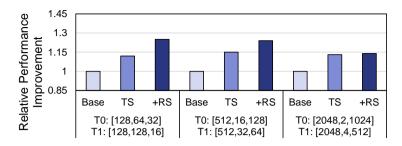

5.4 Relative performance improvement with the same SL during BERT–Large training. We incrementally apply traffic shaping (TS) and

- resource sharing (RS) over the baseline (Base). The task is expressed as [SL, mini-batch, gradient accumulation step]. .... 69

- 5.5 Relative performance improvement with different SLs. We incrementally apply traffic shaping (TS) and resource sharing (RS) the over baseline (Base). The task is expressed as [SL, mini-batch, gradient accumulation step]. Blue represents the results of the same SL, and yellow denotes the results of different SLs. . . . 71

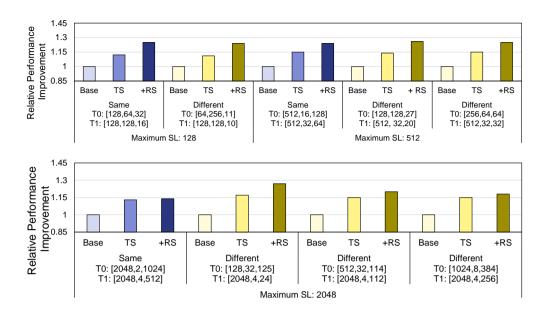

| 6.1 | Classification of places handling DW-CONV in modern DNN           |    |

|-----|-------------------------------------------------------------------|----|

|     | accelerators. We further subdivide the optimization methods about |    |

|     | a matrix unit (MU)                                                | 74 |

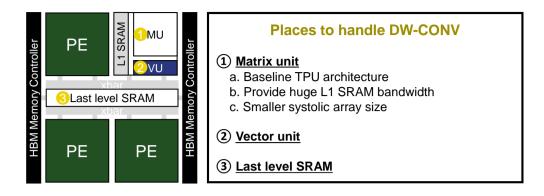

| 6.2 | Comparison of baseline TPU v3 and FAST architectures when         |    |

|     | processing DW-CONV                                                | 75 |

| 6.3 | Use case for load balancing technique.                            | 77 |

### Chapter 1

### Introduction

Machine learning is one of the most popular applications today, and deep neural networks (DNNs) are the most influential aspect of machine learning. Although the popularity of DNNs has been growing, they remained out of the limelight initially. Early DNNs [57] operated successfully, but the performance of the computation units at the time could not cope with the vast amounts of computation. Thus, researchers mainly used statistical learning methods [46] such as those known as regression, tree, clustering, and support vector machine, as they are associated with smaller computational loads compared to the use of a DNN.

The advent of GPUs directly addressed the greatest problem facing DNNs. With the continuous development of semiconductor processes, modern data– parallel architectures have been able to provide massive computational perfor– mance advancements within a single chip. Early DNNs undertook significant

This chapter is based on [59].

<sup>&</sup>quot;MVP: An Efficient CNN Accelerator with Matrix, Vector, and Processing–Near–Memory Units", ©2022 by Sunjung Lee and Jaewan Choi and Wonkyung Jung and Byeongho Kim and Jaehyun Park and Hweesoo Kim and Jung Ho Ahn, is licensed under CC BY 4.0. https://doi.org/10.1145/3497745.

numbers of computations, implying that it was difficult to use them in commercial services. However, the combination of the DNN and GPU [54] accelerated the development of related algorithms. In particular, vision and natural language processing evolved considerably, and various studies [21, 22, 38, 39, 41, 42, 44, 54, 64, 73, 77, 79, 83 – 87, 89, 103] using convolution (CONV) and transformers were introduced.

As DNNs have been established as non-fungible applications, specialized DNN accelerators have emerged. Google [50] independently developed a tensor processing unit that provided performance of 92 TOPS and used it for the first time in their service. NVIDIA [12, 19, 20, 68] provided up to 800 TFLOPs of the computational performance by adding a tensor core designed for processing DNNs on the GPU. In addition, many studies [1, 2, 7, 10, 13, 14, 24 – 26, 28, 33, 36, 37, 43, 47 – 50, 56, 62, 63, 72, 78, 80, 81, 92 – 94, 99, 100, 105] have introduced hardwares for DNN acceleration. Therefore, these hardwares significantly reduced the execution time of DNNs.

In a DNN, CONV and general matrix multiplication (GEMM) account for most of the computations. Conventional DNN accelerators are designed to utilize massive parallelism and abundant data reuse by considering the characteristics of these operations. However, the direction of accelerator research has focused on compute-intensive operations, leading to several problems. For the first time, variants of CONV are not processed efficiently because the structure is optimized for the standard CONV. Second, as the execution time of compute-intensive operations decreases, the impact of memory-intensive operations, which formerly required minor amounts, increases.

In this dissertation, we propose a novel DNN accelerator and load balancing

techniques to address the aforementioned challenges. We propose a customized accelerator that efficiently processes the latest convolutional neural network (CNN) models for CNN inference. We also propose load balancing techniques and supporting hardware to accelerate both compute– and memory–intensive operations in the transformer training.

#### 1.1 Accelerating Depth-wise Convolution on Edge Device

Convolutional neural networks (CNNs) are used in a variety of applications such as image recognition and object detection. Mobile and edge devices are becoming a primary platform for CNN inference due to superior response time, security, and privacy. Major smartphone companies such as Apple, Google, and Samsung deploy CNN inference engines in their devices [6,31,80]. By 2022, 7.3 billion mobile device users are projected to have on–device artificial intelligence (AI) capability [27,82], spurring the need for efficient CNN inference acceler– ators.

As standard convolution (ST-CONV) layers dominated the computation of conventional CNN models, a large body of accelerator research has focused on this layer type [10, 13, 14, 24, 26, 50, 63, 92, 94, 99]. Among those, accelerators supporting systolic execution or its variants [50, 65] are gaining popularity due to superior performance, energy, and area efficiency. These architectures efficiently exploit massive parallelism and abundant data reuse opportunities of input feature maps (IFmaps) in computing output feature maps (OFmaps) for CONV layers. Hence, major industry players such as Google have already adopted this systolic-array-based acceleration in their production [30, 50].

The CNN models have evolved to reduce the arithmetic operations while retaining or improving recognition accuracy. In the early days, designers manually determined the model configurations, such as layer types, depth (the number of layers), and kernel sizes. ST-CONV with a kernel size of 3×3 or larger was dominant. As these ST-CONV layers are computationally heavy, various CONV types have been proposed to reduce the number of operations by changing the kernel shape or reducing the number of channels being referenced [18, 84, 85].

The advent of neural architecture search (NAS [106]) has led to several changes in configuring CNNs. Early NAS studies reduced the number of operations drastically by mostly using ST-CONV with 1×1 kernel size (called pointwise CONV, PW-CONV) and depth-wise CONV (DW-CONV). However, due to excessive use of skip connection and unstructured layer configurations, the actual execution time was longer than the time predicted by the number of arithmetic operations. Therefore, the latest CNN models constructed by NAS utilize a building block (BB) composed of PW-CONV, DW-CONV, and squeeze-and-excitation (SE) as a unit since [86], in which memory-intensive operations have become prevalent.

The systolic array (SysAr) architecture has structural limitations in handling these emerging, memory–intensive CNN operations. DW–CONV only uses a single IFmap to create a single OFmap. Therefore, SysAr that feeds a massive number of MACs in its matrix unit (MU) using a limited bandwidth from the unified buffer (UB) in a wavefront manner cannot fully utilize its MACs on DW–CONV. The other accelerator [15] fully utilizes the MACs it owns by arranging those with distributed register files and hierarchical on–chip networks, although

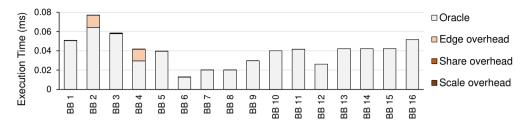

Figure 1.1: (a) The number of operations and (b) execution time breakdown of EfficientNet-B0/B4/B7 of the evaluated systolic-array-based accelerator (con-figurations are specified in Section 4.2.1). NORM, ACT, and POOL operations are not included as their execution time is hidden through pipelining.

at a significant cost in the area [56] and wire energy [33].

When normalization (NORM) and activation (ACT) operations are performed prior to CONV, SysAr becomes inefficient because its MU and vector unit (VU) cannot be pipelined. PW-CONV occupies more than 90% of the number of operations but takes under 40% in execution time (see Figure 1.1). Memory-intensive operations such as DW-CONV and SE-Scale (the operation of applying the squeezed weights to feature maps) take the remaining 60% of execution time, demonstrating the importance of accelerating memory-intensive operations for the latest CNNs. In this paper, we propose an MVP architecture composed of Matrix, Vector, and Processing-near-memory units (more accurately, processing-near-on-chipunified-memory units) to efficiently process both compute- and memory-intensive CNN operations with a small area overhead on the baseline SysAr architecture. VU of SysAr is augmented to process DW-CONV effectively by adding an array of arithmetic units, whose size is much smaller than that of MU. VU stores a tile of an OFmap produced by PW-CONV in small-but-high-throughput buffers and performs DW-CONV with the array of multipliers and adder trees, exploiting the key characteristic of DW-CONV that the reuse distance of its IFmaps is short. Processing-near-memory unit (PNMU) performs elementwise operations (NORM, ACT, and SE-Scale) that are processed immediately prior to CONV, which are performed at MU, to eliminate unnecessary on-/offchip memory access. VU and PNMU significantly reduce the execution time of memory-intensive operations as these operations can mostly be overlapped with computation for the nearby PW-CONV layers.

#### 1.2 Accelerating Transformer Models in Training

The transformer [91] is one of the most popular deep neural networks (DNNs) for language modeling, machine translation, question & answering, and text generation. BERT [22] and GPT [73], which are the modified versions of the vanilla transformer model, accelerate its popularity by improving recognition accuracy levels such that they are close to those of a human. However, due to continuous changes of these models to increase their accuracy, the transformer model is now associated with certain side effects such as a massive increase in

■GEMM ■BMM ■Softmax+Dropout ■Dropout+LayerNorm ■GeLU ■ADD □Etc

Figure 1.2: Execution time breakdown of BERT-Large training using A100. Here, 128, 512, and 2048 sequence lengths are used by BERT-Large, and Megatron-LM [64]. We obtain the results using the latest NVIDIA code [67].

the number of computations and a large model size.

To process DNN models efficiently, many DNN accelerator studies [1, 2, 7, 10, 12-14, 19, 20, 24-26, 28, 33, 36, 37, 43, 47-50, 56, 59, 62, 63, 68, 72, 78, 80, 81, 92-94, 99, 100, 105] have been introduced. As compute-intensive operations such as GEMM and convolution account for most of the computations in DNN models, conventional DNN accelerators are designed to utilize massive parallelism and abundant data reuse by considering the characteristics of these operations. However, because the direction of accelerator research is mainly focused on the compute-intensive operations, the execution time of memory-intensive operations becomes a significant factor. Figure 1.2 shows the execution time breakdown of BERT-Large training. Depending on sequence length (SL), memory-intensive operations such as softmax, layer normalization, and GeLU take up to 60% of the execution time. Also, batched matrix multiplication (BMM) with 10 times fewer operations per byte (OP/B) than GEMM

occupies up to 20% of the execution time. Therefore, it is important to reduce the impact of memory-intensive operations in the transformer.

To reduce the execution time of memory-intensive operations, there have been load balancing studies [8, 51, 52] by partitioning multiple computing units within a single chip, and processing tasks in each partition asynchronously. [51] alleviates temporal fluctuations in the memory bandwidth demands due to the various computational characteristics of the layers through DRAM traffic shaping. AI-MT [8] and MAGMA [52] propose task scheduling methods for multitenant inference. They categorize DNN models into several dependency-free groups according to the compute- or memory-intensive characteristics. Then, they map dependency-free DNN groups on multiple accelerator cores. Lastly, they execute multiple dependency-free groups concurrently. In this way, they can reduce the number of stalls caused by the DRAM bandwidth bottleneck.

However, conventional DNN training does not process multiple tasks simultaneously in an accelerator due to several limitations. In cloud data centers, the inference uses a small number of batch sizes to comply with the quality of service (QoS) requirements. When inference task uses relatively few batch sizes, it cannot utilize all the computing units included in the single accelerator. Also, multi-tenant inference can be processed in parallel because there are no dependencies between multiple inference tasks. Therefore, previous load balancing studies could apply multi-tenant inference by allocating multiple inference tasks in a single accelerator. In contrast, the training processes only a single DNN model in the single accelerator because it uses a large batch size. Also, because the training should update weight parameters every time for every mini-batch, multiple mini-batches cannot be processed in parallel. In this paper, we propose load balancing techniques that utilize the latest DNN training methods, in this case gradient accumulation [29], and sequence binning [67]. Gradient accumulation performs weight updates at once after collecting the gradients of several mini–batches. This relieves the dependency between mini–batches so that during training multiple tasks can be processed in parallel in an accelerator. Sequence binning allocates SL variably according to the padded tokens in the input.

We propose traffic shaping techniques using gradient accumulation. Traffic shaping partitions a single accelerator into multiple clusters and processes multiple clusters asynchronously during the gradient accumulation step. Traffic shaping reduces the execution time of memory–intensive operations by allevi– ating DRAM bandwidth fluctuations during the weight update. Traffic shap– ing realizes an additional performance improvement through sequence binning. Traffic shaping is capable of high performance improvements when tasks with different computational characteristics are assigned to each cluster. Because se– quence binning provides various SLs, it contributes to a further performance improvement.

We also propose a resource sharing technique that executes the matrix units and vector units of all clusters simultaneously when the compute– and memory– intensive operations are performed concurrently on different clusters. Resource sharing reduces the execution time of the compute–intensive operations. To the best of our knowledge this paper is the first work to address training acceleration with load balancing techniques.

### 1.3 Research Contributions

In this dissertation, we make the following contributions:

- We categorize the layer configurations of various CNN models and identify that the latest CNN models are composed of BBs that utilize PW-CONV, DW-CONV, and SE.

- We identify that the arithmetic resource of systolic-array-based CNN accelerators is severely underutilized when processing the memory-intensive operations prevalent in the BBs of the latest CNN models.

- We propose an MVP architecture that combines Matrix, Vector, and Processingnear-memory units to efficiently process both compute- and memoryintensive operations of the latest CNN models with a small area overhead.

- MVP improves performance by 2.6× and reduces energy consumption by 47% on average over EfficientNet-B0/B4/B7, MnasNet, and MobileNet-V1/V2 with a 9% area overhead over the baseline SysAr.

- We apply load balancing techniques in transformer training acceleration using gradient accumulation which is the latest DNN training methods.

- We use sequence binning to realize additional performance improvements in the load balancing techniques.

- We reduce the execution time of compute-intensive operations through resource sharing with the simultaneous execution of matrix and vector units.

- Our load balancing techniques improve performance by up to 1.27× compared to the baseline when we train a BERT–Large model.

### 1.4 Outline

The organization of this dissertation is as follows. Chapter 2 describes the trends of the latest DNN models and the challenges of existing accelerator when they process the latest DNN models. Chapter 3 summarize two DNN accelerators targeting inference and training. In chapter 4, We propose a CNN accelerator tailored for processing DW–CONV, including multipliers, adder trees, and multi–banked buffered to meet the high memory bandwidth requirement. In Chapter 5, we propose tiled architecture and load balancing techniques to alle– viate temporal fluctuations in DRAM bandwidth and to efficiently utilize com– putation units. Chapter 6 discusses the use cases of both techniques and we present the conclusions in Chapter 7.

### Chapter 2

### Background and Motivation

#### 2.1 CNN background and trends

#### 2.1.1 Various types of convolution (CONV) operations

ST-CONV is a basic type of CONV where the size of a kernel,  $KH \times KW$ , is typically larger than 1×1. It convolutes IFmaps and weights to produce OFmaps, requiring  $KH \times KW \times IC \times OH \times OW \times OC$  operations in total (see Figure 2.1(a)). Recent CNN models adopt new types of CONV layers to reduce the number of operations, either by limiting the number of input/output channels or using smaller kernels.

Grouped CONV (GR-CONV) and depth-wise CONV (DW-CONV) reduce the number of required operations compared to ST-CONV by dividing the input channels into multiple groups of channels. We call the number of groups nGR. GR-CONV requires  $KH \times KW \times (\frac{IC}{nGR}) \times OH \times OW \times (\frac{OC}{nGR}) \times nGR$  op-

This chapter is based on [59].

<sup>&</sup>quot;MVP: An Efficient CNN Accelerator with Matrix, Vector, and Processing–Near–Memory Units", ©2022 by Sunjung Lee and Jaewan Choi and Wonkyung Jung and Byeongho Kim and Jaehyun Park and Hweesoo Kim and Jung Ho Ahn, is licensed under CC BY 4.0. https://doi.org/10.1145/3497745.

Figure 2.1: (a) ST-CONV (in general, ST-CONV includes PW-CONV, but we distinguish the two terms to emphasize whether the kernel size is  $1 \times 1$  or not), (b) abbreviations for IFmaps, OFmaps and weights, (c) CONVs with different ways to refer channels, and (d) CONVs with different kernel configurations.

erations, which are reduced by a factor of nGR times compared to ST-CONV (see Figure 2.1(c)). DW-CONV is an extreme form of GR-CONV where nGR = IC = OC.

Point-wise CONV (PW-CONV) and Factorization (FACT) reduce the number of operations by using smaller kernels (see Figure 2.1(d)). PW-CONV exploits  $1 \times 1$  kernels. FACT factorizes a  $KH \times KW$  kernel into two: one with a  $1 \times KH$  size and the other with a  $KW \times 1$  size. Then it performs convolution for each of the two kernels, thereby reducing the total number of operations by a factor of  $\frac{(KH \times KW)}{(KH+KW)}$  times.

#### 2.1.2 Trends in CNN model architecture

Various CNN models have been proposed to increase the accuracy of image recognition and, at the same time, reduce the burden of computation (see Fig-ure 2.2).

Handcrafted models: In the early days, many researchers tried empirical studies, tuning myriads of parameters such as layer types, number of layers, channel size, and resolution by hand to improve the accuracy of CNN models. As the number of layers increases, the accuracy tends to increase, albeit with the following issues. First, CNN models are computationally hungry. Early CNN models populated just a few layers, but later models use dozens of layers or more, requiring lots of arithmetic operations (e.g., VGGNet [79] requires about 20G operations). Therefore, GoogleNet [84], Inception-V3 [85], Xception [18], and ResNext [97] adopted PW-CONV, FACT, DW-CONV, and GR-CONV, respectively, to reduce the number of arithmetic operations. Second, there was a time when training was nearly impossible if the number of layers exceeds a certain threshold due to a vanishing gradient problem during backpropagation. ResNet [38] addressed this problem using skip connection, paving the way for stacking hundreds of layers. Batch normalization (BN) [45] and SE [42] were proposed to further increase the accuracy of CNN models by changing the entire Fmap elements using element-wise operations.

NAS models: Because manually developing CNN models requires significant engineering efforts, NAS has been proposed to design the models automatically. NAS uses machine learning to explore efficient models in performance, computation complexity, and memory capacity by using various layer types developed in the handcrafted models as candidates. In the early NAS works,

Figure 2.2: Top-1 accuracy and the number of OPs of CNN models by year. Handcraft refers to the CNN models in which various configurations are manually tuned by researchers until mid-2017. The radius of a circle is proportional to the number of MAC operations required by the models.

NASNet [106] and AmoebaNet [74] obtained high accuracy, but they required a huge amount of operations and suggested complex structures. Thus, the actual hardware execution time was much longer than the execution time predicted by the number of operations. To solve this problem, MnasNet [86] simplified the model structure using a BB, which was first used in ResNet, as a candidate for design search. EfficientNet [87] expanded MobileNet-V2 [77] and MnasNet to obtain high accuracy with fewer operations than the early NAS models.

Additional optimizations: Because EfficientNet demonstrated strength in computational complexity and accuracy to the other CNN models, subsequent studies tend to use it as a baseline model. NoisyStudent [96] increased the number of layers, channel size, and resolution of EfficientNet and changed the training method to perform pre-processing using ImageNet data and then proceed

|                         | ST           | PW           | FACT         | DW           | GR           | BB           | SE           |

|-------------------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|

| VGGNet [79]             | $\checkmark$ |              |              |              |              |              |              |

| GoogleNet [84]          | $\checkmark$ | $\checkmark$ |              |              |              |              |              |

| ResNet [38]             | $\checkmark$ | $\checkmark$ |              |              |              | $\checkmark$ |              |

| Inception-V3 [85]       | $\checkmark$ | $\checkmark$ | $\checkmark$ |              |              |              |              |

| Xception [18]           | *√           | $\checkmark$ |              | $\checkmark$ |              |              |              |

| ResNeXt [97]            | *√           | $\checkmark$ |              |              | $\checkmark$ | $\checkmark$ |              |

| MobileNet-V1 [41]       | *√           | $\checkmark$ |              | $\checkmark$ |              |              |              |

| MobileNet-V2 [77]       | *√           | $\checkmark$ |              | $\checkmark$ |              | $\checkmark$ |              |

| NASNet [106]            | *√           | $\checkmark$ |              | $\checkmark$ |              |              |              |

| AmoebaNet [74]          | *√           | $\checkmark$ | $\checkmark$ | $\checkmark$ |              |              |              |

| MnasNet [86]            | *√           | $\checkmark$ |              | $\checkmark$ |              | $\checkmark$ | $\checkmark$ |

| EfficientNet [87]       | *√           | $\checkmark$ |              | $\checkmark$ |              | $\checkmark$ | $\checkmark$ |

| NoisyStudent [96]       | *√           | $\checkmark$ |              | $\checkmark$ |              | $\checkmark$ | $\checkmark$ |

| FixEfficientNet [89]    | *√           | $\checkmark$ |              | $\checkmark$ |              | $\checkmark$ | $\checkmark$ |

| Meta Pseudo Labels [71] | *√           | $\checkmark$ |              | $\checkmark$ |              | $\checkmark$ | $\checkmark$ |

| RepVGG [23]             | $\checkmark$ |              |              |              |              |              |              |

Table 2.1: Categorization of operation types used in various CNN models. (\* means that it is only used at the initial layer.)

with self-training using Instagram data. FixEfficientNet [89] improved accuracy by applying image augmentation to both training and test time using EfficientNet. Meta Pseudo Labels [71] achieved a top-1 accuracy of over 90% for the first time using EfficientNet as a baseline model. Meta Pseudo Labels used knowledge distillation [40] which trains a student network with a pre-trained teacher network. For the training, it used the ImageNet dataset as labeled data and the JFT-300M [40,83] dataset as unlabeled data. RepVGG [23] is designed to achieve high utilization on conventional accelerators or GPUs. RepVGG uses skip connection for training and excludes it for inference to simplify the model and to reduce inference time. Also, RepVGG does not use DW-CONV and

PW-CONV which undergo low utilization; instead it only uses ST-CONV like VGGNet. Although RepVGG is suitable for conventional hardware, it has lower top-1 accuracy compared to the EfficientNet variants.

Even though the components of the CNN models have been changed over time, there is little change in the fundamental structure and the types of CONV in CNN models since MnasNet. CNN models mainly use fixed compositions consisting of repeated BBs, including PW-CONV, DW-CONV, and SE (Table 2.1). PW-CONV and DW-CONV are popular as they are the most efficient to reduce the number of operations. BB is used to simplify the structure of the models. SE, like BN, increases accuracy by considering the degree of influence between Fmaps with a small computational cost. In contrast, ST-CONV is used only as the initial layer in the latest CNN models due to its high computational cost. GR-CONV does not appear in the latest CNN models, and FACT is rarely used even if they are candidates of NAS.

#### 2.1.3 EfficientNet: A state-of-the-art CNN model

EfficientNet [87] is a representative of more recent CNN models that use multiple BBs to achieve high accuracy with a relatively low computational cost. EfficientNet is an expanded structure of MobileNet-V2 and MnasNet that scales all three parameters (resolution, the number of channels, and the number of layers) concurrently as opposed to previous works [38,41,84] which scale only subsets of the three dimensions. EfficientNet introduces eight exemplar models (EfficientNet-B0~B7), which require 4~20× lower computational costs compared to the previous CNN models with similar recognition accuracy. For example, both EfficientNet-B0 and ResNet-50 achieve nearly 77% Top-1 accu-

Figure 2.3: Mobile inverted bottleneck block (MBConv) of EfficientNet.

racy, but they require 390M and 4.1G operations, respectively.

EfficientNet is a sequence of mobile inverted BBs (MBConvs). MBConv consists of the first PW-CONV followed by DW-CONV, SE, and the second PW-CONV (see Figure 2.3), where each CONV has trailing NORM and ACT layers. SE includes global average pooling (SE-AvgPOOL), fully connected layer (SE-FC), activation (SE-ACT), and element-wise multiplication (SE-Scale). SE first calculates scale factors for each channel using OFmap created by DW-CONV and then operates SE-Scale using the scale factors and the DW-CONV. There is a data dependency between DW-CONV and SE because each step uses the whole OFmaps directly. In step (), SE-AvgPOOL needs all of the Fmap elements to compute the average, and SE-FC needs all of the channels to get scale factors per channel. In step (2), SE-Scale multiplies the scale factors with OFmaps of DW-CONV which is stored at UB or DRAM because all the Fmaps were used in the previous step. Last, the second PW-CONV follows SE-Scale.

The compositional characteristics of MBConv make the arithmetic intensity of EfficientNet fluctuate a lot. Figure 2.4 shows operations per byte (OP/B) over

Figure 2.4: Operations per byte (OP/B) of EfficientNet-B0/B4/B7 layers. The leftmost column represents the layer processing an input image. We only show PW-CONV, DW-CONV, and SE-Scale because they occupy most operations of the models. It is assumed that all three operations use 8-bit data type.

the layers in EfficientNet-B0/B4/B7. The leftmost column in each graph represents the layer processing an input image. PW-CONV reuses an IFmap by OC times. Because EfficientNet populates more channels as it comes closer to the classification layer, OP/B increases from left to right on the graphs. DW-CONV produces an OFmap by using a single IFmap; therefore, EfficientNet's kernel sizes determine the degree of data reuse. EfficientNet uses 3×3 and 5×5 kernels. Similar to NORM and ACT (not shown in Figure 2.4), SE-Scale achieves a low OP/B due to the lack of Fmap data reuse in conducting element-wise operations. Even if the number of layers and functions differs by the network sizes (B0 being the smallest and B7 the largest), because OP/B fluctuates a lot and DW-CONV and element-wise operations appear frequently, CNN accelerators must be designed to perform both compute- and memory-intensive layers/functions equally well.

Figure 2.5: BERT model structure. Self-attention and feed forward represent gray and white ranges within an encoder. B, SL, H, and MH refer to batch, sequence length, hidden, and multi-head, respectively. Equations such as  $(B \times SL, H_W)$ ,  $(B \times MH) \times (SL, SL)$  indicate the output size.

# 2.2 Transformer background and trends

#### 2.2.1 Bidirectional encoder representations from transformers (BERT)

BERT [22] consists of an embedding layer, 24 encoder layers, and an output layer (see Figure 2.5). The encoder includes a self-attention layer and a feedforward layer. The self-attention layer includes GEMM (query, key, value, and FC 1 layers), batched GEMM (BMM) (attention, and context layers), and memory-intensive (scale, mask, softmax, dropout, add, and layer normalization layers) operations. The GEMM operation has an OP/B higher than 500 due to a massive data reusability. The BMM operation is less than 100 OP/B because (B x multi-head (MH)) GEMM operations are performed independently. BMM operations can degrade the performance due to a DRAM bandwidth bottleneck when using an accelerator with high computation performance. Because memory-intensive operations have less than 10 OP/B, a bandwidth bottleneck always occurs in all memory hierarchies.

Figure 2.6: (a) Gradient accumulation. (b) Sequence binning.

The proportion of the execution time for GEMM, BMM, and memoryintensive operations varies depending on the SL size. The layers between the attention and context layers change the output size quadratically according to the SL size. In contrast, the remaining layers increase linearly. Therefore, as shown in Figure 1.1, when the SL is small, the execution time for GEMM operations takes up a large portion. When the SL is not small, the execution time for BMM and memory-intensive operations takes up a large portion.

# 2.2.2 Trends in training transformer models

Training refers to the process of learning optimal weight parameters using a large dataset. The training consists of multiple pairs of a forward and a back–ward pass. A forward pass infers results by executing multiple layers with input data. During the forward pass, intermediate values are stored in DRAM, as intermediate values are used during the backward pass. After the forward pass, the classification layer calculates the loss. The backward pass is the step in which the weight parameters are redesigned using the intermediate values and loss. Training is conducted in mini–batch unit, referring to a pair consisting of one forward pass and one backward pass. The weight parameter is updated for each mini–batch.

Due to continuous changes such as increases in the model size and SL [11, 64, 73, 103] in the transformer, the transformer adopts new training methods.

Gradient accumulation: gradient accumulation [29] is proposed to solve the DRAM capacity problem of DNN accelerators. Due to increases in the model size and SL size, the DRAM capacity for intermediate values and weight parameters increases. Due to the limited DRAM capacity, the accelerators use small batch sizes for weight updates. Gradient accumulation increases the total batch size by performing multiple forward and backward passes during the gradient accumulation step and updating the weights at once as shown in Figure 2.6(a). The total batch size is the unit focused on during a single weight update. The mini-batch size is a unit that can be allocated within the DRAM capacity. The gradient accumulation step is calculated by dividing the total batch size by the mini-batch size. Gradient accumulation has the same effect found when multiple GPUs undertake data parallelism in a distributed learning [32].

Sequence binning: sequence binning [67] is proposed to eliminate redundant computations on padded tokens. In conventional training, if the input is less than the maximum SL, padded tokens are added to the input up to maximum SL. Training is then conducted using the maximum SL. However, sequence binning does not require the addition of padded tokens to the input, instead dis-tinguishing multiple inputs into multiple bins during data pre-processing step. For example, if the maximum SL is 512 and there are four bins, the total dataset is distinguished into a unit of 128 (see Figure 2.6(b)). Bin 0 stores less than 128 SL, and bin 1 stores SLs between 128 and 256. The other SLs are stored in the same way. After data pre-processing is finished, training is performed using various SLs.

Figure 2.7: (a) Baseline systolic-array architecture (SysAr). When SysAr computes a CONV layer, IC and OC are mapped to each row and column of MU [75, 76] without using im2col [16]. (b) Tiling features of ST/PW-CONV in SysAr. Tiling notations are listed in (c).

# 2.3 Baseline DNN acceleration architecture

TPU [50] and NVDLA [65] adopt systolic execution or its variants, achieving superior performance and energy efficiency than other architecture types [70] in performing CNN inference. SysAr fully utilizes the data reuse characteristics of CONV by operating  $\mathcal{O}(N^2)$  MACs with  $\mathcal{O}(N)$  on-chip memory bandwidth from UB in a systolic data flow manner (we assume the height ( $H_{MU}$ ) and width ( $W_{MU}$ ) of MU are both N). Because NVDLA similarly achieves high area and energy efficiency by multicasting IFmap elements to MACs, our proposed architecture can also be applied to NVDLA. In this paper, we use SysAr as a baseline.

SysAr consists of MU, UB, systolic data setup, weight FIFO, accumulator (ACC), main-memory controller, and VU that includes NORM/ACT/POOL units (see Figure 2.7(a)). MU is a systolic array, having MACs arranged in a two-dimensional form. We assume the weights and feature maps are 8-bit data. UB is an on-chip buffer that stores IFmaps and OFmaps. Through the systolic data setup, UB sends data to MU in a diagonal wavefront manner and saves the intermediate results. Weight FIFO temporarily stores a part of weights transferred from DRAM and sends them to the registers inside MU. ACC accumulates the partial sums calculated from MU and stores them inside the buffer until partial sums become complete OFmap elements. NORM/ACT/POOL units perform element-wise operations on the 32-bit OFmap elements in a pipelined manner; the OFmap elements are converted into 8-bit values and transferred to UB.

Although MU targets GEMM operations, it also provides specialized hardware [75], algorithm [76], and instruction set architecture [50] for CONV. Therefore, SysAr can perform CONV without converting a 3D Fmap into a 2D one (im2col). Figure 2.7(b) shows the tiles of Fmaps and weights and their dimensions. Each row of MU takes one of  $T_{IC}$  IFmap elements, while each column takes one of  $T_{OC}$  weights. Each IFmap element propagates sequentially from left to right, and the output, which is a partial sum, propagates from top to bottom. Here we call each column a SysAr lane.

The Fmaps are divided into tiles if they do not fit in the on-chip storage (UB or ACC). ACC limits the size of an output tile ( $T_{OW} \times T_{OH}$ ) to the capacity of

ACC divided by  $T_{OC}$ . Data traversal order is determined to maximize the data reuse of Fmaps and weights. Because the datapath from ACC to UB is unidirectional, each partial sum inside ACC must be a complete OFmap element. Thus, SysAr traverses IFmap and weights in all  $IC^-$ ,  $KW^-$ , and  $KH^-$  directions first.

# 2.4 Motivation

#### 2.4.1 Challenges of computing memory–intensive CNN layers

Conventional CNN accelerators focus on compute-intensive ST-CONV and PW-CONV operations. They consider only limited types of memory-intensive operations that immediately follow CONV, such as NORM, ACT, and POOL. As opposed to ST-CONV and PW-CONV, DW-CONV does not reuse IFmap between OCs. Therefore, DW-CONV hardly exploits the broadcasting and systolic execution techniques mainly for IFmap reuse in conventional CNN accelerators. This characteristic of DW-CONV makes MACs in MU underuti-lized or requires more on-chip memory bandwidth to fully utilize MACs.

Figure 2.8(a) shows MACs in use and on-chip memory bandwidth usage when performing ST-CONV or PW-CONV in an  $N \times N$  SysAr. At each cycle, the MACs in the leftmost column of MU takes N IFmap elements transferred from the on-chip memory. The IFmap elements shift from left to right at each cycle, so each element is reused by N weights. In a steady state where IFmap elements are distributed to all the MACs, N B/cycle on-chip bandwidth is enough to utilize all the  $N^2$  MACs. In contrast, DW-CONV requires each column of MACs to take IFmap elements from different OCs (see Figure 2.8(b)), not

Figure 2.8: MAC and on-chip memory bandwidth used inside of MU when  $N \times N$  SysAr computes CONV (assuming that IC and OC are bigger than N): the cases of (a) executing ST-CONV or PW-CONV and (b) executing DW-CONV.

taking advantage of multicasting in systolic execution. Therefore, even if DW– CONV has a significantly smaller computational load compared to ST–CONV and PW–CONV, it takes a large portion of execution time due to low MAC utilization. SysAr can only supply the on–chip bandwidth of *N* B/cycle even when processing DW–CONV. To fully utilize the  $N \times N$  MACs, DW–CONV requires  $\mathcal{O}(N^2)$  of on–chip memory bandwidth, one of the most expensive re– sources in conventional CNN accelerators.<sup>1</sup>

By contrast to SysAr, Eyeriss-v2 [15] adopts a hierarchical mesh structure in its memory system, having its on-chip memory bandwidth high enough to fulfill the bandwidth requirement of DW-CONV. This hierarchical structure exploits distributed SRAM for global buffer where each bank of the global buffer can transfer data simultaneously and connects several global buffer banks to local

<sup>&</sup>lt;sup>1</sup>The structural limitation of Edge TPU also makes it suffer from this problem, resulting in a much larger execution time than predicted by the number of operations [34]. To resolve this issue, Edge TPU replaces DW-CONV with more hardware-friendly ST-CONV at a significantly increased computational cost.

Figure 2.9: Data movement patterns inside SysAr when performing SE–Scale. Fmaps can be read from either UB or DRAM, depending on their size. We focus on only Fmaps because they are much larger than the scale factors.

SRAM inside PEs in an all-to-all manner. However, a major drawback of this design is the large area overhead as it needs to provide local SRAM for all the three data types: weights, IFmaps, and partial sum. As mentioned in [56], assuming an equal number of PEs, Eyeriss-v2 is more than twice as large as SysAr.

Conventional accelerators hide the execution time of NORM, ACT, and POOL by executing them within VU in a pipelined manner when they follow CONV. However, as opposed to these memory–intensive operations, such a pipelined execution is hardly applicable to SE–Scale that follows CONV because of the data dependency between SE–Scale and CONV (see Figure 2.3). SE– Scale requires a complete IFmap from the previous CONV to produce one single OFmap element.

Figure 2.9 shows the data movement patterns inside SysAr when performing SE–Scale. Depending on the size of Fmaps and UB, data should be read from

either UB (yellow arrow) or DRAM (red arrow). We only depict the movement of Fmaps because Fmaps are much larger than the scale factors, whose number is the same as the number of channels.

When Fmaps fits in UB, SE–Scale performs multiplication after reading the Fmaps stored in UB. Because the datapath from UB to VU is uni–directional, Fmaps must go through MU to reach VU, and MU does not operate in the meantime, leading to severe underutilization of the MACs. Also, although SE–Scale requires much smaller computation than that of PW–CONV (150~250× in [87]), the execution time of SE–Scale is high because VU has  $N \times$  fewer MACs than MU (see Figure 1.1). Even if MU handles SE–Scale to utilize its MACs, it takes the same time as in VU because the bandwidth of UB is limited to  $\mathcal{O}(N)$ . When Fmaps do not fit into UB, off–chip memory bandwidth becomes a performance bottleneck because of the extra access to more bandwidth–hungry DRAM.

# 2.4.2 Opportunity for load balancing in BERT training

The load balancing technique minimizes resource under-utilization by processing multiple DNN models in parallel within an accelerator. When the accelerator executes all PE tiles synchronously, compute-intensive operations achieve a high MU utilization rate, but utilize little DRAM bandwidth. In contrast, memory-intensive operations only utilize the VU and DRAM bandwidth. However, the load balancing technique obtains a benefit in terms of the execution time by properly distributing MU, VU, and DRAM bandwidth resources.

Figure 2.10 explains the impact of the load balancing technique with an example in which the memory bandwidth demands from two clusters vary

Figure 2.10: Example of a memory traffic distribution over time [51]: (a) concurrent execution with an unlimited DRAM bandwidth, (b) concurrent execution with a limited DRAM bandwidth and (c) partitioning of PE tiles into two clusters (C0 and C1). The blue layers (L0, L2, L4) are GEMM operations, and the yellow layers (L1, L3, L5) are memory-intensive operations.

depending on the layers. When the DRAM bandwidth is infinite (see Figure 2.10(a)), the execution time for GEMM and memory–intensive operations is determined by the MU and VU performance capabilities, respectively. For real– istic systems with a limited bandwidth, however, memory–intensive operations are associated with a DRAM bandwidth bottleneck and there are additional de– lays at L1, L3, and L5 (see green squares in Figure 2.10(b)). When the accelera– tor is partitioned into two clusters and processes each cluster independently, the GEMM and memory–intensive operations are performed simultaneously (see Figure 2.10(c)). Thus, the load balancing technique can distribute the memory bandwidth demand, which improves the execution time.

However, the load balancing technique cannot be used during conventional training. To apply the load balancing technique, each task must be able to operate independently. During the training processes, only a single DNN model

(c) Training with gradient accumulation and sequence binning

Figure 2.11: Execution time of various training methods using the NVIDIA Nsight system profiler [66]: (a) conventional training, (b) training with gradient accumulation, and (c) training with gradient accumulation and sequence binning. We set the maximum SL size to 128 and used four gradient accumulation steps. The Nsight system uses *multi\_tensor\_apply\_kernel* as the weight update kernel.

is utilized in a single DNN accelerator given the large batch size. Also, because training should update the weight parameters every time for each mini-batch, multiple mini-batches cannot be processed in parallel.

With gradient accumulation, the latest training technique becomes feasible for the application of load balancing techniques. Figure 2.11 shows the results of the NVIDIA Nsight systems profiler [66] with various training methods. Conventional training performs weight updates at every iteration as shown in Figure 2.11(a). To obtain the weight parameters for iteration 1, training for iteration 0 must be finished. Thus, there is a dependency between iterations. Gradient accumulation eliminates the dependency between iterations within a gradient accumulation step. In Figure 2.11(b), iterations 0, 1, 2, and 3 use the same weight parameters, and four iterations can be processed in parallel.

Sequence binning varies the size of the SLs. Figure 2.11(c) depicts training with gradient accumulation and sequence binning. Iterations 0, 1, and 3 are performed with 64 SL because the padded token occupies half of the input. In contrast, iteration 2 consists of full text and is performed with 128 SL.

The load balancing technique can improve the performance when operations with opposite characteristics are performed concurrently in clusters. Therefore, sequence binning helps to obtain an additional performance improvement of our idea.

# Chapter 3

# DNN accelerator tailored for accelerating memoryintensive operations

We propose DNN accelerators tailored for accelerating memory–intensive operations based on a systolic array (see Figure 3.1(a)). Although the systolic array is the most known structure for accelerating DNN, this structure does not perfectly cover the trend of the latest DNN. We analyze the computational characteristics of inference and training of the latest DNN in detail. Through the analysis, we confirm that it is difficult to design an integrated structure for optimizing both inference and training because each process has different com– putational characteristics. Therefore, we design separate architectures for each process as shown in Figure 3.1(b) and (c).

A DNN accelerator that is specialized for inference fully utilizes the pipelined manner between layers to reduce off-chip memory access. The inference only performs a forward pass using a pre-trained model. During inference, when one layer is executed, the intermediate result of one layer is used to process the next layer. The intermediate result is used only once as the input of the next layer, and it is not required after processing the next layer. In most cases, the intermediate result is not stored in on-chip memory because this size is large.

Figure 3.1: (a) Baseline systolic array architecture. (b) A pipelined architecture tailored for accelerating inference. (c) A tiled architecture tailored for accelerating training.

If a specific layer is a memory-intensive operation, off-chip memory access causes a bandwidth bottleneck and degrades the performance. Thus, reusing the intermediate result as much as possible on-chip has a major impact on the performance of the accelerator. To maximally utilize the inter-layer pipeline execution, it is necessary to establish which unit processes the proper operations considering computational characteristics. By reflecting the trend of the latest CNN, we assign operations to units in a slightly different position from that of the existing accelerators.

A DNN accelerator that is specialized for training utilizes computational parallelism to process the massive number of operations. Training performs both forward and backward passes to learn the model. In the forward pass, the intermediate result of one layer enters the input of the next layer and is used to obtain the weight gradient in the backward pass. Because the backward pass is performed after all of the layers of the forward pass are completed, the intermediate result cannot be stored in the on-chip memory. Therefore, the intermediate result is stored in off-chip DRAM. To minimize off-chip memory access, we propose a tiled architecture with multiple levels of memory because on-chip cache help to reuse input and weight data. Unlike inference, training lacks optimization methods to reduce off-chip access. To overcome these, we further propose a load balancing technique that optimizes memory-intensive operation when performing training using a tiled architecture. The details of the structure and operation of the two accelerators are covered in Chapters 4 and 5.

# Chapter 4

# MVP: A CNN accelerator with <u>Matrix</u>, <u>Vector</u>, and <u>Processing-near-memory units</u>

# 4.1 Contribution

#### 4.1.1 MVP organization

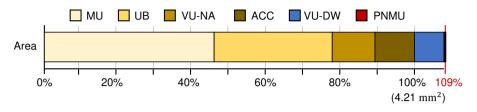

We propose a novel CNN accelerator architecture called MVP, which includes an MU, a VU for NORM/ACT (VU–NA) and for DW–CONV (VU–DW), and a processing–near–memory unit (PNMU) as shown in Figure 4.1(a). As opposed to the baseline SysAr architecture that suffers from poor performance in memory–intensive layers such as DW–CONV and SE, MVP is pragmatically designed to efficiently process both compute–intensive and memory–intensive CNN layers and functions with a minimal area overhead.

VU–DW takes the OFmaps from MU through VU–NA (processing PW– CONV, NORM, and ACT) and performs DW–CONV in a pipelined man– ner (see Figure 4.1(b)). In case DW–CONV does not follow PW–CONV, the OFmaps bypass VU–DW and head to UB directly. Based on the key observa– tion that a SysAr lane only processes an output channel, we place a depth–wise

Figure 4.1: (a) MVP architecture (the red and blue parts represent the units added to the baseline SysAr), (b) VU–DW, and (c) PNMU.

processing element (DWPE) per SysAr lane. Each DWPE consists of depth-wise input/weight buffer (DWIB/DWWB), *k* depth-wise multipliers (DWMULs), an adder tree for partial reduction, and registers for accumulation. Each DWMUL takes the operands from DWIB and DWWB, multiplies them, and sends the output to the adder tree. DWIB is a buffer for IFmaps in DW-CONV; it consists of *k* DWIB slices, each being mapped to a DWMUL. Each DWIB slice is a register file with a word size of 1-byte, allowing the DWMULs to access a row of DWIB SRAM cells simultaneously. DWWB is a buffer for weights in DW-CONV. Because the weights are reused with repeating but shuffled patterns to be aligned with the IFmap values to be multiplied at DWMUL, DWWB consists of a barrel shifter and a small register file. VU and UB are connected bidirectionally. VU-DW also covers the POOL (pooling) function because recent CNN models have relatively simple POOL operations such as global average pooling,

PNMU (Figure 4.1(c)) is a preprocessing unit which is placed near on-chip unified memory to execute simple element-wise operations conducted prior to CONV. These operations are pipelined with the subsequent CONV, thereby hiding the execution time and saving memory accesses. PNMU includes  $H_{MU}$ PNM elements (PNMEs), each placed between a row of UB and MU in an aligned manner. Each PNME consists of a DEMUX, a MAC, a comparator for ReLU, a MUX, and tiny registers holding scale factors used in scaling operations such as SE–Scale and NORM. DEMUX selects either a scale factor or an IFmap element. PNME only supports ReLU because it is a popular ACT function that is also used for MBConv [39, 44], and the logics for other ACT types take up a large area. MUX decides whether or not to use preprocessing.

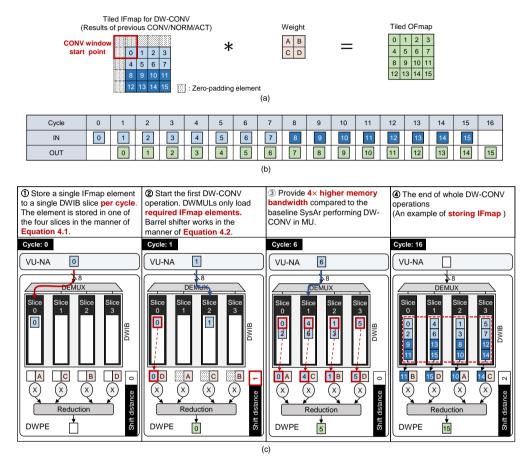

#### 4.1.2 How depth-wise processing element (DWPE) operates

We describe how DWPE operates by showing an example of a DW-CONV layer with stride 1 and with zero-padding: the sizes of inputs are  $4\times4$  for IFmaps and  $2\times2$  for weights (see Figure 4.2(a)). Figure 4.2(b) presents the data movement in DWPE I/O at each cycle, while Figure 4.2(c) shows how DWPE operates internally in detail.

(1) VU-NA receives the OFmap elements of PW-CONV from MU and ACC, performs BN and ACT, and sends the resulting Fmap to DWPE per cycle at each lane. DWPE takes the IFmap element and stores it to DWIB. At cycle 0, DWIB stores the IFmap element in one of the four DWIB slices. The position of DWIB slice where an IFmap element is stored is determined by 4.1.

Position of DWIB slice =

$$(row_{IFmap} + column_{IFmap} \times KH) \% DWMUL$$

$$(4.1)$$

In the equation, the  $row_{IFmap}$  and  $column_{IFmap}$  are the positions of a single IFmap element on a 2-dimensional IFmap. For example, the  $row_{IFmap}$  and  $column_{IFmap}$  of an IFmap element numbered 0 are both 0.

② At cycle 1, DWPE starts the first DW-CONV operation. The first CONV window requires a single IFmap element numbered 0 and three zero-padding elements. DWMULs only load an IFmap element numbered 0 from a DWIB slice for operation. DWMULs which need zero-padding elements do not work. Because weights are recycled for every OFmap elements in an OFmap, the barrel shifter rearranges the weights by a shift distance according to 4.2. If the zero-padding size is odd, a math symbol in the equation is a plus, and vice versa,

Figure 4.2: An example of how DWPE operates when the number of DWMULs and DWIB slices is 4. Because the DWPEs perform the same operations on independent Fmaps, we describe an example for one DWPE. (a) An example of DW-CONV where IH and IW are the same as the tile size used in the previous PW-CONV (4×4 in the example). (b) DWPE data in/out movement status at each cycle. The result of PW-CONV, NORM, followed by ACT, is transferred to DWPE every cycle, assuming that IC of the previous PW-CONV is smaller than  $H_{MU}$  (weights are not shown for convenience of explanation). (c) DWPE operations in specific clock cycles. We assume that read/write operations of DWIB spend one cycle.

the math symbol is a minus. The shift distance numbered 0 means that the weight elements are allocated to the DWMULs in the same way as storing IFmap elements to the DWIB slices as shown in cycle 0. The equation of shift distance is similar to 4.1; however, there are slight differences in considering the OFmap element, ST, and the zero-padding size.

Shift distance =

$$[ST(row_{OFmap} + column_{OFmap} \times KH) \pm padding] \% DWMUL$$

(4.2)

③ From cycles 1 to 16, DWPE performs a convolution operation for every cycle. Compared to the baseline SysAr performing DW-CONV in MU, DWPE provides up to 4× higher memory bandwidth, owing to the 4 DWIB slices operating in parallel. To fully utilize all the DWIB slices at every cycle, each IFmap element in a CONV window should be placed in a proper DWIB slice. Cycle 6 is an example of fully utilizing 4× bandwidth. The CONV window requires the IFmap elements numbered 0, 4, 1, and 5: the four elements are distributed, in column-major order, into the first row of the four DWIB slices. DWPE loads the IFmap elements 0, 4, 1, and 5 from each DWIB slice, multiplies them with the corresponding weights, sums up the output to compute OFmap element 5. ④ This data access pattern is repeated until DW-CONV finishes at cycle 16.

Even when a stride is larger than 1, the DEMUX for storing IFmap in the DWIB slice works the same as the stride 1. The pattern of loading IFmaps into DWMUL needs no change. For example, when the stride is 2, IFmaps are loaded in the same way as 6, 8, 14, and 16 cycles of Figure 4.2(b). The barrel shifter does not change the position of weights when the window moves in the row direction; it only shifts weights by 2 when the window moves in the column

Figure 4.3: Illustration of how PNMU operates. PNMU reads Fmaps from DRAM and performs SE-Scale and the subsequent CONV concurrently. (b) Tile traversal of the next CONV.

direction. Thanks to such a straightforward access pattern, DWPE fully exploits the convolutional reuse on an IFmap, yet being flexible enough to support the various sizes of kernels and the number of DWMULs.

## 4.1.3 How processing-near-memory unit (PNMU) operates

PNMU processes element-wise operations that commonly precede a CONV layer, such as NORM, ACT, and SE-Scale. Figure 4.3 illustrates how PNMU processes SE-Scale. Here we describe an example of fetching IFmaps of SE-Scale from DRAM as it accompanies fetching from UB. First, scale factors required for SE-Scale are computed by VU, stored at UB, fetched from UB, and stored in the registers inside PNME. Each of  $T_{IC}$  PNME holds its own scale factor for a single input channel (see Figure 4.3(a)). Then, PNMU multiplies the scale factors with a tile of Fmaps sized  $T_{IW} \times T_{IH} \times T_{IC}$  in an element-wise manner. The output of SE-Scale is directly fed into MU for the subsequent CONV.

After one Fmap tile is complete, one needs to determine which direction to traverse the Fmap tiles because it determines whether the scale factors are reused or not. As explained in Section 2.2.2, SysAr sends a complete OFmap element from ACC to VU. For that, SysAr traverses in IC-direction first (see Figure 4.3(b)); then, the tiles are traversed in IW- and finally in IH-direction.

PNMU overlaps most of the execution time for SE–Scale with the subsequent CONV and saves memory access for SE–Scale, compared to the baseline SysAr. This design includes inevitable overheads, albeit minimal. Because any two IFmap tiles processed in a row have completely different input channels, the scale factors in the PNME registers should be updated for every IFmap tile. When the datapath between UB and PNME is busy updating the scale factors, it cannot feed the Fmap for SE–Scale and the subsequent CONV. However, once a scale factor is updated, it is reused by  $T_{IW} \times T_{IH}$ , amortizing the time overhead for the scale factor update to  $\frac{1}{(T_{IW} \times T_{IH})}$ . For the CNN models tak– ing input images with a resolution of 224×224, the smallest  $T_{IW} \times T_{IH}$  is 49; limiting the time overhead to 2% (more details in Section 4.2.2).

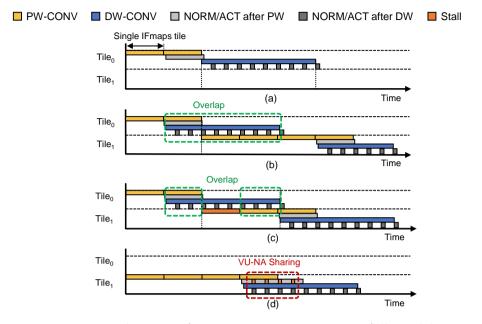

# 4.1.4 Overlapping the operation of DW-CONV with PW-CONV

VU–DW and MU can concurrently execute both PW–CONV and DW–CONV in a pipelined manner, resulting in additional speedup with the overlapped ex– ecution. Figure 4.4 shows timing diagrams of PW–CONV and the following DW–CONV with and without overlapping. Pipelining clearly reduces execution time. The degree of execution time saving depends on the time to produce

Figure 4.4: Timing diagrams for processing PW-CONV followed by DW-CONV. X-axis represents time and y-axis represents operation sequences about multiple OFmap tiles. MU and VU process PW-CONV and DW-CONV (a) without pipeline, (b) with pipeline ( $Cycle_{PW} > Cycle_{DW}$ ), (c) with pipeline ( $Cycle_{PW} < Cycle_{DW}$ ), and (d) with sharing VU-NA.

an OFmap tile during PW-CONV and DW-CONV, defined as  $\frac{T_{IW} \times T_{IH} \times IC}{H_{MU}}$  for PW-CONV and  $\frac{T_{OW} \times T_{OH} \times KH \times KW}{DWMUL}$  for DW-CONV. Figure 4.4(b) shows the case when the processing time for an OFmap tile of PW-CONV is larger than that of DW-CONV. Then, the execution time on DW-CONV fully over-laps with PW-CONV. If the processing time for an OFmap tile in DW-CONV is larger than that in PW-CONV (Figure 4.4(c)), there is a stall (shown as an orange bar) in MU, leading to less saving albeit still beneficial.

Meanwhile, the throughput requirement of VU–NA increases twice due to the concurrent processing. It is simple to duplicate VU–NA for DW–CONV and PW–CONV, but it requires 11% additional area (see Section 4.2.1). To avoid this, we share one VU–NA for both DW–CONV and PW–CONV through multiplexing (see Figure 4.4(d)). We present the performance overhead due to sharing VU–NA in Section 4.2.2.

#### 4.1.5 Considerations for designing DWIB

Because the DWIB size affects the execution time and energy of both DW– CONV and PW–CONV and the area of MVP, it must be carefully designed. PW–CONV can suffer from slowdown and more energy consumption due to the additional DRAM memory access if DWIB size is too small. PW–CONV might experience more frequent DRAM accesses due to weight update when concurrently executing PW–CONV and DW–CONV due to a smaller PW– CONV tile size compared to the non–overlapped case [60].