#### Ph.D. Dissertation of Materials Science and Engineering

## Performance optimization of the TiO<sub>2</sub>based electronic bipolar resistive switching memristor and its neuromorphic computing application

August 2023

Graduate School of Engineering Seoul National University Department of Materials Science and Engineering

Xiang Yuan Li

## Performance optimization of the TiO<sub>2</sub>based electronic bipolar resistive switching memristor and its neuromorphic computing application

Adviser: Prof. Cheol Seong Hwang

Submitting a Ph.D. Dissertation of Materials Science and Engineering

August 2023

#### Graduate School of Engineering Seoul National University Department of Materials Science and Engineering

Xiang Yuan Li

Confirming the Ph.D. Dissertation written by Xiang Yuan Li August 2023

| Chair      | Sang Bum Kim      | _(Seal) |

|------------|-------------------|---------|

| Vice Chair | Cheol Seong Hwang | _(Seal) |

| Examiner _ | Min Hyuk Park     | _(Seal) |

| Examiner _ | Kyung Min Kim     | _(Seal) |

| Examiner   | Hae Jin Kim       | _(Seal) |

### Abstract

In recent decades, there has been significant research activity in resistance random access memory (RRAM) for both one transistorone resistor and crossbar array configurations. Conventional RRAM devices based on conductive filaments (CFs) suffer from issues such as hard breakdown during electroforming, non-uniformity, and high power consumption. In contrast, electronic bipolar resistance switching (e-BRS) devices, which rely on the trapping and detrapping of carriers, offer a more favorable alternative. The gradual current switching in e-BRS reduces the likelihood of electrical breakdown, and the absence of an electroforming step is an advantage. Moreover, e-BRS devices exhibit area scalability, making them suitable for integration in crossbar arrays, resulting in reduced power consumption. These devices have also shown potential in flexible memory, security applications, and artificial synapse implementations. However, the endurance and retention performance of many reported e-BRS devices have been unsatisfactory. These issues necessitate the development of suitable methods to prevent oxygen loss and improve device performance.

The Al/TiO<sub>2</sub>/Al resistance random access memory (RRAM) showed an area-type electronic bipolar resistive switching (e-BRS)

i

mechanism, which was mediated by the trapping and detrapping of the carriers at the trap centers. The area-type e-BRS device had area-scalable characteristics and excellent uniformity, which are beneficial for large-scale integrated applications. However, the unsatisfactory endurance and retention performance needed to be improved. In this work, a 1-2nm-thick ZrO<sub>2</sub> thin layer was deposited by the thermal atomic layer deposition on the 25nm-thick sputterdeposited TiO<sub>2</sub> layer to form an Al/ZrO<sub>2</sub>/TiO<sub>2</sub>/Al memory cell. The thin ZrO<sub>2</sub> layer effectively prevented the active Al top electrode from absorbing oxygen from the TiO<sub>2</sub> resistive switching (RS) layer without significantly affecting the asymmetric energy barrier structure of the device. The suppression of oxygen loss from the  $TiO_2$  RS layer retained the desired trap density of the RS layer even after the extended switching cycle operation. This suppression effect significantly improved the RS performances, such as endurance, uniformity, and retention. The switching endurance was enhanced over two orders of magnitudes (from  $<10^3$  to  $>10^5$ ). The ZrO<sub>2</sub> layer also increased the overall resistance values of the memory cell, making it more suitable than the Al/TiO<sub>2</sub>/Al structure for highdensity applications.

Spiking neural networks (SNN) have attracted considerable interest as a more energy-efficient alternative to deep learning

ii

methodologies. The crucial requirement for artificial synapses in neuromorphic systems lies in their capacity to demonstrate synaptic plasticity, enabling the modulation of synaptic strength through electrical stimulation. Nonvolatile memory devices, such as resistive random access memory, hold promise for emulating artificial synapse functions. Despite the simplicity and flexibility offered by RRAM, many devices suffer from undesired properties due to their reliance on conductive filaments-controlled mechanisms, which exhibit abrupt and stochastic behavior. In contrast, non-filamentary RRAM devices present superior attributes including enhanced uniformity, scalability. and reduced power consumption. However, research on nonfilamentary memristors for synaptic applications remains limited. Hence, there is significant potential in exploring and optimizing nonfilamentary RRAM as a viable solution for artificial synapses in future studies.

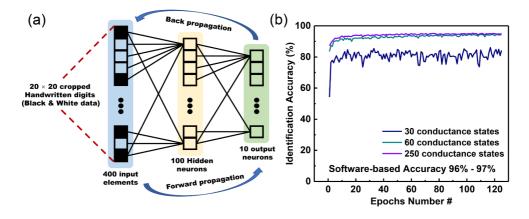

This study presented an Al/ZrO<sub>2</sub>/TiO<sub>2</sub>/Al (AZTA) memristor based on a non-filamentary mechanism for simulating artificial synapses in spiking neural networks (SNN) for neuromorphic computing. This device feasibly implemented short-term plasticity, long-term plasticity, paired-pulse facilitation, and spike-timing-dependent plasticity through precise modulation of the shapes of pre- and postsynaptic spikes. Additionally, the AZTA device demonstrated high linear and symmetrical potentiation and depression under identical pulse operation conditions, facilitating multivalued conductance without auxiliary circuits. The trapping and de-trapping of electrons control the synaptic weight at different depth energy levels provided by oxygen vacancy traps. Also, the AZTA memristor showed promising potential for low power consumption and high operating speed due to its area-dependent behavior based on the electronic bipolar resistance switching mechanism. The simulation of the multilayer perceptron with 400 input, 100 hidden, and 10 output neurons using the AZTA synapses can reach 94.9% accuracy of the MNIST dataset.

**Keywords:** TiO<sub>2</sub>-based resistance random access memory, electronic bipolar resistive switching mechanism, ZrO<sub>2</sub> insertion layer, areadependent behavior, artificial synapses, non-linearity, spiking neural networks, neuromorphic computing

Student Number: 2018-39552

## Table of Contents

| Abstracti                                                                       |

|---------------------------------------------------------------------------------|

| Table of Contents v                                                             |

| List of Tables viii                                                             |

| List of Figuresix                                                               |

| Chapter 1. Introduction 1                                                       |

| 1.1. Resistance random access memory (RRAM) 1                                   |

| 1.2. Two resistance switching mechanisms 4                                      |

| 1.3. Artificial synapses based on nonvolatile memristor for the neural networks |

| 1.4. Nonlinearity of the artificial synapses based on RRAM devices              |

| 1.5. Research scope and objective1 6                                            |

| 1.6. Bibliography                                                               |

| Chapter 2. Performance improvement of Al/TiO <sub>2</sub> /Al electronic        |

| bipolar resistive switching memory via inserting an ultra-thin                  |

| ZrO <sub>2</sub> layer at the top interface 2 8                                 |

| 2.1. Introduction                                                                                                                       |   |

|-----------------------------------------------------------------------------------------------------------------------------------------|---|

| 2.2. Experimental                                                                                                                       |   |

| 2.3. Results and Discussions                                                                                                            |   |

| 2.3.1. Optimization of the ZrO <sub>2</sub> insertion layer thickness                                                                   | 5 |

| 2.3.2. The resistance switching performance comparison                                                                                  | ) |

| 2.3.3. The characteristics test and analysis                                                                                            | 3 |

| 2.3.4. Fitting and analysis of degradation mechanism                                                                                    | ) |

| 2.4. Summary                                                                                                                            |   |

|                                                                                                                                         |   |

| 2.5. Bibliography                                                                                                                       |   |

|                                                                                                                                         | 1 |

| Chapter 3. Artificial Synapse Based on an Al/ZrO <sub>2</sub> /TiO <sub>2</sub> /A                                                      | 1 |

| Chapter 3. Artificial Synapse Based on an Al/ZrO <sub>2</sub> /TiO <sub>2</sub> /A                                                      | 1 |

| Chapter 3. Artificial Synapse Based on an Al/ZrO <sub>2</sub> /TiO <sub>2</sub> /A<br>Electronic Bipolar Resistance Switching Memristor | 1 |

| Chapter 3. Artificial Synapse Based on an Al/ZrO <sub>2</sub> /TiO <sub>2</sub> /A<br>Electronic Bipolar Resistance Switching Memristor | 1 |

| Chapter 3. Artificial Synapse Based on an Al/ZrO <sub>2</sub> /TiO <sub>2</sub> /A<br>Electronic Bipolar Resistance Switching Memristor |   |

| Chapter 3. Artificial Synapse Based on an Al/ZrO <sub>2</sub> /TiO <sub>2</sub> /A<br>Electronic Bipolar Resistance Switching Memristor | 5 |

| Chapter 3. Artificial Synapse Based on an Al/ZrO <sub>2</sub> /TiO <sub>2</sub> /A<br>Electronic Bipolar Resistance Switching Memristor | 5 |

| 3.3.4. Neuromorphic computing application |   | 1   | 1   | 0 |

|-------------------------------------------|---|-----|-----|---|

| 3.4. Summary                              | 1 | 1   | . 9 | ) |

| 3.5. Bibliography                         | 1 | 2   | 2 1 |   |

| Chapter 4. Conclusion                     |   | 3   | 31  | - |

| Abstract in Korean                        | 1 | . 3 | 36  | 5 |

## List of Tables

**Table 3.1.** Online learning accuracy results and detailed simulationparameters in NeuroSim software.

### List of Figures

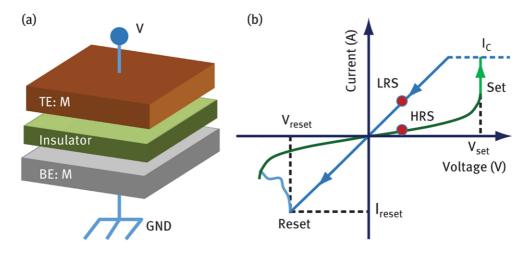

**Figure 1.1.** (a) Schematic diagram showing typical metal-insulatormetal (MIM) structure of ReRAM with electrical biasing. (b) Schematic illustration of bipolar switching characteristics in ReRAM. For the bipolar switching, "set" and "reset" processes occur at different polarity.

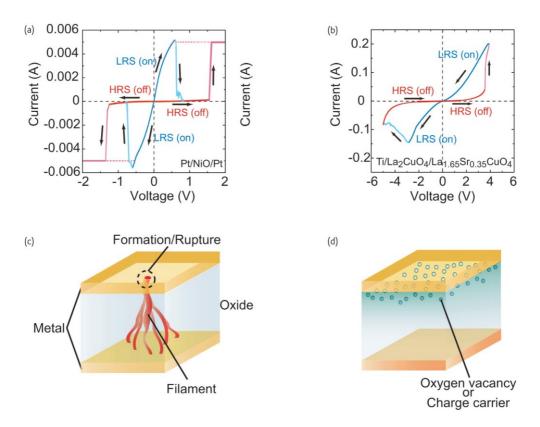

**Figure 1.2.** I–V curves for (a) unipolar (nonpolar) switching in a Pt/NiO/Pt cell and (b) bipolar switching in a Ti/La<sub>2</sub>CuO4/La<sub>1.65</sub>Sr<sub>0.35</sub> CuO<sub>4</sub> cell. In unipolar switching, the switching direction depends on the amplitude of the applied voltage. Bipolar switching shows directional resistance switching according to the polarity of the applied voltage. Proposed models for resistive switching can be classified according to either (c) a filamentary conducting path, or (d) an interface-type conducting path. (Part (a) courtesy of I. H. Inoue, AIST.)

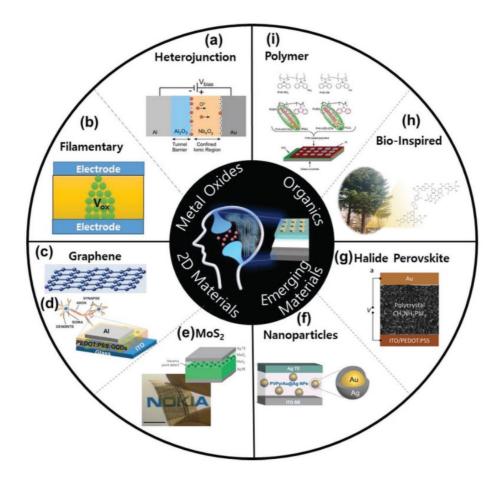

**Figure. 1.3.** Recent memristive materials applied for artificial synapses: metal oxides, organic materials, 2D materials, and emerging materials.

ix

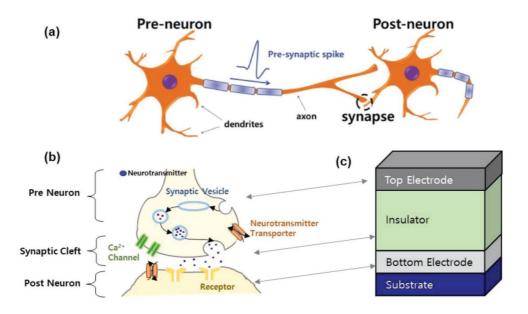

**Figure. 1.4.** Comparison between biological synapses and artificial synapses. a) Schematic diagram of a preneuron, postneuron, and synapse. Reproduced with permission. b) Schematic diagram of neurotransmission process. c) A general structure of two terminal memristors-based artificial synapses.

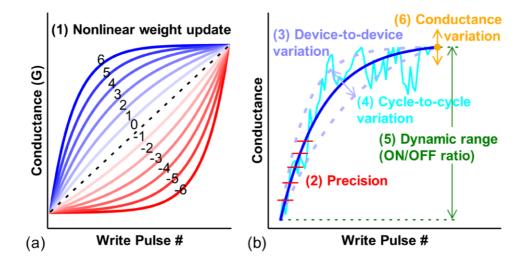

**Figure. 1.5.** Schematic illustration of non-ideal synaptic device properties modeled in the MLP simulator, including (1) nonlinear weight update (a), (2) weight precision, (3) device-to-device weight update variation, (4) cycle-to-cycle weight update variation, (5) dynamic range (conductance ON/OFF ratio) and (6) conductance variation (b).

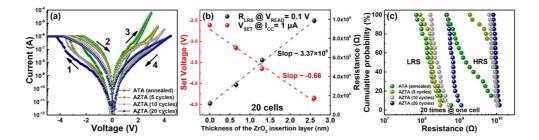

Figure 2.1. The resistance switching characteristics of ATA (annealed) sample and AZTA samples with 5, 10, and 20 deposition cycles of the  $ZrO_2$  film. (a) Typical e-BRS I-V curves with an I<sub>cc</sub> of 1  $\mu$ A. (b) RLRS at the read voltage of 0.1 V and VSET at the I<sub>cc</sub> of 1  $\mu$ A from 20 memory cells. (c) The cumulative probability graphs of LRS and HRS from the 20 I–V sweeps in a single memory cell.

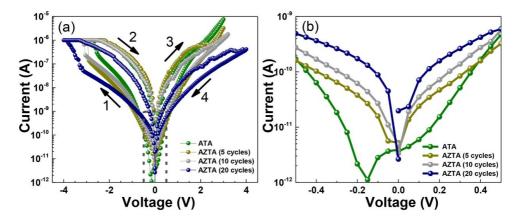

**Figure 2.2.** (a) Typical e-BRS I-V curves of ATA sample (without annealing), AZTA sample (5 cycles, 40 minutes), AZTA sample (10

cycles, 60 minutes), and AZTA sample (20 cycles, 80 minutes) fabricated by the thermal ALD with the different deposition time. (b) The I-V curves with a smaller range clearly show the degradation of HRS.

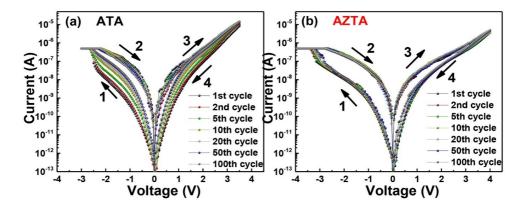

**Figure 2.3.** Typical e-BRS I-V curves of (a) ATA and (b) AZTA samples at the 1st, 2nd, 5th, 10th, 20th, 50th, and 100th cycles with an Icc of 0.5 µA. The arrows and numbers indicate the switching sequences.

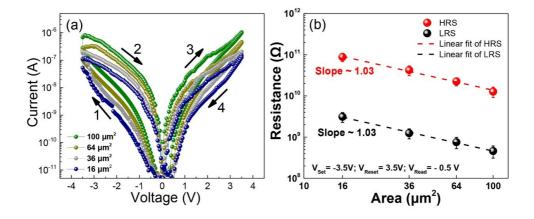

Figure 2.4. The I–V curves of the AZTA sample with the different electrode sizes without the  $I_{cc}$ . (b) The electrode area-dependence of LRS and HRS for AZTA sample. Each data point was achieved from 20 cells.

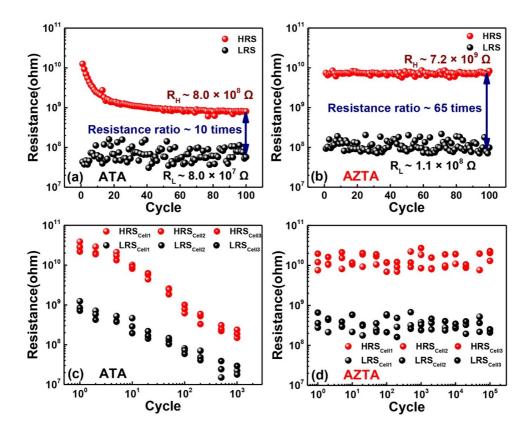

**Figure 2.5.** The endurance test results from the DC I-V sweeps of (a) ATA and (b) AZTA samples, with an Icc of 0.5  $\mu$ A. The AC endurance test results of (c) ATA and (d) AZTA samples from the pulse operation mode. The set and reset pulse conditions of the ATA sample (-2.5 V/20 ms and 2.7 V/20 ms), and AZTA sample (-4 V/20 ms and 5 V/20 ms) were tuned to achieve the best test results. The read voltage was 0.5 V.

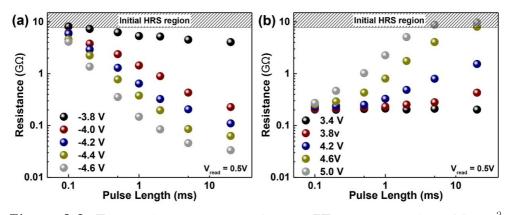

Figure 2.6. The resistance state of the AZTA sample with 100  $\mu$ m<sup>2</sup> area after applying different (a) set and (b) reset pulse excitations. The initial HRS is ~ 8 G $\Omega$  for the set process, and the initial LRS is ~ 0.2 G $\Omega$  for the reset process, obtained after applying a -4V/20ms set pulse. The read voltage is 0.5V.

**Figure 2.7.** The resistance ratio variation of the AZTA samples with different electrode areas after applying set pulses with different pulse lengths when the set pulse amplitude is fixed to -4V.

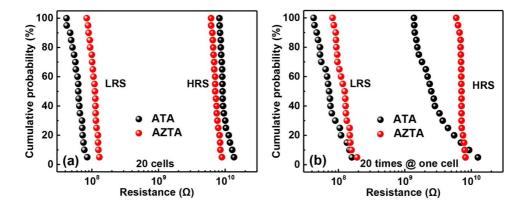

**Figure 2.8.** The cumulative probability graphs of LRS and HRS for ATA and AZTA samples, respectively. (a) The 20 I-V sweeps from 20 memory cells, and (b) the 20 I-V sweeps from a single memory cell. The Icc is 500nA, and the read voltage is 0.5 V.

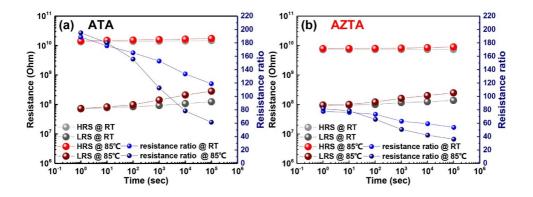

**Figure 2.9.** The retention characteristics of HRS, LRS, and resistance ratio were measured at room temperature (grey symbols) and 85°C (color symbols) of (a) ATA and (b) AZTA samples, respectively. The read voltage is 0.5 V.

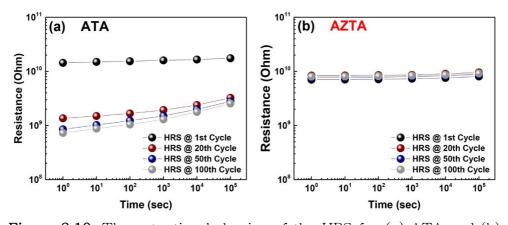

Figure 2.10. The retention behavior of the HRS for (a) ATA and (b) AZTA samples after different cycling numbers at the temperature of

85℃.

**Figure 2.11.** The XPS spectra of (a) Ti 2p and (b) O 1s of ATA and AZTA samples, respectively. (c) Zr 3d core level XPS spectrum of AZTA sample.

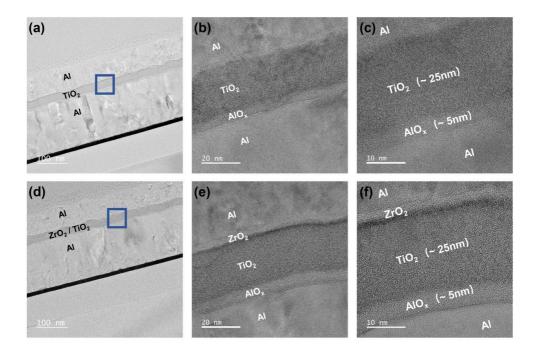

**Figure 2.12.** (a) – (c) The TEM images with the different magnifications of the ATA sample. (d) – (f) The TEM with the different magnifications of the AZTA sample. HRTEM images correspond to the blue square region in low magnification images.

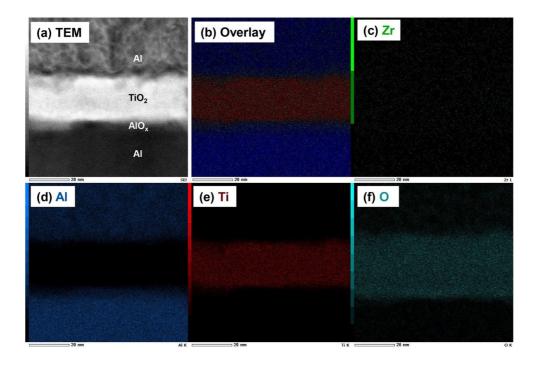

**Figure 2.13.** STEM-EDS mapping analysis of ATA sample: (a) TEM image of the corresponding area; (b) Overlay of Zr-Al-Ti-O; (c) Zr-L; (d) Al-K; (e) Ti-K; (f) O-K.

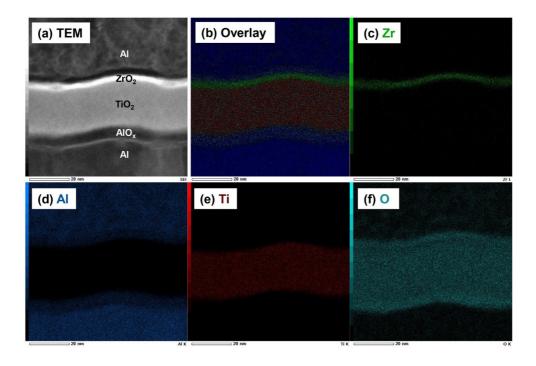

**Figure 2.14.** STEM-EDS mapping analysis of AZTA sample: (a) TEM image of the corresponding area; (b) Overlay of Zr-Al-Ti-O; (c) Zr-L; (d) Al-K; (e) Ti-K; (f) O-K.

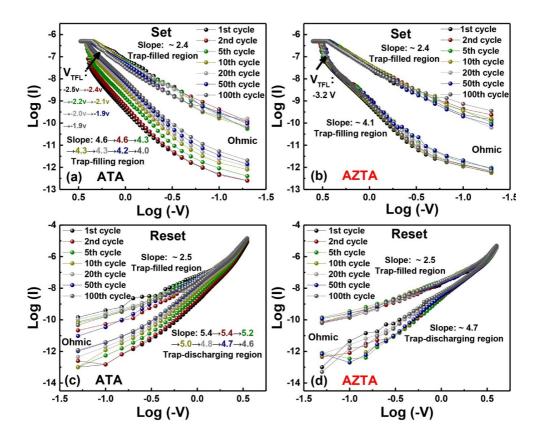

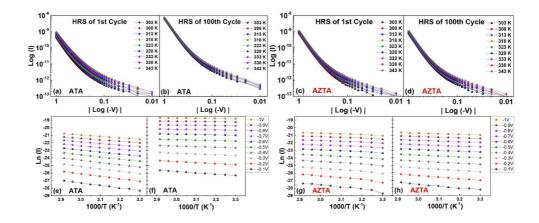

**Figure 2.15.** Double-log scales and linear fitting of SCLC mechanism for different repetition cycles of (a) set process and (b) reset process for the ATA sample and of (c) set process and reset process for the AZTA samples, respectively. **Figure 2.16.** (a) - (d) show the temperature dependence characteristics of HRS after the 1st and 100th cycles were measured at the temperature range of 303 K to 343 K of the ATA and AZTA samples, respectively. The Arrhenius-type plots of the (a) - (d) data are shown in (e) - (h) for calculating the activation energy (Ea).

Figure 2.17. The  $E_a$  at each voltage for HRS of (a) ATA and (b) AZTA samples, respectively, were calculated from the slopes of the best-linear fitting of figure 2.16 (e) - (h).

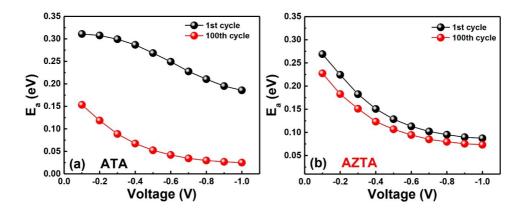

**Figure 2.18.** The schematic band diagram of ATA and AZTA samples at the initial state (upper panels), set process (middle panels), and reset process (middle panels) after 100 switching cycles. The color code of the subfigures is Al electrode, blue square; AlO<sub>x</sub> layer, gray square; ZrO<sub>2</sub> layer, dark blue square; electrons, gray spheres; traps (oxygen vacancies), hollow red spheres; traps filled with electrons (charged oxygen vacancies), hollow red spheres filled with gray; oxygen atoms, violet spheres; direction of current flow, orange arrow; trapping and detrapping of the electrons, red arrow; and direction of oxygen diffusion, violet arrow.

xiv

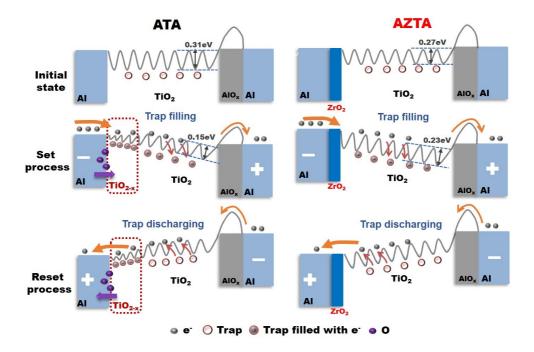

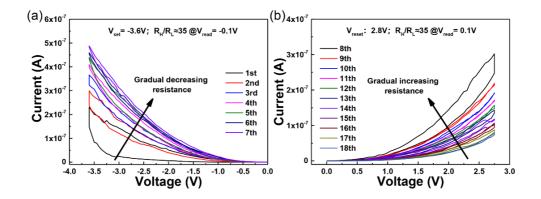

Figure 3.1. (a) Typical I-V curves with an  $I_{cc}$  of 1 µA. (b) The set process with gradually decreasing sweep voltage from -3.6 V to -4.1 V. (c) The reset process with gradually increasing sweep voltage from 4.0 V to 4.5 V. The I-V curves in the semi-log scale within the low sweep voltage range are shown in the inset figures. (d) The set and (e) reset process in pulse operation mode with an input voltage of -4 V and 4 V, respectively. The interval and pulse length are both 1 ms.

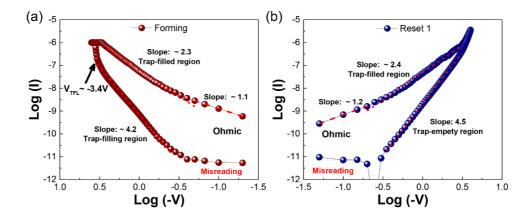

**Figure 3.2.** The double log fitting of the I–V curves of (a) set process and (b) reset process for AZTA memristor, showing the typical SCLC mechanism. The threshold voltage is approximately -3.4V. The poor linear fitting in the HRS region is due to the current level being close to the detection limit of the equipment.

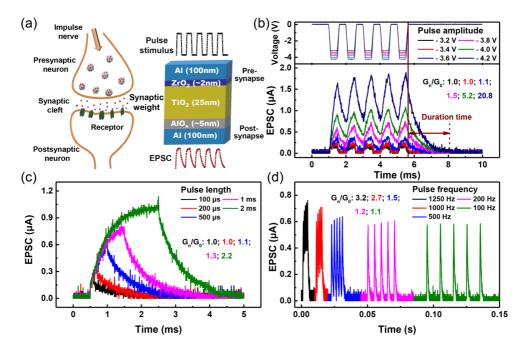

**Figure 3.3**. (a) Schematic diagram of the AZTA memristor simulating the working mechanism of a biological synapse. Excitatory postsynaptic current (EPSC) under different (b) pulse amplitudes (The pulse length and interval are 500 μs with leading and training times of 100 μs), (c) pulse lengths (The pulse amplitude is -4 V), and (d) pulse frequencies (The pulse amplitude is -4 V and the pulse length is 500 μs), respectively. The leading and training times were not set in the pulse length and frequency tests for better comparison and calculation.

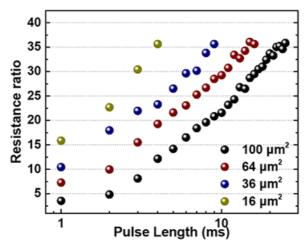

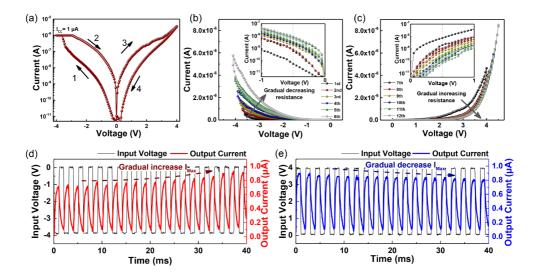

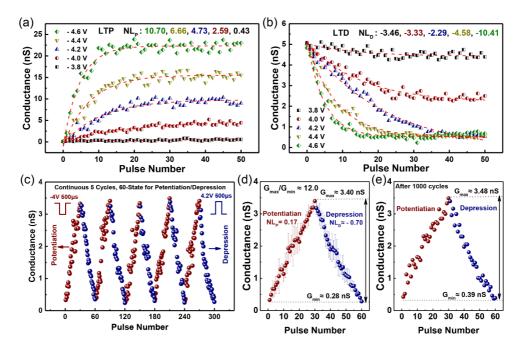

**Figure 3.4.** (a) Long-term potentiation characteristics under different pulse amplitudes from -3.8 V to -4.6 V. (b) Long-term depression characteristics under different pulse amplitudes from 3.8 V to 4.6 V. (c) Five consecutive long-term plasticity tests with the pulse conditions of -4.0 V/500 µs and 4.2 V/500 µs for potentiation and depression, respectively. (d) The average results of five consecutive cycles with the conductance ratio of 12.0. (e) The potentiation and depression test after 1000 pulse cycles.

**Figure 3.5.** The gradual changing I-V characteristics of AZTA memristor at DC sweep mode. (a) The set sweep voltage is set to - 3.6V. (b) The reset sweep voltage is set to 2.8V.

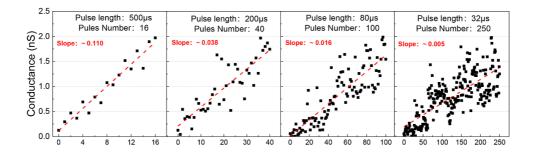

**Figure 3.6.** The conductance change trend as the different pulse lengths and pulse numbers. The switching box switches between pulse trains and 0.5V DC reading operations with a time interval of 1 second. The red dash line is the best linear fitting for the conductance.

xvi

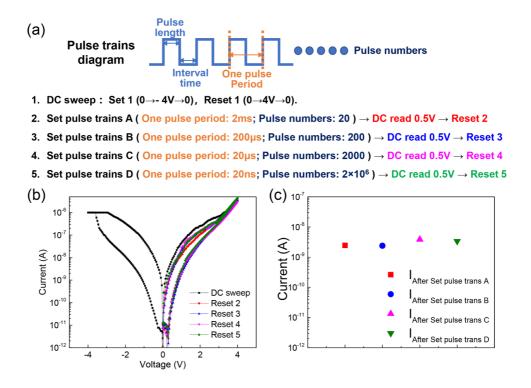

**Figure 3.7.** (a) The schematic diagram of all pulse trains, while the testing was performed in numerical order from 1 to 5. The total applied pulse length and interval time was equal for all pules trains, both 20ms. (b) I-V curves at DC sweep mode, where the reset sweeps were performed to confirm that the device had returned to its initial state. (c) The read currents after the pulse trains at a read voltage of 0.5 V.

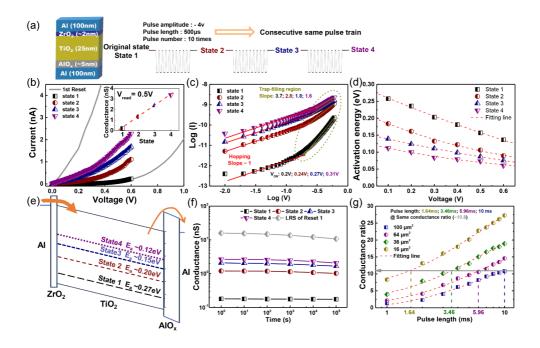

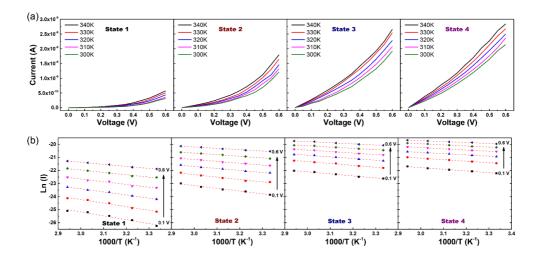

**Figure 3.8.** (a) Four different conductance states were obtained by continuously applying the same pulse trains. (b) The I-V curves of the four states under a DC sweep mode from 0 to 0.6 V. The conductance of four states at the read voltage of 0.5 V is shown in the inset figure. (c) The double log plot of I-V curves in four states. The red and yellow lines represent the fitting of the hopping and SCLC mechanisms, respectively. The intersection point of the two lines is the transition voltage. (d) The activation energies of four states were obtained from 0 V to 0.6 V by the temperature test and Arrhenius fitting. The red dash line is the best nonlinear fitting of 4 states. (e) Schematic diagram of electronic injection during the potentiation process. Electrons at the top interface are massively injected through the ultra-thin ZrO<sub>2</sub> layer, while their loss at the bottom interface is minimized due to the high potential barrier of Al2O3. The dash lines of various colors represent trap energy levels at different depths. The number of segments in the dashed lines represents a qualitative comparison of the number of traps. (f) The retention behavior of the four conductance states and the low resistance state (LRS) for the first reset process at room temperature over 105 seconds. (g) The conductance ratio changes of devices with different areas (100  $\mu$ m<sup>2</sup>, 64  $\mu$ m<sup>2</sup>, 36  $\mu$ m<sup>2</sup>, and 16  $\mu$ m<sup>2</sup>) under different pulse lengths from 1 ms to 10 ms. The solid gray line represents the conductance ratio is 10.8. The red dash line is the best nonlinear fitting for each state.

Figure 3.9. (a) The temperature dependence characteristics of the four states at the temperature range of 300 K to 340 K of the AZTA artificial synapse. (b) The Arrhenius-type plots of the temperature test data for calculating the activation energy ( $E_a$ ) from 0.1 V to 0.6 V.

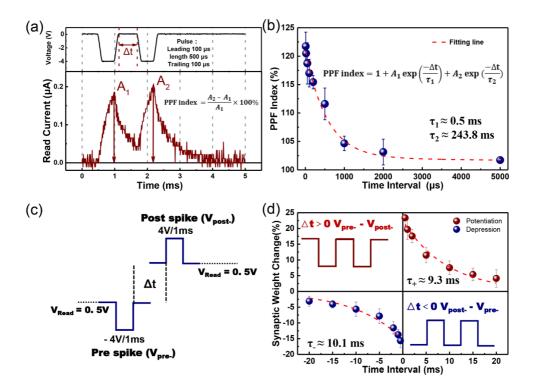

**Figure 3.10.** (a) Schematic diagram of pulse train stimulation for the PPF test. The pulse train parameter is  $-4 \text{ V}/500 \text{ }\mu\text{s}$  with the leading and trailing time is 100  $\mu\text{s}$ . (b) PPF index is plotted as a function of the interval time (blue dot ball), extracted from 3 independent tests. The red dash line best fits the data points with a double exponential

function. (c) The pre-synaptic and post-synaptic pulses were set to -4 V/500 µs and 4 V/500 µs, respectively. The AZTA synapse was read with a 0.5 V DC voltage before and after the pulse train to determine changes in synaptic weight. (d) The asymmetric STDP behavior of the AZTA artificial synapse. Synaptic weight changes are plotted as a function of the interval between the pre-synaptic and post-synaptic pulses. The red dashed line best fits the data points with an exponential function.

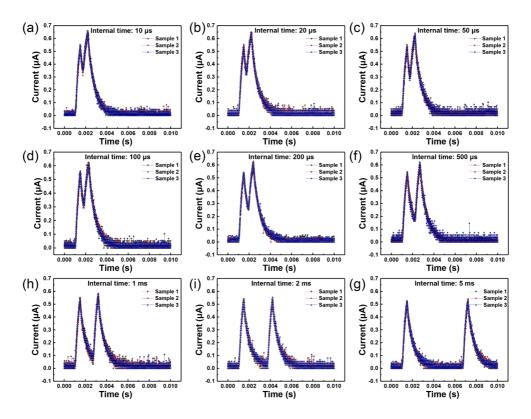

**Figure 3.11.** EPSC characteristics at different interval times for the PPF test.

**Figure 3.12.** (a) Schematic diagram of MLP neural network based on the AZTA synaptic devices. (b) Identification accuracy under different conductance states.

#### Chapter 1. Introduction

#### 1.1. Resistance random access memory (RRAM)

Non-volatile memory is a storage technology that is very different from traditional random access memory (RAM), such as DRAM or SRAM, in that it is able to store data in the event of power failure. In the past decade, this type of non-volatile memory device has developed rapidly and is widely used in many fields, such as smart electronic devices (such as mobile phones, computers, in-vehicle systems), encryption technology, artificial intelligence, etc.<sup>1-4</sup> The resistance random access memory has been widely concerned because of its excellent performance, such as fast read and write speed, low power consumption, and compatibility with CMOS technology.<sup>5-9</sup>

Resistive switching was first observed by Hickmott in 1962 in binary oxides, but it was in the early 2000s only when the resistive switching effect caught huge interest triggered by the search for alternative memory technology. The concept of RRAM used for neural networks and logic circuits was first published in Nature by HP in 2008.<sup>10</sup> The paper titled "The Missing Memristor Found" triggered another heat of RRAM development.

Usually, Resistance random access memory consists of a metal-

1

insulator-metal (MIM) structure, including a top electrode, an intermediate layer as the resistance switching layer, and a bottom electrode.<sup>11</sup> Such a typical MIM-structured RRAM device is schematically shown in Figure 1.1 (a). Under the action of applied voltage, the resistance of the device will be reversibly switched to realize data storage and reading, as shown in Figure 1.1 (b).

**Figure 1.1.** (a) Schematic diagram showing typical metal-insulatormetal (MIM) structure of ReRAM with electrical biasing. (b) Schematic illustration of bipolar switching characteristics in ReRAM. For the bipolar switching, "set" and "reset" processes occur at different polarity.<sup>11</sup>

#### 1.2. Two resistance switching mechanisms

At present, the mainstream resistance switching mechanism can be divided into the filamentary type and non-filamentary type, also known as the interface type.

Filamentary-type resistance random access memory devices are controlled by the random formation and rapture of conductive filaments, which are usually composed of oxygen vacancies or active metal ions (such as copper ions, silver ions, etc.), so the resistance transition relies on highly localized conductive filaments, usually tens or tens of nanometers in diameter. There is no doubt that the formation of conductive filaments will inevitably lead to the problem of high power consumption, and the randomly formed conductive filaments also lead to the problem of poor uniformity and low reliability.

In contrast, non-filamentary types of resistance random access memory devices based on oxygen vacancy/ion movement or carrier capture and release control have irreplaceable advantages in some aspects and maybe a better choice. The resistance switching of this type of resistive device occurs over the entire area, so it usually exhibits slow resistance changes, resulting in excellent uniformity, and is not prone to hard breakdown that can cause device failure. In addition, the power consumption of non-filamentary type devices can

4

be reduced proportionally with the reduction of device size, and this area scalability is particularly beneficial for improving the integration of CBA RRAM. Unfortunately, although non-filamentary resistive devices show many advantages, the reported devices are usually accompanied by poor endurance and retention performance.

**Figure. 1.2.** I–V curves for (a) unipolar (nonpolar) switching in a Pt/NiO/Pt cell and (b) bipolar switching in a  $Ti/La_2CuO_4/La_{1.65}Sr_{0.35}$  CuO<sub>4</sub> cell. In unipolar switching, the switching direction depends on the amplitude of the applied voltage. Bipolar switching shows directional resistance switching according to the polarity of the applied voltage. Proposed models for resistive switching can be classified according to either (c) a filamentary conducting path, or (d) an interface-type conducting path. (Part (a) courtesy of I. H. Inoue, AIST.)<sup>12</sup>

# 1.3. Artificial synapses based on nonvolatile memristors for the neural networks

Current neural networks are based on von Neumann architecture, combined with machine learning as a combination of software and hardware components based on complementary metal oxide semiconductor (CMOS) technology. However, the von Neumann computing system requires a central processing unit (CPU) to perform serial operations, its structural design is very inflexible and requires a large number of transistors. Because of this von Neumann bottleneck, the data processing speed of the storage device is limited between the memory and the CPU, forming a storage wall that requires great power consumption and space. Therefore, there is an urgent need for a new neuromorphic computing system with high computing speed, low energy consumption, and small size.

In order to meet this requirement, various memory materials have been studied to simulate the various functions of human brain synapses, as shown in Figure 1.3.<sup>13</sup> A memristor device can function as a single synaptic unit without the need for additional software programming support. The neuromorphic architecture based on a non-volatile memristor is implemented by parallel operation, which has the characteristics of low power consumption, small volume, and

7

high data processing capacity.

The concept of artificial synapses can be traced back to the 1940s when researchers first began exploring the construction of artificial neural networks. These networks were designed to perform tasks similar to the human brain, and early prototypes employed simple circuits to implement artificial synapses. In recent years, the rapid advancement of technology has allowed researchers to investigate more complex neural networks to achieve more advanced artificial intelligence systems. As a result, artificial synapses have received widespread attention as a key electronic component of these systems, designed to simulate the behavior of biological synapses, which are the connections between neurons in the brain. The primary requirement for artificial synapses that can be used in neuromorphic systems is their ability to exhibit synaptic plasticity, which is the ability to change synaptic strength based on electrical stimulation.<sup>1, 3,</sup> <sup>14-16</sup> In addition to synaptic plasticity, other crucial indicators that must be considered include power consumption, scalability, signalto-noise ratio, operation speed, reliability, non-linearity and so on.<sup>17-</sup> <sup>21</sup> Currently, there are numerous emerging non-volatile memory devices, including resistive random access memory (RRAM),<sup>22-28</sup> magnetic random access memory (MRAM),<sup>29, 30</sup> phase change memory (PCM),<sup>31, 32</sup> and ferroelectric memory (FRAM),<sup>33-36</sup> that have

8

been reported to simulate artificial synapses in neuromorphic computing systems. However, few devices can simultaneously fulfill all the necessary requirements for an ideal artificial synapse. Out of these options, metal-oxide RRAM has been widely studied due to its exceptional physical properties, electrical adjustability, and compatibility with traditional complementary metal-oxidesemiconductor (CMOS) integration processes.<sup>37, 38</sup> A schematic diagram of artificial synapses stimulating biological synapses based on ReRAM is shown in Figure 1.4.<sup>13</sup>

**Figure. 1.3.** Recent memristive materials applied for artificial synapses: metal oxides, organic materials, 2D materials, and emerging materials.<sup>13</sup>

**Figure. 1.4.** Comparison between biological synapses and artificial synapses. a) Schematic diagram of a preneuron, postneuron, and synapse. Reproduced with permission. b) Schematic diagram of neurotransmission process. c) A general structure of two terminal memristors-based artificial synapses.<sup>13</sup>

# 1.4. Nonlinearity of the artificial synapses based on RRAM devices

As mentioned in the previous section, an ideal artificial synapse needs to meet a variety of performance indicators, among which non-linearity is a very important one, as shown in Figure 1.5.<sup>17</sup> Under ideal conditions, the device can greatly reduce the design pressure of the peripheral circuit, and it is expected to obtain satisfactory multiple operable states.

Ideal linearity is defined as a state in which changes in conductance update due to a potentiation/depression do not depend on the current conductance state. To obtain the linearity factor of the potentiation (NL<sub>P</sub>) and depression (NL<sub>D</sub>), the conductance as a function of the normalized pulse number is modeled by:

$$\begin{cases} G_P = K(1 - e^{-NL_P \times P_n}) + G_{min} \\ G_D = G_{max} - K(1 - e^{-NL_D(p_{max} - P_n)}) \\ K = \frac{G_{max} - G_{min}}{1 - e^{-NL \times P_{max}}} \end{cases}$$

(1)

, where the  $G_P$  and  $G_D$  are the conductance value for each potentiation and depression.  $G_{max}$  and  $G_{min}$  are the maximum and minimum conductance values, respectively.  $P_n$  and  $P_{max}$  are the normalized pulse number and maximum normalized pulse number  $(P_{max}=1)$ , respectively. K is the function of NL to fit the  $G_P$  and  $G_D$  functions within the range of  $G_{max}$ ,  $G_{min}$ , and  $P_{max}$ . When the NL is zero, the conductance update is ideally linear.

Many resistive switching devices have been shown to possess superior potential in achieving synaptic functions for neuromorphic systems.<sup>23-26, 39-41</sup> Memristors based on CFs have received widespread attention due to their exceptional performance as memory devices, which includes low programming voltage, high on/off ratio, and good endurance and retention properties. As a result, filamentary-type RRAM has been extensively studied to simulate artificial synapses and successfully showed various basic features such as short-term and long-term synaptic plasticity, PPF, and STDP. However, the randomly formed and broken filaments result in relatively poor uniformity, and the current of the device cannot be uniformly scaled with device size, leading to high power consumption. Also, the conductance change of synapses based on the filamentary mechanism usually exhibits unsatisfactory non-linearity. In order to achieve near-linear modulation of conductance change to improve synaptic performance, the devices need to apply gradually varying electrical stimuli, such as gradually increasing or decreasing the amplitude or width of the pulse trains, which poses significant challenges in peripheral circuit design.<sup>30, 42-45</sup> Although some researchers have attempted to achieve linearly modulated

1 3

conductance by doping, this approach still cannot solve the high power consumption issue associated with such devices.<sup>46</sup> In contrast, RRAM based on a non-filamentary mechanism may represent a better choice for simulating synapses to achieve superior synaptic properties. This is because, unlike filaments that form and break at random, such non-filamentary type memristors participate in electrical conduction throughout the entire electrode area, generally displaying excellent uniformity and good scalability behavior, whereby the area of the device can be scaled to achieve very low power consumption.<sup>7, 21, 47</sup> This unique mechanism makes this device promising to obtain better nonlinearity. However, the synaptic devices based on non-filamentary memristors have been the subject of limited research, and the modulation mechanism of conductance to simulate synaptic behavior still requires further discussion and exploration. 48, 49

**Figure. 1.5.** Schematic illustration of non-ideal synaptic device properties modeled in the MLP simulator, including (1) nonlinear weight update (a), (2) weight precision, (3) device-to-device weight update variation, (4) cycle-to-cycle weight update variation, (5) dynamic range (conductance ON/OFF ratio) and (6) conductance variation (b).

#### 1.5. Research scope and objective

The objective of this paper is to investigate the unique electronic bipolar resistive switching mechanism in non-filamentary-type TiO<sub>2</sub>based RRAM. Based on the analysis of its degradation mechanisms, a method is proposed to improve its resistance switching performance by inserting an ultra-thin ZrO<sub>2</sub> layer. Additionally, based on this optimized AZTA RRAM device, the various synaptic characteristics are simulated, exploring its application in neuromorphic computing.

The demand for memory devices is increasing with the development of information technology. Traditional storage devices have some limitations, such as high-power consumption and poor reliability. Therefore, the researchers began to focus on new types of memory devices, including electronic bipolar resistance switching (e-BRS) RRAM, which is controlled by the switching of resistance states through the capture and release of electrons. Compared with other types of memory devices, e-BRS RRAM has the characteristics of low failure risk and no current formation. The study aimed to improve the performance of e-BRS RRAM devices, in particular, to improve their durability and data retention capabilities. In Chapter 2, the method of inserting a protection layer in the resistance switching process is proposed, hoping to prevent the active aluminum electrode

from continuously absorbing oxygen ions, thereby increasing the trap density in the resistance switching layer, and thereby improving the stability and consistency of the device. The main objective of the study was to evaluate the performance improvement after the insertion of ZrO<sub>2</sub> layers at the top interface of the Al/TiO<sub>2</sub>/AlO<sub>x</sub>/Al RRAM structure. By comparing the  $Al/TiO_2/AlO_x$  (ATA) structure with no protective layer inserted, it is expected to observe improved durability, data retention, consistency, and reduced power consumption. At the same time, it is also hoped to verify that the selection of the ZrO<sub>2</sub> layer meets the requirements of the protective layer and does not have a negative impact on the e-BRS mechanism. The resistive conversion process based on the space charge limiting current mechanism will also be discussed in detail. The results of this study will help advance the development of e-BRS RRAM technology and provide a potential solution for the application of high-density memory devices.

With the rapid development of artificial intelligence systems, the third-generation artificial neural morphologic network has been widely studied. Artificial neural networks need to simulate the connections between biological neurons, so artificial synapses, as an important electronic component, have attracted much attention. In order to simulate the performance of brain synapses, artificial

$1 \ 7$

synapses need to have key indicators such as plasticity, low power consumption, scalability, high signal-to-noise ratio, fast operation speed, and reliability. Among many new non-volatile memory devices, metal oxide resistance random access memory (RRAM) has been widely studied due to its excellent physical properties, electrical performance, and compatibility with traditional integrated processes. In Chapter 3, based on the previously developed non-filamentary Al/ZrO<sub>2</sub>/TiO<sub>2</sub>/Al RRAM device, which has excellent uniformity, no formation operation, and scalability, the ability of the device to simulate artificial synapses is systematically investigated. It also demonstrates excellent synaptic plasticity under more complex biological synaptic functions such as long-term enhancement, longterm inhibition, pulse-pair enhancement, and time-dependent plasticity. By optimizing the pulse stimulation conditions, near-linear long-term enhancement and inhibition changes are achieved. The conductive mechanism that governs the synaptic plasticity of the non-fiber RRAM device, namely the trap-assisted space chargelimiting current mechanism, is also revealed. In addition, due to its area-scalable behavior, non-fiber AZTA synaptic devices show potential for ultra-low power consumption and fast operating speeds. The purpose of this study is to explore and understand the synaptic performance and conduction mechanism of non-fiber Al/ZrO<sub>2</sub>/TiO<sub>2</sub>/Al

RRAM devices, so as to promote the development of artificial synapses and improve the performance of neural networks.

#### 1.6. Bibliography

1. Jo, S. H.; Chang, T.; Ebong, I.; Bhadviya, B. B.; Mazumder, P.; Lu, W., Nanoscale memristor device as synapse in neuromorphic systems. *Nano Lett* **2010**, *10* (4), 1297-301.

2. Yu, S.; Wu, Y.; Jeyasingh, R.; Kuzum, D.; Wong, H. S. P., An Electronic Synapse Device Based on Metal Oxide Resistive Switching Memory for Neuromorphic Computation. *IEEE Transactions on Electron Devices* **2011**, *58* (8), 2729–2737.

3. Wang, Z.; Joshi, S.; Savel'ev, S. E.; Jiang, H.; Midya, R.; Lin, P.; Hu, M.; Ge, N.; Strachan, J. P.; Li, Z.; Wu, Q.; Barnell, M.; Li, G. L.; Xin, H. L.; Williams, R. S.; Xia, Q.; Yang, J. J., Memristors with diffusive dynamics as synaptic emulators for neuromorphic computing. *Nat Mater* **2017**, *16* (1), 101–108.

4. Hong, X.; Loy, D. J.; Dananjaya, P. A.; Tan, F.; Ng, C.; Lew, W., Oxide-based RRAM materials for neuromorphic computing. *Journal of Materials Science* **2018**, *53* (12), 8720-8746.

5. Kim, S.; Choi, Y.-K., A Comprehensive Study of the Resistive Switching Mechanism in  $Al/TiO_x/TiO_2/Al$ -Structured RRAM. *IEEE Transactions on Electron Devices* **2009**, *56* (12), 3049–3054.

Waser, R.; Dittmann, R.; Staikov, G.; Szot, K., Redox-Based Resistive Switching Memories - Nanoionic Mechanisms, Prospects, and Challenges. *Advanced Materials* 2009, *21* (25-26), 2632-2663.

7. Kim, S.; Jeong, H. Y.; Choi, S.-Y.; Choi, Y.-K.,

Comprehensive modeling of resistive switching in the  $Al/TiO_x/TiO_2/Al$  heterostructure based on space-charge-limited conduction. *Applied Physics Letters* **2010**, *97*(3).

Kwon, D. H.; Kim, K. M.; Jang, J. H.; Jeon, J. M.; Lee, M.

H.; Kim, G. H.; Li, X. S.; Park, G. S.; Lee, B.; Han, S.; Kim,

M.; Hwang, C. S., Atomic structure of conducting nanofilaments in TiO<sub>2</sub> resistive switching memory. *Nat Nanotechnol* 2010, *5* (2), 148– 53.

9. Hermes, C.; Wimmer, M.; Menzel, S.; Fleck, K.; Bruns,

G.; Salinga, M.; Bottger, U.; Bruchhaus, R.; Schmitz-Kempen,

T.; Wuttig, M.; Waser, R., Analysis of Transient Currents During

Ultrafast Switching of TiO<sub>2</sub> Nanocrossbar Devices. *IEEE Electron Device Letters* 2011, *32* (8), 1116-1118.

Strukov, D. B.; Snider, G. S.; Stewart, D. R.; Williams, R. S., The missing memristor found. *Nature* 2008, 453 (7191), 80–3.

11. Prakash, A.; Hwang, H., Multilevel Cell Storage and Resistance Variability in Resistive Random Access Memory. *Physical Sciences Reviews* **2016**, *1* (6).

Sawa, A., Resistive switching in transition metal oxides.

Materials Today 2008, 11 (6), 28-36.

13. Kim, S. G.; Han, J. S.; Kim, H.; Kim, S. Y.; Jang, H. W., Recent Advances in Memristive Materials for Artificial Synapses. *Advanced Materials Technologies* **2018**, *3* (12).

14. Zhou, G.; Wang, Z.; Sun, B.; Zhou, F.; Sun, L.; Zhao, H.; Hu, X.; Peng, X.; Yan, J.; Wang, H.; Wang, W.; Li, J.; Yan, B.;

$2\ 1$

Kuang, D.; Wang, Y.; Wang, L.; Duan, S., Volatile and Nonvolatile Memristive Devices for Neuromorphic Computing. *Advanced Electronic Materials* **2022**, *8* (7).

15. Milo, V.; Malavena, G.; Monzio Compagnoni, C.; Ielmini, D., Memristive and CMOS Devices for Neuromorphic Computing. *Materials (Basel)* **2020**, *13* (1).

16. van de Burgt, Y.; Melianas, A.; Keene, S. T.; Malliaras,

G.; Salleo, A., Organic electronics for neuromorphic computing. *Nature Electronics* 2018, 1 (7), 386–397.

17. Islam, R.; Li, H.; Chen, P.-Y.; Wan, W.; Chen, H.-Y.; Gao, B.; Wu, H.; Yu, S.; Saraswat, K.; Philip Wong, H. S., Device and materials requirements for neuromorphic computing. *Journal of Physics D: Applied Physics* **2019**, *52* (11).

18. Chen, Y.; Yu, H.; Gong, J.; Ma, M.; Han, H.; Wei, H.; Xu,

W., Artificial synapses based on nanomaterials. *Nanotechnology* 2019, *30*(1), 012001.

19. Han, H.; Yu, H.; Wei, H.; Gong, J.; Xu, W., Recent Progress in Three-Terminal Artificial Synapses: From Device to System. *Small* **2019**, *15* (32), e1900695.

20. Xia, Q.; Yang, J. J., Memristive crossbar arrays for braininspired computing. *Nat Mater* **2019**, *18* (4), 309-323.

21. Burr, G. W.; Shelby, R. M.; Sebastian, A.; Kim, S.; Kim, S.; Sidler, S.; Virwani, K.; Ishii, M.; Narayanan, P.; Fumarola, A.; Sanches, L. L.; Boybat, I.; Le Gallo, M.; Moon, K.; Woo, J.; Hwang, H.; Leblebici, Y., Neuromorphic computing using non-volatile

$2 \ 2$

memory. Advances in Physics: X 2016, 2(1), 89-124.

22. Liu, Q.; Yin, L.; Zhao, C.; Wu, Z.; Wang, J.; Yu, X.; Wang, Z.; Wei, W.; Liu, Y.; Mitrovic, I. Z.; Yang, L.; Lim, E. G.; Zhao, C. Z., All-in-one metal-oxide heterojunction artificial synapses for visual sensory and neuromorphic computing systems. *Nano Energy* **2022**, *97*.

Yan, X.; Qin, C.; Lu, C.; Zhao, J.; Zhao, R.; Ren, D.;

Zhou, Z.; Wang, H.; Wang, J.; Zhang, L.; Li, X.; Pei, Y.; Wang,

G.; Zhao, Q.; Wang, K.; Xiao, Z.; Li, H., Robust Ag/ZrO<sub>2</sub>/WS<sub>2</sub>/Pt

Memristor for Neuromorphic Computing. ACS Appl Mater Interfaces

2019, 11 (51), 48029-48038.

Wang, T.; Shi, Y.; Puglisi, F. M.; Chen, S.; Zhu, K.; Zuo,

Y.; Li, X.; Jing, X.; Han, T.; Guo, B.; Bukvisova, K.; Kachtik,

L.; Kolibal, M.; Wen, C.; Lanza, M., Electroforming in Metal-Oxide

Memristive Synapses. ACS Appl Mater Interfaces 2020, 12 (10),

11806-11814.

25. Li, J.; Hao, C.; Guo, S.; Li, Y.; Ren, J.; Zhou, L.; Zhao, J., Flexible Ta/TiOx/TaOx/Ru memristive synaptic devices on polyimide substrates. *Nanotechnology* **2021**, *32* (33).

26. Wang, H.; Yan, X.; Wang, S.; Lu, N., High-Stability Memristive Devices Based on Pd Conductive Filaments and Its Applications in Neuromorphic Computing. *ACS Appl Mater Interfaces* **2021**, *13* (15), 17844-17851.

27. Leng, K.; Yu, X.; Ma, Z.; Li, W.; Xu, J.; Xu, L.; Chen, K., Artificial synapse arrays based on SiOx/TiOx memristive crossbar with high uniformity for neuromorphic computing. *Applied Physics*

#### Letters 2022, 120(4).

28. Lee, M. J.; Park, G. S.; Seo, D. H.; Kwon, S. M.; Lee, H. J.; Kim, J. S.; Jung, M.; You, C. Y.; Lee, H.; Kim, H. G.; Pang, S. B.; Seo, S.; Hwang, H.; Park, S. K., Reliable Multivalued Conductance States in TaO<sub>x</sub> Memristors through Oxygen Plasma-Assisted Electrode Deposition with in Situ-Biased Conductance State Transmission Electron Microscopy Analysis. *ACS Appl Mater Interfaces* **2018**, *10* (35), 29757-29765.

29. Romera, M.; Talatchian, P.; Tsunegi, S.; Abreu Araujo, F.; Cros, V.; Bortolotti, P.; Trastoy, J.; Yakushiji, K.; Fukushima, A.; Kubota, H.; Yuasa, S.; Ernoult, M.; Vodenicarevic, D.; Hirtzlin, T.; Locatelli, N.; Querlioz, D.; Grollier, J., Vowel recognition with four coupled spin-torque nano-oscillators. *Nature* **2018**, *563* (7730), 230-234.

30. Zhang, X.; Cai, W.; Wang, M.; Pan, B.; Cao, K.; Guo, M.; Zhang, T.; Cheng, H.; Li, S.; Zhu, D.; Wang, L.; Shi, F.; Du, J.; Zhao, W., Spin-Torque Memristors Based on Perpendicular Magnetic Tunnel Junctions for Neuromorphic Computing. *Adv Sci (Weinh)* **2021**, *8* (10), 2004645.

31. Sebastian, A.; Tuma, T.; Papandreou, N.; Le Gallo, M.; Kull, L.; Parnell, T.; Eleftheriou, E., Temporal correlation detection using computational phase-change memory. *Nat Commun* **2017**, *8*(1), 1115.

32. Le Gallo, M.; Sebastian, A.; Mathis, R.; Manica, M.; Giefers, H.; Tuma, T.; Bekas, C.; Curioni, A.; Eleftheriou, E., Mixed-precision in-memory computing. *Nature Electronics* **2018**, *1*

(4), 246-253.

33. Yang, Y.; Xi, Z.; Dong, Y.; Zheng, C.; Hu, H.; Li, X.; Jiang, Z.; Lu, W. C.; Wu, D.; Wen, Z., Spin-Filtering Ferroelectric Tunnel Junctions as Multiferroic Synapses for Neuromorphic Computing. *ACS Appl Mater Interfaces* **2020**, *12* (50), 56300-56309.

34. Xi, F.; Han, Y.; Liu, M.; Bae, J. H.; Tiedemann, A.; Grutzmacher, D.; Zhao, Q. T., Artificial Synapses Based on Ferroelectric Schottky Barrier Field-Effect Transistors for Neuromorphic Applications. *ACS Appl Mater Interfaces* **2021**, *13* (27), 32005–32012.

35. Shen, R.; Jiang, Y.; Li, X.; Tian, J.; Li, S.; Li, T.; Chen, Q., Artificial Synapse Based on an InAs Nanowire Field-Effect Transistor with Ferroelectric Polymer P(VDF-TrFE) Passivation. *ACS Applied Electronic Materials* **2022**, *4* (10), 5008-5016.

36. Wang, Z.; Guan, Z.; Sun, H.; Luo, Z.; Zhao, H.; Wang, H.; Yin, Y.; Li, X., High-Speed Nanoscale Ferroelectric Tunnel Junction for Multilevel Memory and Neural Network Computing. *ACS Appl Mater Interfaces* **2022**, *14* (21), 24602–24609.

37. Zahoor, F.; Azni Zulkifli, T. Z.; Khanday, F. A., Resistive Random Access Memory (RRAM): an Overview of Materials, Switching Mechanism, Performance, Multilevel Cell (mlc) Storage, Modeling, and Applications. *Nanoscale Res Lett* **2020**, *15* (1), 90.

Wang, Z.; Wu, H.; Burr, G. W.; Hwang, C. S.; Wang, K.

L.; Xia, Q.; Yang, J. J., Resistive switching materials for information processing. *Nature Reviews Materials* 2020, *5* (3), 173–195.

39. Wang, T. Y.; Meng, J. L.; Rao, M. Y.; He, Z. Y.; Chen, L.; Zhu, H.; Sun, Q. Q.; Ding, S. J.; Bao, W. Z.; Zhou, P.; Zhang, D. W., Three-Dimensional Nanoscale Flexible Memristor Networks with Ultralow Power for Information Transmission and Processing Application. *Nano Lett* **2020**, *20* (6), 4111-4120.

40. Wang, L.; Liao, W.; Wong, S. L.; Yu, Z. G.; Li, S.; Lim, Y. F.; Feng, X.; Tan, W. C.; Huang, X.; Chen, L.; Liu, L.; Chen, J.; Gong, X.; Zhu, C.; Liu, X.; Zhang, Y. W.; Chi, D.; Ang, K. W., Artificial Synapses Based on Multiterminal Memtransistors for Neuromorphic Application. *Advanced Functional Materials* **2019**, *29* (25).

41. Ren, J.; Liang, H.; Li, J.; Li, Y. C.; Mi, W.; Zhou, L.; Sun, Z.; Xue, S.; Cai, G.; Zhao, J. S., Polyelectrolyte Bilayer-Based Transparent and Flexible Memristor for Emulating Synapses. *ACS Appl Mater Interfaces* **2022**, *14* (12), 14541-14549.

42. Kim, S.; Kim, H.; Hwang, S.; Kim, M. H.; Chang, Y. F.; Park, B. G., Analog Synaptic Behavior of a Silicon Nitride Memristor. *ACS Appl Mater Interfaces* **2017**, *9* (46), 40420–40427.

43. Mahata, C.; Kang, M.; Kim, S., Multi-Level Analog Resistive Switching Characteristics in Tri-Layer HfO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub>/HfO<sub>2</sub> Based Memristor on ITO Electrode. *Nanomaterials (Basel)* **2020**, *10* (10).

44. Li, Y.; Chen, S.; Yu, Z.; Li, S.; Xiong, Y.; Pam, M. E.; Zhang, Y. W.; Ang, K. W., In-Memory Computing using Memristor Arrays with Ultrathin 2D PdSeO(x) /PdSe(2) Heterostructure. *Adv Mater* **2022**, *34* (26), e2201488.

45. Tang, B.; Veluri, H.; Li, Y.; Yu, Z. G.; Waqar, M.; Leong,

J. F.; Sivan, M.; Zamburg, E.; Zhang, Y. W.; Wang, J.; Thean, A. V., Wafer-scale solution-processed 2D material analog resistive memory array for memory-based computing. *Nat Commun* **2022**, *13* (1), 3037.

46. Kang, J.; Kim, T.; Hu, S.; Kim, J.; Kwak, J. Y.; Park, J.; Park, J. K.; Kim, I.; Lee, S.; Kim, S.; Jeong, Y., Cluster-type analogue memristor by engineering redox dynamics for highperformance neuromorphic computing. *Nat Commun* **2022**, *13* (1), 4040.

47. Shao, X. L.; Zhou, L. W.; Yoon, K. J.; Jiang, H.; Zhao, J. S.; Zhang, K. L.; Yoo, S.; Hwang, C. S., Electronic resistance switching in the Al/TiO<sub>x</sub>/Al structure for forming-free and area-scalable memory. *Nanoscale* **2015**, *7* (25), 11063-74.

48. Yan, Y.; Li, J. C.; Chen, Y. T.; Wang, X. Y.; Cai, G. R.; Park, H. W.; Kim, J. H.; Zhao, J. S.; Hwang, C. S., Area-Type Electronic Bipolar Switching Al/TiO<sub>1.7</sub>/TiO<sub>2</sub>/Al Memory with Linear Potentiation and Depression Characteristics. *ACS Appl Mater Interfaces* **2021**, *13* (33), 39561-39572.

49. Li, J.; Ge, C.; Lu, H.; Guo, H.; Guo, E. J.; He, M.; Wang, C.; Yang, G.; Jin, K., Energy-Efficient Artificial Synapses Based on Oxide Tunnel Junctions. *ACS Appl Mater Interfaces* **2019**, *11* (46), 43473-43479.

# Chapter 2. Performance improvement of Al/TiO<sub>2</sub>/Al electronic bipolar resistive switching memory via inserting an ultra-thin ZrO<sub>2</sub> layer at the top interface

### 2.1. Introduction

Over the past decades, the research of resistance switching random access memory (RRAM) with either one transistor-one resistor or crossbar array (CBA) has been very active.<sup>1-13</sup> In both configurations, the resistive switching (RS) is mainly controlled by the formation and rupture of conductive filaments (CFs), which are prone to hard breakdown during electroforming.<sup>14-16</sup> Also, the stochastic nature of the CF generally induced non-uniformity and low-reliability issues. Moreover, the operating current of this type of device is relatively high, which causes relatively high-power consumption. In contrast, the electronic bipolar resistance switching (e-BRS) device, induced by the trapping and de-trapping of the carriers (electrons), could be a better option. This assertion is based on the finding that the gradual current switching makes the catastrophic failure by the electrical breakdown much less probable. This improvement is also supported by the electroforming-free nature of the e-BRS

mechanism. Also, the area-scalable characteristic of the e-BRS device is especially conducive to improving integration for CBA RRAM, that the power consumption will decrease proportionally with the reduction of device size.<sup>17-19</sup> In addition, RRAM based on the e-BRS mechanism has also been found to have potential applications in highly flexible memory devices,<sup>20-23</sup> security applications,<sup>24</sup> and artificial synapse applications.<sup>25-29</sup>

Kim et al. initially suggested the working e-BRS mechanism in the Pt/TiO<sub>2</sub>/Pt RRAM cells in 2011.<sup>30</sup> They asserted that the e-BRS performance of the Pt/TiO<sub>2</sub>/Pt RRAM, which has to be electroformed first due to the high Schottky barrier between the Pt and TiO<sub>2</sub>, was mediated by the electron trapping (low resistance state, LRS) and de-trapping (high resistance state, HRS) at the defect sites (oxygen vacancies, VO) in the TiO<sub>2-x</sub> region between the Pt electrode and residual CF composed of magnéli phase Ti4O7. They performed a detailed analysis of defect density and the space-charge limited conduction (SCLC) mechanism. They indicated that the asymmetric potential barrier, i.e., high and low Schottky barrier at the Pt/TiO<sub>x</sub> and TiO<sub>x</sub>/magnéli CF, constituted the fundamental reason for the emergence of the BRS mechanism.

Also, Jeong et al. demonstrated stable e-BRS is closely related to the top and bottom interface domains in metal/amorphous-TiO<sub>2</sub>/metal

RRAM devices.<sup>4</sup> They regarded that the top interface with mobile oxygen ions would induce the redox reaction during the set (switching from HRS to LRS) and reset (switching from LRS to HRS) processes. In contrast, the bottom interface played a role as the blocking layer, which prevented the electric breakdown. In 2011, Kim et al. proved the formation of the Al-Ti-O interface layer at the top electrode in the Al/amorphous-TiO<sub>2</sub>/Al RRAM structure owing to the strong oxidation power of the Al.<sup>31</sup> They also suggested that the reversible formation and dissociation processes of the Al-Ti-O interface layer by the migration of oxygen ions under an applied bias constituted the RS mechanism.

Then, in 2015, Shao et al. reported Al/TiOx/Al structure e-BRS RS devices showed outstanding performance, such as electroforming-free and area-scalable behavior.<sup>19</sup> An ~5 nm insulating AlO<sub>x</sub> layer was naturally formed at the bottom Al electrode interface, which was not the case at the top Al interface. Therefore, this different interface configuration provided the necessary asymmetric potential barrier, in which the electron injection and ejection at the top interface were fluent. In contrast, they were prohibited at the bottom interface. Unfortunately, the switching endurance of such devices was not satisfactory, and the operation current level was generally too high. Detailed electrical and chemical

analysis showed that the top Al/TiO<sub>x</sub> interface gradually changed from the quasi-Ohmic contact property to the Schottky-type contact. This change means that the top electrode Al was slowly oxidized to AlO<sub>x</sub> due to continuous electrostimulation. At the same time, the top part of the TiO<sub>x</sub> RS layer became more oxygen-deficient, which no longer provided effective trap centers. This electrochemical reaction is unnecessary for the e-BRS mechanism to operate efficiently. Therefore, inserting a protective layer at the top electrode interface can be a feasible method to prevent the active Al electrode from continuously absorbing oxygen ions in the resistance layer TiO<sub>2</sub> as the cycle increases, which may improve RS endurance.

Nonetheless, the inserted protective layer must meet the following conditions: 1) The protective layer should not affect the e-BRS mechanism. That is, it should not form a too high potential barrier, thus not affecting the fluent injection and ejection of the electrons. 2) It should not absorb oxygen ions in the TiO<sub>2</sub> layer as efficiently as Al, meaning that the oxidation potential should be close to the TiO<sub>2</sub>. 3) The thickness of the protective layer needs to be accurately adjusted, not causing the device operation condition to deviate too much.

To this end, several oxide barrier materials ( $ZrO_2$ ,  $HfO_2$ ,  $Al_2O_3$ ) and different insertion layer thicknesses (1 – 5 nm) were studied, which are grown by thermal atomic layer deposition (ALD). Among them, the  $HfO_2$  and  $Al_2O_3$  layers were too insulating even at a thickness of 1 nm, interfering adversely with the fluent Ohmic contact property. In contrast, the 1-2 nm thick  $ZrO_2$  layer met the above requirements well.

Therefore, this work evaluated the performance improvement, especially the endurance, and retention, by inserting the  $ZrO_2$  layer at the top interface of the Al/TiO<sub>2</sub>/AlO<sub>x</sub> (natively formed)/Al RRAM structure. The Al/TiO<sub>2</sub>/AlO<sub>x</sub>/Al and Al/ZrO<sub>2</sub>/TiO<sub>2</sub>/AlO<sub>x</sub>/Al structures are called the "ATA" and "AZTA" samples, respectively. In the AZTA sample, the ultra-thin ZrO<sub>2</sub> layer blocked the undesired reduction TiO<sub>2</sub> layer in contact with the Al top electrode. As a result, the trap density in the TiO<sub>2</sub> resistive layer was maintained robustly even with the increasing number of the switching cycle, demonstrating the electroforming-free behavior, improved endurance to  $10^5$  times, and optimized uniformity and retention. In addition, the inserted thin ZrO<sub>2</sub> layer also generally decreased the operation current, making the device suitable for high-density array applications.

#### 2.2. Experimental

First, the 100 nm-thick Al bottom electrode film was deposited by the electron beam evaporator (Sorona, SRN-200i) on a 5nm-thick Ta<sub>2</sub>O<sub>5</sub> adhesion layer/SiO<sub>2</sub>/Si substrate. Next, the samples were transported to the TiO2 RS layer sputtering chamber via the air atmosphere, so the bottom Al electrode was oxidized to form an ~5nm-thick AlO<sub>x</sub> layer. Then, a 35nm-thick TiO<sub>2</sub> film was deposited on this AlO<sub>x</sub>/Al/Ta<sub>2</sub>O<sub>5</sub>/SiO<sub>2</sub>/Si substrate by a laboratory-made radio frequency sputter using a  $Ti_4O_7$  target and  $O_2/Ar$  reactive gas at room temperature (RF power: 125 W, deposition pressure: 0.015 Torr, oxygen concentration: 20% O<sub>2</sub>). For fabricating the AZTA samples, the different thick ZrO<sub>2</sub> layer was then deposited on the  $TiO_2$  layer by the thermal ALD system (Quros, Plus 200) with the 5, 10, and 20 deposition cycles, respectively (precursor:  $Zr[N(CH_3)(C_2H_5)]_4$ , oxygen source: O<sub>3</sub>, deposition temperature: 250 °C). The growth per cycle for the  $ZrO_2$  film was ~0.13 nm/cycle, so 10 ALD cycles deposited  $\sim 1.3$ nm-thick ZrO<sub>2</sub> layer on the TiO<sub>2</sub> film. Finally, the 100nm-thick Al top electrode was deposited by the electron beam evaporator. The bottom and top Al electrodes were patterned into line shapes with the width of 4, 6, 8, and 10 µm, respectively, via the lift-off process, so the fabricated RRAMs have 16, 36, 64, and 100  $\mu m^2$  areas. The fabricated samples were

annealed at 250  $\,^\circ C$  for 60 minutes to stabilize the contact property.

The composition and the film thickness of the  $TiO_2$  and  $ZrO_2$  films were examined by an X-Ray fluorescence analyzer (Thermo Scientific, ARL Quant'X EDXRF) and spectroscopic ellipsometry (Woollam, ESM-300, J. A.), respectively. In addition, the chemical structure of the  $TiO_2$  and  $ZrO_2$  film was examined by X-ray photoelectron spectroscopy (XPS, ThermoFisher Scientific, Sigma Probe).

The current-voltage (I–V) characteristics were measured using a semiconductor parameter analyzer (Hewlett Packard, 4145B) for the direct current (DC) sweep mode. The top electrode was biased, while the bottom electrode was grounded. The semiconductor parameter analyzer (Hewlett Packard, 4155B), a pulse generator (Tektronix, AFG3010C), and an oscilloscope (LeCroy, Wave Surfer 62MXs-B) were used for the pulse switching measurement. All data in this work were tested from the ATA and AZTA samples with an electrode area of  $10 \times 10 \ \mu m^2$ .

#### 2.3. Results and Discussions

## 2.3.1. Optimization of the $ZrO_2$ insertion layer thickness

First, the optimal thickness of the ZrO<sub>2</sub> layer was evaluated by estimating the RS performance of the ATA and ATZA samples with the  $ZrO_2$  ALD cycles of 5, 10, and 20, respectively. Figure 2.1(a) shows the typical I-V characteristics of the samples, which exhibit gradual set and reset switching at the positive and negative biases, respectively, with no involvement of the electroforming step. For these tests, an appropriate compliance current ( $I_{cc}$ ) of 1  $\mu A$  was settled to ensure that all traps in the TiO<sub>2</sub> layer could be sufficiently filled with electrons while preventing permanent device degradation. These properties coincide with the previous reports on a similar structure, suggesting that they follow the e-BRS mechanism.<sup>19, 32</sup> Specifically, the fluent electron injection from the top electrode and their trapping within the TiO<sub>2</sub> layer under the negative bias set the device. The de-trapping and trapping of the electrons under the positive bias reset the device.

The initial resistance values of all samples showed no significant difference. Still, the set voltage ( $V_{set}$ ) and LRS resistance ( $R_{LRS}$ ) increased with the increasing thickness of the ZrO<sub>2</sub> layer. The  $V_{set}$

and the  $R_{LRS}$  are tested at an  $I_{cc}$  of 1  $\mu A$  from 20 cells for statistical accuracy, as shown in Figure 2.1(b), with the different thickness ZrO<sub>2</sub> insertion layer. The ATA sample in Figure 2.1(b) underwent the same annealing process as the AZTA samples (250  $^{\circ}$ C, for 1 hour). This step was necessary to make all the samples' initial HRS resistance ( $R_{HRS}$ ) similar. The long ALD time (40 to 80 min for 5 to 20 cycles) for the AZTA samples rendered the initial  $R_{HRS}$  smaller as the ZrO<sub>2</sub> film thickness increased, as shown in Figure 2.2. This abnormal behavior must be due to the structural relaxation of the TiO<sub>2</sub> layer caused by the annealing effect during ALD, which decreased the trap density. Figure 2.1(b) shows that the total  $R_{LRS}$ , measured at 0.1 V, increases almost linearly with the ZrO<sub>2</sub> layer thickness, which indicates that the ZrO<sub>2</sub> layer act as a series resistance in the LRS in such a thin thickness range. Therefore, the |V<sub>set</sub>| also increased almost linearly with the ZrO<sub>2</sub> layer thickness. The slope of the bestlinear-fitted graphs indicated the increase rates in the  $R_{LRS}$  and  $|V_{set}|$  was  $3.37 \times 10^8$   $\Omega/nm$  and 0.66 V/nm, respectively. Figure 2.1(c) shows the cumulative distribution of the  $R_{HRS}$  and the  $R_{LRS}$  for each sample from the 20 cycles in one cell. The uniformity of the samples was improved as the ZrO<sub>2</sub> layer thickness increased, but the resistance ratio tended to decrease mainly due to the rapid increase of the R<sub>LRS</sub>. The high non-uniformity of the ATA sample could be ascribed to the irregular chemical interaction between the top Al electrode and TiO<sub>2</sub> layer, which the adopted  $ZrO_2$  protection layer could suppress. The 5 ALD cycles of  $ZrO_2$  correspond to a physical thickness of 0.65nm, slightly thicker than the one unit-cell thickness of the  $ZrO_2$  (~0.5nm). Therefore, suppressing such side effects by the 0.65nm-thick  $ZrO_2$  layer could be insufficient. Therefore, the data in Figures 2.1 (b) and (c) indicate that the 1.3nm-thick (10 cycles)  $ZrO_2$  layer is the optimum protection layer at the top interface. In the following sections, therefore, the data for the ATA and AZTA samples with the 1.3nm-thick  $ZrO_2$  layer effects.

**Figure 2.1.** The resistance switching characteristics of ATA (annealed) sample and AZTA samples with 5, 10, and 20 deposition cycles of the  $ZrO_2$  film. (a) Typical e-BRS I-V curves with an I<sub>cc</sub> of 1  $\mu$ A. (b) RLRS at the read voltage of 0.1 V and VSET at the I<sub>cc</sub> of 1  $\mu$ A from 20 memory cells. (c) The cumulative probability graphs of LRS and HRS from the 20 I-V sweeps in a single memory cell.

**Figure 2.2.** (a) Typical e-BRS I-V curves of ATA sample (without annealing), AZTA sample (5 cycles, 40 minutes), AZTA sample (10 cycles, 60 minutes), and AZTA sample (20 cycles, 80 minutes) fabricated by the thermal ALD with the different deposition time. (b) The I-V curves with a smaller range clearly show the degradation of HRS.

## 2.3.2. The resistance switching performance comparison

Figures 2.3 (a) and (b) showed the typical I-V curves of the ATA and AZTA samples, respectively, measured at room temperature with an  $I_{cc}$  of 0.5  $\mu$ A during the set. Both samples exhibited a gradual set/reset process without the abrupt current jump, which is consistent with the typical electronic type RS characteristics.<sup>19, 30, 33</sup> However, the two samples showed distinctive I-V curves with the increasing number of switching cycles. For the case of the ATA sample, the HRS current ( $I_{HRS}$ , read at -0.5V) increases rapidly from  $2.1 \times 10^{-2}$  nA at the first cycle to  $1.4 \times 10^{-1}$  nA at the 10th cycle and then slowly to  $4.7 \times 10^{-1}$  nA at the 100th cycle. The possible reason for such  $I_{HRS}$  variation was discussed in the later section, which examined the detailed conduction mechanisms. In contrast, the I<sub>HRS</sub> of the AZTA sample remained almost unvaried with a value of 3.3 - 7.1  $imes 10^{-2}$  nA at the same read voltage during the 100 switching cycles. This improvement could be ascribed to the suppression of the unwanted side effect of the top Al electrode by adopting the reaction barrier  $ZrO_2$  layer. Besides, the  $|V_{set}|$  of the AZTA sample increased from  $\sim 2.5V$  for the ATA sample to  $\sim 3.2V$  by the voltage partake effect of the ZrO<sub>2</sub> layer. The electrode area (S)-dependent behavior of the AZTA sample is shown in Figure 2.4. The  $R_{HRS}$  and  $R_{LRS}$  showed a slope of ~1 in the log R vs. log S graph, indicating a uniform current flow across the entire electrode area.

Figures 2.5 (a) and (b) showed the endurance performance of two samples from I–V sweeps up to 200 cycles. I<sub>cc</sub> was set to 0.5  $\mu$ A, and the resistance value was read at 0.5V for both samples. For the ATA sample, the R<sub>HRS</sub> rapidly decreased from ~ 1×10<sup>10</sup>  $\Omega$  in the first cycle to ~ 1×10<sup>9</sup>  $\Omega$  in the 20th cycle, then slowly down to ~ 8×10<sup>8</sup>  $\Omega$  in the 100th cycle. The R<sub>LRS</sub> did not show a notable variation and remained at ~ 8×10<sup>7</sup> ohms. The resistance ratio decreased from ~ 200 to ~ 10. While the resistance ratio of 10 is not insufficient for a feasible RRAM operation, such a substantial variation adds a burden to the drive circuit.

However, this was not the case in the AZTA sample, as shown in Figure 2.5 (b). The  $R_{HRS}$  and  $R_{LRS}$  values and their ratio (~ 65) did not show notable variations up to 100 I-V cycles. A similar contrasting trend could be found for the pulse-type switching, which is more relevant to the actual RRAM operation, as shown in Figures 2.5 (c) and (d). The resistance switching characteristics of the AZTA sample in the pulse test mode as shown in Figure 2.6. The resistance changes gradually with the pulse amplitude and length. A similar resistance ratio can be achieved at the pulse conditions with the

increasing pulse amplitude and decreasing pulse length. However, to achieve the best endurance performance in the pulse test, a set pulse with a relatively small pulse amplitude and a long pulse length was chosen to avoid a hard breakdown of the devices. At the same time, a reset pulse with a relatively large pulse amplitude and a long pulse length is chosen to confirm that the trapped electrons are fully detrapped. Finally, the set and reset pulses of -2.5 V/20 ms and 2.7 V/20 ms were selected for the ATA, and -4.0 V/20 ms and 5.0 V/20ms were for the AZTA sample. For statistical accuracy, three cells per sample were tested. The unusually long pulse (normal RRAM requires  $< 1 \mu s$ ) must also be ascribed to the relatively large area of the test cells (100  $\mu$ m<sup>2</sup>). Because the whole electrode region of the device participates in the electrical transportation for e-BRS devices. However, the size of the randomly formed conduct filaments for the filamentary-controlled devices is usually only a few tens of nanometers or even smaller.<sup>14, 34, 35</sup> Therefore, the area-type switching requires sufficient time to supply the required charges, but it also implies that the much smaller area device (ca.  $4 \times 10^{-4} \ \mu m^2$ ) might require a much shorter switching time (~ 0.1  $\mu$ s), which can be estimated by the resistance switching characteristics of the AZTA sample with different electrode areas in the pulse test mode, as shown in Figure 2.7. While the ATA sample showed significant decay of the  $R_{HRS}$  and  $R_{LRS}$ , even after 1000 cycles, at which the  $R_{HRS}$  became even smaller than  $R_{LRS}$  of the initial state, AZTA samples showed stable  $R_{HRS}$  and  $R_{LRS}$  values up to  $10^5$  switching cycles. This level of stability has not been reported for the TiO<sub>2</sub>-based e-BRS RRAMs, demonstrating the superiority of the AZTA sample to the previous works.<sup>19, 22, 36, 37</sup>

The cell-to-cell and cycle-to-cycle uniformity performance of the ATA and AZTA samples are shown in Figures 2.8 (a) and (b), respectively. Both samples showed high device-to-device uniformity, which corroborates the general expectation that the e-BRS type device would have better uniformity than the CF-based ionic RS mechanism device. In contrast, only the AZTA sample exhibited high cycle-to-cycle uniformity in both the  $R_{HRS}$  and  $R_{LRS}$ .

The retention of the ATA and AZTA samples was measured at room temperature and 85°C for up to  $10^5$  s, and the results are shown in Figures 2.9 (a) and (b), respectively. The retention characteristic of the RRAM based on the SCLC mechanism is closely related to the electrons de-trapping from the traps by the influence of thermal noise. Because of the electron trapped configuration in LRS, the R<sub>LRS</sub> was generally more prone to increase in its value than the R<sub>HRS</sub>.<sup>19, 22, <sup>25</sup> This was also the case in this work, especially at 85°C, and the tendency was more evident for the ATA sample. The retention</sup> behavior of the HRS for ATA and AZTA sample after different cycling numbers at the temperature of  $85^{\circ}$ C, as shown in Figure 2.10, further confirm the failure of the device is closely related to the trap depth (E<sub>a</sub>). That is, electrons in the trap level closer to the conduction band are more easily to be excited. In addition, the relative resistance ratio in Figure 2.10, normalized to the data at 1 s, decreased by ~ 69 % and ~ 54% for the ATA and AZTA samples, respectively. The improvement could be ascribed to the electron barrier effect of the thin ZrO<sub>2</sub> layer against the carrier detrapping under no bias conditions.

Figure 2.3. Typical e-BRS I-V curves of (a) ATA and (b) AZTA samples at the 1st, 2nd, 5th, 10th, 20th, 50th, and 100th cycles with an Icc of 0.5  $\mu$ A. The arrows and numbers indicate the switching sequences.

Figure 2.4. The I-V curves of the AZTA sample with the different electrode sizes without the  $I_{cc}$ . (b) The electrode area-dependence of LRS and HRS for AZTA sample. Each data point was achieved from 20 cells.

**Figure 2.5.** The endurance test results from the DC I–V sweeps of (a) ATA and (b) AZTA samples, with an Icc of 0.5  $\mu$ A. The AC endurance test results of (c) ATA and (d) AZTA samples from the pulse operation mode. The set and reset pulse conditions of the ATA sample (-2.5 V/20 ms and 2.7 V/20 ms), and AZTA sample (-4 V/20 ms and 5 V/20 ms) were tuned to achieve the best test results. The read voltage was 0.5 V.

Figure 2.6. The resistance state of the AZTA sample with 100  $\mu$ m<sup>2</sup> area after applying different (a) set and (b) reset pulse excitations. The initial HRS is ~ 8 G $\Omega$  for the set process, and the initial LRS is ~ 0.2 G $\Omega$  for the reset process, obtained after applying a -4V/20ms set pulse. The read voltage is 0.5V.

Figure 2.7. The resistance ratio variation of the AZTA samples with different electrode areas after applying set pulses with different pulse lengths when the set pulse amplitude is fixed to -4V.

**Figure 2.8.** The cumulative probability graphs of LRS and HRS for ATA and AZTA samples, respectively. (a) The 20 I-V sweeps from 20 memory cells, and (b) the 20 I-V sweeps from a single memory cell. The Icc is 500nA, and the read voltage is 0.5 V.

**Figure 2.9.** The retention characteristics of HRS, LRS, and resistance ratio were measured at room temperature (grey symbols) and 85°C (color symbols) of (a) ATA and (b) AZTA samples, respectively. The read voltage is 0.5 V.

Figure 2.10. The retention behavior of the HRS for (a) ATA and (b) AZTA samples after different cycling numbers at the temperature of 85 °C.

### 2.3.3. The characteristics test and analysis

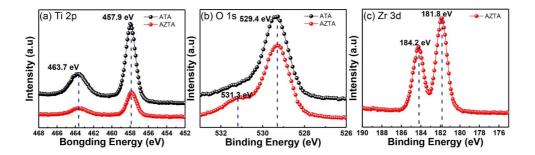

In this section, the scrutinized chemical properties of the ATA and AZTA by XPS are discussed. The Al top electrode was not deposited for this analysis. The XPS binding energy was calibrated with the C-C binding energy of the adventitious C signal (284.6 eV). Figures 2.11 (a) and (b) showed the XPS Ti 2p and O 1s spectra of the  $TiO_2$ film in the ATA and AZTA samples, respectively. There is no significant shift of the Ti 2p peak position between the two samples, meaning that no significant loss of oxygen has occurred in the  $TiO_2$ film after the deposition of the ZrO<sub>2</sub> film. The weaker peak intensity of the AZTA sample was ascribed to the presence of the 1.3nm-thick ZrO<sub>2</sub> layer on top of the TiO<sub>2</sub> layer. The binding energy difference between the Ti 2p 1/2 (463.7 eV) and Ti 2p 3/2 (457.9 eV) peaks was ~ 5.8eV, indicating that the TiO<sub>2</sub> films are fully oxidized for both samples.<sup>38</sup> The O 1s peak corroborates the Ti 2p spectrum. The 529.4 eV binding energy of the O 1s peak from the ATA and AZTA samples showed no shift and is consistent with the reported value for the Ti–O bonding in TiO<sub>2</sub> (529.7 eV). Also, the 531.3 eV binding energy of another O 1s peak from the AZTA sample is consistent with the Zr–O bonding in  $ZrO_2$  (531.2 eV).<sup>39</sup> These results confirm that the TiO<sub>2</sub> layer of the AZTA sample was almost unaffected by the

deposited  $ZrO_2$  layer and maintained its initial oxidized chemical state. Nonetheless, these XPS data do not necessarily imply that the TiO<sub>2</sub> layer had a defect- (or trap-) free property. Sputtered TiO<sub>2</sub> films usually have a V<sub>0</sub> density of 1% or less, which is sufficiently high to induce the e-BRS mechanism but still too low to be detected by XPS. Furthermore, the two peaks of the Zr 3d spectrum of the AZTA sample showed a binding energy difference of 2.4 eV, as shown in Figure 2(c), which corresponds to the Zr<sup>4+</sup> in ZrO<sub>2</sub>, suggesting that the ZrO<sub>2</sub> layer was fully oxidized.<sup>40</sup> Therefore, such a thin, fully oxidized ZrO<sub>2</sub> may play a tunneling barrier role, not the RS layer.

In addition, the cross-section TEM images of the ATA and AZTA sample (10 cycles) were included in Figure 2.12. Both samples show the presence of a ~5nm-thick  $AlO_x$  layer at the bottom interface, which provided the necessary asymmetric barrier for the e-BRS mechanism. Also, the high-resolution TEM image shown in Figure 2.12 (f) revealed the presence of an ~2nm-thick  $ZrO_2$  layer at the top interface of the AZTA sample. At the same time, the STEM-EDS mapping confirmed the presence of the different layers according to the suggested device structures, as shown in Figures 2.13 and 2.14, respectively.

**Figure 2.11.** The XPS spectra of (a) Ti 2p and (b) O 1s of ATA and AZTA samples, respectively. (c) Zr 3d core level XPS spectrum of AZTA sample.

**Figure 2.12.** (a) – (c) The TEM images with the different magnifications of the ATA sample. (d) – (f) The TEM with the different magnifications of the AZTA sample. HRTEM images correspond to the blue square region in low magnification images.

**Figure 2.13.** STEM-EDS mapping analysis of ATA sample: (a) TEM image of the corresponding area; (b) Overlay of Zr-Al-Ti-O; (c) Zr-L; (d) Al-K; (e) Ti-K; (f) O-K.

**Figure 2.14.** STEM-EDS mapping analysis of AZTA sample: (a) TEM image of the corresponding area; (b) Overlay of Zr-Al-Ti-O; (c) Zr-L; (d) Al-K; (e) Ti-K; (f) O-K.

### 2.3.4. Fitting and analysis of degradation mechanism