**Ph.D. Dissertation**

# Design Techniques for Clock Generation and Recovery in Serial Interface

직렬 인터페이스에서 클록 생성 및 복구를 위한 설계 기법

by

Woosong Jung

August, 2023

Department of Electrical and Computer Engineering College of Engineering Seoul National University

# Design Techniques for Clock Generation and Recovery in Serial Interface

지도 교수 정 덕 균

이 논문을 공학박사 학위논문으로 제출함 2023 년 8 월

> 서울대학교 대학원 전기·정보공학부 정 우 송

정우송의 박사 학위논문을 인준함 2023 년 8 월

| 위 육 | <u></u>     | 김 | 재 하             | · (인)      |

|-----|-------------|---|-----------------|------------|

| 부위  | 원장 <u>-</u> | 정 | 덕 균             | . (인)      |

| 위   | 원_          | 모 | - <del>डे</del> | . (인)      |

| 위   | 원           | ネ | 우 석             | (인)        |

| 위   | 원           | 비 | · 관 서           | <u>(인)</u> |

# Design Techniques for Clock Generation and Recovery in Serial Interface

by

Woosong Jung

A Dissertation Submitted to the Department of Electrical and Computer Engineering in Partial Fulfillment of the Requirements for the Degree of Doctor of Philosophy

at

#### SEOUL NATIONAL UNIVERSITY

August, 2023

Committee in Charge:

Professor Jaeha Kim, Chairman

Professor Deog-Kyoon Jeong, Vice-Chairman

Professor Yong Moon

Professor Woo-Seok Choi

Professor Kwanseo Park

## Abstract

This dissertation outlines the clocking system within SerDes and associated common issues. It proposes a phase-locked loop (PLL)-based clock driver for clock generation in the transmitter and clock and data recovery (CDR) in the receiver. The thesis suggests a wide frequency tuning range (FTR) LC resonator for frequency synthesis, which achieves fast frequency acquisition. For reference-less operation, a stochasticbased frequency acquisition scheme is implemented in a Baud-rate CDR. Additionally, this dissertation presents a Baud-rate CDR with a reference clock, which achieves pulse amplitude modulation (PAM)-4 signaling.

Initially, a digital-PLL (DPLL) based clock driver with a wide FTR LC oscillator is presented. The clock driver employs an 8-shaped inductor structure to implement three mode-switchings for wide FTR in one compact area. The analysis demonstrates the compact inductor-stacked layout. Furthermore, the clock driver achieves fast frequency acquisition by using a fast Fourier transform (FFT) algorithm, reducing the lock time significantly compared to the conventional PLL that uses a bang-bang phase and frequency detector (BB-PFD) or time-to-digital converter (TDC). The prototype is fabricated in a 40-nm CMOS technology verifying low-jitter, wide FTR, and fast frequency acquisition. The presented LC oscillator achieves a phase noise of -118.5 dBc/Hz to -124.7 dBc/Hz, achieving the figure of merit (FoM) from FoM<sub>T</sub> from 173.5 dBc/Hz to 181.5 dBc/Hz and 196 dBc/Hz to 204 dBc/Hz, respectively. The clock driver generates a clock frequency ranging from 0.82 to 4.1 GHz, achieving an FTR of 133%. The clock driver achieves a root mean square (RMS) jitter of 84.64 fs at 4 GHz output clock frequency, showing FoM<sub>RMS</sub> of -249.1 dB. Furthermore, the proposed clock driver reduces the settling time requiring only 0.99  $\mu$ s, whereas it requires 2.27 ms in conventional techniques, thus verifying fast frequency acquisition.

The dissertation proposes a reference-less Baud-rate CDR with a stochastic-based phase and frequency detection for the second implementation. It proposes a 14 - 28 Gb/s reference-less Baud-rate CDR that uses a stochastic-based phase and frequency detector (PFD). The PFD with the optimum weight through histogram-based correlation of various data patterns achieves phase and frequency detection. The reference-less Baud-rate CDR utilizes data samples and phase error samples obtained from the integrator. The proposed CDR achieves a data rate of up to 28 Gb/s employing a continuous-time linear equalizer (CTLE) under a 4.7-dB data loss channel at Nyquist frequency. Fabricated in 28-nm CMOS technology, the proposed CDR achieves a bit error rate (BER) of less than 10<sup>-12</sup> and an energy efficiency of 1.06 pJ/b.

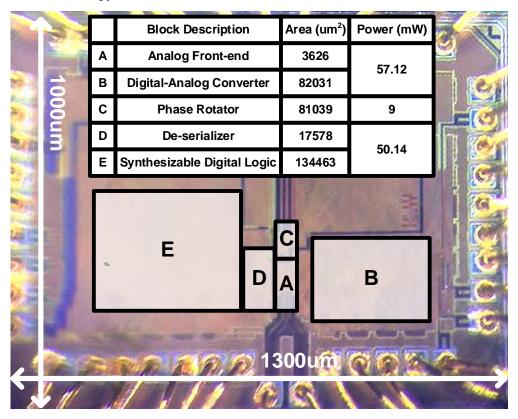

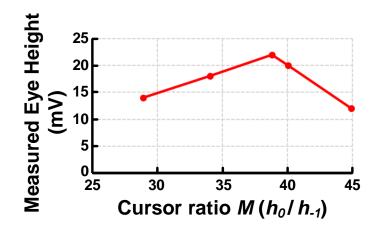

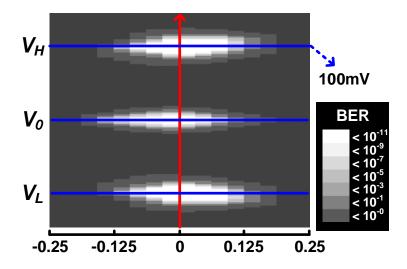

The final embodiment is about a 48 Gb/s PAM-4 receiver with a Baud-rate CDR suitable for multi-level signaling. By deriving the association between the vertical eye margin and the ratio of the main cursor to the pre-cursor, the proposed Baud-rate phase detector (BRPD) adjusts the pre-cursor and finds the lock point with targeted vertical eye-opening. Thus, the BRPD offers a unique lock point when used with an adaptive decision feedback equalizer (DFE) where post-cursor  $h_1$  is removed. Otherwise, the lock point could drift with the conventional Mueller-Müller PD. Furthermore, a summer loading of the DFE reduces the input loading of the DFE by embracing the RZ sampler output instead of the conventional NRZ output adding to the delay associated with an RS latch. A prototype chip fabricated in 40 nm CMOS technology consists of an analog front end, a phase rotator, a current digital-to-analog converter, and

synthesizable digital logic, occupying a total active area of 0.24 mm<sup>2</sup>. The proposed PAM-4 receiver achieves a bit-error rate (BER) of less than 10<sup>-11</sup> at 48 Gb/s and offers an energy efficiency of 2.42 pJ/b.

**Keywords:** Fast Fourier Transform (FFT), 8-shaped inductor, wide frequency tuning range, mode switching, phase-locked loop (PLL), clock driver, fast frequency acquisition, Baud-rate, clock and data recovery (CDR), phase and frequency detector (PFD), reference-less, receiver, stochastic, integrator, adaptive equalizer, decision feedback equalizer (DFE), merged-summer, Mueller-Müller PD, PAM-4, a phase detector (PD), pre-cursor.

Student Number: 2019-29990

# Contents

| ABS' | TRACT    |                           | Ι   |

|------|----------|---------------------------|-----|

| CON  | TENTS    |                           | IV  |

| LIST | T OF FIG | JURES                     | VII |

| LIST | T OF TAI | BLES                      | XII |

| СНА  | PTER 1   | INTRODUCTION              | 1   |

|      | 1.1 Мот  | TIVATION                  | 1   |

|      | 1.2 THE  | SIS ORGANIZATION          | 4   |

| СНА  | PTER 2   | BACKGROUNDS               | 5   |

|      | 2.1 CLO  | CKING IN SERIAL INTERFACE | 5   |

|      | 2.2 Phas | SE-LOCKED LOOP            | 8   |

|      | 2.2.1    | PLL FUNDAMENTALS          | 8   |

|      | 2.2.2    | TYPES OF OSCILLATORS      |     |

|      | 2.2.3    | CHALLENGES OF OSCILLATORS |     |

|      | 2.3 CLO  | CK AND DATA RECOVERY      | 16  |

|      | 2.3.1    | RECEIVER FUNDAMENTALS     | 16  |

|      | 2.3.2    | TYPES OF CDR              | 17  |

|      | 2.3.3    | TYPES OF PD               |     |

|      |          |                           |     |

#### CHAPTER 3 FAST LOCKING WIDE TUNING RANGE DPLL-BASED

| CLO | CK DRI   | VER                                                   | 23 |

|-----|----------|-------------------------------------------------------|----|

|     | 3.1 Ove  | RVIEW                                                 | 23 |

|     | 3.2 WID  | E TUNING RANGE LC RESONATOR                           | 26 |

|     | 3.2.1    | COMPACT 8-SHAPED INDUCTOR                             | 26 |

|     | 3.2.2    | TRANSFORMER-BASED MODE-SWITCHING                      | 30 |

|     | 3.3 FFT  | BASED FAST FREQUENCY ACQUISITION                      | 33 |

|     | 3.3.1    | FAST-FOURIER TRANSFORM                                | 33 |

|     | 3.3.2    | PROPOSED FFT-BASED FREQUENCY TUNING                   | 38 |

|     | 3.4 Circ | CUIT IMPLEMENTATION                                   | 15 |

|     | 3.5 MEA  | SUREMENT RESULTS                                      | 50 |

| СНА | PTER 4   | REFERENCE-LESS BAUD-RATE CDR WITH STOCHASTIC          | 1  |

| PHA | SE AND   | FREQUENCY DETECTOR                                    | 56 |

|     | 4.1 OVE  | RVIEW                                                 | 56 |

|     | 4.2 Stoc | CHASTIC BAUD-RATE PHASE AND FREQUENCY DETECTION       | 50 |

|     | 4.2.1    | INTEGRATOR-BASED BAUD-RATE EDGE DETECTION TECHNIQUES. | 50 |

|     | 4.2.2    | METHODOLOGY OF THE STOCHASTIC PHASE AND FREQUENCY     |    |

| DE  | TECTION  | 63                                                    |    |

|     | 4.3 Circ | CUIT IMPLEMENTATION                                   | 74 |

|     | 4.4 MEA  | SUREMENT RESULTS                                      | 78 |

| СНА | PTER 5   | PAM-4 RECEIVER WITH PRE-CURSOR ADJUSTABLE             |    |

| BAU | D-RATE   | PHASE DETECTOR                                        | 81 |

|     | 5.1 Ove  | RVIEW                                                 | 31 |

| 5.2 Pro                   | POSED PHASE ACQUISITION TECHNIQUE                   | 85  |

|---------------------------|-----------------------------------------------------|-----|

| 5.2.1                     | CONCEPT OF PROPOSED BAUD-RATE PHASE DETECTOR        | 85  |

| 5.2.2                     | DATA LEVEL AND DFE ADAPTATION                       | 91  |

| 5.2.3                     | PRE-CURSOR ADJUSTABLE BAUD-RATE PHASE DETECTOR WITH |     |

| MULTI-LEV                 | EL MODULATION SIGNALING                             | 96  |

| 5.3 Circ                  | CUIT IMPLEMENTATION                                 | 100 |

| 5.3.1                     | PROPOSED PAM-4 RECEIVER ARCHITECTURE                | 100 |

| 5.3.2                     | PROPOSED MERGED-SUMMER DFE WITH THE INVERTER-BASED  |     |

| AMPLIFIER                 | 104                                                 |     |

| 5.4 MEA                   | SUREMENT RESULTS                                    | 107 |

| CHAPTER 6 CONCLUSIONS 115 |                                                     |     |

| BIBLIOGRA                 | РНҮ                                                 | 118 |

| 초 록                       |                                                     | 128 |

# **List of Figures**

| Fig. 1.1 The data rate and process scaling over time                      |

|---------------------------------------------------------------------------|

| Fig. 1.2 The data rate of various I/O standards per lane over time2       |

| FIG. 1.3 THE I/O BANDWIDTH PROGRESS OVER TIME                             |

| FIG. 2.1 THE OVERALL ARCHITECTURE OF THE TYPICAL SERDES6                  |

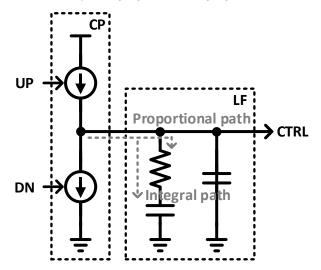

| FIG. 2.2 THE CONVENTIONAL PLL ARCHITECTURE                                |

| FIG. 2.3 CHARGE PUMP AND LOOP FILTER IN THE ANALOG PLL9                   |

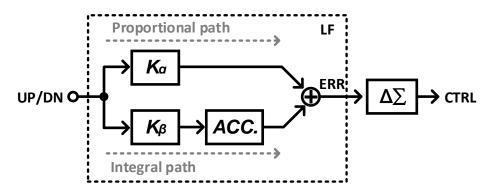

| Fig. 2.4 Loop filter and delta sigma modulator in the digital PLL10 $$    |

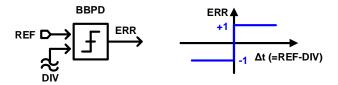

| FIG. 2.5 THE BBPD IMPLEMENTATION AND ITS OUTPUT11                         |

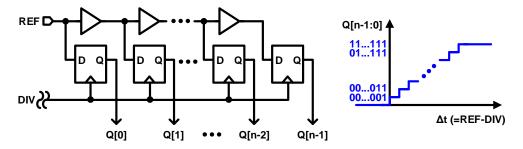

| Fig. 2.6 The time-to-digital converter implementation and its output $11$ |

| FIG. 2.7 SCHEMATIC OF AND INVERTER-BASED RING OSCILLATOR12                |

| FIG. 2.8 SCHEMATIC OF LC OSCILLATOR WITH (A) NMOS-BASED NEGATIVE          |

| RESISTANCE AND (B) CMOS-BASED NEGATIVE RESISTANCE                         |

| FIG. 2.9 THE CONVENTIONAL RECEIVER ARCHITECTURE                           |

| FIG. 2.10 BLOCK DIAGRAM OF REFERENCE CDR ARCHITECTURE: (A) PLL-BASED      |

| CDR AND (B) PI-BASED CDR                                                  |

| FIG. 2.11 BLOCK DIAGRAM OF THE REFERENCE-LESS CDR STRUCTURE               |

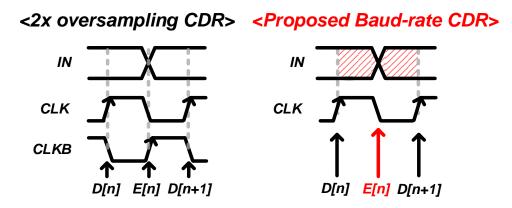

| FIG. 2.12 COMPARISON BETWEEN 2X OVERSAMPLING PD AND BAUD-RATE PD20        |

| FIG. 2.13 HOGGE PHASE DETECTOR AND ITS GAIN CURVE                         |

| FIG. 2.14 ALEXANDER PHASE DETECTOR AND ITS GAIN CURVE                     |

| FIG. 2.15 BAUD-RATE MÜELLER-MÜLLER PHASE DETECTOR AND ITS BLOCK           |

| DIAGRAM                                                                   |

| Fig. 3.1 Overall characteristic: (a) Wide frequency tuning range $LC$      |

|----------------------------------------------------------------------------|

| OSCILLATOR, (B) FAST FREQUENCY ACQUISITION, AND (C) RJ-REDUCTION CLOCK     |

| DRIVER                                                                     |

| FIG. 3.2 8-SHAPED INDUCTOR EMPLOYED FOR PROPOSED LC OSCILLATOR             |

| Fig. 3.3 Impedance response of two LC tanks using stacked inductor: (a)    |

| OCTAGONAL INDUCTOR AND (B) 8-SHAPED INDUCTOR                               |

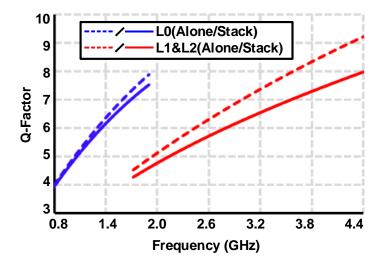

| FIG. 3.4 Q VS FREQUENCY OF THE 8-SHAPED INDUCTORS                          |

| Fig. 3.5 Mode-switching in the proposed LC oscillator: (a) single core     |

| (MODE1), (B) IN-PHASE COUPLING (MODE2), AND (C) OUT-OF-PHASE COUPLING      |

| (MODE3)                                                                    |

| FIG. 3.6 STRUCTURE OF THE BUTTERFLY CELL                                   |

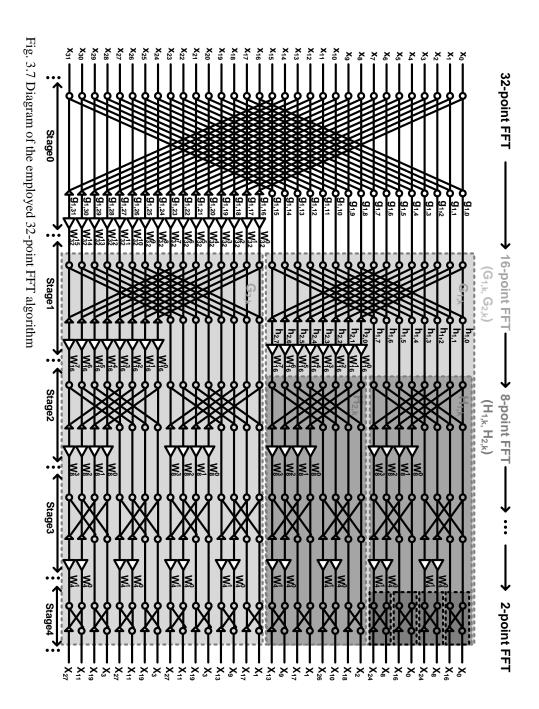

| FIG. 3.7 DIAGRAM OF THE EMPLOYED 32-POINT FFT ALGORITHM                    |

| FIG. 3.8 COMPARISON BETWEEN THE CONVENTIONAL COUNTER-BASED FREQUENCY       |

| ACQUISITION AND PROPOSED FFT-BASED FREQUENCY ACQUISITION AND ITS LOCK TIME |

| DEPENDING ON THE INTEGRAL GAIN                                             |

| FIG. 3.9 FLOW CHART OF FREQUENCY TUNING AND BLOCK DIAGRAM OF THE FFT       |

| TUNING ALGORITHM                                                           |

| FIG. 3.10 PROCUREMENT OF THE 32-POINT FFT INPUT                            |

| FIG. 3.11 THE CHARACTERISTIC OF THE FFT OUTPUT DEPENDING ON THE            |

| CORRELATION BETWEEN INPUT FREQUENCY AND SAMPLING FREQUENCY                 |

| FIG. 3.12 MATRIX CALCULATION TO OBTAIN THE FFT TUNING COEFFICIENT43        |

| FIG. 3.13 OVERALL ARCHITECTURE OF THE PROPOSED DPLL-BASED CLOCK DRIVER     |

|                                                                            |

| FIG. 3.14 CAPACITOR DAC STRUCTURE IN THE LC OSCILLATOR                     |

| FIG. 3.15 THE TIME-TO-DIGITAL CONVERTER STRUCTURE                                                                                                                                                                                                                                                                     |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FIG. 3.16 EMPLOYED PHASE AND FREQUENCY DETECTOR ARCHITECTURE                                                                                                                                                                                                                                                          |

| FIG. 3.17 CHIP PHOTOGRAPH OF THE PROPOSED DPLL-BASED CLOCK DRIVER50                                                                                                                                                                                                                                                   |

| FIG. 3.18 Phase noise of the free-runing LC oscillator at each mode51                                                                                                                                                                                                                                                 |

| Fig. 3.19 PN and FoM and FoM $_{\rm T}$ at each mode depending on the frequency                                                                                                                                                                                                                                       |

|                                                                                                                                                                                                                                                                                                                       |

| Fig. 3.20 Measured integrated RMS jitter W/ and W/O random jitter in the                                                                                                                                                                                                                                              |

| REFERENCE CLOCK                                                                                                                                                                                                                                                                                                       |

| Fig. 3.21 Measured jitter reduction vs jitter magnitude at each mode $\dots 53$                                                                                                                                                                                                                                       |

| Fig. 3.22 Frequency transient curve with the frequency from $3.82 \text{GHz}$ to                                                                                                                                                                                                                                      |

| 4GHz                                                                                                                                                                                                                                                                                                                  |

| Fig. 3.23 Frequency transient curve with the frequency from $3.82 GHz$ to                                                                                                                                                                                                                                             |

| 1GHz                                                                                                                                                                                                                                                                                                                  |

| Fig. 4.1 Sampling type comparison between $2x$ oversampling CDR and                                                                                                                                                                                                                                                   |

|                                                                                                                                                                                                                                                                                                                       |

| PROPOSED BAUD-RATE CDR                                                                                                                                                                                                                                                                                                |

| PROPOSED BAUD-RATE CDR                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                       |

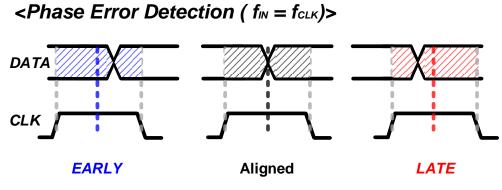

| FIG. 4.2 PROPOSED PHASE DETECTION MECHANISM                                                                                                                                                                                                                                                                           |

| FIG. 4.2 PROPOSED PHASE DETECTION MECHANISM                                                                                                                                                                                                                                                                           |

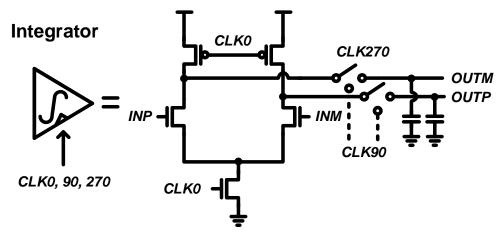

| Fig. 4.2 Proposed Phase detection mechanism       58         Fig. 4.3 Phase error decision table       58         Fig. 4.4 The structure of the exploited integrator       60                                                                                                                                         |

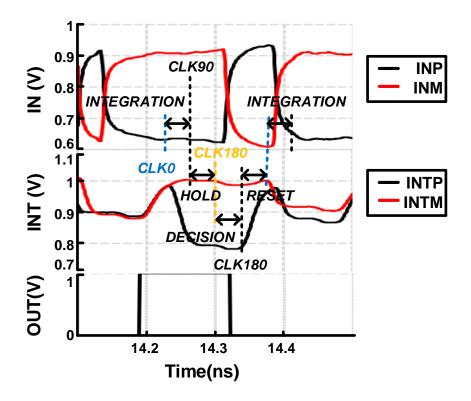

| Fig. 4.2 Proposed Phase detection mechanism       58         Fig. 4.3 Phase error decision table       58         Fig. 4.4 The structure of the exploited integrator       60         Fig. 4.5 The simulation of the integrator       61                                                                              |

| FIG. 4.2 PROPOSED PHASE DETECTION MECHANISM       58         FIG. 4.3 PHASE ERROR DECISION TABLE.       58         FIG. 4.4 THE STRUCTURE OF THE EXPLOITED INTEGRATOR       60         FIG. 4.5 THE SIMULATION OF THE INTEGRATOR       61         FIG. 4.6 PATTERN ACQUISITION IN THE PROPOSED BAUD-RATE CDR       63 |

| FIG. 4.2 PROPOSED PHASE DETECTION MECHANISM58FIG. 4.3 PHASE ERROR DECISION TABLE58FIG. 4.4 THE STRUCTURE OF THE EXPLOITED INTEGRATOR60FIG. 4.5 THE SIMULATION OF THE INTEGRATOR61FIG. 4.6 PATTERN ACQUISITION IN THE PROPOSED BAUD-RATE CDR63FIG. 4.7 OBTAINED PATTERN (A) WHEN PHASE IS EARLY OR LATE AND (B) WHEN   |

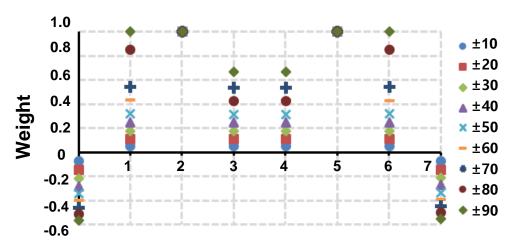

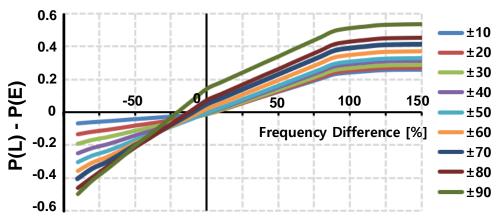

| FIG. 4.11 WEIGHT GAIN CURVE DEPENDING ON THE FREQUENCY DIFFERENCE 69                                     |

|----------------------------------------------------------------------------------------------------------|

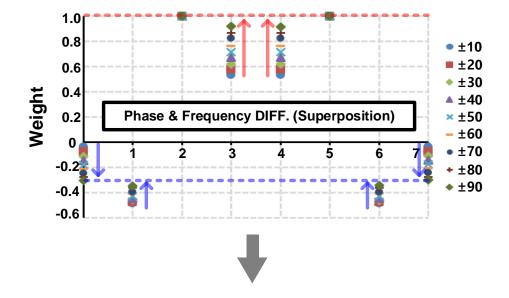

| Fig. 4.11 Frequency gain curve depending on the frequency difference . $69$                              |

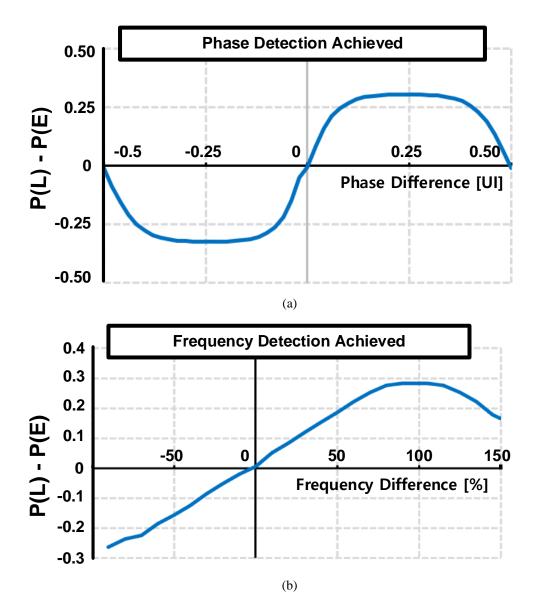

| FIG. 4.12 THE WEIGHT GAIN CURVE DEPENDING ON THE SUPERPOSITION OF PHASE                                  |

| AND FREQUENCY DIFFERENCE AND THE DETERMINED PATTERN WEIGHT VALUE $70$                                    |

| Fig. 4.13 Phase and frequency gain curve when the determined weight is                                   |

| APPLIED TO THE PROPOSED BAUD-RATE PHASE AND FREQUENCY DETECTOR71                                         |

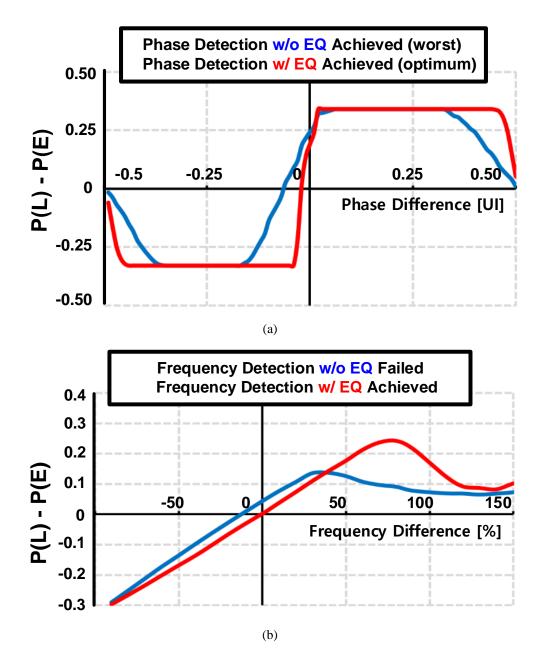

| FIG. 4.14 Phase and frequency gain curve of the proposed PFD with the                                    |

| INPUT DATA PASSED THROUGH LOSSY CHANNEL AND AN EQUALIZATION                                              |

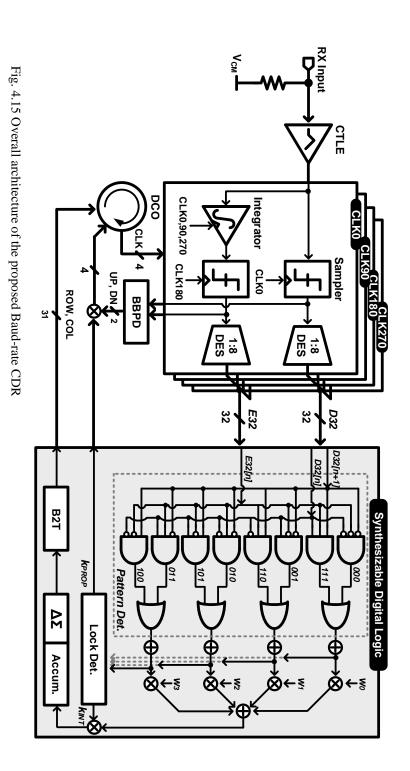

| FIG. 4.15 OVERALL ARCHITECTURE OF THE PROPOSED BAUD-RATE CDR75                                           |

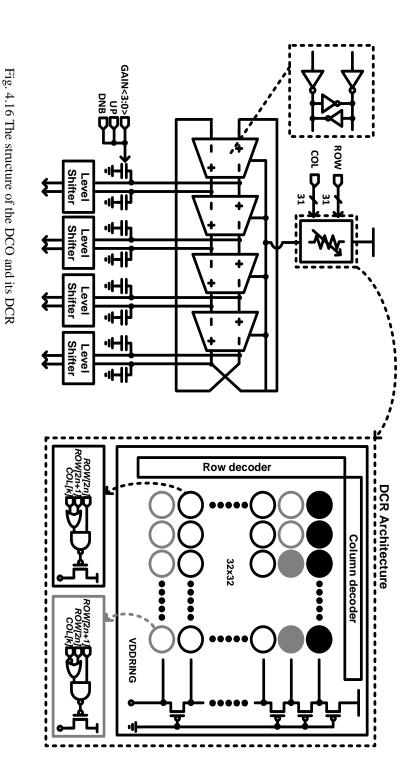

| Fig. 4.16 The structure of the DCO and its DCR76                                                         |

| FIG. 4.17 THE CHIP PHOTOGRAPH AND ITS AREA AND POWER CONSUMPTION                                         |

| Fig. 4.18 Recovered clock histogram                                                                      |

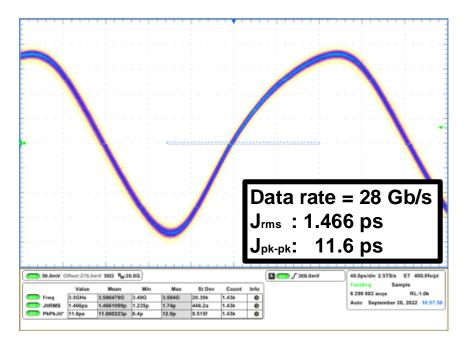

| Fig. 4.19 The measured jitter histogram at 28 GB/s with the $BER{<}10^{{-}12}$ 80                        |

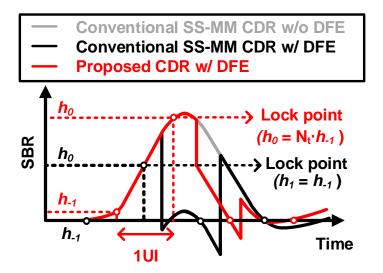

| Fig. 5.1 Lock point of conventional MMPD and proposed MMPD with DFE                                      |

| ON SINGLE-BIT RESPONSE                                                                                   |

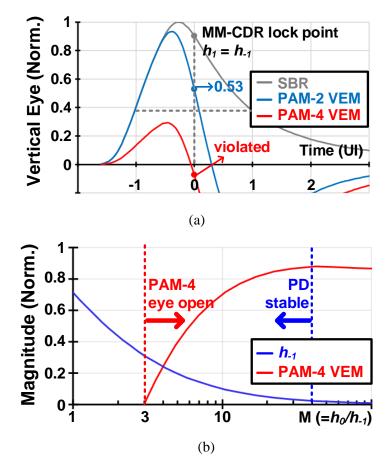

| FIG. 5.2 SIMULATED VERTICAL EYE OPENING OF THE PAM-4 AND PAM-2 SIGNAL                                    |

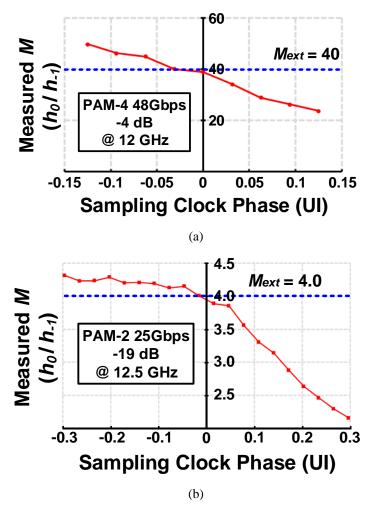

| WITH ACTIVATED DFE VS (A) SAMPLING TIME AND (B) CURSOR RATE $M$ 87                                       |

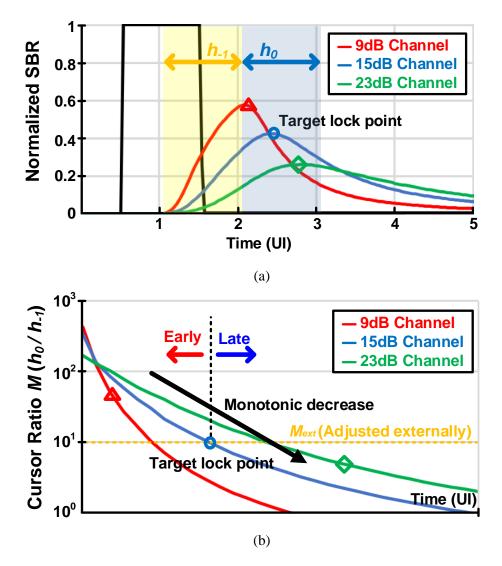

| Fig. 5.3 (a) Simulated single-bit responses and (b) cursor ratio on the                                  |

| TIME WITH VARIOUS CHANNEL LOSSES                                                                         |

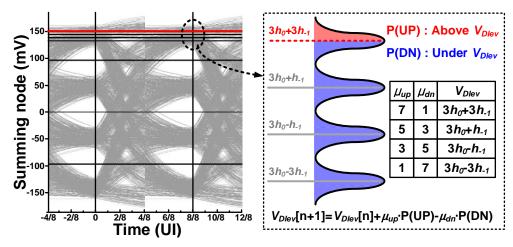

| Fig. 5.4 The eye diagram of the PAM-4 and data histogram for data $+3\ .92$                              |

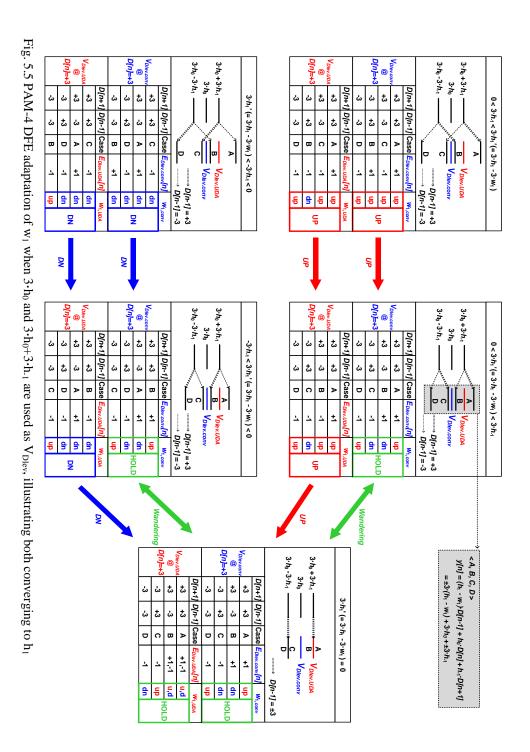

| FIG. 5.5 PAM-4 DFE ADAPTATION OF $W_1$ when $3 \cdot H_0$ and $3 \cdot H_0 + 3 \cdot H_{-1}$ are used as |

| $V_{\text{DLev}}, \text{ILLUSTRATING BOTH CONVERGING TO } H_1 \dots 93$                                  |

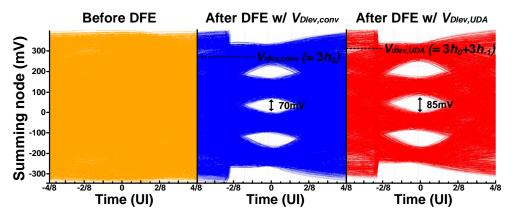

| FIG. 5.6 SIMULATED EYE DIAGRAM WITH CONVENTIONAL DATA LEVEL ADAPTATION                                   |

| AND PROPOSED DATA LEVEL ADAPTATION                                                                       |

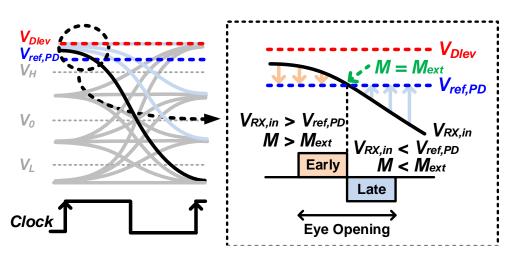

| Fig. 5.7 Generating phase error based on the consecutive data (D[n],         |

|------------------------------------------------------------------------------|

| $D[\text{N}{+}1])$ = (+3, -3) and the sign of the $V_{\text{Ref},\text{PD}}$ |

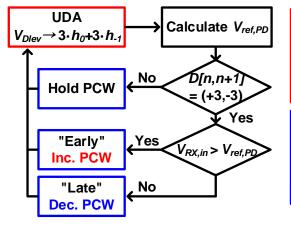

| FIG. 5.8 THE FLOW CHART OF THE PROPOSED MMPD98                               |

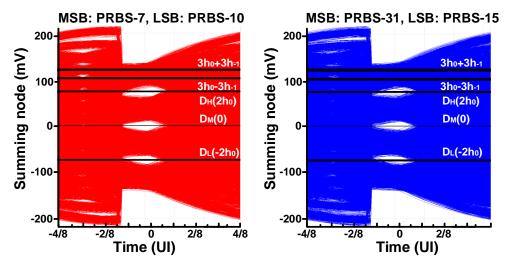

| Fig. 5.9 Simulated eye diagram of the proposed MMPD under two input          |

| DATA CONDITIONS:                                                             |

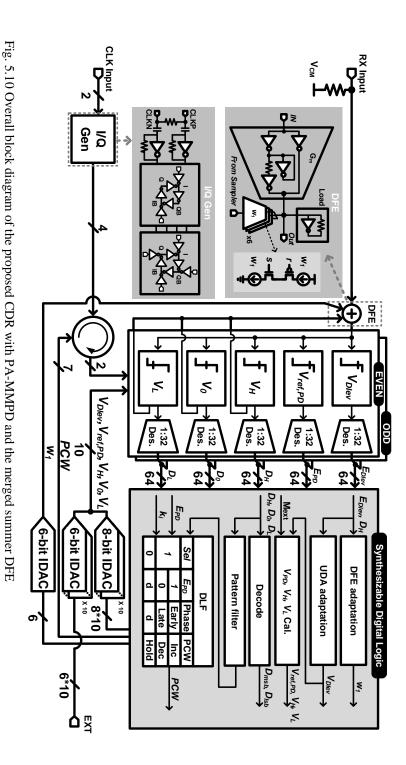

| Fig. 5.10 Overall block diagram of the proposed CDR with PA-MMPD and         |

| THE MERGED SUMMER DFE                                                        |

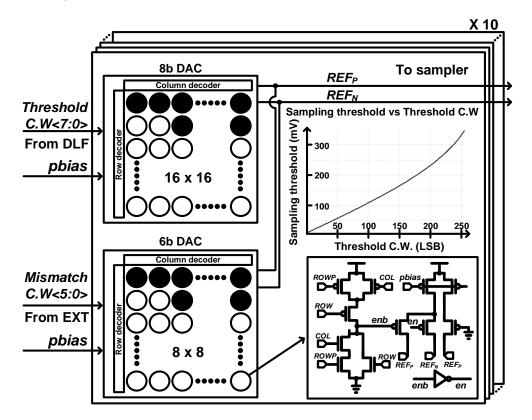

| FIG. 5.11 I-DAC IMPLEMENTATION FOR SAMPLER THRESHOLD VOLTAGE AND             |

| MISMATCH CALIBRATION                                                         |

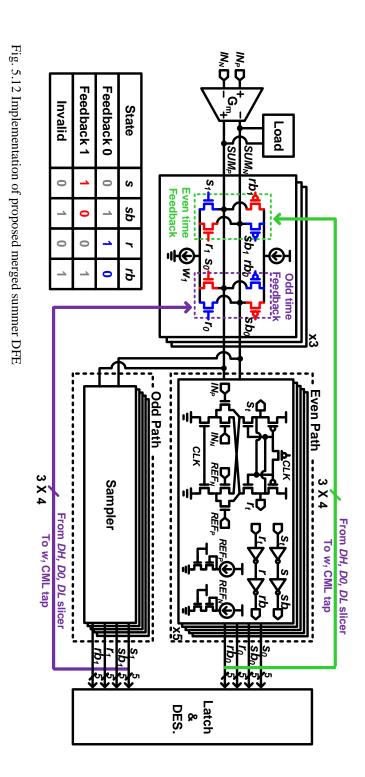

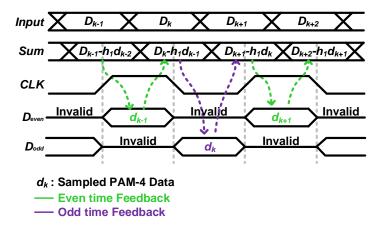

| FIG. 5.12 IMPLEMENTATION OF PROPOSED MERGED SUMMER DFE 105                   |

| FIG. 5.13 TIMING DIAGRAM OF PROPOSED MERGED SUMMER DFE 106                   |

| FIG. 5.14 CHIP PHOTOMICROGRAPH OF THE IMPLEMENTED RECEIVER WITH THE          |

| DETAILED AREA AND                                                            |

| FIG. 5.15 BLOCK DIAGRAM OF THE MEASUREMENT SETUP                             |

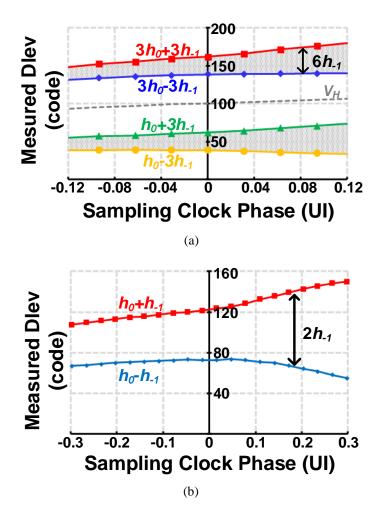

| Fig. 5.16 Measured DLev code vs sampling time in (a) PAM-4 signaling and     |

| (B) PAM-2 SIGNALING                                                          |

| Fig. 5.17 Measured ratio M from measured cursor values in (a) PAM-4          |

| SIGNALING AND (B) PAM-2 SIGNALING                                            |

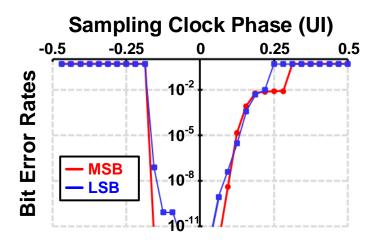

| FIG. 5.18 MEASURED BATHTUB CURVE111                                          |

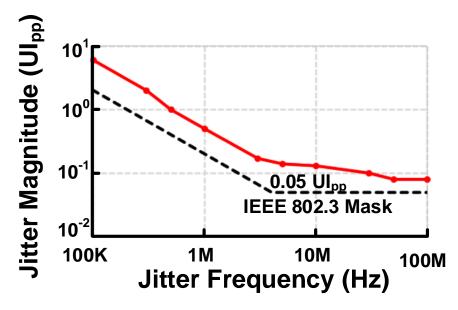

| FIG. 5.19 MEASURED JITTER TOLERANCE AT BER OF 10 <sup>-11</sup>              |

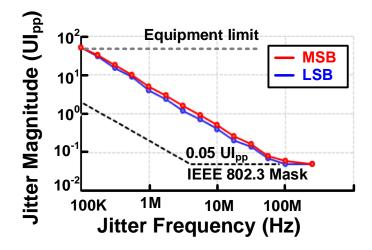

| FIG. 5.20 MEASURED PAM-4 EYE HEIGHT VS CURSOR RATIO M112                     |

| Fig. 5.21 Measured PAM-4 eye diagram with BER $< 10^{-11}$                   |

## **List of Tables**

|    | TABLE I COMPARISON BETWEEN RING OSCILLATOR AND LC OSCILLATOR           | .15  |

|----|------------------------------------------------------------------------|------|

|    | TABLE II COMPARISON TABLE AND PERFORMANCE SUMMARY                      | .55  |

|    | TABLE III THE PATTERN PROBABILITY TABLE WHEN PHASE OR FREQUENCY IS (A) |      |

| EA | ARLY AND (B) LATE                                                      | .65  |

|    | TABLE IV PERFORMANCE SUMMARY AND COMPARISON                            | . 80 |

|    | TABLE V PERFORMANCE SUMMARY AND COMPARISON WITH OTHER DESIGNS          | 114  |

## Chapter 1

## Introduction

### **1.1 Motivation**

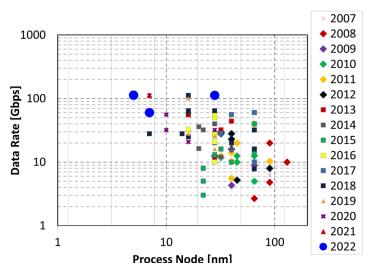

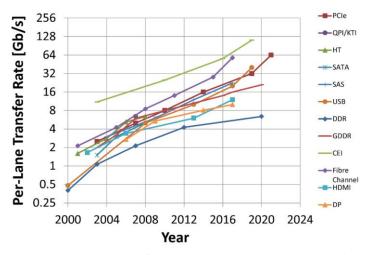

A data center is a physical facility designed to house computer systems and their related components. It plays a critical role in providing IT services and supporting business processes. The rapid growth in data centers and their traffic has led to a corresponding increase in transmission speed [1] - [2]. As illustrated in Fig. 1.1, the process has shrunk over time, and the data rate has gradually increased [3]. Moreover, Fig. 1.2 shows the exponential growth in the data rates per lane for various I/O standards over time [3].

Peripheral Component Interconnect Express (PCIe) is one of the prominent wirelines, doubling every 3-4 years, with a trend accelerating as Fig. 1.3 [4]. The memory interface speed also increases with each generation, with the increasing

Fig. 1.1 The data rate and process scaling over time

Fig. 1.2 The data rate of various I/o standards per lane over time

number of lanes additionally. The demand for data throughput on interfaces is increasing exponentially, leading to the widespread adoption of multilevel signaling such as pulse amplitude modulation (PAM), especially PAM-4, in many standards [5] - [7]. Although PAM signaling can improve data rate significantly, inter-symbol

Fig. 1.3 The I/O bandwidth progress over time

interference (ISI) and signal-to-noise ratio (SNR) of the channel can degrade signal integrity and bit error rate (BER) performance severely.

As the data rate increases, the effect of data loss and noise becomes more significant, reducing the data's timing margins and making the quality of clock signals crucial for the transceiver. In the transmitter, the clock signal is generated and used by the phase-locked loop (PLL), while the clock and data recovery (CDR) regenerates the clock signal with the reference clock or the data only at the receiver.

This paper discusses a PLL-based clock driver that overcomes the limitations of conventional LC oscillators and can obtain a wide frequency tuning range while achieving fast lock times. Additionally, we present a reference CDR and reference-less CDR based on the Baud-rate structure that reduces the requirement on multiphase clock signals and Baud-rate reference CDRs that enable PAM-4 signaling.

### **1.2 Thesis Organization**

This thesis is organized as follows. In Chapter 2, a clocking network used in serial interface is presented briefly. The clocking mechanism within the interface can be categorized into two main components: the PLL and the CDR. The chapter expounds on the underlying principles of PLL, as well as the types of oscillators employed. Additionally, the fundamentals of CDR are elucidated, along with an overview of the various types of CDR and phase detectors (PD) utilized.

Chapter 3 shows the implementation of a fast locking wide tuning range digital PLL (DPLL)-based clock driver. The chapter details an LC oscillator with a wide tuning range that overcomes the limitations of conventional LC oscillators. Additionally, the methodology employed to achieve fast frequency acquisition through fast Fourier transform (FFT) is illustrated.

Chapter 4 describes the implementation of a 28 Gb/s reference-less Baud-rate CDR. In addition, the chapter reveals the stochastic phase and frequency detection techniques and the Baud-rate CDR structure realized by incorporating an integrator.

In Chapter 5, a 48 Gb/s PAM-4 receiver is presented. The receiver design utilizes a reference CDR structure and incorporates a Baud-rate PD that determines the locking position by analyzing the main cursor and pre-cursor ratio. Furthermore, the chapter shows the decision feedback equalization (DFE) adaptation methodology in the PAM-4 structure, verified by the simulation results.

Chapter 6 summarizes the proposed works and concludes this thesis.

## Chapter 2

### **Backgrounds**

### 2.1 Clocking in Serial Interface

Modern wireline communication systems employ serial links over parallel links due to their advantages, such as reduced pin count, increased throughput, etc. Serial links have seen an increase in transmission rate due to the exponential increase in data, and most interface standards have doubled in speed with every generation. For example, the specification for PCIe Gen 6.0, running at 64 GT/s, is advancing to version 7.0, running at 128 GT/s [4]. This increase in speed has led to decreased timing margins and increased design challenges for timing circuits.

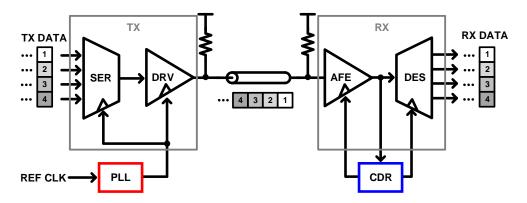

A serial link converts parallel data into serial data for high-speed transmission. As depicted in Fig. 2.1, the parallel data is serialized at the transmitter end and transmitted as serial data through the channel to the receiver end. The received data

Fig. 2.1 The overall architecture of the typical SerDes

are then deserialized back into parallel form for further processing, which is accomplished by using SerDes components.

Clocking in SerDes refers to the generation of a clock signal synchronized to a specified data rate and the architecture of the transmitter and receiver. The transmitter in a serial link synchronizes parallel data by serializing it with a high-frequency clock that is synthesized on-chip from a low-frequency crystal reference clock. On the other hand, the timing circuit on the receiver end has a distinct relationship between the received data and the sampling clock. In such cases, the serial data is parallelized as the receiver's clock samples the data center.

SerDes can be categorized into various structures based on specific viewpoints. One such viewpoint is the presence or absence of a phase relationship and frequency difference between data and clock, which leads to four synchronization types: synchronous, mesochronous, plesiochronous, which is addressed in this thesis, and asynchronous [8]. Additionally, in the multiphase clocking regime, SerDes can be classified into full-rate, half-rate, quadrature, and other sub-rate structures, depending on the number of clock phases used for synchronization [9] – [10].

The clock architectures employed in SerDes significantly impact system performance metrics such as eye height, jitter amount, bit error rate (BER), and jitter tolerance. Therefore, it is necessary to employ an appropriate clock architecture for each application based on its specific requirements.

### 2.2 Phase-Locked Loop

#### 2.2.1 PLL Fundamentals

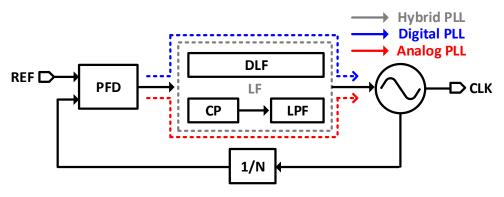

Fig. 2.2 illustrates the block diagram of a conventional PLL. The oscillator output clock signal is divided based on a predetermined division ratio and forwarded to the phase and frequency detector (PFD). The input clock signal is compared to an on-chip or off-chip reference clock in terms of phase and frequency. The phase or frequency error information is fed to the loop filter (LF), which modulates the oscillator frequency, constituting a negative feedback loop to generate the clock at the desired frequency. The output frequency is  $f_{out}=N \cdot f_{ref}$  in a steady state, where N and  $f_{ref}$  represent the division ratio and reference clock frequency, respectively. In the case of integer PLL, the division ratio is an integer N, whereas, in the case of fractional PLL, it becomes a fraction N+ $\alpha$ . The fractional division ratio enables the PLL to achieve a very fine resolution to meet stringent channel requirements in most

Fig. 2.2 The conventional PLL architecture

wireless applications [11] - [13]. However, it requires more complex hardware than an integer PLL and generates additional noise and spurious tones. These characteristics are unsuitable for SerDes, which require strict timing margins, but some require fractional PLLs, such as spread spectrum clocking. Nevertheless, the scope of this dissertation includes only integer PLL

PLL can be classified into three types, and the LF structure in a PLL depends on the type of PLL. In an analog PLL, the LF is implemented as a passive element consisting of a resistor and capacitor combination. In this case, the LF is preceded by the charge pump (CP). Fig. 2.3 shows the LF of a conventional analog PLL. This PLL is based on a 3rd-order type-2 architecture. The resistor in the LF functions as a proportional path, while the capacitor connected in series to the resistor serves as an integral path. Furthermore, a capacitor connected in parallel is used to suppress the ripple caused by the UP/DN current of the CP. The CP adjusts the frequency of the voltagecontrolled oscillator (VCO) by charging or discharging the LF based on the

Fig. 2.3 Charge pump and loop filter in the analog PLL

UP/DN signals from the PD.

On the other hand, in a digital PLL, the resistor and capacitor paths are established using a digital loop filter (DLF) [14] . Additionally, a digitally-controlled oscillator (DCO) is used as the oscillator in DPLLs, which was first introduced by Westlake in 1960 [15] . A delta-sigma modulator (DSM,  $\Delta\Sigma$ ) is commonly employed between the DLF and DCO to effectively suppress the quantization noise of the DCO, dithering the digital control word. The structure of a conventional DLF is presented in Fig. 2.4. K<sub>a</sub> represents the gain of the proportional path, and the gain of the integral path is represented by K<sub>β</sub>. Additionally, an accumulator (ACC) is employed in the integral path of the DLF. The DLF computes the phase and frequency error by processing the UP/DN signals from the PD (PFD). Then, the computed error is transmitted to the DSM for further processing. Finally, the LF of a hybrid PLL combines the LF of analog and digital PLL structures. This thesis focuses on the digital PLL.

DPLLs employ two types of PDs commonly: Bang-Bang PD (BBPD) and time-todigital converter (TDC). Fig. 2.5 illustrates the implementation and output of the

Fig. 2.4 Loop filter and delta sigma modulator in the digital PLL

BBPD, where the phase error (ERR) produced is either 1 or -1 depending on the phase

difference ( $\Delta$ t) between the reference clock and the divided oscillator clock. The structure of the TDC and its phase difference output can be observed in Fig. 2.6. In 2004, Staszewski [16] introduced a TDC to replace analog PFDs in all-digital PLLs (ADPLLs), which effectively reduced quantization error and resulted in low jitter performance. Fig. 2.6 shows how the TDC operates by sampling the reference clock that has been delayed by each inverter stage using the divided oscillator clock. When the phases of the reference clock and the divided oscillator clock delay by each inverter stage, the output of the TDC increments by 1 bit, represented in the thermometer code.

Fig. 2.5 The BBPD implementation and its output

Fig. 2.6 The time-to-digital converter implementation and its output

#### 2.2.2 Types of Oscillators

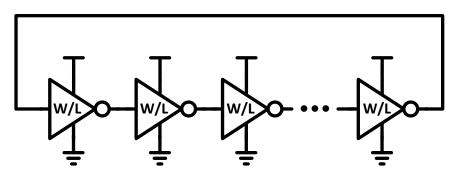

There are two main types of oscillators: Ring Oscillators (RO) and LC Oscillators (LCO). ROs consist of using a sequence of inverter delay cells that are connected in a cascaded way and are phase-shifted by 180 degrees via negative feedback satisfying Barkhausen's criteria. Fig. 2.7 shows the conventional RO structure. The oscillation frequency of RO can be expressed as  $1/(N \cdot T_D)$ , where *N* is the number of stages, and  $T_D$  is the propagation time of delay cells. The load capacitance is determined by the product of the inverter width (*W*) and length (*L*), which is inversely proportional to the oscillation frequency. On the other hand, the driving strength is determined by *W/L*, which is directly proportional to the oscillation frequency. Thus, the oscillation frequency is independent of the inverter width, while the frequency is quadratically increased by reducing the inverter length. However, increasing the inverter width reduces flicker noise and improves phase noise (PN) at the cost of higher power consumption. The common techniques for controlling the frequency of the RO are as follows: adjustment of the supply voltage [18], or regulation of the inverter current [19].

Fig. 2.7 Schematic of and inverter-based ring oscillator

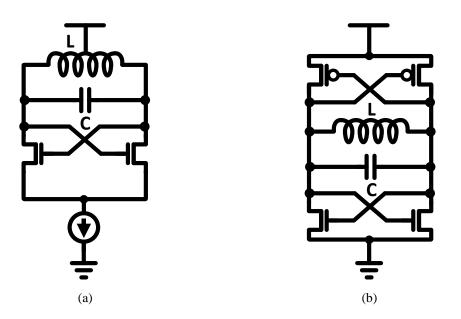

Fig. 2.8 Schematic of LC oscillator with (a) NMOS-based negative resistance and (b) CMOSbased negative resistance

LCO is a resonant circuit composed of passive elements. Fig. 2.8 illustrates the schematics of two conventional LC oscillators. The frequency of LCO is determined by the inductance (*L*) and capacitance (*C*) as  $1/\sqrt{LC}$ . However, due to the difficulty in controlling inductance, the frequency is primarily determined by adjusting capacitance. The quality factor (Q-factor) of an inductor is defined as  $L \cdot \omega/R_s$ , which is inversely dependent on series inductance,  $R_s$ , determining gain and oscillation. For oscillation, NMOS-LCO satisfies a condition as  $R_p - \frac{2}{g_m} \ge 0$ , where  $R_p$  denotes the equivalent parallel resistance of the inductor,  $R_p \approx \frac{L^2 \cdot \omega^2}{R_s} \approx Q^2 \cdot R_s$  [20]. In the case of NMOS-based LCO, as shown in Fig. 2.8(a), the output swing oscillates at the dc level of  $V_{DD}$ , which is the supply voltage, whereas in the case of CMOS-based LCO, as shown in Fig. 2.8(b), it oscillates at the dc level of  $V_{DD}/2$ . As the swing of

NMOS-LCO is twice that of CMOS-LCO, PN is improved by 6dB. However, this improvement comes at the expense of quadrupled power consumption [21]. Additionally, since NMOS-LCO oscillates at the dc level of  $V_{DD}$ , there is a reliability issue, and therefore, a thick gate element is used, increasing parasitic capacitance that limits the tuning range. In contrast, CMOS-LCO offers a wider tuning range by utilizing a thin gate element, and reducing parasitic capacitance thereby.

### 2.2.3 Challenges of Oscillators

RO and LO possess certain advantages and disadvantages. RO provides a wide frequency tuning range (FTR) and facilitates multi-phase generation. Furthermore, RO is implemented in a small area without requiring passive devices. However, they are vulnerable to supply noise and have inferior PN performance compared to LC oscillators.

On the other hand, LCO utilizes the resonance of passive components, rendering them resilient to supply noise and exhibiting superior PN performance. Nevertheless, their reliance on passive components restricts their area, limiting their tuning range. Additionally, it is challenging to generate multiple phases using LC oscillators.

This paper concentrates on LCO that possesses a wide FTR while being implemented in small area, overcoming the limitations of area and tuning range.

|      | Ring Oscillator                                           | LC Oscillator                                                |

|------|-----------------------------------------------------------|--------------------------------------------------------------|

| Pros | Wide tuning range<br>Multi-phase generation<br>Small area | Supply insensitve<br>Superior phase noise                    |

| Cons | Supply sensitive<br>Inferior phase noise                  | Small tuning range<br>Large area<br>Limited phase generation |

Table I Comparison between Ring oscillator and LC oscillator

### **2.3 Clock and Data Recovery**

#### 2.3.1 Receiver Fundamentals

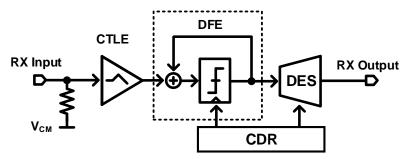

The receiver, based on the plesiochronous clocking architecture as shown in Fig. 2.9, is absent a dedicated clock channel in the transceiver. Instead of a clock forwarding system, the receiver employs a reference clock to generate the sampling clock. However, since the reference clocks in the transmitter and the receiver cannot be perfectly synchronized, a frequency difference between the received data and the sampling clock of the receiver arises, which necessitates a CDR.

Fig. 2.9 illustrates the conventional receiver structure. The equalizer, such as continuous time linear equalizer (CTLE) and DFE, compensates for the channel loss to remove inter-symbol interference (ISI), which allows for accurate sampling of incoming serialized data without errors. The CDR is required to recover the clock signal for synchronization operations such as retiming or deserializing data. The CDR achieves this objective by receiving a reference clock or by extracting the clock signal from the transmitted data.

Fig. 2.9 The conventional receiver architecture

#### 2.3.2 Types of CDR

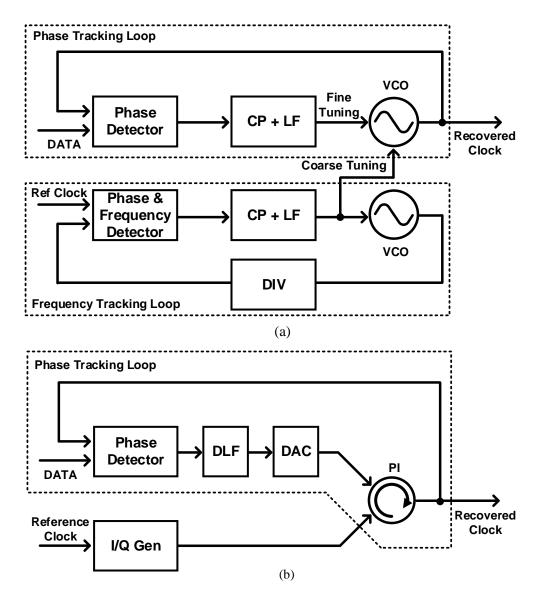

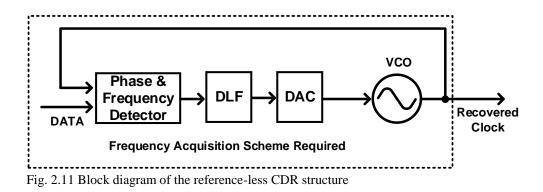

CDR is categorized into two types: reference CDR and reference-less CDR. The conventional block diagrams of these two types are presented in Fig. 2.10 and Fig. 2.11, respectively. Further, the reference CDR is classified into PLL-based CDR and PI-based CDR. The PLL-based CDR comprises two tracking loops, as illustrated in Fig. 2.10 (a). The first loop receives a reference clock, similar to a conventional PLL, and coarsely tracks the frequency. The second loop tracks the phase finely through the output clock and data through the PD, with the clock frequency adjusted by the first loop. Because two loops employ the identical oscillator sharing the frequency control voltage, the mismatch between the two oscillators causes inadequate frequency, which degrades the CDR performance.

On the other hand, the PI-based CDR, as shown in Fig. 2.10 (b), recovers the clock utilizing a high-speed reference clock. First, the I/Q generator receives the reference clock and outputs the multi-phase clock to the phase interpolator (PI). Then, the optimal clock is achieved through the phase tracking loop by processing the data and output clock signal from the PI. Although, compared to the PLL-based CDR, PI-based CDR requires only one tracking loop, reducing circuit complexity and power consumption, it necessitates a high-speed clock signal and more pins increasing the hardware cost.

As shown in Fig. 2.11, the CDR consists of a single loop and operates without a reference clock, resulting in a reduction of the required number of pins. Nonetheless, an additional technique for frequency acquisition is necessary alongside the existing phase detector to achieve clock recovery without a reference clock. To ensure that

Fig. 2.10 Block diagram of reference CDR architecture: (a) PLL-based CDR and (b) PI-based

CDR

clock recovery occurs within the oscillator's frequency range, the system requires a wide capture range performance capable of tracking frequencies at various data rates.

#### 2.3.3 Types of PD

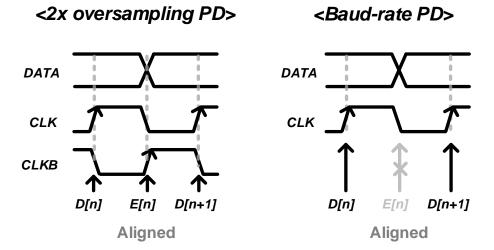

Conventionally, the types of PDs used in CDR can be classified into oversampling PDs and Baud-rate PDs, based on the number of samplings per data. Fig. 2.12 illustrates two commonly used methods, the 2x oversampling and Baud-rate type. In the 2x oversampling method, edge sampling clocks are necessary, in contrast to the Baud-rate structure, which samples data only once. Although twice as many clock phases are required for the additional sampling of data edges, increasing the hardware complexity and power consumption, 2x oversampling obtains more information on frequency and phase errors, facilitating better frequency and phase tracking.

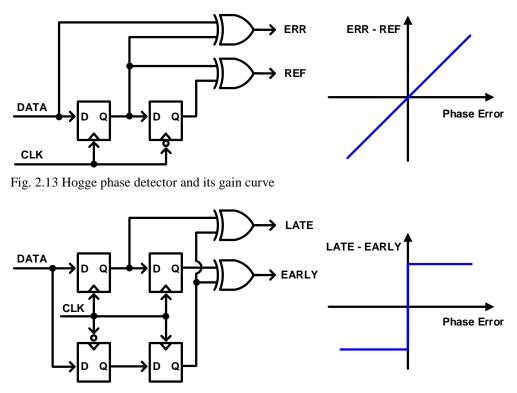

Two commonly used 2x oversampling PDs are linear PD and binary PD. The Hogge PD [22] is an example of a linear PD, and its structure and output are shown in Fig. 2.13. The linear PD generates an output voltage that is proportional to the

Fig. 2.12 Comparison between 2x oversampling PD and Baud-rate PD

Fig. 2.14 Alexander phase detector and its gain curve

phase error, and it comprises two D flip-flops (DFFs) and two XOR logic gates. The Hogge PD outputs a reference pulse (REF) with a constant pulse width and an error pulse (ERR) with a pulse width that is proportional to the phase error (ERR). If the clock is early than the data edge, the pulse width of ERR is less than that of REF, and vice versa if the clock is late.

Fig. 2.14 illustrates the structure and gain curve of the Alexander PD [23], which is an example of a binary PD. Contrary to the linear PD, the binary PD displays the polarity of the phase error, as shown in its gain curve. The Alexander PD consists of four DFFs and two XOR gates. By detecting the transition of the four DFFs as phase error, the Alexander PD is implemented in a more straightforward and powerefficient design than the linear PD. Since The clock signal in Hogge PD and Alexander PD means the edge sampling clock phase, the phase error is the difference between the clock and data edge.

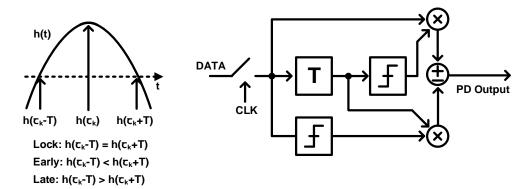

The Baud-rate PD necessitates only one sampling clock per data, which reduces the number of clock phases compared to the 2x oversampling PD. This reduction decreases the cost of clock generation and distribution and can significantly reduce power consumption in clocking. Fig. 2.15 illustrates the operating principle and structure of Mueller-Müller PD (MMPD)[24], a representative example of a Baudrate PD. MMPD achieves locking at the point where  $h(\tau_k - T) = h(\tau_k + T)$ , where h denotes the single-bit response (SBR),  $\tau_k$  is the sampling time, and T represents one data period. If  $h(\tau_k - T) < h(\tau_k + T)$ , the clock is early, and if  $h(\tau_k - T) > h(\tau_k + T)$ , it is considered late. Despite a Baud-rate structure, MMPD implementation requires significant hardware complexity. Thus, for simplicity, signsign MMPD (SS-MMPD) using two binary samples is widely employed [25] -[27].

Fig. 2.15 Baud-rate Müeller-Müller phase detector and its block diagram

# Chapter 3 Fast Locking Wide Tuning Range DPLL-based Clock Driver

### **3.1 Overview**

Owing to the jitter-filtering nature, a PLL often plays as a clock driver in memory systems, filtering out high-frequency noise present in the overall clock distribution path. For LC oscillators, a parallel multi-core topology enhances the output PN but still suffers from a narrow FTR. To overcome this, [28] – [29] employ a mode switching, but the negligible equivalent inductance in the odd mode requires excessively large capacitance for low-frequency oscillation. While the coupling method in [30] also gives a wide FTR, the achievable area efficiency is limited due to the spiral inductor structure. In a DPLL, a wide-range TDC achieves fast frequency acquisition but at the expense of a larger area and power. Although gear-shifting [31] – [33] or digital frequency-error recovery [34] may reduce the lock time without much hard-

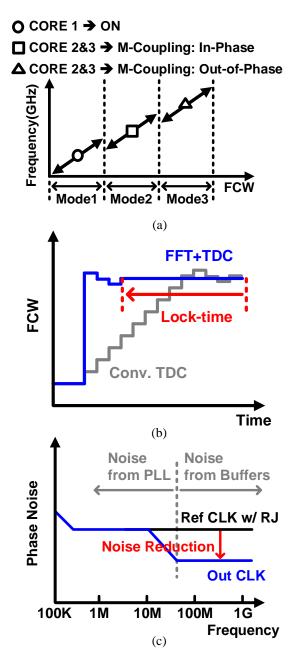

Fig. 3.1 Overall characteristic: (a) Wide frequency tuning range LC oscillator, (b) Fast frequency acquisition, and (c) RJ-reduction clock driver

-ware overhead, an effective method for a wide FTR still remains to be sought.

This work presents a DPLL-based input-jitter-filtering clock driver that achieves 0.99 µs lock time and 133% FTR. Fig. 3.1 shows the overall scheme of the presented clock driver. By using three different modes, the implemented LC oscillator provides an extensive FTR. One standalone LC tank covers the first frequency band (mode1), while two other LC tanks together cover the second and third frequency bands (mode2, mode3), which are mode-switched by conjugating the magnetic coupling thereof. Furthermore, the presented DPLL incorporates an FFT-based frequency acquisition technique, achieving fast frequency lock over a wide FTR. Compared to conventional DPLL, which corporates the TDC, proposed DPLL reduces the lock time significantly by adjusting a frequency control word (FCW) to the near target point. And the proposed DPLL serves as a clock driver. As a clock driver, it reduces high-frequency noise components such as random jitter (RJ), which is caused in a buffer stage.

# **3.2 Wide Tuning Range LC Resonator**

#### **3.2.1** Compact 8-shaped Inductor

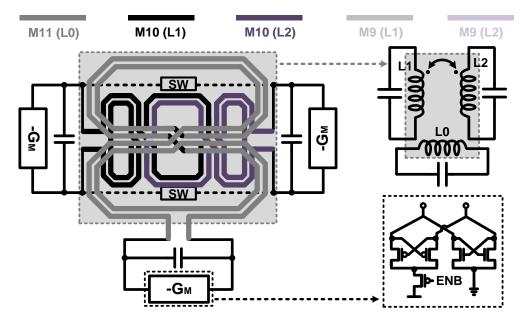

Fig. 3.2 illustrates the implemented LC tanks. The inductor L0, drawn with the top metal, covers mode1. Meanwhile, the two magnetically coupled inductors, L1 and L2, are placed under L0, with a symmetric layout. This transformer-based magnetic coupling offers not only a wide FTR but also an adequate equivalent inductance, being suitable for supporting low-frequency oscillation. To minimize the interference between L0 and L1/L2, each inductor adopts the 8-shaped structure.

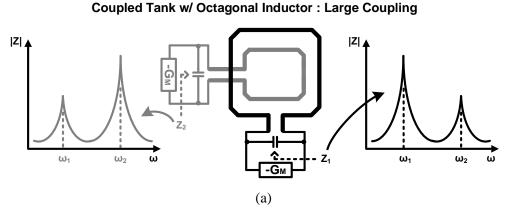

Compared to the conventional octagonal inductor design, the 8-shaped inductor

Fig. 3.2 8-shaped inductor employed for proposed LC oscillator

Coupled Tank w/ 8-Shaped Inductor: Small Coupling

Fig. 3.3 Impedance response of two LC tanks using stacked inductor: (a) Octagonal inductor and (b) 8-shaped inductor

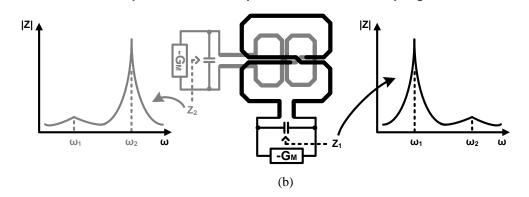

exhibits a lower Q-factor due to its higher resistance to inductance. Despite the lower Q-factor of the 8-shaped inductor compared to the octagonal inductor, it offers a significant advantage when utilized in a stack because of its unique structure that minimizes interference. Fig. 3.3 presents a comparison of the impedance response between an inductor with a conventional octagonal design and one with an 8-shaped design when stacked. When conventional octagonal inductors are stacked as Fig. 3.3 (a), the coupling factor between inductors is significant, resulting in a high peak value at other

resonant frequencies, making it challenging to maintain oscillation in steady-state and leading to PN degradation.

However, the 8-shaped inductor has an upper and lower coil whose directions are opposite, causing the magnetic fields generated in opposite directions in the upper and lower inductors to cancel each other out. Consequently, when 8-shaped inductors are stacked as Fig. 3.3 (b), the coupling is minimal, and the impedance has a slight peak value at other resonant frequencies. This ensures that the two stacked inductors have little influence on each other, allowing for stable oscillation.

Moreover, the stacked 8-shaped inductors generate a stable and high-performance clock signal when compared to existing octagonal inductors. Fig. 3.4 illustrates the Q-factor when the 8-shaped inductor is alone and when arranged in a stacked structure with other inductors. Unlike the octagonal inductor, the coupling is small when the 8-character structure is implemented in a multilayer structure, and the Q-factor is reduced accordingly. Moreover, the negative resistance implemented by a thin-oxide

Fig. 3.4 Q vs frequency of the 8-shaped inductors

CMOS differential pair reduces parasitic capacitance as compared to that of the NMOS-only design with thick-oxide devices.

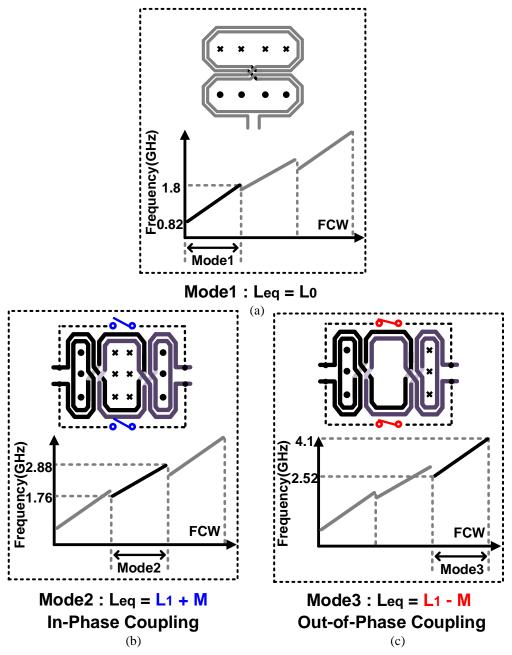

#### 3.2.2 Transformer-based Mode-Switching

Proposed DCO is implemented with mode-switching to enhance FTR. Three modes are available as shown in Fig. 3.5. Mode1 covering the FTR from 0.82 GHz to 1.8 GHz is achieved by LC tank employing inductor L0, described in Fig. 3.2 and in Fig. 3.5 (a). In this mode, the active core with L0 using top metal is turned on while the other active cores are off. The effective inductance at mode0 is,  $L_{eq} = L_0$ .

Mode2 and mode3 are implemented by the transformer-based inductor. In mode2 and mode3, the active cores with L1 and L2 are activated, while the active core with L0 is decommissioned. Through the switches connecting two cores, mode2 and mode3 change. In mode2, the coupled magnetic fields are set to be in-phase, adding the mutual inductance, M, to the equivalent inductance,  $L_{eq}$ . The switches interconnecting the two cores are in the deactivated state, leading to the emergence of a magnetic field oriented in the direction of magnetic field addition, as depicted in Fig. 3.5 (b). The effective inductance at mode2 is,  $L_{eq} = L_1 + M$ . Mode2 achieves a frequency range from 1.76 GHz to 2.88 GHz.

In mode3, the magnetic fields are out-of-phase, canceling out each other, giving a lower value of  $L_{eq}$ . In contrast to mode2, mode3 activates the switches that interconnect the two cores, resulting in the flow of current in a direction that facilitates the cancellation of the magnetic fields. The resulted magnetic field is illustrated in Fig. 3.5 (c). The effective inductance at mode3 is,  $L_{eq} = L_1 - M$ . By employing mode3, it becomes feasible to accomplish a frequency spectrum ranging from 2.52 GHz to 4.1 GHz.

Fig. 3.5 Mode-switching in the proposed LC oscillator: (a) single core (mode1), (b) in-phase coupling (mode2), and (c) out-of-phase coupling (mode3)

L1 and L2 inductors are magnetically coupled to each other, whereby the 1 rotation area of one inductor affects the magnetic field of the other. To reduce the interference of the self-induced magnetic field, the two-turn area of the inductors is implemented to be half the size of the single-turn area. This results in the inductors having a distinctive 8-shaped design, which effectively cancels out the external magnetic field generated by the inductor, improving area efficiency.

## **3.3 FFT-based Fast Frequency Acquisition**

#### 3.3.1 Fast-Fourier Transform

The fundamental principle of Fourier analysis is that all functions are composed of an infinite number of sinusoidal waves. Specifically, our focus lies on discrete functions of finite length. It is possible to represent the function as a sum of sine and cosine waves with different frequencies, and for any such function,  $x_n$ , its frequencies can be entirely represented by another discrete function,  $X_k$ , with an equivalent number of samples. The discrete Fourier transform (DFT) is a widely used transformation technique employed to represent discrete signals in the frequency domain. The N-point DFT is established as

$$X_{k} = \sum_{n=0}^{N-1} x_{n} W_{N}^{nk}, \quad 0 \le k \le N-1, \quad (3.1)$$

where  $X_k$  is the frequency domain,  $x_n$  is the time domain of the sequence, and N denotes the number of samples in  $x_n$ .  $W_N^{nk}$  is the twiddle factor and is represented as

$$W_N^{nk} = e^{-j2\pi nk/N} = \cos(\frac{2\pi nk}{N}) - j\sin(\frac{2\pi nk}{N})$$

(3.2)

The FFT is an efficient algorithm for the computation of the DFT. Through the elimination of redundant calculations, FFT algorithms optimize the DFT. The FFT

algorithm, called the divide and conquer method, follows: The input is split into two halves, each half undergoes an FFT, and the results are combined to form the overall transform. Cooley and Tukey proposed the FFT algorithm to simplify the computational complexity of the DFT, specifically, from N<sup>2</sup> to N/2·log<sub>2</sub>(N/2) multiplications and from N·(N-1) to N·log<sub>2</sub>N additions [35] . We can rewrite (3.1) as follows:

$$X_{k} = \sum_{n=0}^{N/2-1} x_{n} W_{N}^{nk} + \sum_{n=N/2}^{N-1} x_{n} W_{N}^{nk}$$

$$= \sum_{n=0}^{N/2-1} x_{n} W_{N}^{n} + \sum_{n=0}^{N/2-1} x_{n+N/2} W_{N}^{(n+N/2)k} , \quad 0 \le k \le N-1.$$

(3.3)

$$= \sum_{n=0}^{N/2-1} x_{n} W_{N}^{n} + W_{N}^{(N/2)k} \cdot \sum_{n=0}^{N/2-1} x_{n+N/2} W_{N}^{nk}$$

Using the definition of W<sub>N</sub>, the following equation can be derived as,

$$W_N^{(N/2)k} = e^{-j2\pi(N/2)k/N} = e^{-jk\pi} = (-1)^k.$$

(3.4)

With (3.3) and (3.4), we get

$$X_{k} = \sum_{n=0}^{N/2-1} (x_{n} + (-1)^{k} \cdot x_{n+N/2}) \cdot W_{N}^{nk} \quad , \ 0 \le k \le N-1,$$

(3.5)

where  $X_k$  is the N-point DFT of  $x_n$ . The N-point DFT can be divided into two N/2-point DFTs as follows.

$$\begin{cases} X_{2k} = \sum_{n=0}^{N/2-1} (x_n + x_{n+N/2}) \cdot W_{N/2}^{nk} \\ X_{2k+1} = \sum_{n=0}^{N/2-1} ((x_n - x_{n+N/2}) \cdot W_N^n) \cdot W_{N/2}^{nk} \end{cases}, \quad 0 \le k \le (N/2) - 1, \quad (3.6)$$

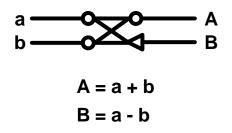

Equation (3.6) shows how a complete transform can be divided into two half-transforms. The aforementioned process can be easily executed by iteratively employing the butterfly structure depicted in Fig. 3.7, from N-point FFT to 2-point FFT. This approach relies on the recursive use of the butterfly structure, which enables the simplification of the overall process.

Fig. 3.6 Structure of the butterfly cell

Fig. 3.7 presents a diagram of the 32-point FFT structure utilized in the proposed DPLL. It can be observed that each stage of the FFT is based on a butterfly cell. The 32-point FFT is decomposed into a 16-point FFT, which is further divided into an 8-point FFT, and eventually a 2-point FFT. Notably, the G(k) and H(k), which are the 16-point and 8-point FFTs respectively, can be expressed as follows:

$$G_{1,k} = X_{2k} = \sum_{n=0}^{15} g_{1,n} \cdot W_{16}^{nk}, \quad 0 \le k \le 15,$$

$$G_{2,k} = X_{2k+1} = \sum_{n=0}^{15} (g_{2,n} \cdot W_{32}^{n}) \cdot W_{16}^{nk}$$

(3.7)

and

$$\begin{cases} H_{1,k} = G_{1,2k} = \sum_{n=0}^{7} h_{1,n} \cdot W_8^{nk} \\ H_{2,k} = G_{1,2k+1} = \sum_{n=0}^{7} (h_{2,n} \cdot W_{16}^n) \cdot W_8^{nk} \end{cases}, \quad 0 \le k \le 7,$$

(3.8)

where  $g_{1,n} = x_n + x_{n+16}$ ,  $g_{2,n} = x_n - x_{n+16}$ ,  $h_{1,n} = g_{1,n} + g_{1,n+8}$ , and  $h_{2,n} = g_{1,n} - g_{1,n+8}$ . As (3.7) and (3.8), the 32-point FFT can be divided into 16-point FFTs and further 8-point FFTs, and 2-point FFTs finally. In other words, a 32-point FFT can be easily implemented based on a 2-point FFT cell.

#### 3.3.2 Proposed FFT-based Frequency Tuning

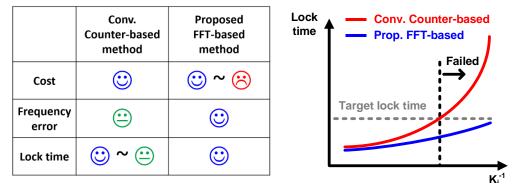

Fig. 3.8 Comparison between the conventional counter-based frequency acquisition and proposed FFT-based frequency acquisition and its lock time depending on the integral gain

Before delving into the explanation of the proposed FFT-based fast frequency calibration, a comparative analysis was conducted, considering three key aspects: hardware cost, frequency error, and lock time. Fig. 3.8 shows the comparison table between the conventional counter-based frequency acquisition and FFT-based frequency acquisition and its frequency acquisition time according to the integral gain of the DLF. The conventional counter-based method offers a straightforward implementation, whereas the adoption of the proposed FFT method may require a significant amount of hardware, depending on the number of FFT points. However, it is worth noting that the conventional counter-based approach. Consequently, the lock time, which denotes the time required to achieve frequency lock, becomes prolonged. In cases where the integral gain is small, as the Fig. 3.8 on the right, it is possible that the required lock time might not be satisfied in the conventional counter-

based method.

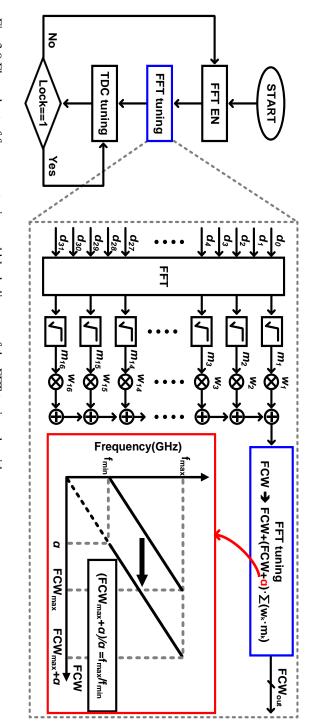

Fig. 3.9 explains the proposed fast-frequency acquisition scheme. Upon initialization, the reference clock samples the divided oscillator clock, whose frequency is given from a certain frequency control word (FCW<sub>lin</sub>), feeding the output sequence to the 32-point FFT module. An adequate division ratio is employed for the FFT to satisfy the Nyquist theorem, thereby preventing aliasing. Although 32-point FFT does not require high hardware complexity, the raw frequency detection resolution obtained by choosing the dominant bin is insufficient for achieving a fast lock. To mitigate this, we utilize the fact that the profile of the sampled signal is known; given that it is always a rectangular pulse with a duty cycle of 50%, there exists a deterministic set of weight coefficients,  $w_k$ , that relates the FFT output bins to the oscillator frequency. Using this, the coarse frequency calibration detects the oscillator frequency with a much higher effective resolution without significantly increasing the hardware overhead. Then, based on a linear model of the frequency tuning curve given from the simulation, the FCW is updated by

$$FCW_{cal} = FCW_{lin} + (FCW_{lin} + \alpha) \cdot \sum_{k=1}^{16} (m_k \cdot w_k)$$

(3.9)

where  $m_k$  is the FFT output bin value. Here,  $\alpha$  is a pre-defined constant that equalizes the full-range ratio of FCW to that of output frequency, i.e.,

$$(FCW_{max} + \alpha)/\alpha = f_{max} / f_{min}, \qquad (3.10)$$

validating the given FCW update for all input frequencies. Since the linearization precedes the calibration, the updated FCW is reverted to the one corresponding to the original mode before being applied to the oscillator. After the coarse FCW calibration by the FFT, the DLF performs fine-tuning through a 7-bit Vernier-delay-line-based TDC having a 2.5 ps resolution. Once the FFT tuning proceeds, the lock detector in the DLF disables the FFT and adjusts the frequency through the TDC loop until the unlock state is recognized. Overall, in comparison with the conventional TDC-DPLL suffering from an excessive hardware cost, the proposed DPLL with the FFT frequency calibration achieves fast frequency acquisition time, retaining good jitter performance.

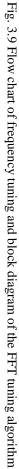

Fig. 3.10 Procurement of the 32-point FFT input

Fig. 3.10 shows the process of acquiring a 32-point FFT input. The input is obtained by sampling the clock, derived from dividing the oscillator by 8, as the reference clock. This division ratio of 8 was chosen to comply with the Nyquist theorem, while taking into account the minimum and maximum frequencies. The code at the reference clock frequency is referred to as  $FCW_{ref}$ , while the code at the current frequency of the oscillator is referred to as FCW<sub>in</sub>. The FCW value is determined based on the linearized model of the implemented oscillator, and the difference between FCW<sub>ref</sub> and FCW<sub>in</sub> is defined as the  $\Delta$ FCW.

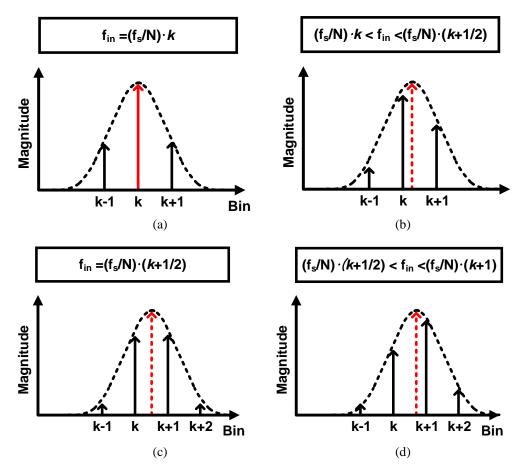

Fig. 3.11 illustrates the FFT output as a function of the sampling frequency and input frequency. In Fig. 3.11 (a), when the input frequency is a multiple of k with respect to the sampling frequency divided by N, the output is shown in a skirt shape

Fig. 3.11 The characteristic of the FFT output depending on the correlation between input frequency and sampling frequency

rather than a single peak value due to the input signal with a pulse shape rather than a sine wave. If the input frequency is greater than this, as shown in Fig. 3.11 (b), and less than (k+1/2) of the sampling frequency/N, the magnitude of the  $k^{th}$  bin decreases while the magnitude of the  $(k+1)^{th}$  bin increases. Fig. 3.11 (c) shows that when the input frequency is a multiple of (k+1/2) of the sampling frequency/N, the bin size of k and k+1 are the largest and output the same value. As the input frequency exceeds this and approaches the (k+1) multiple of the sampling frequency/N, the bin sizes of (k+1) and (k+2) increase while the bin size of k decreases. Thus, depending on the relationship between the input frequency and the sampling frequency, the bins tend to interpolate the two maximum values. By utilizing the interpolation characteristics of these bin values, the frequency can be calibrated by inferring the relationship between the current oscillator frequency and the input frequency using the FFT outputs.

Fig. presents how to calculate the FFT tuning coefficient by using a formula (3.9). To get the desired coefficient,  $w_k$ , we collect samples for the FFT output magnitudes using a  $\Delta_k$  value that's determined by dividing the  $\Delta$ FCW by FCW<sub>in</sub>+ $\alpha$ . By computing the inverse of the matrix shown in Fig. 3.12 using the collected values, we can obtain

$$\begin{bmatrix} \Delta_{1} \\ \Delta_{2} \\ \Delta_{3} \\ \vdots \\ \Delta_{n} \end{bmatrix} = \begin{bmatrix} m_{1,1} & m_{1,2} & m_{1,3} & \circ & \circ & m_{1,16} \\ m_{2,1} & m_{2,2} & m_{2,3} & \circ & \circ & m_{2,16} \\ m_{3,1} & m_{3,2} & m_{3,3} & \circ & \circ & m_{3,16} \\ \vdots & & & & \vdots \\ m_{n,1} & m_{n,2} & m_{n,3} & \circ & \circ & m_{n,16} \end{bmatrix} \bullet \begin{bmatrix} w_{1} \\ w_{2} \\ w_{3} \\ \vdots \\ w_{16} \end{bmatrix} \bullet \begin{bmatrix} w_{1} \\ w_{2} \\ w_{3} \\ \vdots \\ w_{16} \end{bmatrix} = KCW_{in} + (FCW_{in} + \alpha) \cdot \sum (w_{k} \cdot m_{k})$$

Fig. 3.12 Matrix calculation to obtain the FFT tuning coefficient

the value of  $w_k$ . This method allows for FFT-based fast-frequency acquisition.

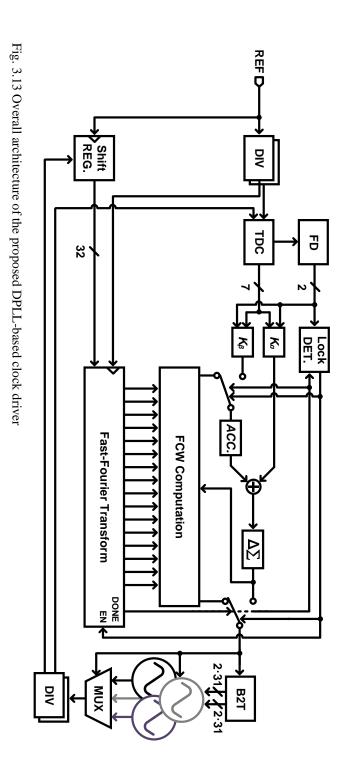

## **3.4 Circuit Implementation**

Fig. 3.13 depicts the proposed DPLL-based clock driver, which features a TDC with FFT-based frequency acquisition and employs three mode-switching LC oscillators to allow for a wide frequency tuning range. The system uses a shift register to obtain a 32-point FFT input and incorporates a lock detector in the DLF to enable FFT-based frequency tuning. The lock detector detects the lock state based on frequency detector outputs such as up and down and decides whether to control the FCW using a conventional TDC-based proportional and integral path or an FFT adjustment.

Moreover, the DLF contains the FCW computation logic that implements frequency calibration by FFT. Before FCW computation, this logic converts the current FCW into an FCW<sub>in</sub> that fits the linearized model. The computation is then performed using the FFT output, after which the FCW<sub>cal</sub> is converted back to the FCW of the original model.

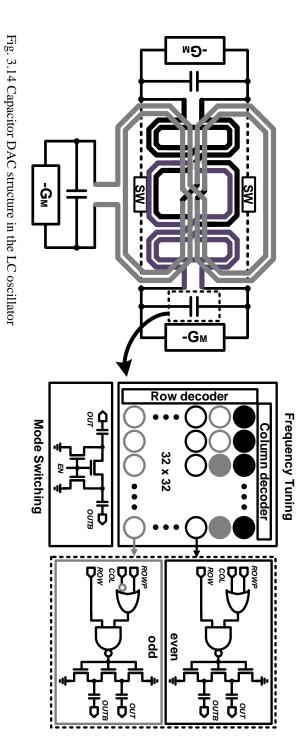

The binary to thermometer (B2T) receives a 10-bit binary code and outputs a 32x32-bit thermometer code to the LC oscillator. In mode1 and mode2, two different 32x32-bit thermometer codes are employed, while mode2 and mode3 share the same cap bank. Fig. 3.14 illustrates the implementation of the cap bank used in the LC oscillator. The cap digital to analog converter (DAC) operates using row 32-bit and column 32-bit inputs from digital logic. In thermometer-based operation, the even and odd rows are designed differently, and a cell is turned on/off based on a 1-bit increase or decrease.

Fig. 3.15 The time-to-digital converter structure

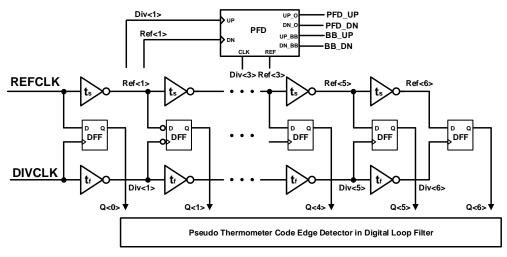

The employed TDC [36] is presented in Fig. 3.15. It is based on a 7-bit Vernierdelay line structure and has a resolution of 2.5 ps as  $t_s - t_f$ , defined as the delay difference between the fast and slow paths. The capture range is determined as follows.

$$3 \cdot (t_f - t_s) \le Capture \le 3 \cdot (t_s - t_f). \tag{3.11}$$

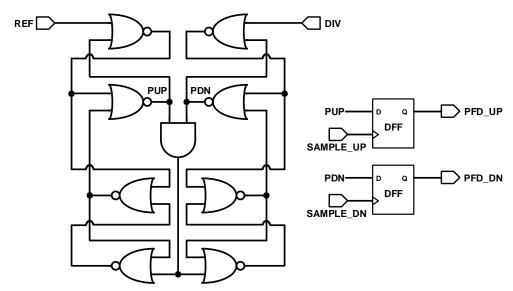

To detect frequency outside of the capture range, PFD generates a down (dn) signal by sampling div<3> with ref<1> and an up signal by sampling ref<3> with div<1>. The implemented structure of the PFD is illustrated in Fig. 3.16. Within the capture range, the signals, ref, and div, up before the ref<1> or div<1> signal is activated. As a result, PUP and PDN are reset, which prevents the generation of PFD\_UP and PFD\_DN.

Fig. 3.16 Employed phase and frequency detector architecture

# **3.5 Measurement Results**

Fig. 3.17 Chip photograph of the proposed DPLL-based clock driver

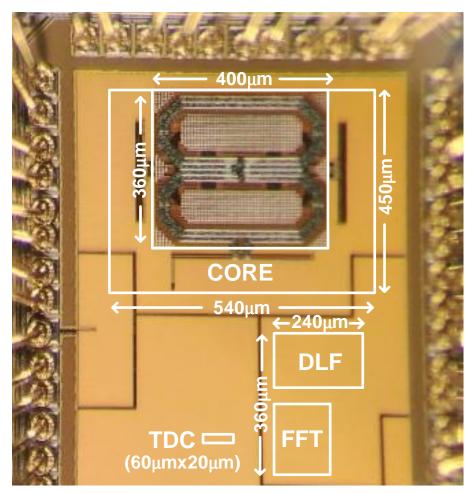

The proposed clock driver, fabricated in 40nm CMOS, generates a clock frequency ranging from 0.82 GHz to 4.1 GHz (FTR=133%). As shown in chip photograph in Fig. 3.17, the core size is 540  $\mu$ m by 450  $\mu$ m, and the total active area

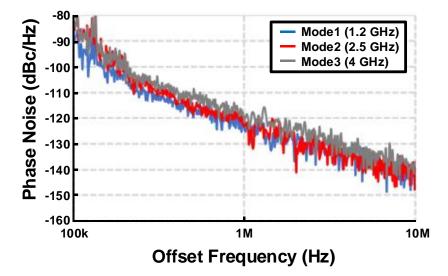

Fig. 3.18 Phase noise of the free-runing LC oscillator at each mode

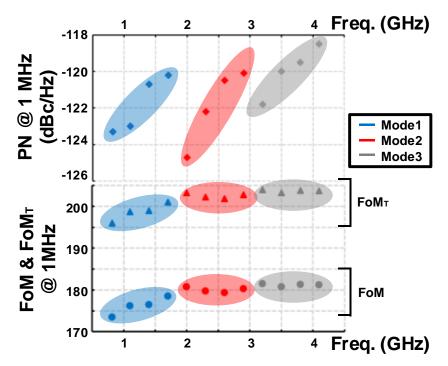

Fig. 3.19 PN and FoM and FoM<sub>T</sub> at each mode depending on the frequency

is 0.3 mm<sup>2</sup>. Implementing a 32-point FFT does not significantly increase hardware complexity.

Fig. 3.18 and Fig. 3.19 present the measured phase noise of the free-running oscillator in the three modes, along with the corresponding FoM and FoM<sub>T</sub> at various frequencies. The phase noise varies from -118.5 dBc/Hz to -124.7 dBc/Hz at 1 MHz offset frequency, achieving FoM and FoM<sub>T</sub> ranging from 173.5 dBc/Hz to 181.5 dBc/Hz and 196 dBc/Hz to 204 dBc/Hz, respectively.

Fig. 3.20 Measured integrated RMS jitter w/ and w/o random jitter in the reference clock

#### Jitter Reduction = 20log(J<sub>RMS,PLL</sub>/J<sub>RMS,REF</sub>)

Fig. 3.21 Measured jitter reduction vs jitter magnitude at each mode

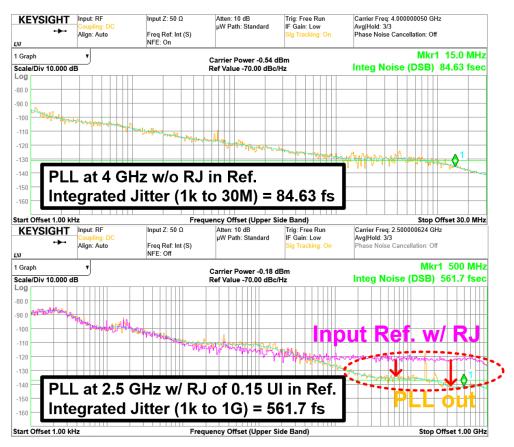

Further, integrated root-mean-square (RMS) jitter is observed in Fig. 3.20. In the absence of a reference clock jitter (RJ), the RMS jitter integrated over a frequency range of 1 kHz to 30 MHz was measured to be 84.63 fs. However, in the presence of a 0.15 unit interval RJ<sub>peak-to-peak</sub> in the reference clock, the RMS jitter integrated over a wider frequency range of 1 kHz to 1 GHz was measured to be 561.7 fs. The plot in Fig. 3.20 shows that the phase noise of the reference signal reduces the high-frequency noise component at the output of the PLL.

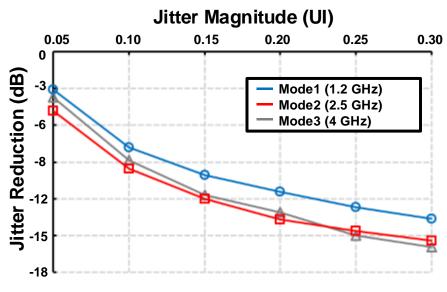

Jitter reduction over the input jitter magnitude present in the reference is observed in Fig. 3.21. Since RJ by clock buffering typically predominates in the highfrequency region, the jitter reduction is evaluated by comparing the integrated RMS jitter from 1 kHz to 1 GHz. Overall, the proposed clock driver offers good nominal jitter performance and significant RJ reduction under a noisy reference clock.

Fig. 3.22 Frequency transient curve with the frequency from 3.82GHz to 4GHz

Fig. 3.23 Frequency transient curve with the frequency from 3.82GHz to 1GHz

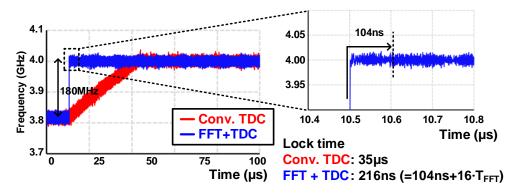

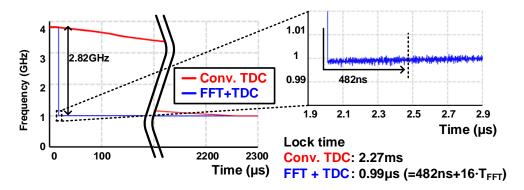

Fig. 3.22 and Fig. 3.23 compare the proposed FFT-DPLL frequency-locking transients with the conventional TDC-DPLL when the frequency jumps from 3.82 GHz to 4 GHz and 3.82 GHz to 1 GHz. It is observed that the frequency acquisition time is significantly reduced regardless of the polarity and magnitude of the frequency jump. With a small frequency jump, the required time for the settlement is measured to be a few hundred nanoseconds. Even with a very large frequency jump from 3.82 GHz to 1 GHz, the DPLL requires only 0.99 µs to settle again, while it takes 2.27 ms without the proposed technique, verifying fast frequency acquisition. Table II summarizes the performance of the proposed clock driver and compares it with other complementary oscillators or fast-locking PLLs. Compared with the oscillators in [28] and [30], the proposed oscillator achieves the widest FTR, showing an outstanding FoM<sub>T</sub>. In addition, the presented work exhibits the shortest frequency tracking time of 0.99  $\mu$ s, notwithstanding a large frequency jump. Lastly, this work gives FoM<sub>RMS</sub> of -249.1dB, validating the outstanding jitter performance.

| Reference                                   |     | This work                | Oscillator Comparison    |                        | PLL Comparison     |                |                     |

|---------------------------------------------|-----|--------------------------|--------------------------|------------------------|--------------------|----------------|---------------------|

|                                             |     |                          | CICC, 21 [26]            | JSSC, 21 [28]          | JSSC, 20 [30]      | ISSCC, 18 [31] | JSSC, 20 [32]       |

| PLL Architecture                            |     | ADPLL                    | N/A                      | N/A                    | BBPLL              | BBPLL          | BBPLL               |

| Technology                                  |     | 40nm                     | 65nm                     | 40nm                   | 28nm               | 65nm           | 28nm                |

| Туре                                        |     | Integer-N                | N/A                      | N/A                    | Integer-N          | Fractional-N   | Fractional-N        |

| Locking Method                              |     | Aux. FFT                 | N/A                      | N/A                    | Aux. BBPD<br>+ GS  | Aux. BBPDs     | Aux. BBPD<br>+ DFER |

| Oscillator Description                      |     | Dual-core<br>Triple-mode | Dual-core<br>Quad-mode   | Quad-core<br>Quad-mode | N/A                | N/A            | N/A                 |

| Ref. Freq. [MHz]                            |     | 1000 ~ 4000              | N/A                      | N/A                    | 216                | 52             | 500                 |

| Out. Freq. [GHz]                            |     | 0.82 ~ 4.1               | 8.2 ~ 21.5               | 18.6 ~ 41.1            | 22.5 ~ 27.7        | 3.7 ~ 4.1      | 12.8 ~ 15.2         |

| Active Area [mm <sup>2</sup> ]              |     | 0.243 / 0.3              | 0.4                      | 0.08                   | 0.017 <sup>†</sup> | 0.5†           | 0.03 <sup>†</sup>   |

| FTR [%]                                     |     | 133                      | 89.6                     | 73.2                   | 20.7               | 10.2           | 17.1                |

| Power [mW]                                  | OSC | 4.3 ~ 11                 | 4 ~ 6                    | 9 ~ 15                 | 13.7               | N/A            | N/A                 |

|                                             | PLL | 17.1                     | N/A                      | N/A                    | 25                 | 5.28           | 19.8                |

| Phase noise [dBc/Hz]<br>@ 1 MHz offset      |     | -118.5~-124.7            | -100 ~ -109 <sup>†</sup> | -108.5 ~ -100.3        | -108.1             | N/A            | N/A                 |

| <sup>1</sup> FoM [dBc/Hz]<br>@ 1 MHz offset |     | 173.5 ~ 181.5            | 177 ~ 181 <sup>†</sup>   | 181.4 ~ 184.4          | -183.8             | N/A            | N/A                 |

| <sup>2</sup> FoM⊤[dB]<br>@ 1 MHz offset     |     | 196 ~ 204                | 196 ~ 201 <sup>†</sup>   | 198.7 ~ 201.7          | -189.8             | N/A            | N/A                 |

| Locking time [µs]                           |     | 0.99                     | N/A                      | N/A                    | 45                 | 5.6            | 18.55               |

| Integration Bandwidth [Hz]                  |     | 1k to 30M                | N/A                      | N/A                    | 10k to 20M         | 1k to 30M      | 1k to 100M          |

| RMS Jitter[fs]                              |     | 84.63                    | N/A                      | N/A                    | 220                | 183            | 66.2                |

| <sup>3</sup> FoM <sub>RMS</sub> [dB]        |     | -249.1                   | N/A                      | N/A                    | -239.2             | -247.5         | -250.6              |

| Reference Spur [dBc]                        |     | -63.1                    | N/A                      | N/A                    | -65                | N/A            | -80.1               |

Table II Comparison table and performance summary

$^{1}$ FoM = |PN| + 20  $\log_{10}(f_{0}/\Delta f)$  - 10  $\log_{10}(Power(mW))$

<sup>†</sup> = Estimated from the literature

$^{2}FoM_{T} = FoM + 20 \cdot log_{10}(FTR/10)$

<sup>3</sup>FoM<sub>RMS</sub> = 10·log[(Power/1mW)·(RMS jitter/1s)<sup>2</sup>]

# Chapter 4 Reference-less Baud-rate CDR with Stochastic Phase and Frequency Detector

# 4.1 Overview

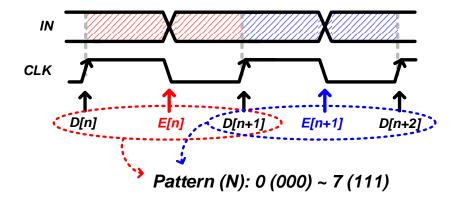

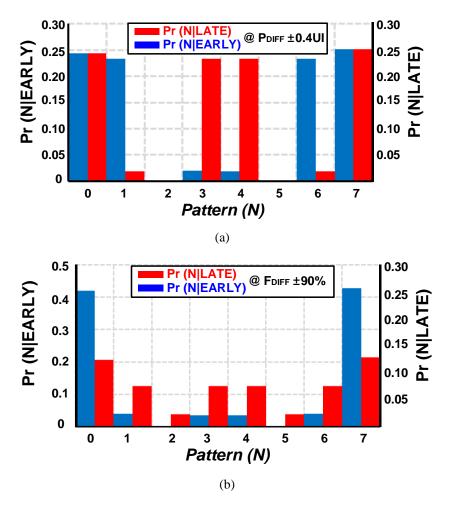

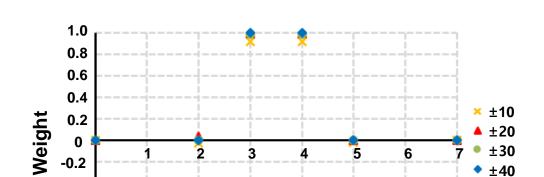

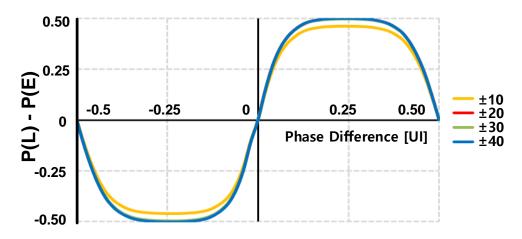

As the data rate increases in the wireline system, CDR accounts for a significant portion of the total power consumption. The commonly employed 2x oversampling CDR samples the data more than once per unit interval (UI), necessitating the generation of a data sampling clock and edge sampling clock [37] - [38]. Fig. 4.1 presents the comparison between the 2x oversampling mechanism and the proposed Baud-rate technique. In the 2x oversampling CDR, the data are sampled on the data clock phase (D[n]) and edge clock phase (E[n]). The phase and frequency errors are determined through D[n] and E[n]. This structure requires a double clock phase and more

Fig. 4.1 Sampling type comparison between 2x oversampling CDR and proposed Baud-rate CDR

sophisticated phase error correction, resulting in large power consumption and frequency limitation.