공학박사 학위논문

## Accelerating Transformer-Based Model Inference using Efficient Matrix Multiplications on GPUs

GPU에서 효율적인 행렬 곱셈을 사용하여 Transformer 기반 모델 추론 가속화 제안

2023년 8월

서울대학교 융합과학기술대학원 융합과학부 지능형융합시스템전공 이 해 룡

### Accelerating Transformer-Based Model Inference using Efficient Matrix Multiplications on GPUs

지도교수 안 정 호 이 논문을 공학박사 학위논문으로 제출함

2023년 07월

서울대학교 융합과학기술대학원

융합과학부 지능형융합시스템전공

이해룡

이해룡의 공학박사 학위 논문을 인준함

2023년 07월

| 위 원 장:               | 이 진 호 | (인) |

|----------------------|-------|-----|

| 부 위원장:               | 안 정 호 | (인) |

| 위 원:                 | 김 동 준 | (인) |

| 위 원:<br>위 원:<br>위 원: | 심 재 웅 | (인) |

| 위 원:                 | 이 석 한 | (인) |

### Abstract

# Accelerating Transformer-Based Model Inference using Efficient Matrix Multiplications on GPUs

Hailong Li Intelligence Systems Department of Transdisciplinary Studies The Graduate School Seoul National University

Transformer-based models have become the backbone of many state-ofthe-art natural language processing (NLP) and computer vision tasks. As existing powerful models become large, enabling the models to learn and represent complex data relationships. Additionally, increasing the input sequence can be an effective way to improve performance for challenging real-world tasks. However, high inference cost hinders the use of powerful transformers because of large memory footprint, quadratic complexity with input sequence length in attention layers, and inefficient kernel operations.

In this thesis, we propose Transformer optimization methods to reduce inference costs in various scenarios, depending on the model size, input sequence length, and batch size. First, we propose Multigrain, an optimization method for scenarios where the input length  $(L_{in})$  is significantly greater than the hidden dimension  $(D_h)$ . Existing sparse attention techniques can effectively reduce computation and memory footprints in long input sequences; however, they are inefficiently processed on GPUs and still account for the majority of the execution time. Multigrain takes into account the sparse patterns of sparse attention, processing the coarse-grained part with a coarse-grained kernel using high-performance tensor cores and the fine-grained part with a fine-grained kernel using CUDA cores, respectively. As a result, Multigrain achieves a 2.07× end-to-end speedup over DeepSpeed when running Longformer inference.

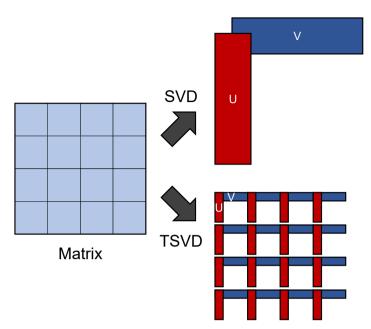

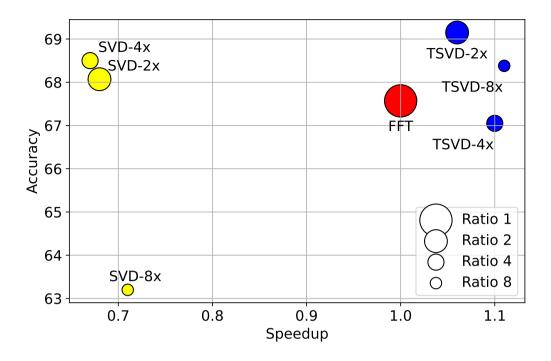

Second, we propose a tiled singular value decomposition (TSVD) method to reduce inference costs in scenarios where  $L_{in}$  is similar to or smaller than  $D_h$ . TSVD is a technique that divides a matrix into tiles, performs singular value decomposition (SVD) on each tile, and compresses the matrix using low-rank approximation. By performing matrix multiplication, the fundamental operation of attention layers and feed-forward layers in Transformer models, using low-rank approximation-based TSVD-matmul, memory footprint and computation can be reduced, significantly lowering inference costs. Consequently, when compressing matrices by 2 to 8×, TSVD-based matrix multiplication is 1.02 to 2.26× faster than the uncompressed matrix multiplication. However, when applying TSVD to models, the execution time is reduced, but there is a trade-off in decreased accuracy.

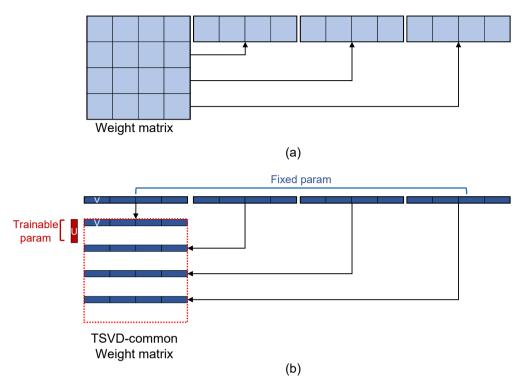

To address this issue, we propose TSVD-common, a parameter-efficient fine-tuning method based on TSVD. TSVD-common shares one of the submatrices decomposed by SVD in each tile across all tiles and fine-tunes only the common submatrix during training. As a result, TSVD-common improves accuracy by approximately 2% even when compressing the GPT-2 model by 2 or  $4 \times$  in E2E NLG tasks, compared to full fine-tuning without compression.

keywords: Transformer acceleration, Model optimization, Sparse attention, Parameter efficient fine-tuning, Model compression student number: 2017-37405

### Contents

| Ał  | ostrac  | t                                                          | i   |

|-----|---------|------------------------------------------------------------|-----|

| Сс  | ontent  | 3                                                          | iv  |

| Lis | st of 7 | <b>Fables</b>                                              | vii |

| Lis | st of I | Figures                                                    | ix  |

| 1   | Intro   | oduction                                                   | 1   |

|     | 1.1     | Accelerating Sparse-Attention-Based Transformer Inference  | 3   |

|     | 1.2     | Accelerating Transformer Inference using Low-Rank Approxi- |     |

|     |         | mation                                                     | 6   |

|     | 1.3     | Research Contributions                                     | 7   |

|     | 1.4     | Outline                                                    | 8   |

| 2   | Back    | zground                                                    | 9   |

|     | 2.1     | Transformer Model                                          | 9   |

|     |         | 2.1.1 Transformer architecture                             | 9   |

|     |         | 2.1.2 Transformer model trends                             | 12  |

|     | 2.2     | Transformer Inference                                      | 13  |

|   | 2.3   | Sparse  | Attention-Based Transformers                           | 16 |

|---|-------|---------|--------------------------------------------------------|----|

|   | 2.4   | Singul  | ar Value Decomposition (SVD)                           | 19 |

|   |       | 2.4.1   | SVD-Based Matrix Multiplication in Transformer models  | 19 |

|   | 2.5   | Param   | eter Efficient Fine-Tuning (PEFT)                      | 21 |

|   | 2.6   | Graph   | ics Processing Unit (GPU)                              | 22 |

| 3 | Mul   | tigrain |                                                        | 24 |

|   | 3.1   | Contr   | ibution                                                | 24 |

|   |       | 3.1.1   | Multigrain mechanism                                   | 24 |

|   |       | 3.1.2   | Coarse-grained GPU kernels                             | 27 |

|   |       | 3.1.3   | Compound sparse softmax GPU kernel                     | 31 |

|   | 3.2   | Evalua  | ation                                                  | 33 |

|   |       | 3.2.1   | Experiment Setup                                       | 33 |

|   |       | 3.2.2   | End-to-End latency on sparse Transformers              | 35 |

|   |       | 3.2.3   | Speedup on the sparse attention                        | 38 |

|   |       | 3.2.4   | Speedup on the sparse softmax                          | 41 |

|   |       | 3.2.5   | Speedup on the coarse-grained kernel                   | 43 |

|   | 3.3   | Relate  | d Work                                                 | 45 |

|   |       | 3.3.1   | Coarse-grained methods                                 | 45 |

|   |       | 3.3.2   | Fine-grained methods                                   | 46 |

| 4 | Tileo | l Singu | lar Value Decomposition (TSVD)                         | 48 |

|   | 4.1   | Contr   | ibution                                                | 48 |

|   |       | 4.1.1   | Tiled Singular Value Decomposition (TSVD)              | 49 |

|   |       | 4.1.2   | TSVD-based matrix multiplication in Transformer models | 51 |

|   |       | 4.1.3   | Kernel Design                                          | 52 |

|    |      | 4.1.4   | TSVD-Common: a PEFT of low-rank approximation .       | 55 |

|----|------|---------|-------------------------------------------------------|----|

|    | 4.2  | Evalua  | ntion                                                 | 57 |

|    |      | 4.2.1   | Experiment Setup                                      | 57 |

|    |      | 4.2.2   | End-to-end latency on various input and output tokens |    |

|    |      |         | for GPT models                                        | 57 |

|    |      | 4.2.3   | TSVD-common accuracy on various cases                 | 64 |

|    | 4.3  | Related | d Work                                                | 67 |

|    |      | 4.3.1   | Model compression                                     | 67 |

|    |      | 4.3.2   | PEFT                                                  | 69 |

| 5  | Con  | clusion |                                                       | 71 |

| RI | EFER | ENCES   |                                                       | 84 |

| 국  | 문초록  | Ę       |                                                       | 85 |

### List of Tables

| 3.1 | Specifications of the GPUs used in the evaluation. *Peak rates |    |

|-----|----------------------------------------------------------------|----|

|     | are based on the GPU's base clock. **Recent GPU architectures  |    |

|     | combine L1 data cache and SMEM functionality into a single     |    |

|     | memory block                                                   | 33 |

- 4.1 Impact of increasing the number of trainable parameters while keeping the compression ratio fixed, by changing the number of shared matrices or tile sizes when applying TSVD-common to GPT-2 medium on WebNLG [22] (In our method name, 'T' denotes tile size, and 'U' denotes the number of shared matrices.) . 64

- 4.3 Impact of the different compression ratio when applying TSVDcommon to GPT-2 medium on WebNLG [22] We set the tile size as 256. ('all' denotes both attention and feedforward part. 'R' represents the compression ratio of the fixed parameter size.) . . 66

# List of Figures

| 1.1 | Various Transformer inference scenarios categorized based on              |    |

|-----|---------------------------------------------------------------------------|----|

|     | factors such as the model size, input sequence length, and batch          |    |

|     | size                                                                      | 2  |

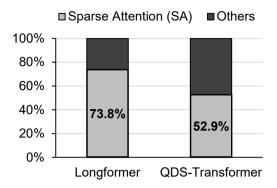

| 1.2 | Execution time breakdown of Longformer, QDS-Transformer                   |    |

|     | on an A100 GPU. Detailed model configurations and tasks are               |    |

|     | described in Section 3.2.1.                                               | 5  |

| 0.1 |                                                                           | 10 |

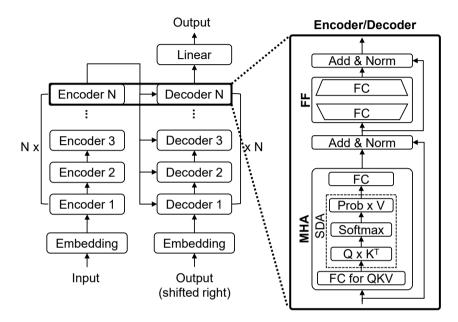

| 2.1 | Transformer architecture                                                  | 10 |

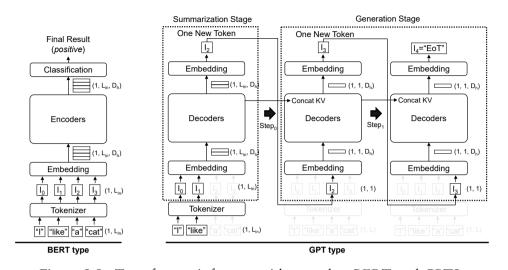

| 2.2 | Transformer inference with regard to BERT and GPT2                        | 14 |

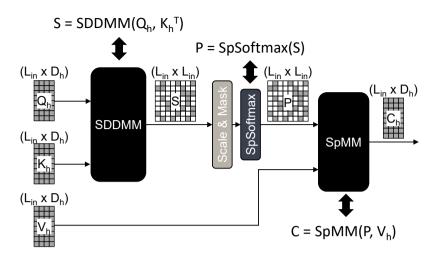

| 2.3 | The sparse attention of a single head in a sparse Transformer. ${\cal S}$ |    |

|     | and $P$ are sparse matrices, and the other matrices are dense. $L_{in}$   |    |

|     | refers to the input sequence length, and $D_h$ represents the head        |    |

|     | dimension of a single head.                                               | 16 |

|     |                                                                           |    |

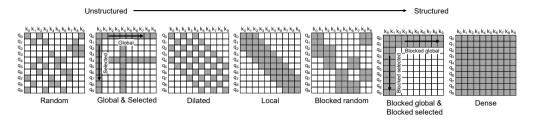

2.4 Various atomic sparse patterns in the existing sparse Transformers. From left to right, the patterns are listed from the least to the most structured pattern. In a sparse pattern, a row refers to the query vector and a column refers to the key vector. Gray squares refer to the valid elements resulting from an inner product of corresponding query and key vectors. Blank squares are invalid elements, and the corresponding query and key vectors are not used for the operations.

18

A Multigrain mechanism. 1) We categorize sparse patterns into 3.1 coarse-grained and fine-grained patterns. 2) we generate the metadata (e.g., row offsets and column indices) for the compressed sparse matrices with the model configuration and positions of the special tokens before inferring the model. 3) In the compound SA, either SDDMM or SpMM is executed through both coarse-grained and fine-grained kernels, processed in parallel using multi-stream. SpSoftmax fused with scaling and masking is processed by a single kernel that can handle coarse-grained and fine-grained results represented by different sparse formats. 25 Hierarchical decomposition of SDDMM with the blocked row 3.2 splitting scheme. 27 3.3 Hierarchical decomposition of SpMM with the blocked one-

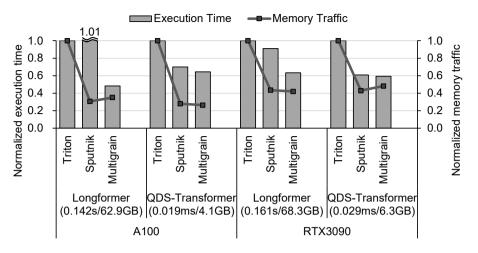

| 3.4 | Execution time and memory traffic of Longformer-large and QDS-    |    |

|-----|-------------------------------------------------------------------|----|

|     | Transformer models by applying Triton, Sputnik, and Multigrain.   |    |

|     | We normalized the other results based on the Triton. The abso-    |    |

|     | lute execution cycle and memory traffic of each baseline is shown |    |

|     | below each model                                                  | 35 |

| 3.5 | Execution time of Longformer-large at the DeepSpeed and Faster-   |    |

|     | Transformer libraries.                                            | 37 |

| 3.6 | Speedup in Longformer-large and QDS-Transformer at the var-       |    |

|     | ious batch sizes by applying Triton, Sputnik, and Multigrain      | 37 |

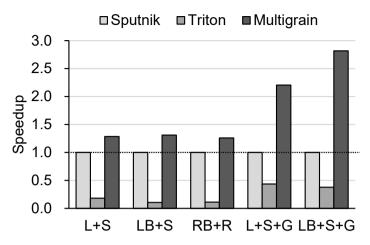

| 3.7 | Speedup of Multigrain compared to Sputnik and Triton in the       |    |

|     | compound-sparse GEMM with various compound sparse pat-            |    |

|     | terns. (L: local, S: selected, G: global, R: random, LB: blocked  |    |

|     | local, and RB: blocked random sparse pattern). Compound-          |    |

|     | sparse GEMMs are sparse operations in the sparse attention (i.e., |    |

|     | SDDMM and SpMM). The operations are processed with pa-            |    |

|     | rameters such as 1 batch size, 4096 input sequence length, 4      |    |

|     | multi-heads, 64 head dimensions, and 95% sparsity in each row.    | 40 |

| 3.8 | Speedup of our compound sparse softmax kernel (Multigrain)        |    |

|     | compared to Sputnik and Triton with various compound-sparse       |    |

|     | patterns in SpSoftmax on A100.                                    | 41 |

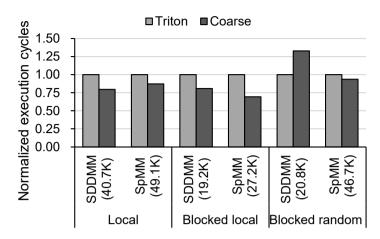

| 3.9  | Execution cycles of SDDMM and SpMM (sequence length=4096,                  |    |

|------|----------------------------------------------------------------------------|----|

|      | batch size=1, number of heads=4, window size=256, window                   |    |

|      | block=3, block size=64, and sparsity=95%) by applying Triton               |    |

|      | and our customized coarse-grained kernel (Coarse). We nor-                 |    |

|      | malize the values based on the execution cycles of Triton. The             |    |

|      | absolute execution cycle of each Triton is shown next to SD-               |    |

|      | DMM and SpMM                                                               | 43 |

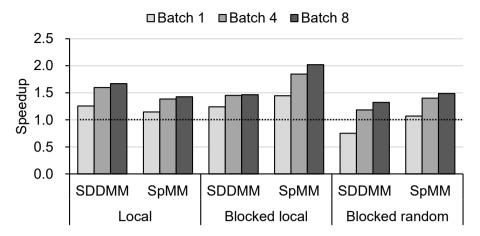

| 3.10 | Speedup of our customized coarse-grained kernel (Coarse) com-              |    |

|      | pared to Triton with various batch sizes on A100                           | 44 |

| 4.1  | Concept of the TSVD, which divides a matrix into smaller tiles             |    |

|      | and factorizes each tile using SVD                                         | 49 |

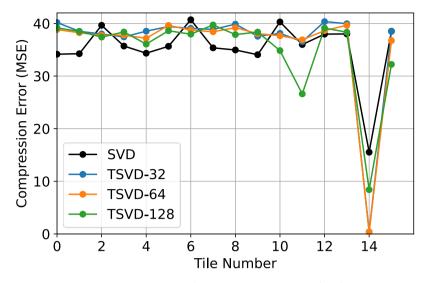

| 4.2  | Compression errors on the various SVD methods at a $2 \times \text{com}^-$ |    |

|      | pression ratio. The compression error is calculated by mean                |    |

|      | square error (MSE) of each tile between recovered matrix after             |    |

|      | compression and original matrix with dimension of (256, 256).              |    |

|      | We randomly set an important tile (e.g., the 14th tile values are          |    |

|      | much larger than other tiles in the matrix), and the size of this          |    |

|      | important tile is (64, 64). As the tile size decreases, TSVD pre-          |    |

|      | serves more important information.                                         | 50 |

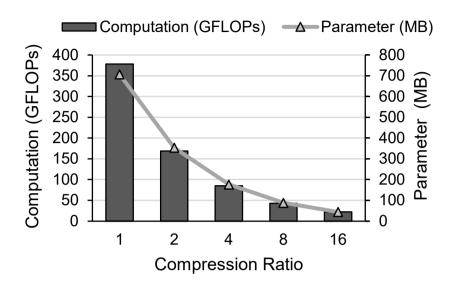

| 4.3 | Total computation and weight parameters in GPT-2 medium              |    |

|-----|----------------------------------------------------------------------|----|

|     | with TSVD as the compression ratio increases. When the com-          |    |

|     | pression ratio is one, the computation and parameters are iden-      |    |

|     | tical to the original GPT-2 medium with 512 input sequences          |    |

|     | and 64 output tokens. These results are calculated by applying       |    |

|     | TSVD to all trainable parameters, such as the embedding table        |    |

|     | and weights in the attention and feedforward                         | 52 |

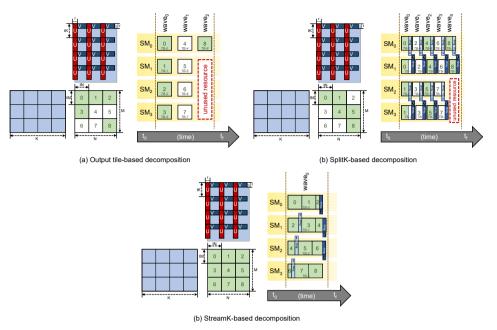

| 4.4 | A various parallel workload decomposition techniques [46] at the     |    |

|     | TSVD-matmul. The green and white blocks in the SMs represent         |    |

|     | output tiles. In the figure (a), the entire output tile 0, allocated |    |

|     | by thread block 0 $(TB_0)$ , is processed on $SM_0$ . The two types  |    |

|     | of blue blocks represent reduction operations for load and store     |    |

|     | from the global memory.                                              | 54 |

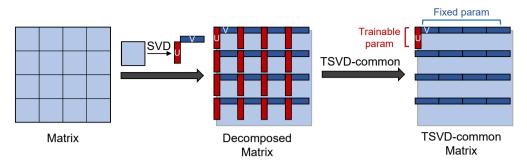

| 4.5 | The concept of the TSVD-common method. It shares one of the          |    |

|     | submatrices decomposed by SVD in each tile across all tiles and      |    |

|     | fine-tunes only the common submatrix (red U) during training.        | 55 |

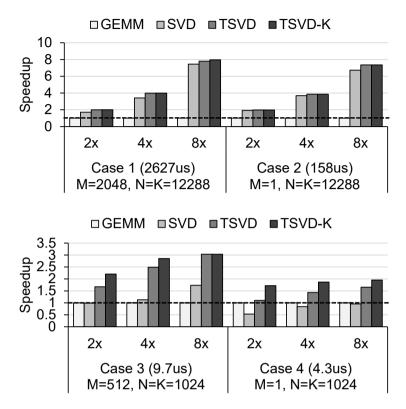

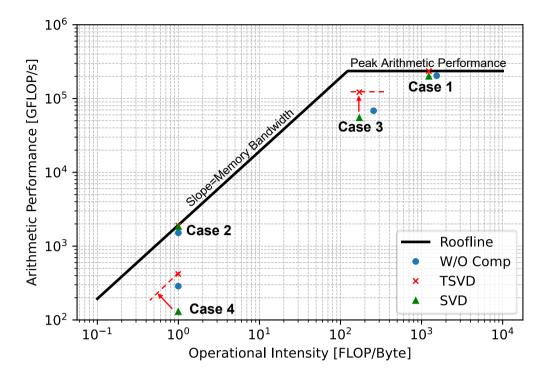

- 4.8 Roofline model for the matrix multiplication in four cases. The performance ceiling is based on the NVIDIA GPU A100 with 80GB HBM achieving up to 1,935GB/s with the base frequency of SM. The blue circles in the figure are matrix multiplications without compression as a baseline in Fig. 4.7 In case 3 and 4, where smaller matrices are involved in the matrix multiplication, TSVD-based matrix multiplications are faster than the other approaches by utilizing more GPU resources. . . . . . . . . 60

59

| 4.10 | ) Tradeoff between accuracy and speedup on A100 GPU. Ratio is      |    |  |

|------|--------------------------------------------------------------------|----|--|

|      | the compression ratio for the weights in GPT2-M except for the     |    |  |

|      | embedding layer. (FFT: full fine-tuning, SVD: singular value       |    |  |

|      | decomposition, TSVD: tiled singular value decomposition)           | 62 |  |

| 4.11 | Differences among Quantization, SVD, and TSVD Methods dur-         |    |  |

|      | ing Matrix Multiplication.                                         | 63 |  |

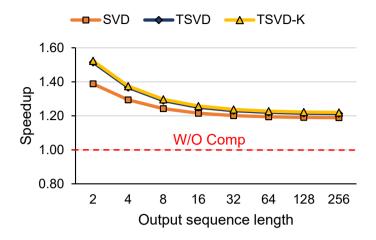

| 4.12 | speedup of the end-to-end execution time in the GPT-2 medium       |    |  |

|      | model as the length of the output sequence increases. The input    |    |  |

|      | sequence length is fixed at 512, and a beam search width of 10 is  |    |  |

|      | used with a single batch size. The red dotted line is our baseline |    |  |

|      | without any compression methods. TSVD is more efficient at         |    |  |

|      | shorter output sequence lengths due to the predominance of the     |    |  |

|      | summarization portion.                                             | 64 |  |

### Chapter 1

### Introduction

The advent of Transformer–based models has catalyzed a revolution in the realms of artificial intelligence and machine learning, particularly in natural lan– guage processing (NLP) [5,15,31,52,61,65] and computer vision [17,35]. These models, due to the power of their Transformer–based structure, can understand and represent complex data relationships by capturing long–range dependencies within the data. Furthermore, expanding the size of these models and the length of their input sequences has shown to significantly enhance their performance, particularly in the execution of complex, real–world tasks [4,5,28,50,67]. These advancements have unlocked the potential for more accurate language transla–tions, more effective sentiment analysis, and more nuanced image recognition, among other applications.

However, deploying Transformer-based models presents certain difficulties. As model sizes increase and input sequences lengthen, inference costs rise proportionately. This is due to a number of factors, including an increased memory footprint, a quadratic complexity associated with input sequence length in attention layers, and the inefficiencies in kernel operations [50]. These challenges act as substantial hurdles, hindering the broader usage of powerful Transformer

This chapter is based on [32].

<sup>&</sup>quot;A Slice and Dice Approach to Accelerate Compound Sparse Attention on GPU" ©2022 by Hailong Li, Jaewan Choi, and Jung Ho Ahn is licensed under CC BY 4.0. https://doi.org/ 10.1109/IISWC55918.2022.00019.

| Seenerie ture                                 |                      | GPT type             |                  |

|-----------------------------------------------|----------------------|----------------------|------------------|

| Scenario type                                 | BERT type            | Summarization        | Generation       |

| Scenario 1: $L_{in} >> D_h$                   | Long input sequence  | Long input sequence  | x                |

| Scenario 2: $L_{in} \approx D_h$              | General case         | General case         | Large batch size |

| Scenario 3: L <sub>in</sub> << D <sub>h</sub> | Short input sequence | Short input sequence | General case     |

L<sub>in</sub>: Input sequence length D<sub>h</sub>: Hidden dimension

Figure 1.1: Various Transformer inference scenarios categorized based on factors such as the model size, input sequence length, and batch size.

models in numerous applications where they could be beneficial.

In this dissertation, we propose Transformer optimization methods to reduce inference costs on graphics processing units (GPUs), which are known for their high-performance capabilities in handling parallel operations. We propose two main strategies for various inference scenarios (see Fig. 1.1), and that these scenarios are categorized according to the model size, input sequence length, and batch size. The first, Multigrain, is designed to optimize a scenario where the input length ( $L_{in}$ ) significantly exceeds the hidden dimension ( $D_h$ ), taking advantage of the unique characteristics of sparse attention patterns. Our second proposal, the tiled singular value decomposition (TSVD) method, is devised for scenarios where  $L_{in}$  is similar to or smaller than  $D_h$ , and focuses on matrix compression to reduce inference costs. Recognizing the potential accuracy trade-off with the inference costs, we also introduce TSVD-common, a parameter efficient fine-tuning method that mitigates this issue.

### 1.1 Accelerating Sparse–Attention–Based Transformer In– ference

In a Transformer-based model, the attention mechanism plays a crucial role in the model's success. The attention mechanism relates different positions of an input sequence to capture contextual information from the entire sequence, representing the long-distance dependency of the model.

Recently, processing long sequences has been gaining interest in NLP research [3,56,57]. For example, scientific literature has 1K – 10K words or even longer in a typical document, and digital humanity books can easily exceed 1K words. Therefore, existing models must deal with long sequences to understand long documents for the tasks such as document classification, multi-hop QA, and reading comprehension. However, early-stage Transformer-based models exhibit unsatisfying accuracies in long-sequence tasks compared to shortsequence tasks [55, 56]. The existing studies [13, 15] segment or shorten long sequences into short sequences during training, which can induce information loss due to the data loss [4]. To tackle such information loss, [4,67] merge short, segmented sequences into one single input sequence to increase the contextual representation. As the sequence length increases, the accuracy of the model is improved.

Long-sequence processing has shortcomings in that its attention operations become expensive as the computation and memory footprint sizes are proportional to  $L_{in}^2$  when the input length is  $L_{in}$ . For  $L_{in} = 4096$ , BERT-large [15] requires a memory size of 64GB, which is equipped only in the most expensive graphics processing units (GPUs). Considering that attention operations

3

have quadratic space and time complexities, attention operations on long input sequences are limited by existing hardware resources.

Recently, sparse Transformer models based on sparse attention (SA) have been actively researched to address these issues. In particular, they perform SA with pre-defined sparse patterns using inductive biases, which reflect the additional assumption of language- and image-data features for accurate prediction. SA exhibits linear complexity, reducing computation and memory footprints. However, SA is processed inefficiently on existing GPUs during inference because the locality of the pre-defined, compound-sparse patterns, which combine multiple atomic sparse patterns,<sup>1</sup> are not considered for processing SA.

More models adopt a compound SA, with the compound-sparse-patternbased SA as the main operation. However, such models only treat the compound SA using either the coarse-grained method based on a blocked sparse format (e.g., block coordinate format (BCOO) and block compressed row format (BSR)) or the fine-grained method based on an element-wise sparse format (e.g., compressed sparse row format (CSR), coordinate format (COO), and compressed sparse column format (CSC)). Only utilizing one of the two methods causes unnecessary computation and memory access and also causes poor data reuse during inference. Also, it is challenging to utilize the highperformance tensor cores in the fine-grained method [9, 34]. From Fig. 1.2, SA takes up significant execution time (73.8% and 52.9% in Longformer [4] and QDS-Transformer [27], respectively). Thus, the compound SA primarily contributes to the end-to-end execution time of the sparse Transformer model during inference.

<sup>&</sup>lt;sup>1</sup>The atomic sparse pattern means a single sparse pattern in a compound-sparse pattern having various sparse patterns.

Figure 1.2: Execution time breakdown of Longformer, QDS-Transformer on an A100 GPU. Detailed model configurations and tasks are described in Section 3.2.1.

In this paper, we propose Multigrain, a compound processing method that accelerates the compound SA on GPUs. We categorize the atomic sparse patterns in the compound sparse patterns into coarse–grained and fine–grained parts by considering the locality of each pattern. Then, we accelerate the compound SA by performing coarse–grained and fine–grained parts with the corresponding kernels separately. To achieve such objectives, we design a customized coarse–grained kernel for the coarse–grained part that utilizes high–performance tensor cores with enhanced data reuse. We use a fine–grained kernel based on an optimized version of the Sputnik library<sup>2</sup> [20] for the fine–grained part to reduce unnecessary computation and memory access. We execute the coarse–grained and fine–grained kernels using multi–stream [36]; hence they can run concurrently in different SMs to utilize the hardware resources better.

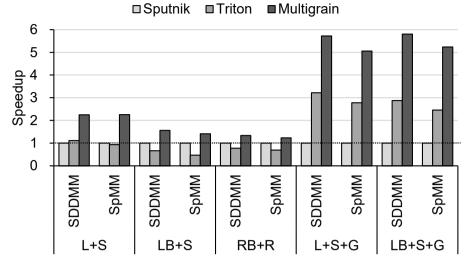

Multigrain outperformed the latest sparse Transformer models such as Longformer and QDS-Transformer up to  $2.08 \times$  and  $1.68 \times$  on the latest GPUs (A100

<sup>&</sup>lt;sup>2</sup>The optimized version of Sputnik used by our fine-grained method will be referred to as Sputnik in the following sections.

and RTX3090). We also evaluated our proposed method in the compound SA with various sparse patterns. We achieved  $1.73 \times -2.34 \times$ ,  $5.06 \times -12.63 \times$ , and  $1.79 \times -3.04 \times$  speedup in the sampled dense-dense matrix multiplication (SD-DMM), sparse softmax (SpSoftmax), and sparse matrix-matrix multiplication (SpMM), respectively, over Triton [58], which only uses the coarse-grained method. Moreover, we achieved  $1.34 \times -5.81 \times$ ,  $1.26 \times -2.82 \times$ , and  $1.23 \times -5.24 \times$  speedup compared to Sputnik, which only uses the fine-grained method.

### 1.2 Accelerating Transformer Inference using Low-Rank Approximation

Transformer-based models have become the backbone of many state-of-theart natural language processing (NLP) tasks, including large language models such as GPT3 [5] and GPT4 [45]. These models employ a self-attention mechanism that allows them to capture long-range dependencies in text, leading to improved performance in various NLP tasks [15,51,61]. Matrix multiplication plays a crucial role in the Transformer models [10, 32, 33, 48]. It accounts for most of the execution time because key operations such as self-attention and feed-forward layers heavily rely on matrix multiplications.

Matrix multiplications often have different computational characteristics with respect to the input sequence length  $(L_{in})$  and hidden dimension  $(D_h)$  in the Transformer-based models. When  $L_{in}$  is similar to or larger than  $D_h$ , the operation is compute-bound, which means that reducing the computation of the operation is crucial for decreasing the execution time. When  $L_{in} \ll D_h$ , the operation is memory-bound, which means that reducing the data size of the input/output matrices can lead to a decrease in execution time [29].

Singular value decomposition (SVD)-based matrix multiplication can accelerate matrix multiplication by reducing the complexity of computation and memory footprint through rank size reduction [47]. Such techniques can influence the result and the execution time of the matrix multiplication depending on the rank size. Compressing Transformer-based models using SVD approach can degrade the model quality, leading to a drop in accuracy [25] even after fine-tuning, due to the difficulty in preserving important information. Moreover, in small models (e.g., GPT2-M [51] and BERT-large [15]), the computing resources of the GPU are not fully utilized, leading to no speedup even at high degrees of compression. Therefore, we propose tiled SVD (TSVD, see Fig. 4.1) approach to mitigate the decrease in accuracy of the Transformer-based model while still achieving speedup.

### 1.3 Research Contributions

- We categorize the Transformer inferences into three scenarios based on model size, input sequence length, and batch size (see Fig. 1.1).

- We perform an analysis of the computational characteristics of the operations in the aforementioned inference scenarios.

- In cases where  $L_{in}$  is much greater than  $D_h$ , we propose a Multigrain solution to accelerate the sparse attention layer.

- When  $L_{in}$  is less than or similar to  $D_h$ , we propose a fast matrix multiplication method based on TSVD with low-rank approximation.

- We design a customized GPU kernel to accelerate the TSVD-based matrix multiplication's speed on a GPU.

- Additionally, we optimize the TSVD-based matrix multiplication using the stream-K method [46].

- We propose a parameter-efficient fine-tuning method, TSVD-common, to improve accuracy.

#### 1.4 Outline

The organization of this dissertation is as follows. Chapter 2: Background provides an understanding of the Transformer model, Transformer inference, sparse attention-based Transformers, singular value decomposition, parameter efficient fine-tuning (PEFT), and graphics processing unit (GPU). Chapter 3: "Multigrain ( $L_{in} \gg D_h$ )" introduces the Multigrain mechanism, elaborates its GPU kernels, and evaluates its effects on Sparse Transformer and Compound Sparse Attention, followed by a review of related work. Chapter 4: "TSVD ( $L_{in} \le D_h$ )" details the tiled singular value decomposition (TSVD), its GPU Kernel, its role in parameter efficient fine-tuning of low-rank approximation, and compares its performance with conventional SVD. Related work in this area is also reviewed. Chapter 5: Conclusion summarizes the research, revisits its contributions, and speculates on the future of the field.

### Chapter 2

### Background

### 2.1 Transformer Model

#### 2.1.1 Transformer architecture

The advent of Transformer models brought a substantial shift in the natural language processing (NLP) and computer vision (CV) domains. Distinguished from their precursors, Transformer models operate without recurrence, enabling greater parallelization.

A vanilla Transformer [61] architecture is composed of an encoder-decoder structure where each part is a stack of identical blocks. Over time, Transformer variant models such as those in the BERT [4, 15, 30] and GPT [2, 5, 45, 59] families have demonstrated superior performance on a variety of tasks.

The BERT family of models, which are comprised exclusively of the encoder part of the vanilla Transformer model, are auto-encoding models that allow each token to attend to all other tokens in its context, regardless of their positions. This enables these models to better capture the contextual relationships among tokens. As a result, these models excel at natural language understand-

This chapter is based on [32].

<sup>&</sup>quot;A Slice and Dice Approach to Accelerate Compound Sparse Attention on GPU" ©2022 by Hailong Li, Jaewan Choi, and Jung Ho Ahn is licensed under CC BY 4.0. https://doi.org/ 10.1109/IISWC55918.2022.00019.

MHA: Multi-Head Attention

FF: Feed-Forward

SDA: Scaled Dot-product Attention

Figure 2.1: Transformer architecture

ing (NLU) tasks such as question answering, sentiment analysis, and reading comprehension.

On the other hand, the GPT family of models, based on the decoder part of the Transformer, are auto-regressive models that predict the next token according to previous tokens. These models exhibit superior generative abilities, making them well-suited for natural language generation (NLG) tasks such as text generation, machine translation, and summarization.

The basic block (e.g., encoder and decoder) in Transformer-based models primarily consists of a multi-head attention layer (MHA) and a feed-forward layer (FF) (see Fig. 2.1). Layer normalization and residual connections are utilized between the MHA and FF to stabilize learning and allow for deeper models. The MHA allows the model to focus on different tokens in the input sequence, thereby enabling a better understanding of the context. In the first encoder/decoder, the MHA receives hidden states ( $L_{in}$ ,  $D_h$ ) generated by the embedding layer and produces an output matrix through the following procedure. In subsequent encoders/decoders, the MHA receives hidden states from the previous FF. Here,  $L_{in}$  denotes the input sequence length, while  $D_h$  represents the hidden vector size of a single token.

Firstly, the MHA utilizes the hidden state as input to prepare the queries (Q), keys (K), and values (V) through fully connected layer (FC). Then, Q, K, and V are split into multiple heads, allowing the attention process to run multiple times in parallel. Secondly, these are used in scaled dot-product attention (SDA) for each head. The SDA computes the dot product of Q and the transpose of K ( $K^T$ ) to generate attention scores that represent the level of focus for each element in the sequence. The attention scores are then normalized using a softmax function to obtain attention probabilities (*Prob*). These attention probabilities are then used to compute a weighted sum of V. The output matrices from each head are subsequently concatenated. Thirdly, the concatenated results are passed through another FC. The output matrix of the MHA is then subjected to layer normalization, and the results are added to the input hidden states of the MHA (see Fig. 2.1).

The FF following the layer normalization consists of two FC with an activation layer (e.g., ReLU) in between. This structure enlarges the hidden dimension of the input hidden states, then reduces it back to the original dimension. As a result, the model can capture patterns that occur at any position in the sequence. The first FC enlarges the hidden dimension of the input hidden states from  $D_h$  to  $4 * D_h$ , and the second FC reduces the dimension back to the original  $D_h$ .

Recently emerged Transformer–based models still maintain this architecture. However, as models grow larger and to address the limitations of the attention mechanism, various Transformer variants have appeared. In particular, there are many large models that increase the dimension  $D_h$  and the number of encoders/ decoders. These models show performance surpassing humans in various tasks. It leads to trigger a new boom in artificial intelligence. In the following section, we show the Transformer model trends.

#### 2.1.2 Transformer model trends

The field of NLP has been witnessing significant advancements, primarily driven by the use of Transformer models. The most dominant strategy to improve performance in these models has been the increase in model size [28]. The trend of increasing model size is particularly evident in the development of large language models (LLMs) that followed GPT-2 [51]. These models are characterized by their ability to demonstrate few- or even zero-shot learning capabilities when pretrained on large datasets. For instance, GPT-J is an LLM with 6 billion parameters and trained on 400 billion tokens. It was followed by GPT-3 [5] from OpenAI, a family of decoder-only models, the largest of which has 175 billion parameters and is trained on 300 billion tokens. Recently, PaLM2 [2] was released from Google, the largest model in this family having 300 billion parameters and trained on 1 tillion tokens in various languages.

In tandem with the trend of increasing model size, there has been a notable focus on making attention mechanisms more efficient, especially for processing documents with longer sequence lengths. Sparse attention has emerged as a piv-

otal trend in Transformer models. This technique has been adopted by models such as Longformer [4] and BigBird [67], which have introduced explicit sparse bias in their self-attention mechanisms. This innovation has effectively reduced the computational complexity from  $O(L_{in}^2)$  to  $O(L_{in})$ , making these models more efficient. For instance, Longformer from AllenAI employs a combination of local attention (attention only calculated from a fixed window size around each token) and global attention (only for specific task tokens like [*CLS*] for classification) to create sparse attention scores instead of full attention scores. The BigBird [67] model, proposed by Google, employs a unique sparse attention mechanism that consists of three main components: local, global, and random attention. Local and global attention are similar to Longformer's, except that BigBird's are composed as blocks. In addition to local and global attention, the model also includes random attention. The model starts with a sliding window on the block, then a random subset of all connections is replaced with a random connection, while retaining the other local connections.

These sparse attention mechanisms reduce the computational and memory requirement from quadratic to linear in the sequence length, thereby enabling the handling of longer sequences.

#### 2.2 Transformer Inference

The inference of BERT family models, as shown in the left of Fig. 2.2, processes multiple input tokens simultaneously. For example, when preprocessing the sentence "I like a cat" with a tokenizer and passing it through a embedding layer, it generates a set of embedding vectors, which is a  $(L_{in}, D_h)$  hidden states. Here,

Lin: Input seqeunce length

D<sub>h</sub>: Hidden dimension

Figure 2.2: Transformer inference with regard to BERT and GPT2.  $L_{in}$  is the input sequence length and  $D_h$  is the size of the embedding vector and also the size of the hidden dimension. This hidden states is passed to the encoder to perform the MHA and FF operations we described earlier. At last, it carries out the last layer (e.g., classification layer in the Fig. 2.2) to obtain the final result. Depending on the task, the last layer is different.

GPT family models, unlike BERT family, are usually divided into a summarization stage and a generation stage. The summarization stage, similar to the BERT type, processes multiple input tokens at once. However, in the Generation stage, it processes token-by-token. For instance, in the Generation stage (see the right graph in Fig. 2.2), it first takes one new token generated from the summarization stage as input. This one input token, denoted as  $I_2$  in the figure, is converted into an embedding vector through embedding layer and then processed by the decoders. During the decoding process, matrix multiplication in the SDA is carried out in the "Q by  $K^T$ , *Prob* by V" operations, which include the keys and values up to the previous step. To reduce redundant calculations, the previously calculated keys and values are reused. This is often referred to as "storing in the KV cache". The hidden vector generated through the decoders is then converted back into a new token via embedding layer. Text generation continues until an end of token (EoT) index is obtained.

However, high inference cost hinders the use of powerful Transformers for real-world tasks at scale [50]. This cost is often driven by large model size, long input sequences, and inefficient kernel operations. First, large models have a high memory footprint due to both the trained model parameters and the transient state needed during decoding. The model parameters usually do not fit in the memory of a single accelerator chip. Furthermore, key and value tensors of each layer, also known as the KV cache, must be stored in memory during the duration of decoding. This leads to a large amount of memory traffic and a high total memory bandwidth requirement, particularly to meet certain latency targets. Larger models need to be partitioned across many accelerator chips to fit in memory, but this introduces chip-to-chip communication costs. Second, the inference cost from the attention mechanism in large models scales quadratically with the input sequence length. The KV cache is unique for each sequence in the batch, meaning that it grows in size with longer sequences and larger batch sizes. This places a higher demand on memory capacity and bandwidth costs. For instance, for a 500B+ model with multihead attention and a context length of 2048 and a batch size of 512, the KV cache totals 3TB. Third, Sparse attention mechanisms, which are designed to reduce the computational and memory burden of attention operations in Transformer models, come with their own challenges. Sparse attention operations are not as efficiently supported on cur-

Figure 2.3: The sparse attention of a single head in a sparse Transformer. S and P are sparse matrices, and the other matrices are dense.  $L_{in}$  refers to the input sequence length, and  $D_h$  represents the head dimension of a single head.

rent hardware as dense operations. Modern hardware accelerators like GPUs and TPUs are designed to perform dense matrix operations efficiently, but they may not handle sparse operations as well. This mismatch can lead to inefficient utilization of hardware resources, thus increasing the inference cost.

We categorize the Transformer inference according to the model size, input sequence length, and batch size (see Fig. 1.1). In this thesis, we propose Transformer optimization methods to reduce inference cost (e.g., low latency, high throughput, and minimum hardware requirement) for these inference scenarios.

#### 2.3 Sparse Attention–Based Transformers

In a sparse Transformer, SA is performed with multiple heads in the same way as the multi-head attention [61] in a typical Transformer. In other words, in an input matrix of  $(L_{in}, D_h)$ , a single row vector of  $(1, D_h)$  is split by the number of heads, and the matrix of  $L_{in} \times D_h$  generated by applying it to other row vectors is repeatedly applied in parallel with a single head SA. Here,  $L_{in}$  represents the input sequence length,  $D_h$  represents the head dimension of a single head, and  $D_h$  (i.e.,  $D_h \times$  the number of heads) represents the vector size for the entire head.

The SA for a single head sequentially performs sparse operations consisting of SDDMM, scaling and masking, SpSoftmax, and SpMM (see Fig. 2.3). It finally obtains the context ( $C_h$ ) by a single head of query ( $Q_h$ ), key ( $K_h$ ), and value ( $V_h$ ).  $Q_h$ ,  $K_h$ , and  $V_h$  are dense matrices whose shapes are ( $L_in$ ,  $D_h$ ), being split by the number of heads in the query, key, and value of the entire head to perform SA for a single head. The query, key, and value of the entire head are hidden states, dense matrices in which hidden vectors with a vector size of  $D_h$ are stacked in  $L_{in}$  and are calculated by multiplying them with different weight matrices of ( $D_h$ ,  $D_h$ ). The hidden states refer to the input sequence consisting of  $L_{in}$  tokens, an ( $L_{in}$ ,  $D_h$ ) dense matrix, which is the output matrix of the embedding layer, the previous layer of SA.

We describe each sparse operation below: SDDMM is a sparse operation that multiplies two dense input matrices to obtain a sparse output matrix. The sparse output matrix is generated by loading and calculating only the portion of the non-zero output elements using the metadata of a sparse format. In SA, SDDMM is an operation that multiplies  $Q_h$  and  $K_h$  to obtain an attention score (*S*) that shows the relevance between tokens (a word or word piece, which is different from the tokenizing methods [54, 63]).

Scaling is an element-wise operation; a sparse matrix calculated by SD– DMM is multiplied by scaling factors (SF= $1/\sqrt{D_h}$ ). It alleviates the gradient vanishing problem, pushing the softmax function into regions with extremely

Figure 2.4: Various atomic sparse patterns in the existing sparse Transformers. From left to right, the patterns are listed from the least to the most structured pattern. In a sparse pattern, a row refers to the query vector and a column refers to the key vector. Gray squares refer to the valid elements resulting from an inner product of corresponding query and key vectors. Blank squares are invalid elements, and the corresponding query and key vectors are not used for the operations.

small gradients as the result of SDDMM growing large in magnitude [61].

Masking is an operation that masks out invalid elements in the mask matrix. If the input sequence length is smaller than the maximum sequence length the model can process, zero padding is conducted. Masking invalidates the zero– padded parts. In SA, it also masks out the invalid portion of the pre–defined sparsity. For invalidating zero–padded parts and the invalid portion, masking assigns an infinite negative value to them represented in the mask matrix.

SpSoftmax normalizes S to an attention probability (P) to mitigate the scale-up of S following SDDMM, scaling, and masking. SpSoftmax performs row-wise softmax only on non-zero elements of S, a sparse matrix represented by a sparse format. Similar to S, P is also an attention map expressing input tokens' importance.

SpMM is a sparse operation that multiplies the sparse input matrix represented by a sparse format with a dense input matrix to obtain a dense output matrix. The output matrix is calculated by loading only the non-zero elements in the input sparse matrix using the metadata of the sparse format and the corresponding element in the other input dense matrix. In SA, the left-hand side matrix is a sparse matrix P, the right-hand side matrix is a dense matrix  $V_h$ , and the output matrix is a dense matrix, referred to as context ( $C_h$ ). Consequently, the context has a higher value for the more important hidden vector, i.e., it gives valuable weight to an important token; hence it can attend to important information.

## 2.4 Singular Value Decomposition (SVD)

Singular value decomposition (SVD) is a well-known technique for decomposing a matrix into three matrices, namely, the left singular matrix U, the singular values S, and the right singular matrix V. Given a matrix W of dimensions (K, N), SVD factorizes W into three matrices U, S, and V<sup>T</sup>, such that  $W = U * S * V^T$ , where U is an (K, R) orthogonal matrix, S is an (R, R) diagonal matrix with non-negative values on the diagonal, and V<sup>T</sup> is an (N, R) orthogonal matrix. To compute the low-rank approximation of W, we truncate the U, S, V<sup>T</sup> matrices to a predetermined rank R', where  $R' \ll min(K, N)$ . This truncation results in  $W \approx U_r * S_r * V_r^T$ , where  $U_r$ ,  $S_r$  and  $V_r^T$  represent the truncated matrices with shape of (K, R'), (R', R') and (N, R'), respectively.

#### 2.4.1 SVD-Based Matrix Multiplication in Transformer models

Applying SVD-based low-rank approximation to the Transformer model enables model compression. By factorizing the weight matrices involved in the matrix multiplications of Transformer models, we can obtain smaller matrices,  $U_r$ ,  $S_r$ , and  $V_r$ , decomposed by SVD. In addition, the  $S_r$  matrix with dimensions (R', R') can be multiplied by either the U<sub>r</sub> matrix with dimensions (K, R')or the V<sub>r</sub> matrix with dimensions (N, R'). This implies that the actual weight parameter only needs to retain two matrix parameters with dimensions equivalent to those of U<sub>r</sub> and V<sub>r</sub><sup>T</sup>. Therefore, if a weight matrix W with dimensions (4096, 4096) is compressed by SVD, with R' being 1024, it can be decomposed into matrices U<sub>r</sub> and V<sub>r</sub> with dimensions (4096, 1024) and (1024, 4096), respectively. This makes it possible to achieve a compression ratio of 2 : 1.

During inference, applying the SVD approach to matrix multiplications in Transformer models can reduce execution time by decreasing computation. Matrix multiplication accounts for the most of time in Transformer model [48], and the computation of this matrix multiplication based on SVD (SVD-matmul, i.e.,  $\mathbf{Y} = \mathbf{X} * \mathbf{U}_r * \mathbf{V}_r$ ) can be reduced as the rank size decreases. For example, if the dimensions of X and W are (M, K) and (K, N), respectively, and the dimensions of  $\mathbf{U}_r$  and  $\mathbf{V}_r$  obtained by factorizing W via SVD are (K, R')and (R', N), then the computation of the matrix multiplication changes from 2MKN to 2MR'(K + N). If  $R' \ll min(K, N)$ , the computation is reduced. For example, if M = K = N = 4096 and R' = 1024, the computation of the former is twice that of the latter. As R' decreases (i.e., higher compression ratio), the computation decreases even further. Therefore, we can accelerate Transformer models using SVD through the decrease in computation of matrix multiplication.

However, SVD-matmul (i.e.,  $\mathbf{Y} = \mathbf{X} * \mathbf{U}_r * \mathbf{V}_r$ ) is inefficient on GPUs. This is particularly noticeable in inference scenarios involving skewed matrix multiplication (i.e., including tall-and-skinny matrices) or small matrix multiplication (e.g., matrix shape dimensions under 1024). Without fusing the SVD-matmul (i.e., two GEMMs such as  $P = X * U_r$ ,  $Y = P * V_r$ ), there are two memory–bound matrix multiplications in the skewed matrix multiplication. It leads to a memory bandwidth bottleneck and could waste computing resources [8]. Additionally, if the partial matrix P is too large to be stored in the L2 cache, unnecessary memory accesses may occur. We can alleviate the above problems by fusing the SVD–matmul (i.e., launching  $Y = X * U_r * V_r$  with one kernel), but this could lead to unnecessary data loading or multiplication. To obtain an output tile, re– peatedly loading the whole U leads to increase the memory traffic and additional multiplication operations. This hinders performance because GPU compute and memory resources could be underutilized. To address the limitations of SVD– matmul and offer a more efficient solution for matrix multiplication, especially when implemented on GPUs, we propose a tiled singular value decomposition (TSVD) approach.

## 2.5 Parameter Efficient Fine-Tuning (PEFT)

Parameter-efficient fine-tuning (PEFT) [7, 16, 26] is a cutting-edge approach designed to mitigate the challenges that arise when fine-tuning large models (LMs). PEFT methods only fine-tune a small number of model parameters while freezing most parameters of the pre-trained models. This approach decreases the computational and storage costs and overcomes the issue of catastrophic forgetting observed during full fine-tuning of LMs. PEFT methods also generalize better to out-of-domain scenarios and are useful in low-data regimes. Furthermore, PEFT methods allow for portability, enabling users to get tiny checkpoints worth a few MBs compared to the large checkpoints of

full fine-tuning. This is possible because the small trained weights from PEFT methods are added on top of the pre-trained models, so the same model can be used for multiple tasks by adding small weights without having to replace the entire model.

## 2.6 Graphics Processing Unit (GPU)

Modern NVIDIA GPU architecture includes arrays of streaming multiprocessors (SMs), and multiple SMs are connected to the L2 cache and device memory via the interconnect. In an SM, there are CUDA cores for arithmetic operations, special function units for transcendental functions, and tensor cores that support tensor operations to accelerate machine learning workloads. Register files (RFs), L1 cache, and shared memory (SMEM) store temporary data. L1 cache and SMEM are combined into a single memory block, which supports both types of memory accesses to provide bandwidth and capacity efficiently starting from the Volta architecture. The Ampere architecture starts to provide a new load–global–store–shared asynchronous copy instruction that saves SM internal bandwidth by bypassing the L1 cache and the RFs.

A GPU operates in a single instruction multiple thread manner, and a GPU kernel spawns numerous threads and processes them in parallel. These threads constitute a thread hierarchy consisting of thread, warp, thread block (TB), and grid. The consecutive 32 threads compose a warp, multiple warps compose a TB, and multiple TBs compose a grid. A kernel executes one or more grids in parallel. Modern GPUs can process up to four warps simultaneously within each SM, where an SM allocates tasks in units of TBs. One SM can allocate multiple

TBs if there is no capacity limit on the SMEM or RFs. When the operation for a single TB finishes, the next TB is assigned to the SM in a round-robin manner.

Besides CUDA cores, the Volta architecture starts to add tensor cores to the SM, drastically speeding up tensor operations. A tensor core performs one  $4\times4$  matrix multiplication and accumulation in a single cycle, supporting FP16/FP32 mixed precision [11, 12].

NVIDIA GPUs introduce the concept of streams [36], a sequence of commands executed in order (i.e., possibly issued by different host threads) to manage concurrency by executing asynchronous commands. Multi-stream fully utilizes hardware resources by enabling concurrent execution of different streams.

# Chapter 3

# Multigrain

# 3.1 Contribution

We propose Multigrain, a new Transformer-specific optimization approach, to accelerate sparse operations on the compound-sparse patterns to overcome the problems of the aforementioned approaches. Multigrain can solve the problems of the existing solutions while maintaining the advantages of the coarse-grained and fine-grained approaches as much as possible and mitigating the disadvan-tages.

## 3.1.1 Multigrain mechanism

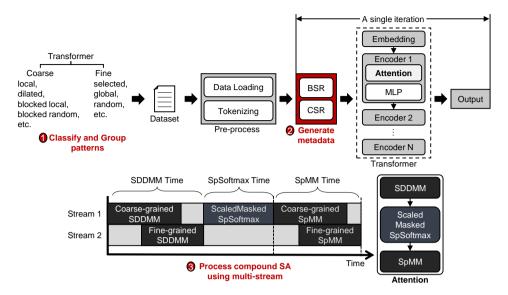

Sparse patterns (e.g., local, global, and selected) of compound-sparse-pattern based Transformer are determined offline by the model to be used, but the number and position of nonzeros are changed by the input data at every iteration. According to these environmental characteristics, Multigrain mechanism works with the following steps (see Fig. 3.1).

First, we classify and group sparse patterns into the coarse-grained and

This chapter is based on [32].

<sup>&</sup>quot;A Slice and Dice Approach to Accelerate Compound Sparse Attention on GPU" ©2022 by Hailong Li, Jaewan Choi, and Jung Ho Ahn is licensed under CC BY 4.0. https://doi.org/ 10.1109/IISWC55918.2022.00019.

Figure 3.1: A Multigrain mechanism. 1) We categorize sparse patterns into coarse-grained and fine-grained patterns. 2) we generate the metadata (e.g., row offsets and column indices) for the compressed sparse matrices with the model configuration and positions of the special tokens before inferring the model. 3) In the compound SA, either SDDMM or SpMM is executed through both coarse-grained and fine-grained kernels, processed in parallel using multi-stream. SpSoftmax fused with scaling and masking is processed by a single kernel that can handle coarse-grained and fine-grained results represented by different sparse formats.

fine-grained parts according to the spatial locality before processing the sparse Transformer with Multigrain. We regard local, dilated, blocked local, blocked selected, blocked global, and blocked random patterns as the coarse-grained part and selected, global, and random patterns as the fine-grained part. We represent the coarse-grained part where nonzeros are structured and clustered as BSR format and the fine-grained part where nonzeros are unstructured and distributed as CSR format.

Second, when preprocessed input data are fed, we generate the BSR and CSR metadata. We use the window size in the model configuration to generate the BSR metadata for the coarse–grained part; and we use global indices (i.e., start

and end tokens for a sentence, paragraph, and document) from the position of special tokens to generate the CSR metadata for the fine-grained part. However, the positions of special tokens change depending on each example in the datasets; we need to generate the CSR metadata at every iteration. In contrast, we generate the BSR metadata only once due to the fixed window size. We load the generated the metadata to the GPU for reuse in the repeated SA.

Third, we allocate the part represented in BSR format to the coarse-grained kernel and the part represented in CSR format to the fine-grained kernel. In the sparse GEMMs (i.e., SDDMM and SpMM), we process SDDMM/SpMM through both coarse-grained and fine-grained kernels in parallel using multi-stream.

We used a coarse-grained kernel we designed, which will be elaborated on in detail in Section 3.1.2. For the fine-grained kernels, we adopt Sputnik, which supports sparse GEMMs using CSR. We modify it to support half-precision (FP16) operations in SDDMM and optimize it further to achieve 3.3× to 6.2× speedups over the unmodified Sputnik. In SpSoftmax, we fused the scaling and masking operations with the sparse softmax using our customized sparse softmax kernel. In QDS-Transformer, we process SDDMM and SpMM of the local pattern part using our customized coarse-grained kernel using BSR metadata. Moreover, the selected pattern part is processed in the fine-grained kernel using CSR metadata.

We make exceptions for the special sparse patterns similar to the global pattern (a default pattern in the Longformer), whose parts can be processed independently in SpSoftmax and processed as dense operations in the sparse GEMMs. For those patterns, we perform SDDMM and SpMM for the special

Figure 3.2: Hierarchical decomposition of SDDMM with the blocked row splitting scheme.

pattern parts using CUTLASS [1] kernels and perform SpSoftmax using the TensorRT's [60] softmax kernel because these libraries perform more efficiently than Sputnik.

## 3.1.2 Coarse-grained GPU kernels

We design two new coarse–grained kernels using BSR for the sparse GEMMs (i.e., SDDMM and SpMM), which handle coarse–grained pattern parts. Al– though we can use Triton for the coarse–grained part, it uses an inconsistent blocked sparse format between SDDMM and SpMM, requiring more memory spaces for storing the metadata of the different sparse formats. Also, Triton is not written in CUDA; hence it is difficult to process it with other kernels im– plemented by CUDA concurrently through multi–stream. Our design is on par with Triton in terms of the execution time, and outperforms Triton by 1.32× by 2.02×, particularly in batch processing (see Fig. 3.10).

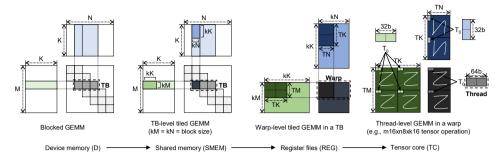

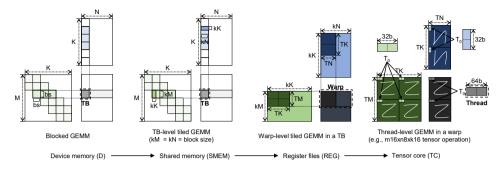

**Coarse-grained SDDMM kernel design:** We design a new coarse-grained SDDMM kernel that embodies a blocked row-splitting scheme following the row-splitting scheme [64]. In the blocked row-splitting scheme, we assign each row block in the output matrix represented by BSR to a single TB. Fig. 3.2 shows

the hierarchical decomposition of SDDMM using the blocked row-splitting scheme. We apply tiling to implement SDDMM efficiently by decomposing the blocked GEMM into a hierarchy of TB-level tiled GEMM, warp-level tiled GEMM, and thread-level tiled GEMM, similar to CUTLASS. *LHS* is the left-hand-side dense matrix, *RHS* is the right-hand-side dense matrix, and *OUT* is the sparse output matrix represented by BSR. The blocked GEMM, a part of SDDMM, is handled by a single TB. Each TB computes its output non-zero blocks (*OUT* blocks) in a row by iteratively loading the matrix blocks from *RHS* and *LHS*.

To exploit locality and parallelism, we partition the blocked GEMM into a TB-level tiled GEMM. We empirically set kM and kN, the sub-tile sizes of the column and row dimensions, as the block size of the non-zero blocks because the maximum number of TBs allocated to SM is limited depending on the memory resources actively used by a TB. A sub-tile block, a single non-zero block of the output matrix (*OUT* block), is obtained by accumulating the products of matrices by stepping through the *K* dimension (i.e., the row dimension in the *LHS*, and the column dimension in the *RHS*) in blocks. Then, the TB processes a series of different output non-zero blocks in the row sequentially to get the entire output row blocks. Thus, we reuse the LHS block repeatedly when processing *OUT* blocks sequentially in the TB-level tiled GEMMs, during which we load data from device memory (*D*) to *SMEM* for data reuse.

In processing warp-leveled GEMM, we still follow the blocked row-splitting scheme. We assign each output row block on the warp level to a single warp. A warp performs a matrix multiply-accumulate (MMA) operation using the tensor core with an m16n8k16 shape supporting FP16 operations. We prevent

Figure 3.3: Hierarchical decomposition of SpMM with the blocked onedimensional tiling scheme.

overflow by using an MMA instruction that supports FP32 for the data type of the output element. We split the warp-level *LHS* blocks and *RHS* blocks into kK dimensions (i.e., the row dimension of the warp-level *LHS* and the column dimension of the warp-level *RHS*, as shown in Fig. 3.2) to reuse registers (*REG*). If the warps inside a TB use too much of *REG*, we enforce SM to use fewer TBs and decrease the occupancy of GPU. It degrades the GPU performance because low occupancy always reduces the ability to hide latencies.

We use software pipelining (double buffering) to hide the latency of memory operations. The method feeds the output of each stage to its dependent stage during the next iteration and executes all stages of the GEMM hierachy in parallel within a loop. We eliminate the latency of the *RHS* loading from device memory to *SMEM* by double buffering the tile size of *SMEM* used by the *RHS*.

**Coarse-grained SpMM kernel design:** Our coarse-grained SpMM kernel uses a blocked one-dimensional (1D) tiling scheme. It follows the blocked row splitting scheme like our SDDMM, except that a single TB is not mapped to an entire output row block, but similar to the 1D tiling scheme [20], where we shard the output matrix into 1D tiles and map independent TBs to each tile.

We empirically set the output tile size the same as the non-zero block of BSR. Fig. 3.3 shows the hierarchical decomposition of SpMM using the blocked 1D tiling scheme, and we also apply tiling to implement SpMM efficiently, similar to our SDDMM kernel. *LHS* is a sparse input matrix represented by BSR, *RHS* is a dense input matrix, and *OUT* is a dense output matrix.

In a blocked GEMM, we accumulate the products of matrices by loading non-zero blocks of the *LHS* and the corresponding *RHS* and obtain the *OUT* blocks. However, if the number of non-zero blocks is large, a TB cannot load all LHS non-zero blocks at once due to the limited memory resources in the SMs. Therefore, we partition the blocked GEMM into the TB-level tiled GEMMs.

In the TB-level tiled GEMM, we accumulate the products of matrices by stepping through the non-zero blocks in a row of the sparse matrix to obtain the OUT blocks. We apply a tiling structure to reuse additional *OUT* blocks and allocate more TBs to SM. To process a single non-zero block, we split each non-zero block of *LHS* and the corresponding block of *RHS* into the *K* dimensions, and we load the slice of *LHS* and *RHS* to get the *OUT* block. Therefore, an *OUT* block can be reused by the number of non-zero blocks of *LHS* and the number of slices in a non-zero block. First, we store the split slice of the *LHS* block and the *RHS* block in *SMEM* and then use the warp-level tiled GEMM. Second, *SMEM* stores twice as much the slice of the *LHS* and *RHS* blocks. Similar to SDDMM, this is to use software pipelining to hide latency for data movement. The number of TBs that can be allocated in an SM is more limited by *REG* than by *SMEM* because *REG* is generally smaller than *SMEM* available for TB in an SM. The warp-level tiled GEMM follows the blocked row-splitting scheme, and we implemented the operations in the same

way as SDDMM.

### 3.1.3 Compound sparse softmax GPU kernel

In SpSoftmax, we also design a new sparse softmax kernel. As opposed to SDDMM and SpMM, we use a single sparse softmax kernel to process the outputs of coarse-grained and fine-grained kernels altogether. It is difficult to obtain accurate softmax results with one type of SDDMM output if coarse-grained and fine-grained sparse patterns are in the same row as softmax sweeps all row elements (e.g., find the max or exponential sum). Prior to the sparse softmax operation, we process scaling and masking operations to reduce the memory access.

Before running the model, we invalidate the overlapped parts if the coarsegrained and fine-grained patterns are overlapped. It avoids inaccuracies from the softmax operations due to the overlapped fields. We use a mask matrix, an attention map where valid elements are represented as zeros and invalid elements are infinite negative values. The valid elements refer to the coarse-grained pattern because some non-zero blocks represented as BSR for the coarse-grained patterns, such as the local pattern, may be sparse. The invalid elements refer to the zero-padding portion to meet the maximum sequence length and overlapped parts between the coarse-grained and fine-grained patterns.

Our compound sparse softmax kernel follows the blocked row-splitting scheme. We assign a single TB to an entire output row block to perform a row-wise softmax operation. As the output row block appears in a combination of the non-zero blocks represented by BSR and the non-zero elements represented by CSR, the output row blocks processed by a single TB depend on the number of the non-zero blocks present in each row. We proceed with the following three steps to perform the safe softmax in each row [37]: First, the max-finding process searches for the maximum of non-zero elements. Second, in the exponential sum process, we subtract the maximum value from each element, exponent the differences, and sum the results. Due to the limited range of values representable in existing GPUs, the subtraction can prevent overflow or underflow during the exponent operations. Finally, the normalization process normalizes each exponent element executed in the previous process to obtain the final output.

In each step, the dataflow sweeps the row elements of the non-zero blocks in the BSR format and the non-zero elements in the CSR format. Taking the max-finding process as an example, we first sweep the non-zero blocks present in each row using the BSR metadata, and we find the maximum value among the ones held by each thread in the coarse-grained pattern part. Next, we sweep non-zero elements in each row using CSR metadata and find the maximum value among elements held by a thread in the fine-grained pattern part. Therefore, each thread holds the maximum value among the swept elements. We find the maximum element by comparing the elements between threads with each other through warp shuffling, which exchanges the register values between threads within the warp. As a result, each thread holds the maximum element among row elements.

However, we make an exception for the special patterns, which areglobal patterns that can perform softmax independently. If the compound sparse pattern includes the special pattern, we process the special pattern parts through the dense softmax kernel and use multi-stream to process with the compound

Table 3.1: Specifications of the GPUs used in the evaluation. \*Peak rates are based on the GPU's base clock. \*\*Recent GPU architectures combine L1 data cache and SMEM functionality into a single memory block.

|                            | A100  | RTX 3090 |

|----------------------------|-------|----------|

| Memory Bandwidth (GB/s)    | 1,555 | 936.2    |

| TFLOPS (FP16 CUDA core)*   | 42.3  | 29.3     |

| TFLOPS (FP16 Tensor core)* | 169   | 58       |

| L1 D\$ per SM (KB)**       | 192   | 128      |

| L2 (MB) \$                 | 40    | 6        |

sparse softmax kernel for other pattern parts in parallel.

## 3.2 Evaluation

We evaluated the effectiveness of Multigrain with various batch sizes in the Longformer and QDS-Transformer, which are sparse Transformers based on the compound SA. To show the performance improvement in the region of interest, we evaluated Multigrain in the various compound patterns. They includes real workloads and synthetic workloads considering that the work-loads will be applied to future models. Finally, we evaluated the performance improvement of the blocked row-splitting scheme. We compared our cus-tomized coarse-grained kernels to Triton at the sparse operation based on various coarse-grained patterns such as a local, blocked local, and blocked random pattern.

## 3.2.1 Experiment Setup

We evaluated inference speed for the sparse Transformer models using FP16 operations in real–world tasks. We use the Longformer and QDS–Transformer models, which achieved superior accuracy due to exploiting the compound SA.

Longformer employs local, selected, and global patterns and records SOTA scores on tasks such as question and answer (QA) and reading comprehension. QDS–Transformer utilizes local and selected patterns and records impressive accuracy on document ranking tasks. We used a large model of Longformer provided by HuggingFace [62] and a base, officially–release model of QDS–Transformer. We measured the end–to–end execution time of Longformer us– ing the hotpotQA [66] dataset, and of QDS–Transformer using the Microsoft MAchine Reading Compensation (MS–MARCO) [41] dataset.

We run the PyTorch 1.8.2 framework [49] on two GPUs with different computational characteristics (A100 [43] and Geforce RTX 3090 [6]) running CUDA toolkit 11.3 [44]. Hardware specifications are shown in Table 3.1. The execution time and the off-chip memory accesses on GPUs are measured through NVIDIA Nsight Compute. We used a deep learning optimization library DeepSpeed (v0.5.1), released by Microsoft, that efficiently handles Transformer models. This library performs SA with OpenAI's Triton (v1.1.1) and processes it in the coarse-grained method. However, it suffers from excessive local memory accesses due to the register spill issue in SDDMM; hence we applied optimizations to SDDMM in our experiments.<sup>1</sup> We used Sputnik, which processes SDDMM and SpMM in the fine-grained method. We extended it for supporting FP16 and batched operations. Moreover, we optimized the SDDMM kernel using the row-splitting scheme instead of the 1D tiling scheme, which is the official Sputnik version.<sup>2</sup> In SDDMM, the 1D tiling scheme wastes the SM

<sup>&</sup>lt;sup>1</sup>In SDDMM (a single batch, four multi-head, and 64 head dimensions), our optimized Triton was  $6.24 \times$ ,  $6.23 \times$ , and  $6.73 \times$  faster than the original version at the local, blocked local, and blocked random patterns, respectively.

$<sup>^2</sup> The SDDMM$  kernel optimized with the row–splitting scheme reduces execution time by 3.3× to 6.2× over the 1D tiling scheme.

Figure 3.4: Execution time and memory traffic of Longformer–large and QDS– Transformer models by applying Triton, Sputnik, and Multigrain. We normal– ized the other results based on the Triton. The absolute execution cycle and memory traffic of each baseline is shown below each model.

resource because warps that do not perform operations cost extra TBs. Thus, it decreases the achieved active warps per SM and induces overhead from context switching in the warp scheduler, and the GPU performance degrades.

## 3.2.2 End-to-End latency on sparse Transformers

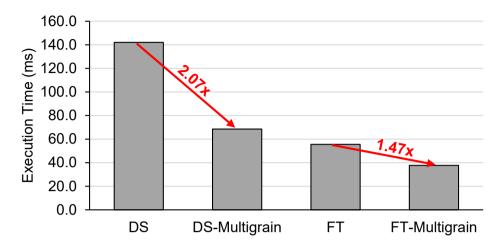

Multigrain accelerated Longformer and QDS–Transformer by optimizing compound SA during the inference. Fig. 3.4 shows the end–to–end execution time and memory traffic of Longformer and QDS–Transformer using Triton, Sput– nik, and Multigrain on the GPUs (A100 and RTX3090) with different com– putational characteristics. In Longformer and QDS–Transformer, Multigrain reduced memory traffic by 2.84× and 3.78×, respectively, compared to Triton, while reducing execution time by 2.07× and 1.55×. Moreover, it reduced the execution time by 2.08× and 1.09×, respectively, with similar memory traffic compared to Sputnik.

Comparing the speedup in Longformer and QDS-Transformer, we observed that the degree of performance improvement varies because each model has a different ratio between the number of the sparse blocks and dense blocks due to the differences in the window size and the maximum sequence length. For example, the ratios between the number of sparse blocks and dense blocks are 1:3 and 2:1, respectively, when performing the sparse operation of a local pattern with a block size of 64 in Longformer and QDS-Transformer. The more lowsparsity sparse blocks there are, the more benefits the fine-grained kernel has over the coarse-grained kernel because the fine-grained kernel only operates on valid elements. Although the coarse-grained kernel improves performance using tensor cores in the fine-grained parts, the gains are negated by the unnecessary computation and memory accesses when processing sparse blocks with low sparsity. By contrast, the coarse-grained kernel performed better than the fine-grain kernel when performing operations with more dense blocks. It benefits from data reuse and high-performance tensor cores. Therefore, Multigrain has higher speedup in Longformer, where there are more dense blocks than QDS-Transformer. Moreover, Multigrain achieved more improvement in Triton than Sputnik for QDS-Transformer.

We evaluated the performance of Multigrain with DeepSpeed [53] and Faster-Transformer [42], libraries that accelerate Transformer-based models (see Fig. 3.5). In the latest FasterTransformer (v5.3), the Longformer is faster than the Deep-Speed version. As a result, Multigrain demonstrates a speedup of  $2.07 \times$  in DeepSpeed and  $1.47 \times$  in FasterTransformer.

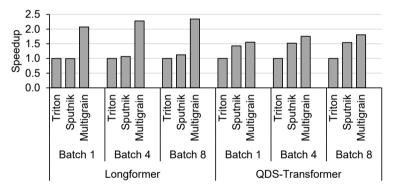

Multigrain exhibits improved performance as the batch size increases (see Fig. 3.6). The sparsity of the sparse patterns in SDDMM and SpMM is similar

36

Figure 3.5: Execution time of Longformer-large at the DeepSpeed and Faster-Transformer libraries.

Figure 3.6: Speedup in Longformer-large and QDS-Transformer at the various batch sizes by applying Triton, Sputnik, and Multigrain.

for each batch. The local pattern beneficial for Triton remains consistent, while the global or selected pattern, which is advantageous for Sputnik, can vary based on the input sequence. Consequently, as the batch size increases, the limitations of Triton and Sputnik become more expanded. However, Multigrain effectively mitigates these shortcomings by fully utilizing GPU resources, leading to notable performance improvement. It shows up to  $2.34 \times$  and  $1.82 \times$  speedups compared to Triton and  $2.13 \times$  and  $1.17 \times$  speedups compared to Sputnik, respectively, in Longformer and QDS-Transformer.

Multigrain achieved a similar degree of performance improvement for both RTX3090 and A100 by reducing memory traffic. However, compared to A100, RTX3090 experiences more performance degradation for the coarse–grained kernel using tensor cores compared to the fine–grained kernel using CUDA cores. It is because the peak floating–point operations per second (FLOPS) value of the tensor cores is reduced more than that of the CUDA cores, as shown in Table 3.1. Therefore, Sputnik showed a greater performance improvement than Triton on RTX3090. In Longformer and QDS–Transformer, it shows 1.10× and 1.64× speedup, respectively. Both coarse–grained and fine–grained ker–nels exist in Multigrain; hence their performances are determined by the GPU's computing abilities. Multigrain shows 1.58× and 1.44× speedups compared to Triton and Sputnik in Longformer, respectively, which shows less performance improvement than A100 due to the performance degradation of the tensor core. By contrast, in QDS–Transformer, Multigrain is 1.68× and 1.02× faster than Triton and Sputnik, respectively.

## 3.2.3 Speedup on the sparse attention

Multigrain improves performance for the compound sparse patterns besides the sparse patterns exploited in the existing sparse Transformers. In the following, we analyzed the results of sparse operations in the various sparse patterns, including existing compound-sparse and synthetic patterns.