# A 2 GHz CMOS Double Conversion Downconverter with Robust Image Rejection Performance against the Process and Temperature Variations

Eunseok Song, Soo-Ik Chae and Wonchan Kim

System Design Group, SoEE, Seoul National University 56-1 Shillim-dong, Kwanak-gu, Seoul 151-742, Korea

## Abstract

This paper presents a 2 GHz image rejection (IR) down-converter implemented in a 0.65  $\mu m$  CMOS technology. It maintains high IR ratio against the process and temperature variations if the on-chip passive RC components are relatively matched. The experimental circuit provides an IR ratio of 40.8 dB without any off-chip filtering or tuning, and dissipates 91 mW at 3.3 V.

### Introduction

The proliferation of portable communication systems has brought about a great demand for low-cost, low-power, small form-factor transceiver. A method that can satisfy these requirements is to develop a monolithic transceiver using a standard CMOS technology. Although the superheterodyne receiver is popular nowadays, it requires many discrete components to suppress the image. Therefore it is difficult to achieve high integration level with conventional superheterodyne systems.

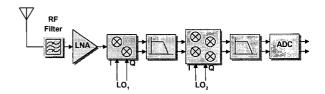

Recently, double conversion receiver, shown in Fig. 1, is often used to reject the image sufficiently without off-chip element [1]-[3]. It suppresses the image through quadrature modulation. Therefore the IR filter and IF filter that are required in a superheterodyne receiver can be eliminated. Consequently, the receiver can be fully integrated from the LNA to the ADC. However, the IR ratio of the double conversion downconverter is very sensitive to I-Q mismatches. The I-Q mismatches are usually caused by on-chip RC variations used in phase shifters. In this paper we propose a double conversion downconverter whose IR ratio is less sensitive to RC variations.

## Image Rejection Downconverter

A. Image Rejection in the Conventional Double Conversion Downconverter

Image rejection in the double conversion downconverter is very sensitive to I-Q mismatches. If the quadrature LO signals are generated from off-chip phase shifters with high accuracy, double conversion downconverter can suppress the image about 40 dB. However, to integrate a receiver fully including a frequency synthesizer, the quadrature LO signals must also be generated from on-chip phase shifters.

Fig. 1. Double conversion receiver. It suppresses the image through quadrature modulation.

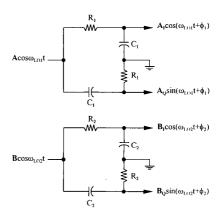

Fig. 2. Quadrature LO<sub>1</sub> and LO<sub>2</sub> signals generation. I-Q mismatches may occur when RC product deviates from designed value.

Fig. 2 shows an example of how to make quadrature  $LO_1$  and  $LO_2$  signals using RC-CR phase shifters. The ratio of  $\mathbf{A_I}$  to  $\mathbf{A_Q}$  and that of  $\mathbf{B_I}$  to  $\mathbf{B_Q}$  in Fig. 2 vary with the R, C and  $\omega$ . Because it is difficult to achieve the exact value of on-chip passive components, I-Q amplitude mismatches can arise. However, the ratio of  $R_1$  to  $R_2$  and that of  $C_1$  to  $C_2$  rarely deviate from the designed value if two phase shifters are placed closely to each other inside a chip. Therefore, if we assume that the relative accuracy error of the passive components is zero, then the following relationship can be obtained.

$$\frac{A_Q}{A_I} = \frac{B_Q}{B_I} \tag{1}$$

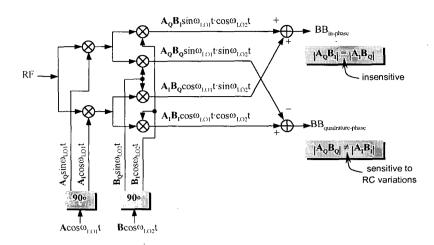

Fig. 3. Conventional double conversion downconverter. Though the on-chip passive elements are relatively matched, IR ratio of BBquadrature-phase is still sensitive to the absolute inaccuracy of passive elements.

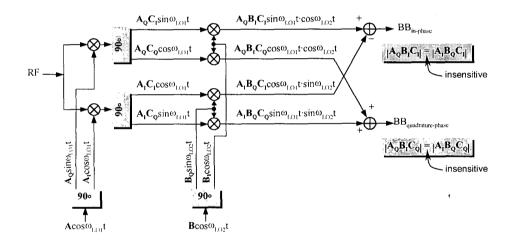

Fig. 4. Proposed downconverter. It maintains good IR ratios for both BB<sub>in-phase</sub> and BB<sub>quadrature-phase</sub> if the on-chip passive elements are relatively matched.

Considering Eq. (1), a conventional double conversion downconverter is drawn in Fig. 3 with variations of signal amplitude. From Eq. (1), we can describe the  $BB_{in-phase}$  signal as follows:

$$\begin{split} BB_{in-phase}(t) &= v_{RF}(t) \cdot \left( A_{Q}B_{I} \sin \omega_{LO1} t \cos \omega_{LO2} t + A_{I}B_{Q} \cos \omega_{LO1} t \sin \omega_{LO2} t \right) \\ &= v_{RF}(t) \cdot \left( A_{Q}B_{I} \sin \omega_{LO1} t \cos \omega_{LO2} t + A_{I}B_{Q} \cos \omega_{LO1} t \sin \omega_{LO2} t \right) \\ &= v_{RF}(t) \cdot A_{Q}B_{I} \sin (\omega_{LO1} + \omega_{LO2}) t \\ &= \left[ K_{w} \cos \omega_{wanted} t + K_{i} \cos \omega_{image} t \right] \cdot A_{Q}B_{I} \sin (\omega_{LO1} + \omega_{LO2}) t \end{split}$$

Here  $\omega_{\text{wanted}} = \omega_{\text{LO1}} + \omega_{\text{LO2}} + \omega_{\text{BB}}$  and  $\omega_{\text{image}} = \omega_{\text{LO1}} - \omega_{\text{LO2}} - \omega_{\text{BB}}$ . After low pass filtering, the signal becomes:

$$BB_{in-phase}(t) = -\frac{K_{w}A_{Q}B_{I}}{2}\sin\omega_{BB}t$$

This equation shows that the image signal is eliminated and only the wanted signal is left if Eq. (1) holds. However, it is not true for the  $BB_{quadrature-phase}$  in Fig. 3 even though Eq. (1) holds. The  $BB_{quadrature-phase}$  signal can be described as:

$$\begin{split} BB_{qurature-phase}(t) &= v_{RF}(t) \cdot \left( A_I B_I \cos \omega_{LO1} t \cos \omega_{LO2} t - A_Q B_Q \sin \omega_{LO1} t \sin \omega_{LO2} t \right) \\ &= v_{RF}(t) \cdot \left[ A_I B_I (\cos \omega_{LO1} t \cos \omega_{LO2} t - \sin \omega_{LO1} t \sin \omega_{LO2} t \right) \\ &+ \left( A_I B_I - A_Q B_Q \right) \sin \omega_{LO1} t \sin \omega_{LO2} t \right] \\ &= v_{RF}(t) \cdot \left[ A_I B_I \cos(\omega_{LO1} + \omega_{LO2}) t \\ &+ \left( A_I B_I - A_Q B_Q \right) \sin \omega_{LO1} t \sin \omega_{LO2} t \right] \\ &= \left[ K_w \cos \omega_{wanted} t + K_i \cos \omega_{image} t \right] \\ &\cdot \left[ A_I B_I \cos(\omega_{LO1} + \omega_{LO2}) t + \left( A_I B_I - A_Q B_Q \right) \sin \omega_{LO1} t \sin \omega_{LO2} t \right] \end{split}$$

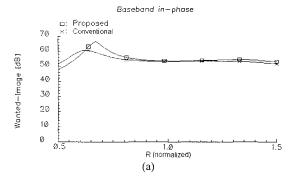

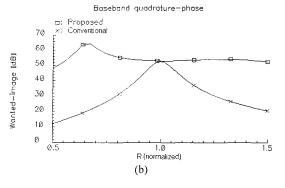

Fig. 5. IR ratio vs. R variation. (a) BB<sub>in-phase</sub>. (b) BB<sub>quadrature-phase</sub>. IR ratio of BB<sub>quadrature-phase</sub> in a conventional downconverter is very sensitive to the absolute accuracy error of R.

Similarly, after low pass filtering, the BB<sub>quadrature-phase</sub> signal becomes:

$$BB_{q-phase}(t) = \frac{K_w A_I B_I}{2} \cos \omega_{BB} t + \frac{K_i \left( A_I B_I - A_Q B_Q \right)}{4} \cos \omega_{BB} t$$

The second term in this equation is the image. Consequently, in a conventional double conversion downconverter, either in-phase or quadrature-phase signal is seriously affected by the absolute inaccuracy of passive components caused by process and temperature variations.

# B. Image Rejection in the Proposed Double Conversion Downconverter

The proposed downconverter is shown in Fig. 4. By introducing two additional phase shifters in the IF signal paths, we can change the connections of  $\mathbf{B}_1 \text{cos}\omega_{\text{LO2}} t$  and  $\mathbf{B}_{\text{Q}} \text{sin}\omega_{\text{LO2}} t$  in  $BB_{\text{quadrature-phase}}$  signal path. Therefore, both equations of  $BB_{\text{in-phase}}$  and  $BB_{\text{quadrature-phase}}$  are well reduced and no image term appears if Eq. (1) holds.

Consequently, the IR ratio of the proposed downconverter is insensitive to the absolute inaccuracy of RC product in a phase shifter and only depends on the relative matching. Because the relative matching property of on-chip passive components is usually satisfactory [4], [5], the IR performance is robust against the process and temperature variations. However there is some attenuation because phase shifters are inserted in the signal paths.

Fig. 6. Microphotograph of proposed image rejection downconverter.

Fig. 7. Chip-on-board (COB) test setup.

# Simulation and Experimental Results

The conventional double conversion downconverter in Fig. 3 and the proposed one in Fig. 4 were compared through simulations with SpectreRF. Fig. 5 shows the simulation results of IR ratio vs. R variation, while maintaining the ratio of  $R_1$  to  $R_2$  in Fig. 2. From Fig. 5 (b), the IR ratio of a conventional downconverter is below 40 dB when R deviates by more than  $\pm 10$  % from the designed value (R=1), even though the relative accuracy error is zero. The proposed downconverter, on the other hand, maintains IR ratio above 50 dB though the R deviates up to  $\pm 50$  %.

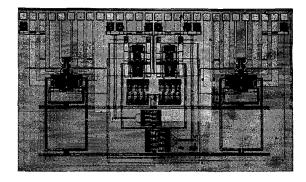

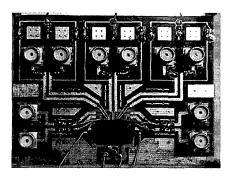

The proposed image rejection downconverter was implemented using 0.65  $\mu m$  CMOS technology. The microphotograph of the IR downconverter is shown in Fig. 6. The active area of the IR downconverter is  $3.3 \times 1.9 \text{ mm}^2$ . The prototype downconverter was assembled with the testboard using a chip-on-board (COB) packaging technology. Fig. 7 shows the COB test setup. This was done to reduce the effects of parasitic lead inductance of package.

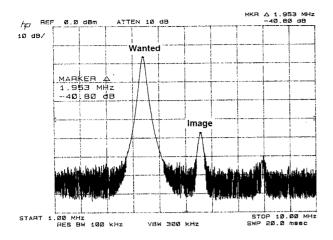

The following measurements have been performed on the realized chip at supply voltage of 3.3 V. The RF signal frequency and power were 2 GHz and -20 dBm, respectively. 1.8 GHz LO<sub>1</sub> and 204 MHz LO<sub>2</sub> signals were applied by the external sources and their power levels were 0 dBm. Fig. 8 shows the downconverter output spectrum. In order to distinguish the image from the wanted in the output spectrum, the image was applied at the frequency of 1.602 GHz, though the real image frequency is 1.6 GHz.

Fig. 8. Measured baseband output spectrum. IR ratio of 40.8 dB was obtained.

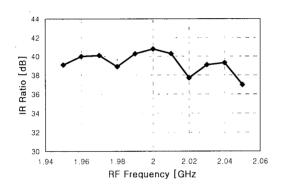

Fig. 9. Measured IR ratio as a function of RF frequency.

The measured power level of baseband signal was -16 dBm at 4 MHz. The downconverted image appeared at the frequency of 6 MHz. The measured IR ratio was 40.8 dB without any off-chip filtering or tuning. The overall IR ratio required in a receiver is about 60 dB in general. However, IR of 40 dB is sufficient for the downconverter core because the off-chip RF filter prior to the LNA offers IR of 20 dB.

Fig. 9 shows the IR ratio as a function of RF frequency. The measured IR ratio almost maintained above 37 dB as the RF frequency varied in the range of 100 MHz. Channel selection is performed by the LO<sub>1</sub>. Because the frequency of LO<sub>1</sub> is very high, the LO<sub>1</sub> phase shifter is less sensitive to the same amount of frequency variation. In order to reduce the effect of frequency and RC variations more, we used 2nd order polyphase filters [6] rather than 1st order RC-CR phase shifters. The output buffer was designed to drive a 50  $\Omega$  load and the total power consumption of the downconverter was 91 mW. The measurement results of the proposed downconverter are summarized in TABLE I.

TABLE I

MEASUREMENT RESULTS OF IMAGE REJECTION DOWNCONVERTER

| · RF frequency            | - 2 GHz                                        |

|---------------------------|------------------------------------------------|

| LO <sub>1</sub> frequency | 1.8 GHz                                        |

| IF frequency              | 200 MHz                                        |

| LO <sub>2</sub> frequency | 204 MHz                                        |

| Baseband frequency        | 4 MHz                                          |

| Silicon Technology        | 0.65 μm CMOS                                   |

| Power Consumption         | 27.7 mA @ 3.3 V                                |

| Conversion Gain           | 4 dB @ 0 dBm LO <sub>1</sub> , LO <sub>2</sub> |

| IR Ratio                  | 40.8 dB                                        |

# Conclusion

A double conversion downconverter with robust IR performance has been described in this paper. The proposed downconverter maintains high IR ratio against the process and temperature variations if the on-chip passive RC composnents are relatively matched.

The prototype circuit was implemented using  $0.65~\mu m$  CMOS technology and it dissipates 91 mW at 3.3~V. The measured IR ratio was 40.8~dB.

### References

- [1] Jacques C. Rudell, et al, "A 1.9-GHz wide-band IF double conversion CMOS receiver for cordless telephone applications," *IEEE Journal of Solid-State Circuits*, vol. 32, pp. 2071-2088, Dec. 1997.

- [2] F. Behbahani, Y. Kishigami, J. Leete and A. A. Abidi, "CMOS 10 MHz-IF downconverter with on-chip broadband circuit for large image-suppression," 1999 Symposium on VLSI Circuits, Digest, pp. 83-86, June 1999.

- [3] Jan Crols and Michiel S. J. Steyaert, "A single-chip 900 MHz CMOS receiver front-end with a high performance low-IF topology," *IEEE Journal of Solid-State Circuits*, vol. 30, pp. 1483-1492, Dec. 1995.

- [4] Phillip E. Allen and Douglas R. Holberg, CMOS Analog Circuit Design, Oxford University Press, Inc., pp. 58-66, 1987.

- [5] Thomas H. Lee, The Design of CMOS Radio-Frequency Integrated Circuits, Cambridge University Press, Chap. 2, 1998

- [6] M. J. Gingell, "Single sideband modulation using sequence asymmetric polyphase networks," *Electrical Commun.*, vol. 48, no. 1-2, pp. 21-25, 1973.