## Three-Stage InP JFET Amplifier for Receiver Optoelectronic Integrated Circuits

JICHAI JEONG, G. P. VELLA-COLEIRO, MEMBER, IEEE, SUNG J. KIM, MEMBER, IEEE, AND JAMES ENG

Abstract—Three-stage InP JFET amplifiers have been fabricated on semi-insulating InP using ion implantation. The amplifiers show dc gain of 43–65 calculated from amplifier transfer characteristics. From highfrequency measurements, a 3-dB bandwidth of 400 MHz and a gain of 38 have been measured from the amplifiers.

InP JFET's have been integrated with InGaAs p-i-n diode for receiver optoelectronic integrated circuits (OEIC's) [1], [2] since JFETs offer the potential of high performance for long wavelength OEIC's. These receiver OEIC's used single stage amplifiers and were limited in performance because of the relatively low voltage gain. Using multistage high gain amplifiers, performance comparable with that of hybrid receivers is expected. In this letter, we report dc and ac performance of three-stage InP JFET amplifiers fabricated on semi-insulating InP substrates. The amplifiers utilized fully ion-implanted InP JFET and were designed to have a gain > 30 and a bandwidth > 350 MHz, making them suitable for use in 600 Mb/s receiver OEIC's.

The processing steps of InP JFET's were described in an earlier paper [3]. Si was implanted at 220 keV with a dose of  $8 \times 10^{12}$  cm<sup>-2</sup> for the channel and 130 keV with a dose of  $10^{13}$  cm<sup>-2</sup> for the ohmic contact layer. For p<sup>+</sup> gate, As/Be coimplantation was performed. The wafers were activated at 850°C for 15 s using a capping layer of borosilicate glass. Ohmic contacts were made using Au-Ge/Ni/Au for n-InP and Au/Au-Zn/Cr/Au for p-InP and then alloyed at 440°C for 40 s.

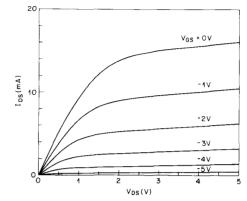

Fig. 1 shows current-voltage characteristics of a typical 1.6  $\mu$ m gate InP JFET for the gate width of 100  $\mu$ m. A maximum transconductance of 90 mS/mm and an output conductance of 4-5 mS/mm were obtained. A cutoff frequency of unity current gain of 10 GHz was measured in InP JFET's with the same gate size [4]. The drain saturation voltage at zero gate voltage was approximately 2 V which is greater than the typical value for GaAs MESFET's. This difference is ascribed to the fact that InP needs a higher electric field to reach the saturation velocity than GaAs. Low gate leakage current of less than 10 nA was observed for gate voltage of -5 V. A turn-on voltage of 1.5 V and a series resistance of 50  $\Omega$  were

Manuscript received February 23, 1990; revised March 29, 1990.

now with the Department of Electronics Engineering, Seoul National University, Seoul, Korea. IEEE Log Number 9036452.

Fig. 1. Drain current-voltage characteristics of a typical InP JFET with a drain saturation current of 150 mA/mm.

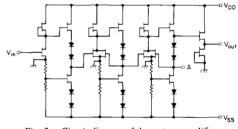

Fig. 2. Circuit diagram of three stage amplifier.

measured in the diode having a dimension of  $5 \times 50 \,\mu\text{m}$ . This diode was used for the level shifting stages of the amplifier.

The circuit diagram of the three stage InP JFET amplifier is shown in Fig. 2. Each stage consists of a gain stage and a level shifting buffer stage, which is similar to the previously reported symmetrical amplifier [3]. In this circuit, two resistors were used for a voltage divider instead of using FET's and localized negative feedback was added to the second and third stages to make the overall gain less dependent on the JFET characteristics and to minimize phase shifts. Wide InP JFET's were added for an output buffer stage capable of driving a 50  $\Omega$  load. In addition to the buffered output, a second output is available at node A. Since the quiescent voltage at this node is zero, it can be connected to the input through a feedback resistor to convert the amplifier to a transimpedance receiver. While all InP JFET's have 1.6 µm gate length, different gate widths were used from 30 to 300  $\mu$ m. All diodes in the level shifting stages have the same size of 5  $\times$  30  $\mu$ m. A gain of 5–7 in the first stage can be expected from [3]. In the second and the third stage, an expected gain of

1041-1135/90/0600-0407\$01.00 © 1990 IEEE

J. Jeong, G. P. Vella-Coleiro, and J. Eng are with AT&T Bell Laboratories, Murray Hill, NJ 07974. S. J. Kim was with AT&T Bell Laboratories, Murray Hill, NJ 07974. He is

Fig. 3. DC characteristics of three-stage amplifier: (a) transfer characteris tics and (b) gain calculated from transfer curve as a function of  $V_{\rm in}$ .

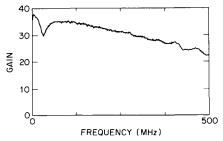

Fig. 4. Frequency response of a typical three-stage amplifier.

each stage was 2.5-3. Therefore, a total gain of the three stage amplifier will be 31-63. The additional gain afforded by a three stage over single stage amplifier is expected to improve the optical sensitivity by  $\sim 3 \text{ dB}$  [5]. Although lower noise operation can be achieved with HEMT's than with JFET's, the increased material and processing complexity is not warranted for many applications.

The measured transfer characteristics and the gain of a typical three stage amplifier are shown in Fig. 3 for  $V_{\rm DD} = 8$  V and  $V_{\rm SS} = -11$  V. Amplifiers could be operated with symmetrical power supply voltages larger than 7 V, which is consistent with the turn-on voltage of two diodes and the drain

saturation voltage. The total gain measured in the fabricated amplifiers was in the range of 43-65. These values are close to the expected total gain by simple calculation. The maximum gain did not occur at zero input voltage for symmetrical supply voltage ( $V_{\rm DD} = -V_{\rm SS}$ ). This asymmetry is due to some resistance being inadvertently present in the source-ground connection of the first stage inverter and it has been corrected in a subsequent redesign. Nonetheless, high gain centered around  $V_{\rm in} = 0$  V can be obtained by using asymmetrical supply voltages.

The packaged amplifiers were mounted into a microwave fixture for the measurement of frequency response using an HP 4195A network analyzer. Capacitors of 2000 pF were mounted on the same package for power supply decoupling. From the measured frequency response shown in Fig. 4, a 3 dB bandwidth of 400 MHz is deduced with  $V_{\rm DD} = 10$  V and  $V_{\rm SS} = -9$  V (the dip in the gain at ~35 MHz is an artifact due to inadequate power supply decoupling).

In conclusion, three-stage amplifiers have been successfully demonstrated using fully ion-implanted InP JFET's. The measured total gain is in the range of 43–65. A 3 dB bandwidth of 400 MHz was measured in the packaged amplifier. High performance receiver OEIC's can be realized using this three stage amplifier.

## ACKNOWLEDGMENT

The authors would like to thank R. A. Resta for dielectric depositions, D. Ingersoll and D. DeBlis for help in processing, F. Elizabeth and J. Collis for help in layout of test patterns, and B. C. DeLoach for support and encouragement.

## REFERENCES

- [1] S. J. Kim, G. Guth, G. P. Vella-Coleiro, C. W. Seabury, W. A. Sponsler, and B. J. Rhoades, "Monolithic integration of InGaAs p-i-n photodetector with fully ion-implanted InP JFET amplifiers," *IEEE Electron. Dev. Lett.*, vol. 9, no. 9, pp. 447-449, 1988.

- [2] W. S. Lee, S. A. Kitching, and S. W. Bland, "Monolithic integration of fully ion-implanted lateral GaInAs pin detector/InP JFET amplifier for 1.3–1.55 μm optical receivers," *Electron. Lett.*, vol. 25, no. 8, pp. 522–523, 1989.

- [3] S. J. Kim, G. Guth, G. P. Vella-Coleiro, "Integrated amplifiers using fully ion-implanted InP JFET's with high transconductance," *IEEE Electron. Dev. Lett.*, vol. 9, no. 6, pp. 306-308, 1988.

- [4] S. J. Kim, J. Jeong, G. P. Vella-Coleiro, and P. R. Smith, "Fully ion implanted InP JFET with buried p-layer," *IEEE Electron. Dev. Lett.*, vol. 11, no. 1, pp. 57-58, 1990.

- [5] G. P. Vella-Coleiro, "Optimization of the optical sensitivity of p-i-n FET receivers," *IEEE Electron. Dev. Lett.*, vol. 9, no. 6, pp. 269– 271, 1988.